Copyright

by

Vinod Viswanath

2013

# The Dissertation Committee for Vinod Viswanath certifies that this is the approved version of the following dissertation:

# Correct Low Power Design Transformations for Hardware Systems

| Committee:                   |   |

|------------------------------|---|

| Jacob A. Abraham, Supervisor |   |

| Adnan Aziz                   | _ |

| Sarfraz Khurshid             |   |

| Lizy John                    |   |

| Rishiyur S. Nikhil           |   |

# Correct Low Power Design Transformations for Hardware Systems

by

Vinod Viswanath, B.E.; M.S.; M.Phil.

#### **DISSERTATION**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

## **DOCTOR OF PHILOSOPHY**

THE UNIVERSITY OF TEXAS AT AUSTIN

August 2013

# Acknowledgments

I would like to thank Professor Jacob Abraham, for his immense patience and confidence in me through the time it took to tie all ends of this thesis. His insight and inspiring discussions played a major role in deciding the course of this thesis. In addition to the research discussions, I would like to particularly acknowledge his Herculean role in helping me get past various administrative hurdles in being able to submit this thesis. Sir, to you, I owe this thesis.

In 2001, when I was trying to transfer from Yale to UT, Professor Adnan Aziz was responsible in making a quick admission possible for me. I fondly remember attending Adnan's group discussions, and discussing Quadratic Forms and Lyapunov Stability functions. Thank you Adnan, for the stimulating conversations, I still cherish them.

Dr. Rishiyur Nikhil was one of the first reasons I decided to do research. I met him in December of 1996 when I was in my undergraduate junior year, at an IEEE conference in Trivandrum, where he was giving a keynote address. It was one of the most inspiring events of my life at that time, and immediately resulted in my pursuing research and a Masters and PhD degree. Nikhil, I'm always thankful to you for seeding the joy of research in a 19-year old's mind.

I would like to thank the other members of my committee, Professors Sarfraz Khurshid and Lizy John for supporting me through my candidacy. I would also like to thank my lab-mate and a dear friend from my UT days, Shobha Vasudevan. We worked together on a lot of research, ate late night donuts, wrote papers, and worked very well together. Shobha, I'm ever grateful to you, for keeping me going in good times and bad.

This work has meandered through different research topics and jumped through administrative hoops. None of this would have been possible without the unquestioned support of various admin staff, and Melanie Gulick in particular. Melanie, thanks for being so kind, thoughtful and sweet during the entire process. You are a gem. I would also like to acknowledge all my friends (too many to list here!) for their support in this process.

Lastly, and perhaps therefore, for the most motivation and support, I would like to thank my wife Roopa Taranath. She urged me to move back to Austin to finish the last part of my research and write the thesis. She has been accommodating of all my, sometimes absurd, demands and moods during this process. Thank you, Roopa, for your considerable patience and an irrational belief in my abilities. To you, I dedicate this thesis. There were times when I thought you wanted it more for me, than I wanted it myself.

# Correct Low Power Design Transformations for Hardware Systems

Publication No.

Vinod Viswanath, Ph.D.

The University of Texas at Austin, 2013

Supervisor: Jacob A. Abraham

We present a generic proof methodology to automatically prove correctness of design transformations introduced at the Register-Transfer Level (RTL) to achieve lower power dissipation in hardware systems. We also introduce a new algorithm to reduce switching activity power dissipation in microprocessors. We further apply our technique in a completely different domain of dynamic power management of Systems-on-Chip (SoCs). We demonstrate our methodology on real-life circuits.

In this thesis, we address the dual problem of transforming hardware systems at higher levels of abstraction to achieve lower power dissipation, and a reliable way to verify the correctness of the afore-mentioned transformations. The thesis is in three parts. The first part introduces *Instruction-driven Slicing*, a new algorithm to automatically introduce RTL/System level annotations in microprocessors to achieve lower switching power dissipation. The second part introduces *Dedicated Rewriting*, a rewriting based generic proof methodology to automatically prove correctness of such high-level transformations for lowering power dissipation. The third

part implements *dedicated rewriting* in the context of dynamically managing power dissipation of mobile and hand-held devices.

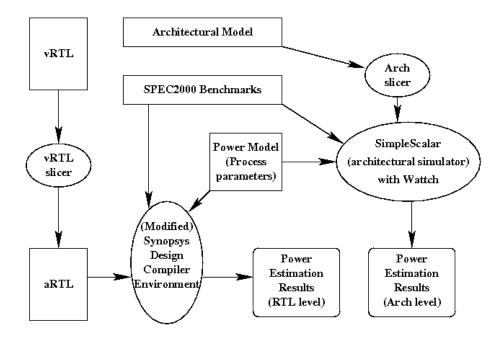

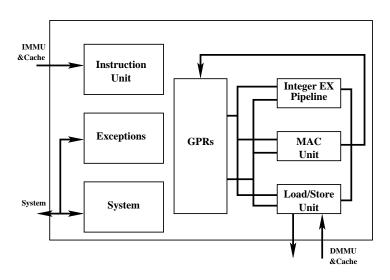

We first present *instruction-driven slicing*, a new technique for annotating microprocessor descriptions at the Register Transfer Level in order to achieve lower power dissipation. Our technique automatically annotates existing RTL code to optimize the circuit for lowering power dissipated by switching activity. Our technique can be applied at the architectural level as well, achieving similar power gains. We first demonstrate our technique on architectural and RTL models of a 32-bit OpenRISC pipelined processor (OR1200), showing power gains for the SPEC2000 benchmarks. These annotations achieve reduction in power dissipation by changing the logic of the design. We further extend our technique to an out-of-order superscalar core and demonstrate power gains for the same SPEC2000 benchmarks on architectural and RTL models of PUMA, a fixed point out-of-order PowerPC microprocessor.

We next present *dedicated rewriting*, a novel technique to automatically prove the correctness of low power transformations in hardware systems described at the Register Transfer Level. We guarantee the correctness of any low power transformation by providing a functional equivalence proof of the hardware design before and after the transformation. Dedicated rewriting is a highly automated deductive verification technique specially honed for proving correctness of low power transformations. We provide a notion of equivalence and establish the equivalence proof within our dedicated rewriting system. We demonstrate our technique on a non-trivial case study. We show equivalence of a Verilog RTL implementation of a

Viterbi decoder, a component of the DRM System-On-Chip (SoC), before and after the application of multiple low power transformations.

We next apply *dedicated rewriting* to the broader context of holistic power management of SoCs. This in turn creates a self-checking system and will automatically flag conflicting constraints or rules. Our system will manage power constraint rules using *dedicated rewriting* specially honed for dynamic power management of SoC designs. Together, this provides a common platform and representation to seamlessly cooperate between hardware and software constraints to achieve maximum platform power optimization dynamically during execution. We demonstrate our technique in multiple contexts on an SoC design of the state-of-the-art next generation Intel smartphone platform.

Finally, we give a proof of *instruction-driven slicing*. We first prove that the annotations automatically introduced in the OR1200 processor preserve the original functionality of the machine using the ACL2 theorem prover. Then we establish the same proof within our *dedicated rewriting* system, and discuss the merits of such a technique and a framework.

In the context of today's shrinking hardware and mobile internet devices, lowering power dissipation is a key problem. Verifying the correctness of transformations which achieve that is usually a time-consuming affair. Automatic and reliable methods of verification that are easy to use are extremely important. In this thesis we have presented one such transformation, and a generic framework to prove correctness of that and similar transformations. Our methodology is constructed in a manner that easily and seamlessly fits into the design cycle of creating complicated hardware systems. Our technique is also general enough to be applied in a completely different context of dynamic power management of mobile and hand-held devices.

# **Table of Contents**

| Acknov  | vledgm  | nents                                                         | V   |

|---------|---------|---------------------------------------------------------------|-----|

| Abstra  | ct      |                                                               | vii |

| Table o | f Cont  | ents                                                          | xi  |

| List of | Figure  | S                                                             | xiv |

| Chapte  | r 1. I  | ntroduction                                                   | 1   |

| Chapte  | er 2. I | Low Power Techniques, Transformations and Verification        | 11  |

| 2.1     | Low I   | Power Transformations and Techniques                          | 17  |

|         | 2.1.1   | Circuit and Design Optimizations and Considerations for Power | 17  |

|         |         | 2.1.1.1 Transistor Level Optimizations                        | 17  |

|         |         | 2.1.1.2 Combinational Logic Optimizations                     | 19  |

|         |         | 2.1.1.3 Sequential Logic Optimization                         | 20  |

|         |         | 2.1.1.4 Survey of Gate Level Optimizations                    | 21  |

|         | 2.1.2   | Behavioral Level (RTL) Optimizations                          | 22  |

|         | 2.1.3   | Micro Architectural Techniques for Low Power                  | 23  |

|         | 2.1.4   | Dynamic Voltage and Frequency Scaling                         | 24  |

|         | 2.1.5   | Operating System Power Management                             | 27  |

|         | 2.1.6   | Memory Power Management                                       | 29  |

|         | 2.1.7   | Compiler Techniques for Low Power                             | 30  |

|         | 2.1.8   | Surveys                                                       | 32  |

| 2.2     | Low I   | Power Verification                                            | 32  |

|         | 2.2.1   | Pre-Silicon Verification                                      | 34  |

|         | 2.2.2   | Platform Verification                                         | 40  |

| 2.3     | Concl   | usions                                                        | 41  |

| Chapte | er 3. Instruction-driven Slicing: Automatic Insertion of Low Power RTL Annotations 43 |

|--------|---------------------------------------------------------------------------------------|

| 3.1    | Introduction                                                                          |

|        | 3.1.1 Contributions of this work                                                      |

| 3.2    | Instruction-Driven Slicing                                                            |

| 3.3    | Our Technique                                                                         |

|        | 3.3.1 Instruction-Driven Slicing Algorithm                                            |

|        | 3.3.2 Methodology                                                                     |

| 3.4    | OR1200 - a Pipelined OpenRISC Implementation                                          |

|        | 3.4.1 OR1200                                                                          |

|        | 3.4.2 Results for OR1200-RTL                                                          |

|        | 3.4.3 Results for OR1200-Arch                                                         |

| 3.5    | Instruction-Driven Slicing in the PowerPC Microprocessor 64                           |

|        | 3.5.1 PUMA                                                                            |

|        | 3.5.2 Results for PUMA-RTL                                                            |

|        | 3.5.3 Results for PUMA-ARCH                                                           |

| 3.6    | Conclusions                                                                           |

| Chapte | er 4. Dedicated Rewriting: Correctness of Low Power Transformations in RTL 77         |

| 4.1    | Introduction                                                                          |

| 4.2    | Rules                                                                                 |

|        | 4.2.1 Structural Rules                                                                |

|        | 4.2.2 Logical Rules                                                                   |

| 4.3    | Dedicated Rewriting                                                                   |

|        | 4.3.1 <i>derive</i> (): Verilog RTL to TRS rules                                      |

|        | 4.3.2 <i>execute ()</i> : TRS rules to expressions                                    |

|        | 4.3.2.1 Reassignments                                                                 |

|        | 4.3.3 prove (): Equivalence of expressions                                            |

|        | 4.3.4 Our notion of equivalence                                                       |

|        | 4.3.5 Error Detection                                                                 |

| 4.4    | Dedicated Rewriting for Combinational Equivalence Checking: Multiplier Verification   |

| 4.5        | Case Study: Viterbi Decoder                                                | 104 |

|------------|----------------------------------------------------------------------------|-----|

|            | 4.5.1 Combinational low power transformations                              | 107 |

|            | 4.5.2 Sequential low-power optimizations                                   | 108 |

|            | 4.5.3 Optimizations for power and timing                                   | 109 |

|            | 4.5.4 Correctness of low power transformations on the Viterbi de-          | 100 |

| 16         | coder                                                                      |     |

| 4.0        | Discussion and Conclusions                                                 | 113 |

| Chapte     | r 5. Holistic Power Management of SoCs using Dedicated Rewrit              |     |

| <i>5</i> 1 | ing                                                                        | 115 |

| 5.1<br>5.2 | Introduction                                                               |     |

| 5.2        | Rules                                                                      |     |

| 5.3<br>5.4 | Power Constraints Consistency Checker                                      |     |

| 5.5        | Dedicated Rewriting as a Dynamic Power Management Rule Engine              |     |

| 3.3        | Case Studies                                                               |     |

|            | 5.5.2 Panel Self Refresh                                                   |     |

|            | 5.5.3 Results                                                              |     |

|            | 5.5.4 Discussion                                                           |     |

|            |                                                                            | 120 |

| Chapte     | r 6. Correctness of Instruction-driven Slicing                             | 130 |

| 6.1        | Introduction                                                               | 130 |

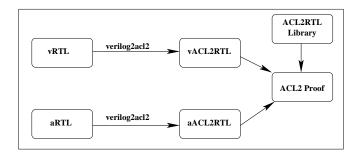

| 6.2        | Automatic Proof Technique                                                  | 131 |

| 6.3        | Interactive Proof by Deductive Verification                                | 135 |

|            | 6.3.1 Proof using the ACL2 theorem prover                                  | 135 |

|            | 6.3.2 Comparing a dedicated rewrite system versus a generic theorem prover | 140 |

| 6.4        | Discussion and Conclusions                                                 | 141 |

| Chapte     | r 7. Discussion and Conclusions                                            | 142 |

| Bibliog    | raphy                                                                      | 146 |

| Vita       |                                                                            | 166 |

# **List of Figures**

| 1.1 | Power consumption trend in Servers and Data Centers (courtesy, Intel)                                                                                                                                                       | 3  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Power consumption trend in Embedded and Handheld Devices (courtesy, Nokia)                                                                                                                                                  | 4  |

| 2.1 | Energy efficient design                                                                                                                                                                                                     | 12 |

| 2.2 | Power dissipation in CMOS devices                                                                                                                                                                                           | 14 |

| 2.3 | Designing for Low Power                                                                                                                                                                                                     | 15 |

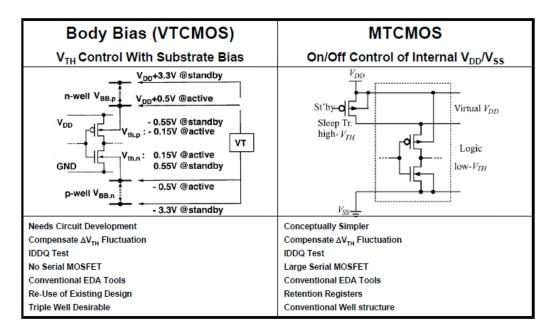

| 2.4 | Body Bias vs. Internal Vdd On/Off [17]                                                                                                                                                                                      | 18 |

| 2.5 | New type of bugs introduced in a low power methodology [153]                                                                                                                                                                | 33 |

| 2.6 | New verification tasks introduced in a low power methodology [153].                                                                                                                                                         | 34 |

| 2.7 | Verification cost of low power transformations                                                                                                                                                                              | 36 |

| 3.1 | Overview of the Instruction-driven Slicing Algorithm for RTL                                                                                                                                                                | 48 |

| 3.2 | Incorporating Instruction-driven slicing into the design flow                                                                                                                                                               | 52 |

| 3.3 | OR1200 Processor Block Diagram                                                                                                                                                                                              | 54 |

| 3.4 | Instruction-driven slicing example                                                                                                                                                                                          | 56 |

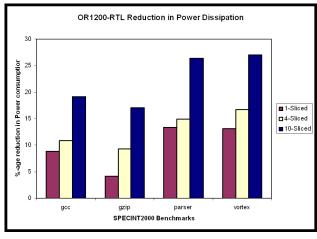

| 3.5 | OR1200-RTL Power dissipation results after slicing on 1, 4 and 10 instructions. These results are for SPECINT2000 benchmarkswith Synopsys clock gating                                                                      | 57 |

| 3.6 | OR1200-RTL Power dissipation results after slicing on 1, 4 and 10 instructions. These results are for SPECINT2000 benchmarkswithout Synopsys clock gating                                                                   | 58 |

| 3.7 | OR1200 reduction in power dissipation for SPECINT2000 benchmarks                                                                                                                                                            | 59 |

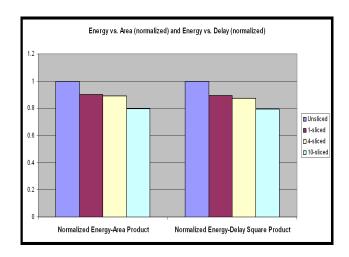

| 3.8 | OR1200-RTL Power reduction compared to increase in area and delay due to slicing. The first set of comparisons depicts the normalized $Energy-Area$ product. The second set depicts the normalized $Energy-Delay^2$ product | 60 |

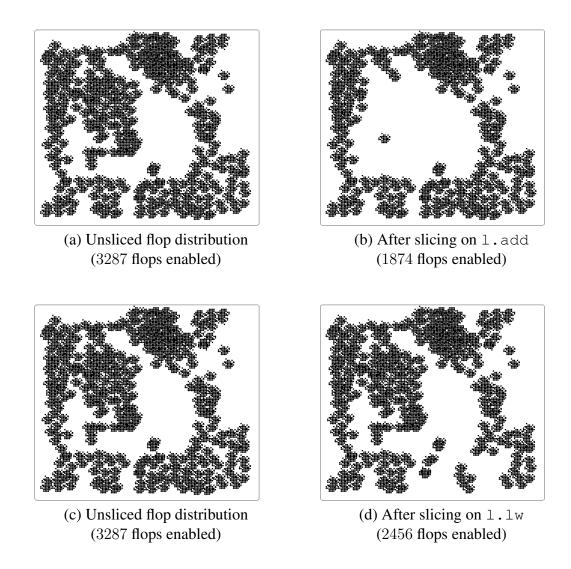

| 3.9 | Flop distribution effect of instruction-driven slicing on 1.add and 1.lw in the OR1200 RTL                                                                                                                                  | 61 |

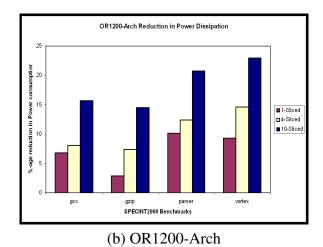

| 3.10 | OR1200-Arch Power dissipation results for SPECINT2000 benchmarks after slicing on 1, 4 and 10 instructions                                                                                                                                                       |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

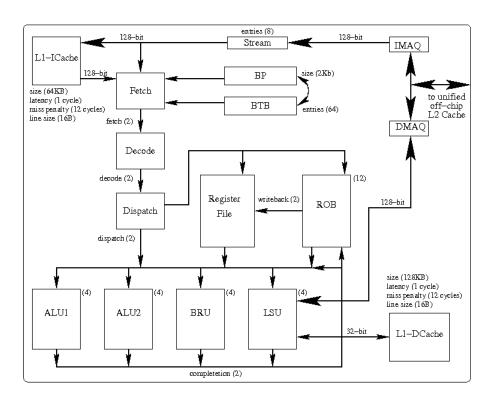

| 3.11 | PUMA Fixed Point Unit Processor Block Diagram 65                                                                                                                                                                                                                 |

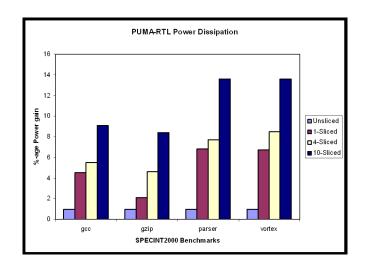

| 3.12 | PUMA-RTL Power dissipation results after slicing on 1, 4 and 10 instructions. These results are for SPECINT2000 benchmarkswith Synopsys clock gating                                                                                                             |

| 3.13 | PUMA-RTL Power dissipation results after slicing on 1, 4 and 10 instructions. These results are for SPECINT2000 benchmarks <b>without</b> Synopsys clock gating                                                                                                  |

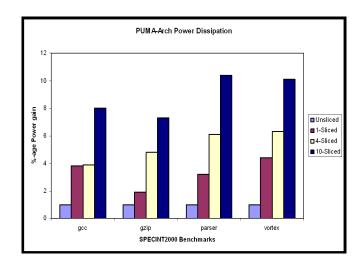

| 3.14 | PUMA-RTL Power gains for SPECINT2000 benchmarks 68                                                                                                                                                                                                               |

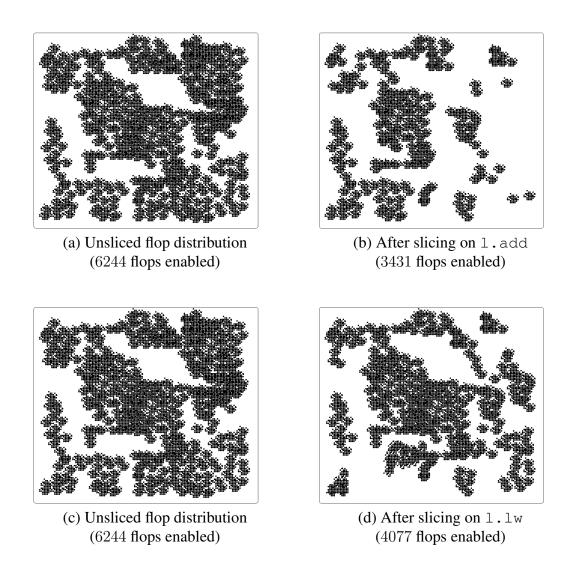

| 3.15 | Flop distribution effect of instruction-driven slicing on 1.add and 1.1w in the PUMA RTL                                                                                                                                                                         |

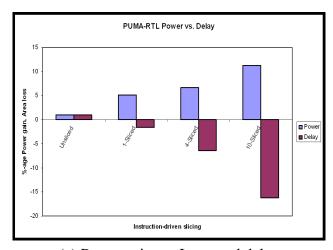

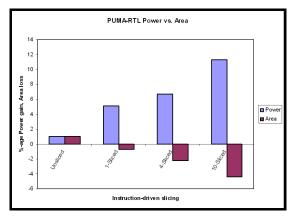

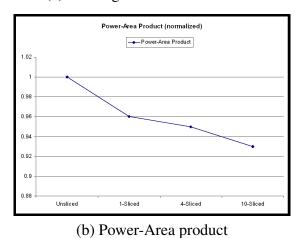

| 3.16 | Time delay and Area estimate for the PUMA RTL                                                                                                                                                                                                                    |

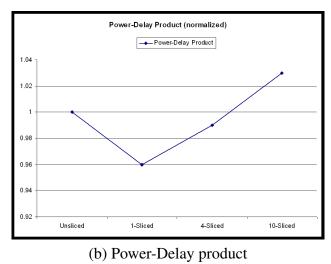

| 3.17 | Power vs. Delay for the PUMA-RTL                                                                                                                                                                                                                                 |

| 3.18 | Power vs. Area for the PUMA-RTL                                                                                                                                                                                                                                  |

| 3.19 | PUMA-Arch Power dissipation results for SPECINT2000 benchmarks after slicing on 1, 4 and 10 instructions                                                                                                                                                         |

| 3.20 | PUMA-Arch Power gains for SPECINT2000 benchmarks                                                                                                                                                                                                                 |

| 4.1  | Term Rewriting Systems: Definitions and concept                                                                                                                                                                                                                  |

| 4.2  | Term Rewriting Systems: Definitions and concept (continued) 82                                                                                                                                                                                                   |

| 4.3  | Sample Verilog RTL and the TRS Rules derived from it 83                                                                                                                                                                                                          |

| 4.4  | Clock gating for lower switching activity power dissipation (Verilog RTL)                                                                                                                                                                                        |

| 4.5  | Clock gating for lower switching activity power dissipation (after translation to TRS)                                                                                                                                                                           |

| 4.6  | Sample logical rules in the dedicated rule database 87                                                                                                                                                                                                           |

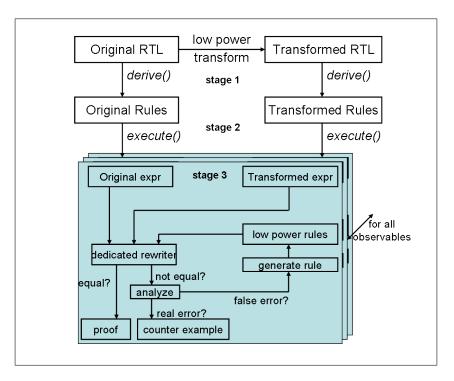

| 4.7  | Dedicated rewriting proof system flow chart                                                                                                                                                                                                                      |

| 4.8  | Dedicated rewriting algorithm                                                                                                                                                                                                                                    |

| 4.9  | Comparison of execution times of Dedicated Rewriting against two commercial equivalence checkers for Booth, Wallace Tree and Dadda Tree multipliers of varying sizes. In each case the golden model was a shift and add multiplier of the corresponding size 102 |

| 4.10 | Number of proof iterations done by $reduce()$ to prove equivalence at the given compare points. The numbers correspond to the $64 \times 64$ Booth, Wallace Tree, and Dadda Tree multiplier designs 103                                                          |

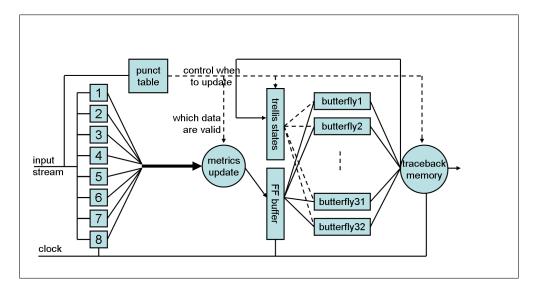

| 4.11 | Basic Viterbi design                                                                                                                                                                                                                                             |

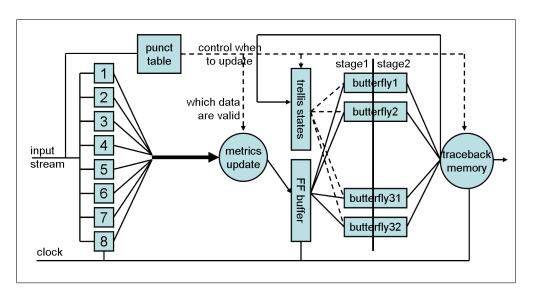

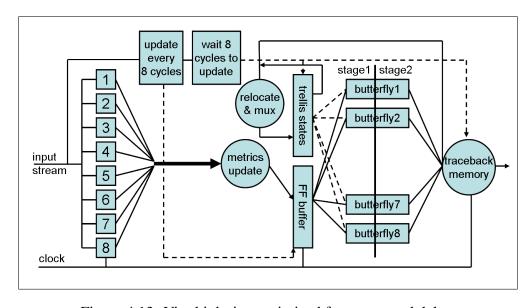

| 4.12 | Viterbi design optimized for low power                                                                                                                                                                                                                                                                                  | 06         |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 4.13 | Viterbi design optimized for power and delay                                                                                                                                                                                                                                                                            | 06         |

| 4.14 | Results of power estimation due to combinational logic low power transformations in the Viterbi decoder. These estimates were based on the macro-modeling technique employed by Gupta <i>et al</i> [50]. These estimates are only over the trellis computation calculation function of the Viterbi decoder              | 08         |

| 4.15 | Results of power estimation after sequential low power transformations in the Viterbi decoder                                                                                                                                                                                                                           | 08         |

| 4.16 | Results of power estimation after sequential optimization for low power and timing in the Viterbi decoder                                                                                                                                                                                                               | 09         |

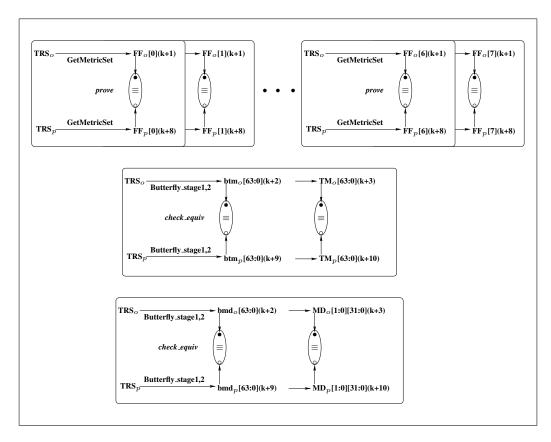

| 4.17 | Picturization of sequential equivalence checking of transformed $TRS_p$ against the original $TRS_o$ of the Viterbi design. The first row is the proof of the FF buffer (over 8 time cycles). The center row shows the proof of the Trellis Computation and the bottom row shows the proof of the MatDec Decision Table | 11         |

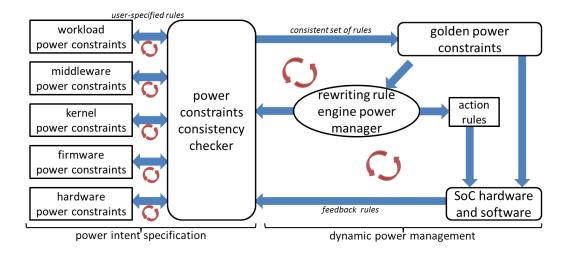

| 5.1  | Rule-based formal Power Specification and Management 1                                                                                                                                                                                                                                                                  | 16         |

| 5.2  | Audio player structural and logical rules                                                                                                                                                                                                                                                                               | 18         |

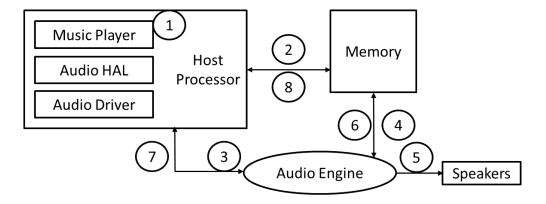

| 5.3  | Low power audio playback policy                                                                                                                                                                                                                                                                                         |            |

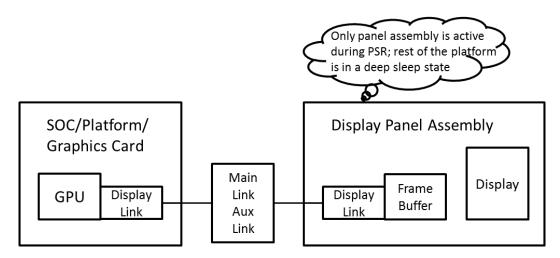

| 5.4  | Panel self refresh policy for video playback and web browsing applications                                                                                                                                                                                                                                              | 27         |

| 5.5  | Summary of results without and with dynamic power management by the rewriting rule engine                                                                                                                                                                                                                               | 29         |

| 6.1  | Instruction-driven slicing example from Figure 3.4 reproduced here for the reader's convenience                                                                                                                                                                                                                         | 32         |

| 6.2  | Rules derived before instruction-driven slicing transformation 1                                                                                                                                                                                                                                                        | 33         |

| 6.3  | Rules derived after instruction-driven slicing transformation 1                                                                                                                                                                                                                                                         | 34         |

| 6.4  | Proof methodology                                                                                                                                                                                                                                                                                                       | 36         |

| 6.5  | Verilog2ACL2 example                                                                                                                                                                                                                                                                                                    | 38         |

| 6.6  | Instruction-driven slicing example after Verilog2ACL2 (pre-transformation)                                                                                                                                                                                                                                              | ion).139   |

| 6.7  | Instruction-driven slicing example after Verilog2ACL2 (post-transformation)                                                                                                                                                                                                                                             | tion). 140 |

|      |                                                                                                                                                                                                                                                                                                                         |            |

# Chapter 1

## Introduction

The importance of power management research has increased tremendously in the last decade with increasing maturity of low power design techniques in the context of micro architecture for small devices and embedded systems. Unprecedented growth in the proliferation of handheld mobile devices has been one of the catalysts for this research, even as power efficient computing remains the holy grail of almost all aspects of computing systems today. There are several trends here that are worth noting.

The last few years have seen the emergence of highly integrated embedded System-on-a-chip (SoC) architectures for several usages and platforms such as high end mobile devices and smartphones. While each SoC component or accelerator can be optimized in various ways, overall platform integration and platform power optimization is a growing challenge since it is not clear how to quantify the impact of applications and workloads on individual platform components. Another trend has been the emergence of multi-core and multi-threaded architectures for all kinds of computing devices, ranging from cell phones to tablets, laptops, and netbooks, to high end computing systems, servers, etc. As the number of cores and threadsper-core increases, such systems present unique challenges in terms of scheduling,

energy efficiency, temperature, heterogeneity, etc.

On such increasingly large and complex digital IC and SoC designs, design power closure and circuit power integrity are starting to become the key engineering challenges, thereby impacting the device's total time-to-market. Power dissipation has emerged as an important design parameter in the design of microelectronic circuits, especially in portable computing and personal communication applications where usage models are becoming increasingly important to the consumer with more and more usages of small devices demanding the performance and connectivity of traditional larger computing systems.

The amount of power consumed by some devices can cause significant design problems. Even in the case of devices intended for use in non-portable equipment where ample power is readily available, power-aware designs can offer competitive advantages with respect to such considerations as size and cost of the power supply and cooling systems. These trends have forced platform designers to abandon traditional performance metrics in favor of performance-per-watt. additionally, aspects like overall platform security, application quality of service, critical thermal conditions, etc. are considered highly critical in the usability of a device.

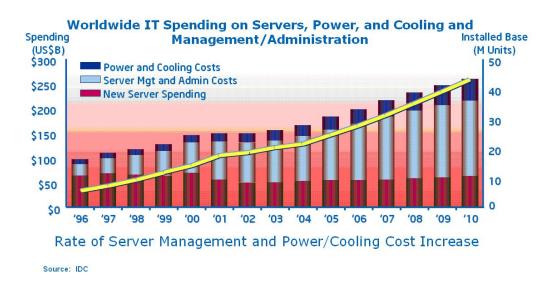

One of the biggest challenges for data-center operators today is the increasing cost of power and cooling as a portion of the total cost of operations. As shown in Figure 1.1, the cost of power and cooling has increased 400%, and these costs are only on the rise. In some cases, power costs account for 40-50% of the total data-center operation budget. The need to deploy more servers to support new business solutions is only increasing. Data centers are therefore faced with the twin problem

Figure 1.1: Power consumption trend in Servers and Data Centers (courtesy, Intel). of how to deploy new services in the face of rising power and cooling costs.

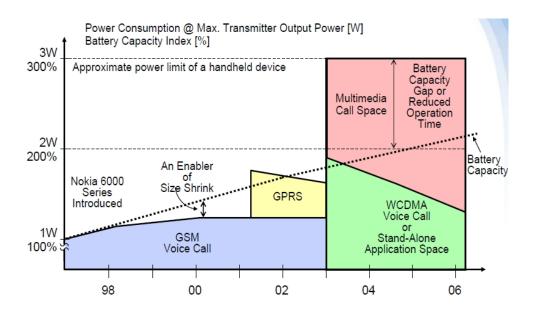

On the other end of the spectrum, power consumption of handheld devices are also on the rise with increasing demands being placed on such devices. Figure 1.2 from Nokia shows the trend of power consumption in the last few years in handhelds. As can be seen, the last few years since 2003 has seen a dramatic increase in the power consumption as well as the usages. Increasingly devices are using up more bandwidth with higher power radios with the emergence of 3G, LTE, etc. and users are expecting the same power of computing from handhelds as was previously being accomplished on larger laptops, desktops, etc.

Power management and optimization research in the last couple of decades has spanned multiple areas - at circuit/design level, hardware and micro-architectural

Figure 1.2: Power consumption trend in Embedded and Handheld Devices (courtesy, Nokia).

level for processors, caches, memories, power management of individual components such as hard drives, external memories, network interfaces. In addition, there has also been research in power-aware compiler optimizations, operating system optimizations for energy efficiency, etc. While power management has traditionally been thought to be for smaller/embedded devices, recently there has been a lot of work on power management in large systems like servers, data centers, etc. There has also been an increased focus toward platform-wide power management that aims to unite different power management techniques and capabilities.

Currently, platform power management broadly falls under two categories. At the one end are low power optimizations implemented by hardware designers like gate level and RTL optimizations, clock and power gating, low power microarchitectural innovations, etc. Power-related constraints are now being imposed throughout the entire design flow in order to maximize the performance and reliability of devices. In the case of today's extremely large and complex designs, implementing a reliable power network and minimizing power dissipation have become major challenges for design teams. Creating optimal low-power designs also involves making trade-offs such as timing-versus-power and area-versus-power at different stages of the design flow. These optimizations are based on generic techniques in the sense that they are done quite independent of the rest of the platform components, and in most cases, with the assumption that hardware is the best judge of what power optimizations to use.

On the other end are the power management techniques that are available for the OS and devices to control. This includes OS control of processor C-states and P-states and device power states, with standardized interfaces like Advanced Configuration and Power Interface (ACPI) that regulate such state control based on the workload and configured policies. In recent years, the focus of power management has moved to more areas than the CPU alone given the trend of increasing power densities of all computing components on the platform. This includes caches, memory modules, buses, storage devices, etc. DRAMs, for instance, have multiple power states (deep and shallow self refresh, support for partial array self refresh, etc.). Both CPU and bus frequencies can be dynamically voltage- and frequency-scaled. In addition, embedded/handheld mobile devices also employ thermal throt-tling to maintain the entire platform and/or individual component under a thermal envelope.

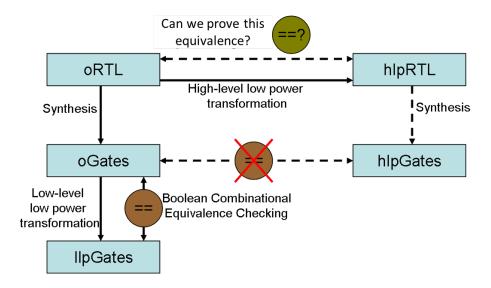

To effectively reduce dynamic power, hardware designers must understand a multitude of low-power transformations and have the practical experience to know when they should be applied. The trade-off between power reduction and verification cost is not always clear which leads the architects and designers to be cautious and conservative in their implementation. Often aggressive low power transformations are not implemented in the design because the verification cost (typically more than 70% of the total time cost) is high enough to adversely impact the total time-to-market. The primary reason for prohibitive verification cost is the hardness of the verification problem. If the low power transformations are at the gate level, then equivalence checking methods can be used to automatically prove the correctness of the transformations. Although there are a few sequential equivalence checking algorithms, they are not widespread in the hardware industry due to their intractable, or hard-to-use nature.

With the emerging mobile internet devices market, the need for quick verification turn-around times on efficient and effective low power transformations is extremely important. The hitherto unexplored (in large measures) area of optimizations is RT-level low power transformations which can utilize the program design information of the RTL in its computation of where to lower dynamic power dissipation. These transformations definitely introduce new variables and state, and change the timing information of the design. Therefore verifying the correctness of these transformations becomes the problem of verifying the equivalence of two sequential circuits. Verifying the equivalence of two sequential circuits is an NP-hard problem. Rather than go after the holy grail, it might be more prudent to focus the

verification problem to equivalence of two sequential circuits that differ only because of the application of a low power transformation. By restricting the domain of difference, one can focus on algorithms that will work well with the domain in context. Therefore, what is of essence, ideally, is effective and efficient RT-level low power transformations, which can be, to the extent possible, automatically proved correct when applied to a particular hardware design.

Platform level optimizations are very coarse-grained and verification of any change in method essentially means a complete re-verification of the system. The optimizations at the platform level include the knowledge of the application and user-intent, and therefore are optimized for exact use-cases of the device. This knowledge is an extremely fine-grained information to achieve a fairly coarse-grained power optimization and has been the way the industry has been trending lately, particularly in the handheld device market.

Given the above challenges, it is very clear that neither hardware nor software in isolation can make the best decision about power and performance management, and neither can these be done for CPU alone, but must now be done at the entire platform level, in a holistic way. Such a holistic power management solution cannot ignore any of the platform components from a power and thermal perspective, neither can it be done in hardware or software alone. We need a synergistic bottom line across RTL, system level, OS level, compiler level, and application level specification of power intent. The kind of information available at a higher level of abstraction at the OS level or even at the application level, is just not visible to the RTL. We need all levels of abstraction of the design to be able to communicate their

power intent to get the most optimized solution. IEEE standard specification format UPF (Unified Power Format [60]) allows us to represent power intent at the RTL and lower levels. We require a method to represent power intent specifications at higher levels of abstraction as well, and a mechanism that can coordinate all such power management capabilities dynamically at runtime with constant feedback from the system about platform conditions (overall power consumption, thermal conditions, etc.).

The key contributions of this thesis are the following:

- We have introduced *Instruction-driven slicing* an effective and efficient RT-level low power transformation in microprocessors and microcontrollers. *Instruction-driven slicing* automatically introduces RTL annotations to achieve lower switching power dissipation.

- We have demonstrated the effectiveness of instruction-driven slicing on OR1200

an in-order RISC pipelined microprocessor and on PUMA, a more complicated out-of-order PowerPC core.

- We have proposed *Dedicated Rewriting*, a proof framework and a methodology to automatically (after some initial training) prove the correctness of RTL low power transformations.

- We have demonstrated the proof methodology on complicated arithmetic circuits, proving correctness of 128-bit Booth multipliers.

- We have demonstrated *dedicated rewriting* on a non-trivial System-on-Chip, the Viterbi decoder that is part of the Digital Radio Mondiale.

- We have given a correctness proof of the *instruction-driven slicing* algorithm as applied to a sample microprocessor. Given that the algorithm is correct by construction, this is sufficient for all microprocessors.

- We have applied *dedicated rewriting* in the context of dynamic power management of SoCs for mobile and hand-held devices in order to achieve communication between power constraints across different levels of design abstraction and to verify consistency of those constraints.

- The dynamic power manager is also a runtime engine which can on-the-fly

drive the device to certain power states, based on the rule engine outcome to

manage user-specified power intent for each workload.

- We demonstrate the holistic dynamic power constraint checker and manager on SoCs built on state-of-the-art Intel smartphone platforms.

The thesis is organized as follows. Chapter 2 gives a survey of low power transformations. We describe our *instruction-driven slicing* algorithm, and its effectiveness in full detail in Chapter 3. We then describe our *dedicated rewriting* system and its application to arithmetic circuits and an SoC in Chapter 4. We further apply our *dedicated rewriting* system in the context of holistic power management of SoCs, in Chapter 5. In Chapter 6 we give a proof of *instruction-driven slicing* in our *dedicated rewriting* system as well as in a general purpose theorem prover, ACL2.

Finally, we discuss some of the relevance and merits of this thesis, and potential future work and conclude in Chapter 7.

# Chapter 2

# Low Power Techniques, Transformations and Verification

Power Management Methodology as an architectural paradigm is still in its infancy. Most techniques in today's designs still follow ad-hoc methodologies. However, most systems are typically amenable to energy efficient design. Figure 2.1 addresses in detail the principles behind energy efficient design. The two key principles are that: (a) apply the lowest voltage to each block at any given time; and (b) keep a block on only when required. There is also a tradeoff between performance and power. In a *race to idle* strategy, the functional block tries to complete its task as fast as possible (high performance) and then shuts off. In a *crawl to idle* strategy, the functional block tries to delay the task as long as possible, while consuming as little power as possible during that process. The power-delay product in any system is conserved. An intelligent management system will choose correctly when to *race* or *crawl* to idle [73].

Sources of power dissipation in CMOS devices are summarized by the following expression:

Switching Short Circuit Leakage Current

$$P = \underbrace{\frac{1}{2} \cdot C \cdot V_{DD}^2 \cdot f \cdot N}_{\text{SC} \cdot V_{DD} \cdot f \cdot N} + \underbrace{I_{leak} \cdot V_{DD}}_{\text{Leak} \cdot V_{DD}}$$

(2.1)

#### Most today's systems are amenable to energy efficient design:

- Systems do not have the same performance needs at all times, and operating at worst case design corner all the time is wasting power.

- The principle of Lowest Active Power is to apply the lowest possible Vdd to each functional block at each instant of time.

- Systems also do not need all functions to be running at the same time.

- The principle of Zero Idle Power is to turn on a block only when necessary; turn it off once it is no longer needed.

- What consumers want in today's complex designs are:

- 1. High Performance

- 2. Multi-media experience,

- 3. Lowest Active Power

- 4. Zero Idle Power.

Figure 2.1: Energy efficient design

where P denotes the total power,  $V_{DD}$  is the supply voltage, and f is the frequency of operation [47], [27].

The first term represents the power required to charge and discharge circuit nodes. Node capacitances are represented by C. The factor N is the switching activity, *i.e.*, the number of gate output transitions per clock cycle. Figure 2.2(a) shows the dynamic power dissipation at a switching gate.

Node capacitance C, depends largely on wire lengths of on-chip structures, and is therefore an architectural metric for determining the trade-offs - for example, between single monolithic large processor cores or smaller processor cores since the latter option is likely to reduce average wire lengths. Similarly, smaller cache mem-

ories or independent banks of cache are likely to reduce wire lengths since many address and data lines will only need to span across each bank array individually.

Supply voltage  $V_{DD}$  is one of the most important aspects of power-aware design given its quadratic influence on dynamic power. We will talk more about this subsequently.

Switching Activity factor N, refers to how often wires actually transition from 0 to 1, or 1 to 0. Techniques such as clock gating are used to save energy by reducing activity factors during a hardware units idle periods.

The clock frequency f, in addition to influencing power dissipation, also influences the supply voltage. Typically, higher clock frequencies will mean maintaining a higher supply voltage. Thus, the combined  $V^2f$  portion of the dynamic power equation has a cubic impact on power dissipation.

Strategies such as dynamic voltage and frequency scaling (DVFS) try to exploit this relationship to reduce (V, f) accordingly.

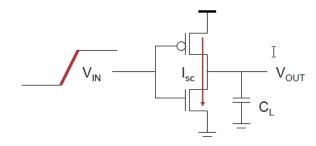

The second term in (Equation 2.1) represents power dissipation during output transitions due to current flowing from the supply to ground. This current is often called short-circuit current. The factor  $Q_{SC}$  represents the quantity of charge carried by the short-circuit current per transition. Figure 2.2(b) shows the power dissipation due to short circuit current. As the output load capacitance increases, the voltage transition time also increases.

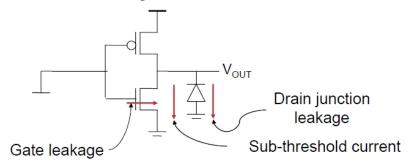

The third term in (Equation 2.1) represents static power dissipation due to leakage current  $I_{leak}$ . Devices source and drain diffusions from parasitic diodes with

(a) Dynamic Power Dissipation due to switching activity.

(b) Power Dissipation due to Short-Circuit current.

(c) Static Power Dissipation due to leakage current.

Figure 2.2: Power dissipation in CMOS devices.

## How do we design for Lowest Active Power and Zero Idle Power?

- Lowest Active Power

- 1. Clock Gating, Device sizing (*old methods*)

- 2. Multi-Vdd (spatial voltage control)

- 3. DVFS (temporal voltage control)

- Zero Idle Power

- 1. Multi-Vt (*old method*)

- 2. Power-gating/retention

- 3. Low Vdd standby, back bias

Figure 2.3: Designing for Low Power

bulk regions. Reverse bias currents in these diodes dissipate power; sub-threshold transistor currents also dissipate power. Figure 2.2(c) shows the leakage power dissipation even when devices are not switching.

Sub-threshold leakage power represents the power dissipated by a transistor whose gate is intended to be off. The main reason behind this leakage is that transistors do not have ideal switching characteristics, and thereby leak a non-zero amount of current even for voltages lower than the threshold voltage.

Figure 2.3 details a list of techniques on how to design based on the principles identified in Figure 2.1. With process technologies below 100 nm, static power consumption has become a prominent and, in many cases, dominant design constraint. Due to the physics of the smaller process nodes, power is leaked from transistors even when the circuitry is quiescent\*. New design techniques have been developed

<sup>\*</sup>No toggling of nodes from 0 to 1 or vice versa

to manage static power consumption. Power gating [151], [154] or power shut-off turns off power for a set of logic elements; back bias techniques [31] are used to raise the voltage threshold at which a transistor can change its state. While back bias slows the performance of the transistor, it greatly reduces leakage. These techniques are often combined with multi-voltages [108] and require additional functionality: power management controllers [33], isolation cells [116] that logically and/or electrically isolate a shutdown power domain from powered-up domains, level-shifters [116], [32] that translate signal voltages from one domain to another, and retention registers [116] to facilitate fast transition from a power-off state to a power-on state for a domain.

In the rest of this thesis, we will refer to the three terms above as switching activity power, short-circuit power and leakage current power. A detailed survey of many of these optimization methods is given in [41]. Most of the optimizations described in this survey concentrate on minimizing switching activity power at various levels of abstraction.

One obvious way to reduce switching activity power is to reduce  $V_{DD}$  (because it appears as a squared term in (Equation 2.1)), and to reduce C, amount of capacitance we have to switch. Reduced  $V_{DD}$  implies reduced threshold voltage, which in turn implies increased leakage current  $I_{leak}$ . Static power dissipation due to leakage current increases exponentially as voltages are scaled down. Since scaling down of voltages is a natural by-product of scaling down the dimensions (width and length of transistors), static power dissipation is a huge problem in nano-scaled CMOS circuits. However, it is not clear how to model or reason about static power dissipation

due to leakage current at the RT-level.

In this survey, we first survey state-of-the-art optimization methods that target low power dissipation in VLSI circuits. Design optimizations for low power at the circuit, logic, architectural and system level are considered in Section 2.1. Section 2.2 details various state-of-the-art attempts at verification of low power transformations, techniques and optimizations. [147] carries more details.

## 2.1 Low Power Transformations and Techniques

#### 2.1.1 Circuit and Design Optimizations and Considerations for Power

## 2.1.1.1 Transistor Level Optimizations

Complex gates are designed such that the late-arriving signals are placed closer to the output to minimize gate propagation delay. However, the average power dissipation is dependent on the transition probabilities of the gate inputs and the internal node capacitances (parasitic drain and source, as well as interconnect capacitance). Therefore, ordering of gate inputs will affect both power and delay. Methods to optimize the power and/or delay of logic gates by transistor re-ordering is given in [104], [125].

Transistor size of any given gate is inversely proportional to the delay of the gate, and directly proportional to the power dissipated in the gate. An increase in transistor size will also increase the delay of the fan-in gates feeding this gate because of increased load capacitance for the fan-in gates. The problem to be tackled here is that given a delay constraint, we have to size the transistor to minimize power dissipation. There are some approaches which treat this problem as a combinato-

rial problem and try to solve it using genetic algorithms, or simulated annealing. Another approach is to compute the slack at each gate of the circuit (how much the gate can be slowed down without affecting the critical delay) [125], [11], [37]. An approach using nonlinear optimization formulation, by introducing a notion of transition density is expostulated by [112]. In particular, [112] also does a good survey of other approaches which have taken power into consideration during transistor sizing.

Figure 2.4: Body Bias vs. Internal Vdd On/Off [17].

Figure 2.4 contrasts two key transistor level changes to accommodate power management. Described on the left hand side is body bias. Adaptive Body Biasing (ABB) [45] is a popularly used technique to mitigate the increasing impact of manufacturing process variations on leakage power dissipation. The efficacy of the

ABB technique can be improved by partitioning a design into a number of *body-bias islands*, each with its individual body-bias voltage.

On the right hand side of Figure 2.4 is described a multi-threshold CMOS technology (MTCMOS) [49] which allows for easy switching between ON and OFF states. Such transistors are very useful to build retention registers [10], etc.

#### 2.1.1.2 Combinational Logic Optimizations

A comprehensive treatment of combinational logic optimization for area and delay is given in [40]. In this subsection we focus on power related optimizations.

Methods to reduce circuit switching activity (and hence, power dissipation), by using controllability-don't-care-set<sup>†</sup> and observability-don't-care-set<sup>‡</sup> was presented in [61] and further improved in [12].

Delays of paths converging at any gate are typically balanced to avoid spurious transitions. Path balancing is done by adding unit-delay buffers on the faster paths, without affecting the timing. However, adding buffers can affect the reduction in switching activity. [74] discuss how to balance paths by reducing instead of completely eliminating spurious switching activity, by adding a minimum number of unit-delay buffers.

Factorization involves finding common sub-expressions and reusing them to reduce transistor count. In kernel extraction algorithms for factorization (discussed

<sup>&</sup>lt;sup>†</sup>The controllability don't-care set corresponds to collections of input combinations that never occur at the gate inputs.

<sup>&</sup>lt;sup>‡</sup>The observability don't-care set corresponds to collections of input combinations which produce the same values at the circuit outputs.

in [110]), the kernels of given expressions are generated and kernels that maximally reduce switching activity are selected.

#### 2.1.1.3 Sequential Logic Optimization

Methods to encode state transition graphs to produce two-level and multi-level implementations with minimal power are described in [110] and [130]. An algorithm to re-encode logic level sequential circuits to minimize power dissipation is presented in [52].

Encoding to reduce switching activity in datapath logic has also been a subject of attention. A method to minimize switching on buses is proposed in [123]. In this method, and extra line is added which indicates whether the value on the bus is true or complemented. For example, if the previous value on the bus is 0000 and the value to be transmitted is 1101, then we can reduce switching activity by transmitting 0010 and setting the extra line to denote the complement.

Retiming is a well-researched optimization technique to reposition flip-flops in a synchronous sequential circuit to minimize the clock period. There isn't much work done in terms of reducing power dissipation using retiming. Although [89] exploit the fact that that due to spurious transitions switching activity at the inputs of flops are substantially more than at the outputs, in order to retime for low power.

Gated Clocks is the most used power optimization technique. This involves "turning off" parts of the circuit governed by a clock which are not used on any given cycle. The cost is some additional circuitry which will decide whether to clock some flops on certain clock cycles or not.

Precomputation [4] builds on gated clocks. Idling sub-circuits are detected and "turned off". In sequential circuits, the output logic values are selectively precomputed one cycle before they are needed, and these precomputed values are used to reduce internal switching activity in the succeeding cycle.

[90] and [129] give algorithms to determine the sub-circuits to be turned off, and the logic required to perform the disabling.

### 2.1.1.4 Survey of Gate Level Optimizations

[76] presents a very good estimation of the power consumption in CMOS VLSI chips. It presents different ways of estimating power consumption in logic, memories, interconnects, clock distribution, and off chip components. This work also presents a method to estimate the power consumption of a chip based on gate count, memory size, logic, layout styles, etc. [94] presents a power optimization and synthesis system that can optimize power at the gate level and also perform area and timing optimizations. [107] presents a model that predicts not only the cycle-bycycle power consumption of a module, but also the moving average of power consumption and the power profile of the module over time. [119] gives an excellent perspective on power-aware CAD tools and methodologies. [99] presents a very detailed survey of the important areas of hardware power optimizations. Some of the broad power-aware design methodologies described here include power-aware algorithm and system design (for example - a given task may be partitioned between various hardware modules or programmable processors or both to reduce the system-level power consumption), clock gating, memory power reduction by

segmenting/partitioning, power-aware behavioral and logic synthesis, etc.

### 2.1.2 Behavioral Level (RTL) Optimizations

An important aspect of optimizing power at the RTL level is to first develop a framework for analyzing the power dissipation at an architectural level. The traditional method has been to translate the given high level architecture description to gates (netlists) and then use reasonably accurate low-level power analysis engines. This method is infeasible if we want to evaluate a large number of design choices.

Most initial work in this area is focused on power analysis and reduction in caches. This is chiefly because embedded microprocessors, historically the reason for low power design, devote nearly 40% of their power budget to caches. Besides, caches are regular structures and are more easily modeled than other circuits. [29] discuss power reduction by reducing unnecessary speculation in branch predictors. [19] discusses gated clocks in integer ALUs. More recently, [20] presents a framework for analyzing power dissipation at the architecture level and [55] discusses optimizations at the microarchitectural level.

[97] propose a multiple clocking scheme for low power RTL design. The basis of this technique is: (a) to use a multiple clocking scheme of n non-overlapping clocks, by dividing the frequency of a single clock into n cycles; (b) to partition the circuit into n disjoint modules and assign each module to a distinct clock; and (c) to operate each module only during its corresponding duty cycle. The overall frequency remains the same, and at best  $\frac{1}{n}$  of the original power is dissipated.

Sequential optimization seeks to replace a given sequential circuit with another

one optimized for some criterion – area, power, or performance, in a way such that the environment of the circuit cannot detect the replacement.

[86] computes logical redundancies in the circuit by a method of recursive learning [72] and eliminates the redundant gates. Identifying and eliminating redundant latches was first studied in [106] and was further explored in [121]. [120] explores safe replacement of sequential circuits. Sequential logic transformation integrating retiming with logic transformations at the technology-independent level is explored in [16].

### 2.1.3 Micro Architectural Techniques for Low Power

Power management for microprocessors can be done over the whole processor, or in specific areas. CPUs, for example, may have their execution suspended simply by stopping the issuance of instructions or by turning off their clock circuitry. Deeper power states however, might successively remove power from the processor's caches, translation lookaside buffers (TLBs), memory controllers, and so on. There is a corresponding latency of deeper power states, and therefore extra energy is required to save and restore the hardware contents, or restart it, or both. Most modern processors support multiple low power states that can be exploited either independently by hardware (hardware idle detection) or through hints from the Operating system. Some examples are Intel's SpeedStep [93], AMD's Cool'n'Quiet, Transmeta's LongRun technologies [44].

Utilizing the program structure or the data flow information available at the architectural and RTL levels can lead to many interesting and complicated low

power transformations [97], [20], [29], [145]; yet most power transformations in today's designs are at the gate-level [104], [4], [129], [90]. The primary reason for this is the hardness of the verification problem. If the low power transformations are at the gate level, then equivalence checking methods [85] can be used to automatically prove the correctness of the transformation. Although there are a few sequential equivalence checking algorithms [138], [59], [148], [149], they are not widespread in the hardware industry. In a typical industry scenario, an RTL or architectural low power transformation implies a full cost of dynamic validation, which can extend to many months, and require a lot of resources. Standardizing power intent specification will largely aid in reducing design and verification cost.

Another aspect of optimization for low power at the microarchitectural level is focused on power analysis and reduction in caches [111],[157]. Current implementations are limited only to *smart sizing* caches, which is done by the micro code in the core. [137] defines application specific cache partitions, called cache molecules, and resizing them to address performance targets for applications. None of these are visible or controllable from software/OS.

### 2.1.4 Dynamic Voltage and Frequency Scaling

The main premise in Dynamic Voltage and Frequency Scaling (DVFS) is that a system, a task, or a program can be slowed down with a small impact on its performance (presumably under acceptable limits), while at the same time obtaining significant savings in power consumption by voltage scaling. Power consumption has a linear dependence on frequency and a quadratic dependence on voltage (Equation

2.1). Power savings can therefore be achieved by intelligently reducing frequency while concurrently reducing the supply voltage. Reducing the frequency reduces the idle time in the system (slack in CPU execution, or instruction slack due to memory accesses in memory-bound program phases, etc). Many commercial implementations are now available for DVFS - Intel's SpeedStep, AMD's PowerNow, for example.

DVFS has been applied at both hardware and operating system/platform level. The main idea is to scale the supply voltage as low as possible for a given frequency while still maintaining correct operation. The voltage can be dropped only up to a certain critical level, beyond which timing faults occur. Some of the hardware mechanisms for DVFS [152], [43] implemented timing fault detection in hardware itself using special, "safe" flip flops that detect timing violations. While DVFS methods are effective in addressing the dynamic power consumption, they are significantly less effective in reducing the leakage power. As minimum feature sizes shrink, supply voltage scaling requires a reduction in the threshold voltage which results in an exponential increase in leakage current with each new technology generation. In [83], the authors show how the simultaneous use of adaptive body biasing (ABB) and DVFS can be used to reduce power in high-performance processors. ABB was previously used to control leakage during standby mode, and has the advantage that it reduces the leakage current exponentially, whereas dynamic voltage scaling reduces leakage current linearly. [132] and [156] look at similar other aspects of DVFS.

At the operating system level, several OSes now deploy some form of DVFS.

For example, Linux uses a very standard infrastructure called *cpufreq* to implement DVFS. cpufreq is the subsystem of the Linux kernel that allows frequency to be explicitly set on processors. cpufreq provides a modularized set of interfaces to manage the CPU frequency changes - it exposes common interface to the various low-level, CPU-specific frequency control technologies and high level CPU frequency controlling policies. cpufreq decouples the CPU frequency controlling mechanisms and policies and helps in independent development of the two. The actual policies are implemented as "governors", the most popular one being the *ondemand governor*. There have been many variations of these governors that have been proposed for different kinds of systems, that have varying requirements/constraints with respect to power and performance [96].

Gurun et al [51] and Simunic et al [118] look specifically at handheld, portable, and embedded systems and propose different techniques for implementing DVFS in such battery constrained devices. For example, in [51], the authors present AutoDVS, a dynamic voltage scaling (DVS) system for handheld computers. AutoDVS distinguishes common, coarse-grained, program behavior and couples forecasting techniques to make accurate predictions of future behavior. AutoDVS estimates periods of user interactivity, user non-interactivity (think time), and computation, per-program and system wide to ensure quality of service while reducing energy consumption.

Pouwelse et al [102] look at application-directed DVFS with the observation that it is difficult to achieve good results using only statistics from the OS level when applications show bursty (unpredictable) behavior. The authors here take

the approach that such applications must be made power-aware and specify their Average Execution Time (AET) and the deadline to the scheduler controlling the clock speed and processor voltage. They implement an Energy Priority Scheduling (EPS) algorithm supporting power aware applications - EPS orders tasks according to how tight their deadlines are and how often tasks overlap.

DVFS for Multi-core Processors is another interesting and challenging area [42]. One major design decision concerns whether to apply DVFS at the chip level or at the per-core level. Per-core DVFS is considered more expensive since it requires more than one power/clock domain per chip, and other circuitry to synchronize between the chips. Several researchers have explored the benefits of per-core versus per-chip DVFS for CMPs - one research reports that a per-core approach had 2.5 times better throughput than a per-chip approach. This is because the per-chip approach must scale down the entire chips (V, f) when even a single core is nearing overheating. With per-core control, only the core with a hot spot must scale (V, f) downward; other cores can maintain high speed unless they themselves encounter thermal problems. Managing power when running parallel/multi-threaded programs especially with the onset of heterogeneous many core architectures is yet another active area of research. [7] considers independent DVFS for each core, while a mixture of chip-wide DVFS and core allocation is considered in [75].

### 2.1.5 Operating System Power Management

The most widely implemented architecture for power management is the Advanced Configuration and Power Interface (ACPI) [62]. It has evolved together

with Intel (R) architecture, the hardware platforms based on the most widely available commodity CPUs and related components. ACPI defines the following power states: seven S-states (S0-S6) at the whole-system; and four D-states (D0-D3) at the per-device level. The zero-numbered state (S0 for the system, or D0 for each device) indicates the running (or active) state, while the higher-numbered ones are non-running (inactive) states with successively lower power and correspondingly decreasing levels of availability (run-readiness), and increasing latency for entry and exit. ACPI also defines performance states, called P-states (P0-P15, allowing a maximum of 16 per device), which affect the component's operational performance while running. Both power states and performance states affect power consumption.

ACPI is a specification and therefore different systems can implement different aspects of the specification in varying degrees of granularity.

Almost all processors in the marketplace today support the concept of multiple processor idle states with varying amounts of power consumed in those idle states. Each such state will have an entry-exit latency associated with it. [133] introduced the now highly popular *cpu-idle* framework, an effort toward a generic processor idle management framework in Linux kernel. The framework introduced *idle drivers*, which implement processor specific mechanisms to enter/exit sleep states, and *idle governors*, which decide which sleep state a processor should enter based on different criteria (current CPU activity, next expected interrupt time, etc.). The goal of these frameworks was to have a clean interface for any processor hardware to make use of different processor idle levels and also provide abstraction between idle-drivers and idle-governors allowing independent development of

drivers and governors.

Polling within the operating system drivers or applications) is one of the biggest source of wakeups, but the use of high-frequency clock-tick interrupts as the basis for timer events, time-keeping, and thread-scheduling became noticeably problematic from a power consumption point of view. The tickless kernel project [127] in Linux introduced the notion of dynamic ticks - by reprogramming the per-CPU periodic timer interrupt to eliminate clock ticks during idle, the average amount of time that a CPU stays in its idle state after each idle state entry can be improved by a factor of 10 or more.

### **2.1.6** Memory Power Management

Memory power management is another area of active research, both from hardware and software points of view. Memory technology itself has been evolving with the recent emergence of triple-channel DIMMs/DDR3 SDRAMs, which have enabled different levels of power management (increasing/decreasing clock frequency, varying degrees of shallow/deep self refresh, etc. One technology which is finding its way into some systems is called "partial array self refresh" or PASR [98], [88]. On a PASR-enabled system, memory is divided into banks, each of which can be powered down independently. If any of those banks of memory is not needed, that memory (and its self-refresh mechanism) can be turned off; the result is a reduction in power use, but also the loss of any data stored in the affected banks. The amount of power actually saved is a bit unclear; estimates fall in the range of 5-15% of the total power used by the memory subsystem. Correspondingly, there is

work going on to enable support for PASR and related memory power management technologies from a operating system point of view.

Main memory, because of its relatively low power requirement (say, 2 watts per DIMM), seems at first glance to be of even less concern than disks. Its average size on contemporary hardware platforms, however, may be poised to grow more rapidly. With hardware system manufacturers' focus primarily on performance levels (to keep up with the corresponding performance demands of multicore CPUs), maintaining full CPU-to-memory bandwidth is critical. The consequence has been an evolution from single to dual-channel and now triple-channel DIMMs along with the corresponding DDR, DDR2, and DDR3 SDRAM technologies. Although reductions in the process feature size (DDR3 is now on 50-nanometer technology) have enabled clock frequency to go up and power per DIMM to go down somewhat, the desire for even greater performance via an increase in DIMMs per memory channel is still increasing the total power consumed by the memory system.

### 2.1.7 Compiler Techniques for Low Power

While hardware and operating system work to provide power management, applications could do their bit to aiding the runtime system by providing hints about their behavior allowing the runtime system to identify application behavior and idle times. Other mechanisms include power aware code transformations and optimizations which can provide reduction in power consumption. Compiler techniques for low power have been explored in different domains. [155] discusses some memory and compiler techniques for low power. Memory compaction to allow contiguous