Copyright

by

Chang Joo Lee

2010

# The Dissertation Committee for Chang Joo Lee certifies that this is the approved version of the following dissertation:

# **DRAM-Aware Prefetching and Cache Management**

| Committee:               |  |  |

|--------------------------|--|--|

|                          |  |  |

| Yale N. Patt, Supervisor |  |  |

| N. A.T. I                |  |  |

| Nur A. Touba             |  |  |

| Derek Chiou              |  |  |

|                          |  |  |

| Hossein Namazi           |  |  |

| Onur Mutlu               |  |  |

## **DRAM-Aware Prefetching and Cache Management**

by

Chang Joo Lee, B.S.E.; M.S.E.

#### **DISSERTATION**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN

December 2010

# Acknowledgments

Many people contributed both directly and indirectly to this dissertation. First of all, I would like to thank the current and previous members of the HPS research group. The HPS group was everything to me during my long graduate student life.

I thank my advisor, Yale N. Patt for giving me the opportunity to work with many people who are great human beings as well as smart and talented, for helping me build a strong foundation in computer architecture, for motivating me to perform serious research, and, most of all, for being patient with me in making good progress on serious research topics.

Many thanks to Onur Mutlu for the mentorship he provided and the professionalism he demonstrated to me. He taught me how to write and publish ideas. He always encouraged me to continue working hard, and his technical feedback and criticism on my work made this dissertation stronger. I also thank him for always being a friend and bearing with my complaints and unreasonable rants. My graduate student life would have been miserable without both his technical and non-technical support.

I thank Veynu Narasiman for working with me on all the topics presented in this dissertation, for correcting both my spoken and written English, and for being a good friend and listening to me whenever I was discouraged or depressed. I cannot forget the valuable discussions with him on both research and life.

I had a wonderful time working with Eiman Ebrahimi on the cache topics proposed in this dissertation. He cared about me on both work and private issues, helped me write and speak English better, and put up with my overreactions, harsh jokes, and complaints. I could not have had any fun in the past three years without him.

I thank José A. Joao for always being a friend and listening to me on both technical and private issues. I enjoyed the time with him when we rebuilt and enhanced our simulation infrastructure environment together.

I also had a great time with Aater M. Suleman, Rustam Miftakhutdinov, and Khubaib during my graduate studies. They provided valuable technical feedback and criticism, and tried to help me all the time. Their feedback on my research also made this dissertation stronger and clearer. Especially, I thank Rustam for always being joyful and enjoying my jokes, and Khubaib for proofreading many chapters of this dissertation.

I thank Hyesoon Kim for providing mentorship and encouraging me to perform meaningful work. I thank Moinuddin K. Qureshi, Francis Tseng, Daniel N. Lynch, Santhosh Srinath, David Thompson, and other previous HPS members for their mentorship and friendship. Many thanks to Leticia Lira for her long-standing administrative support in the HPS group. I also thank recently joined members, Milad Hashemi and Faruk Guvenilir for proofreading some chapters in this dissertation.

Besides the HPS members, I would like to express my gratitude to other people and organizations.

I thank Derek Chiou, Nur Touba, and Hossein Namazi for serving on my dissertation committee and for giving me valuable comments on this dissertation. I also thank Thomas Puzak, Philip Emma, Vijayalakshmi Srinivasan, and James Holt for providing me with a chance to have a great experience as an intern at IBM and Freescale. I gratefully acknowledge the government of Korea and IBM for providing me with fellowships during my graduate studies.

I appreciate the support and friendship of my friends, Dam Sunwoo and Joonsoo Kim. We all had fun making our serious project successful in 382N. I will never forget the great feeling we had at that time.

Special thanks to the "Lunch Bank" lady who delivered a lunch box to me on campus everyday during several semesters, which helped me manage time more efficiently.

Finally, I would like to thank my grandmother, Jung Hee Yong who passed away during my studies, my parents, Jong Rak Lee and Jong Kyo Kwon, my brother, Seung Hoon Lee, and my wife, Eunyoung Park for giving me their endless love and unconditional support. I dedicate this dissertation to them.

Chang Joo Lee

December 2010, Austin, TX

**DRAM-Aware Prefetching and Cache Management**

Chang Joo Lee, Ph.D.

The University of Texas at Austin, 2010

Supervisor: Yale N. Patt

Main memory system performance is crucial for high performance microproces-

sors. Even though the peak bandwidth of main memory systems has increased

through improvements in the microarchitecture of Dynamic Random Access Mem-

ory (DRAM) chips, conventional on-chip memory systems of microprocessors do

not fully take advantage of it. This results in underutilization of the DRAM system,

in other words, many idle cycles on the DRAM data bus. The main reason for this

is that conventional on-chip memory system designs do not fully take into account

important DRAM characteristics. Therefore, the high bandwidth of DRAM-based

main memory systems cannot be realized and exploited by the processor.

This dissertation identifies three major performance-related characteristics

that can significantly affect DRAM performance and makes a case for DRAM

characteristic-aware on-chip memory system design. We show that on-chip mem-

ory resource management policies (such as prefetching, buffer, and cache policies)

that are aware of these DRAM characteristics can significantly enhance entire sys-

tem performance. The key idea of the proposed mechanisms is to send out to the

DRAM system useful memory requests that can be serviced with low latency or in

parallel with other requests rather than requests that are serviced with high latency

viii

or serially. Our evaluations demonstrate that each of the proposed DRAM-aware mechanisms significantly improves performance by increasing DRAM utilization for useful data. We also show that when employed together, the performance benefit of each mechanism is achieved additively: they work synergistically and significantly improve the overall system performance of both single-core and Chip MultiProcessor (CMP) systems.

# **Table of Contents**

| Acknov  | wledgments                                                 | V           |

|---------|------------------------------------------------------------|-------------|

| Abstra  | ct                                                         | vii         |

| List of | Tables                                                     | <b>xv</b> i |

| List of | Figures                                                    | xviii       |

| Chapte  | er 1. Introduction                                         | 1           |

| 1.1     | Problem                                                    | . 1         |

| 1.2     | Thesis Statement                                           | . 5         |

| 1.3     | Contributions                                              | . 5         |

| 1.4     | Dissertation Organization                                  | . 7         |

| Chapte  | er 2. Background: DRAM Performance-Related Characteristics | 9           |

| 2.1     | Row Buffer Locality                                        | . 9         |

| 2.2     | Bank-Level Parallelism                                     | . 12        |

| 2.3     | Write-Caused Interference                                  | . 12        |

|         | 2.3.1 Read-to-write and write-to-read latencies            | . 14        |

|         | 2.3.2 Write-to-precharge latency                           | . 16        |

| Chapte  | er 3. Overview of the Solutions                            | 19          |

| Chapte  | er 4. Related Work                                         | 22          |

| 4.1     | Research in DRAM System Management                         | . 22        |

|         | 4.1.1 DRAM Access Scheduling                               | . 22        |

|         | 4.1.2 DRAM Write Buffer Management                         | . 24        |

| 4.2     | Research in Improving Memory-Level Parallelism             | . 25        |

| 4.3     | Research in Prefetching and Prefetch Handling              | . 26        |

|         | 4.3.1 Prefetching Algorithms                               | . 26        |

|         | 4.3.2 Useless Prefetch Filtering                           | . 27        |

|         | 4.3.3 Adaptive Prefetching                                 | . 28        |

| 4.4     | Research in Cache Management                               | . 29        |

|        | 4.4.1  | Cache Management for Locality                                                          | 29 |

|--------|--------|----------------------------------------------------------------------------------------|----|

|        | 4.4.2  | Cost-Aware Cache Management                                                            | 30 |

|        | 4.4.3  | Writeback Management                                                                   | 30 |

| Chapte | r 5. P | refetch Management for Reducing DRAM Latency                                           | 32 |

| 5.1    | Motiva | ation                                                                                  | 32 |

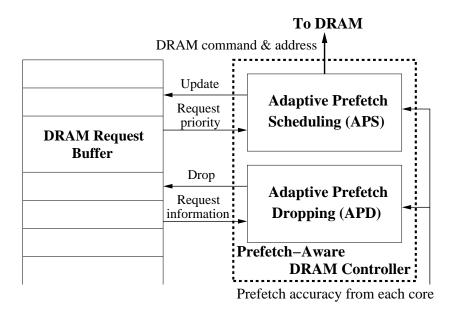

| 5.2    | Mecha  | anism: Prefetch-Aware DRAM Controller (PADC)                                           | 37 |

|        | 5.2.1  | Prefetch Accuracy Estimation                                                           | 37 |

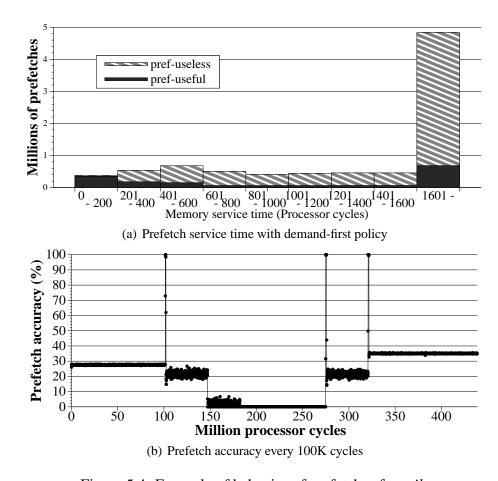

|        | 5.2.2  | Adaptive Prefetch Scheduling                                                           | 39 |

|        | 5.2.3  | Adaptive Prefetch Dropping                                                             | 41 |

| 5.3    | Experi | imental Methodology                                                                    | 44 |

|        | 5.3.1  | Metrics                                                                                | 44 |

|        | 5.3.2  | System Model                                                                           | 45 |

|        | 5.3.3  | Workloads                                                                              | 45 |

| 5.4    | Imple  | mentation and Hardware Cost of PADC                                                    | 47 |

| 5.5    | Experi | imental Evaluation and Analysis on PADC                                                | 49 |

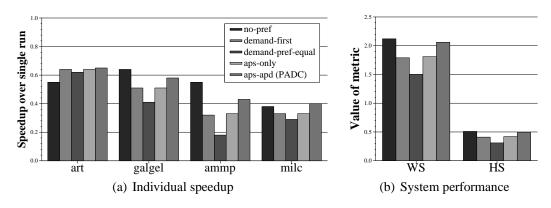

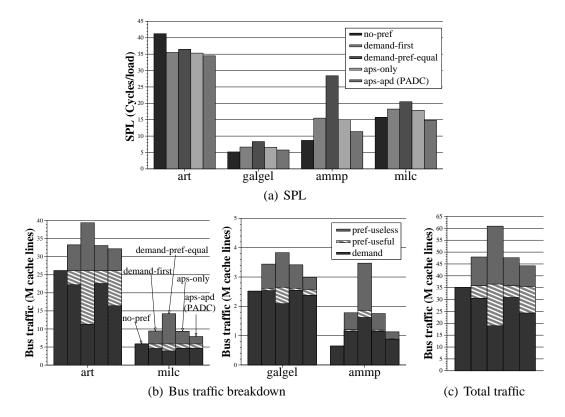

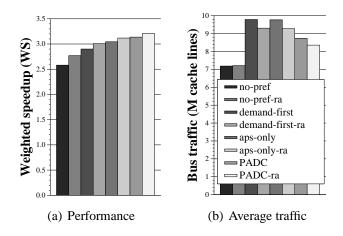

|        | 5.5.1  | Single-Core Results                                                                    | 50 |

|        |        | 5.5.1.1 Adaptive Behavior of PADC                                                      | 53 |

|        |        | 5.5.1.2 Effect of PADC on Row Buffer Hit Rate                                          | 54 |

|        | 5.5.2  | 2-Core Results                                                                         | 55 |

|        | 5.5.3  | 4-Core Results                                                                         | 56 |

|        |        | 5.5.3.1 Case Study I: All Prefetch-Friendly Applications                               | 56 |

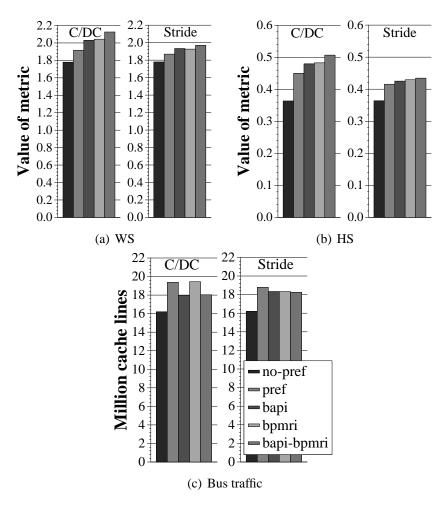

|        |        | 5.5.3.2 Case Study II: All Prefetch-Unfriendly Applications                            | 58 |

|        |        | 5.5.3.3 Case Study III: Mix of Prefetch-Friendly and Prefetch-Unfriendly Applications  | 60 |

|        |        | 5.5.3.4 Effect of Prioritizing Urgent Requests                                         | 62 |

|        |        | 5.5.3.5 Effect on Identical-Application Workloads                                      | 63 |

|        |        | 5.5.3.6 Overall Performance                                                            | 65 |

|        | 5.5.4  | 8-Core Results                                                                         | 65 |

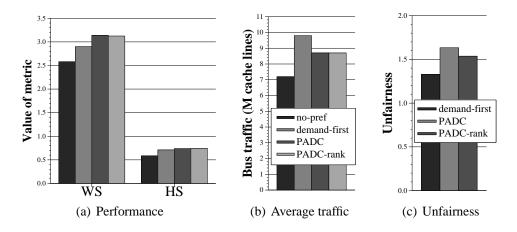

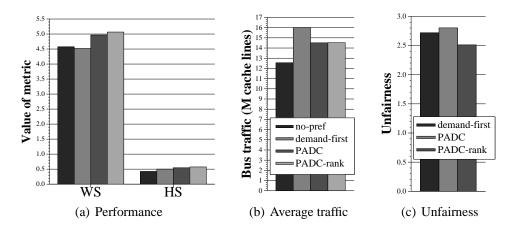

|        | 5.5.5  | Optimizing PADC for Fairness Improvement in CMP Systems: Incorporating Request Ranking | 66 |

|        | 5.5.6  | Effect on Multiple DRAM Controllers                                                    | 70 |

|        | 5.5.7  | Effect with Different DRAM Row Buffer Sizes                                            | 72 |

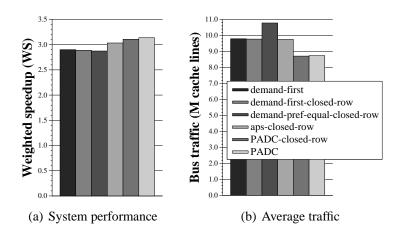

|        | 5.5.8  | Effect with a Closed-Row DRAM Row Buffer Policy                                        | 74 |

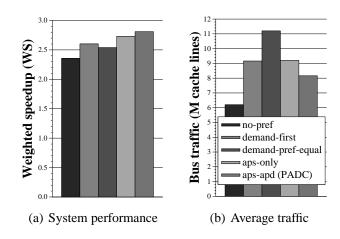

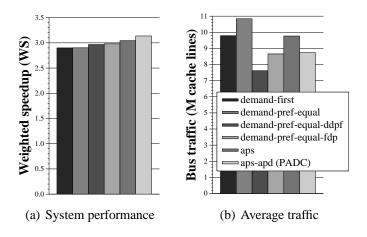

|        | 5.5.9  | Effect with a Shared Last-Level Cache                                                  | 76 |

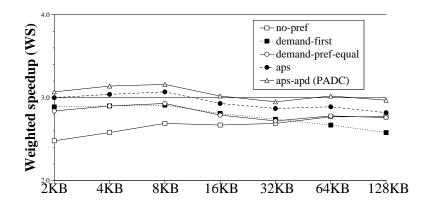

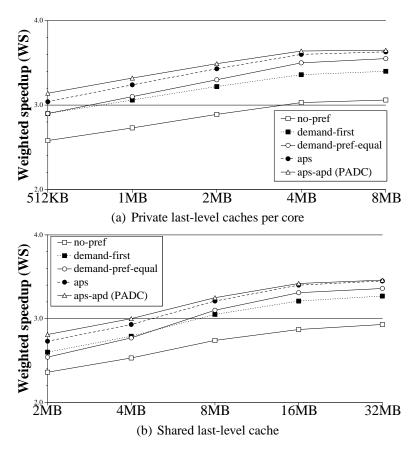

|        | 5.5.10 | Effect with Different Last-Level Cache Sizes                                           | 78 |

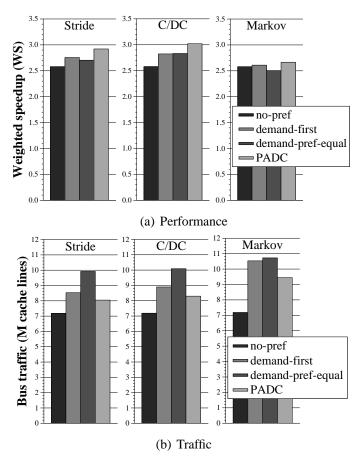

|        | 5 5 11 | Effect on Other Prefetching Mechanisms                                                 | 80 |

|                | 5.5.12 | 2 Effect on a Runahead Execution Processor                                          | . 82         |

|----------------|--------|-------------------------------------------------------------------------------------|--------------|

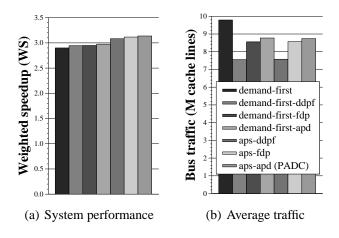

|                | 5.5.13 | B Comparison with Dynamic Data Prefetch Filtering and Feedback Directed Prefetching |              |

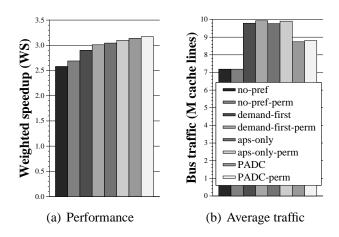

|                | 5.5.14 | Interaction with Permutation-Based Page Interleaving                                | . 87         |

| 5.6            | Summ   | nary                                                                                | . 89         |

| Chapte         | r 6. F | Prefetch Management for Increasing DRAM Bank-Level Parallelism (BLP)                | r-<br>90     |

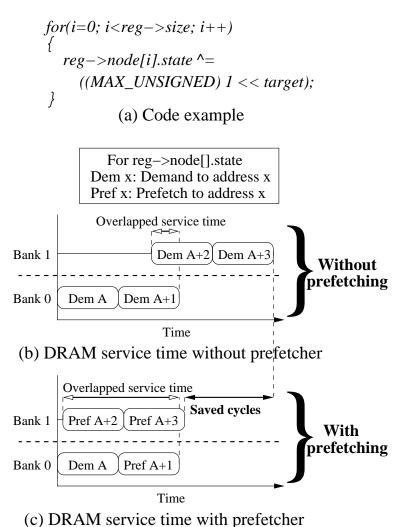

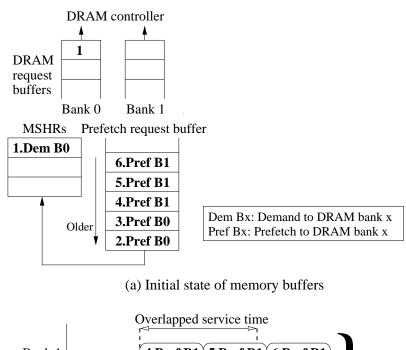

| 6.1            | Prefet | ch Issue Policy to Increase BLP                                                     | . 90         |

|                | 6.1.1  | Prefetching: Increasing Potential for DRAM BLP                                      | . 90         |

|                | 6.1.2  | What Can Limit Prefetching's Benefits?                                              | . 92         |

|                | 6.1.3  | Mechanism: BLP-Aware Prefetch Issue                                                 | . 95         |

|                |        | 6.1.3.1 Hardware Support                                                            | . 95         |

|                |        | 6.1.3.2 BLP-Aware Prefetch Issue Policy                                             | . 96         |

|                |        | 6.1.3.3 Adaptive Thresholding Based on Prefetch Accuracy                            | 97           |

| 6.2            | Preser | rving DRAM Bank-Level Parallelism in CMP systems                                    | . 98         |

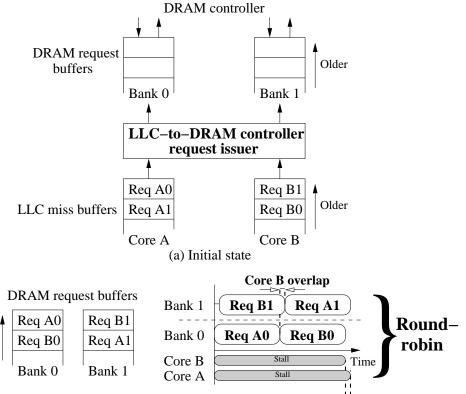

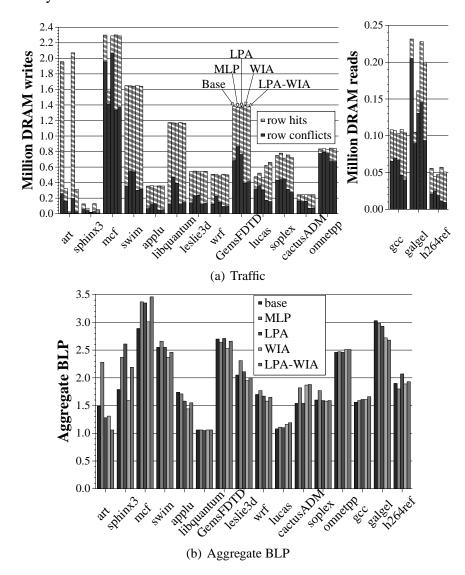

|                | 6.2.1  | What Can Destroy BLP of Applications Running Together?                              | . 99         |

|                | 6.2.2  | Mechanism: BLP-Preserving Multi-core Issue                                          | . 101        |

| 6.3            | Exper  | imental Methodology                                                                 | . 103        |

|                | 6.3.1  | Metrics                                                                             | . 103        |

|                | 6.3.2  | System Model                                                                        | . 104        |

|                | 6.3.3  | Workloads                                                                           | . 104        |

| 6.4            | Imple  | mentation and Hardware Cost of BLP-Aware Issue Policies                             | . 105        |

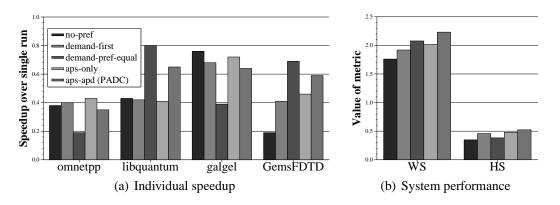

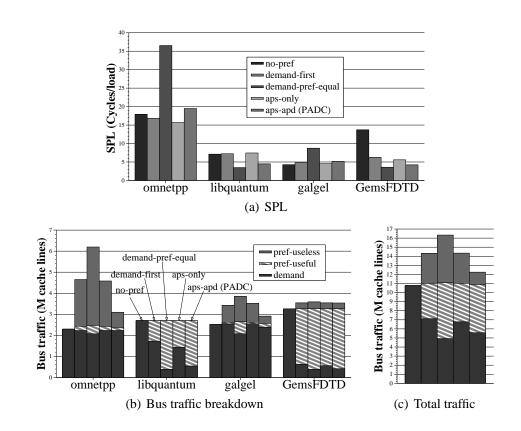

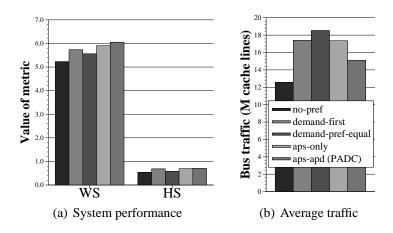

| 6.5            | Exper  | rimental Evaluation and Analysis on BLP-Aware Issue Policies                        | 107          |

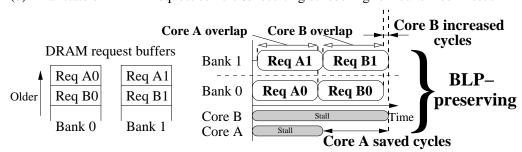

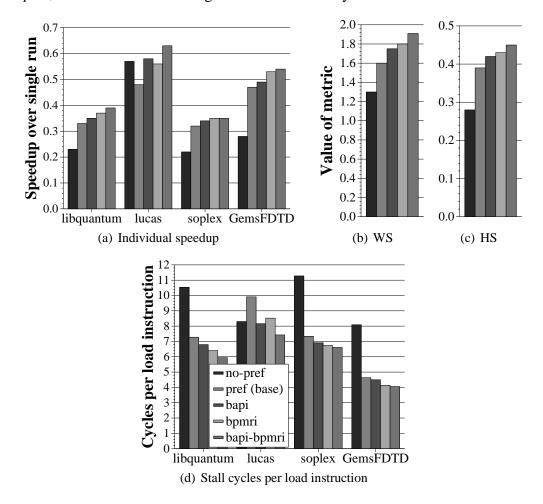

|                | 6.5.1  | Single-Core Results                                                                 | . 107        |

|                |        | 6.5.1.1 Analysis                                                                    | . 108        |

|                |        | 6.5.1.2 Adaptivity to Usefulness of Prefetches                                      | . 110        |

|                |        | 6.5.1.3 Adaptivity to Phase Behavior                                                | . 111        |

|                |        | 6.5.1.4 Sensitivity to MSHR Size                                                    | . 112        |

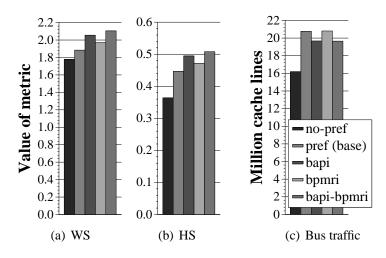

|                | 6.5.2  | 4-Core Results                                                                      | . 113        |

|                |        | 6.5.2.1 Case Study                                                                  | . 113        |

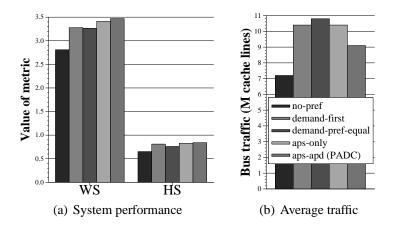

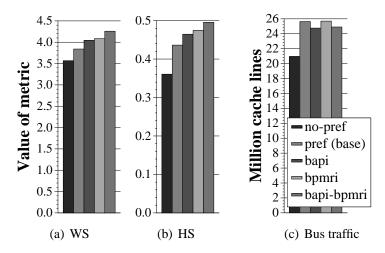

|                |        | 6.5.2.2 Overall Performance                                                         | . 116        |

|                | 6.5.3  | 8-Core Results                                                                      | . 116        |

|                | 6.5.4  | Effect on Other Prefetching Mechanisms                                              | . 117        |

|                | 6.5.5  | Comparison with Parallelism-Aware Batch DRAM Scheduling                             | g 117        |

| 6.6            |        | ination of Prefetch-Aware DRAM Controller and BLP-Aware                             | 100          |

| . <del>.</del> | Issue  | Policies                                                                            | . 120<br>121 |

| h /            | Numm   | 14171/                                                                              | 1 / 1        |

| Chapte | r 7. I | Last-Level Cache Management for Improving DRAM Characteristics        | 122 |

|--------|--------|-----------------------------------------------------------------------|-----|

| 7.1    | Cache  | Replacement for Reducing Latency and Increasing BLP                   | 122 |

|        | 7.1.1  | Why Should We Consider DRAM Characteristics in Cache Management?      |     |

|        | 7.1.2  | Mechanism: Latency and Parallelism-Aware (LPA) Replacement            | 125 |

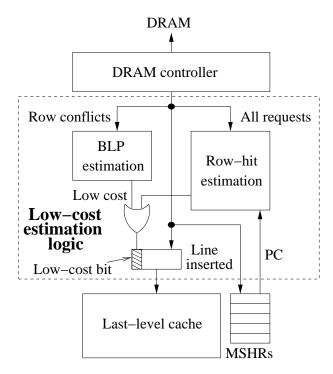

|        |        | 7.1.2.1 Low-Cost Estimation Using BLP Information                     | 127 |

|        |        | 7.1.2.2 Low-Cost Estimation Using Row hit/conflict information        | 129 |

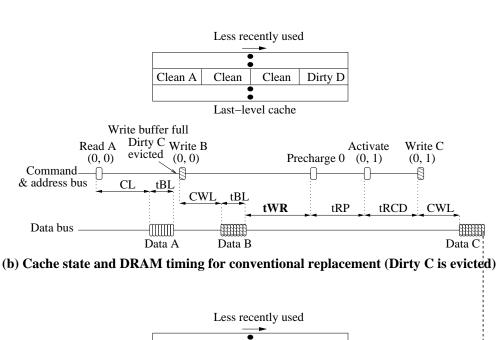

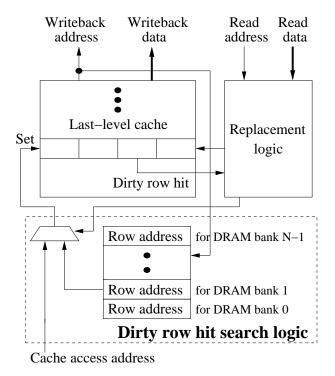

| 7.2    | Cache  | Replacement for Reducing Write-Caused Interference                    | 131 |

|        | 7.2.1  | Why Should We Consider Write-Caused Interference in Cache Management? | 131 |

|        | 7.2.2  | Mechanism: Write-Caused Interference-Aware (WIA) Replacement          | 133 |

| 7.3    |        | ining Latency and Parallelism-Aware and Write-Caused Interfere        |     |

| 7.4    | Multi- | -Core System Considerations                                           | 135 |

|        | 7.4.1  | LPA Replacement in Multi-Core                                         | 136 |

|        | 7.4.2  | WIA Replacement in Multi-Core                                         | 136 |

| 7.5    | Comp   | arison to Memory-Level Parallelism-Aware Replacement                  | 137 |

| 7.6    | Exper  | imental Methodology                                                   | 138 |

|        | 7.6.1  | Metrics                                                               | 138 |

|        | 7.6.2  | System Model                                                          | 138 |

|        | 7.6.3  | Workloads                                                             | 139 |

| 7.7    |        | mentation and Hardware Cost of DRAM-Aware Replacement es              | 140 |

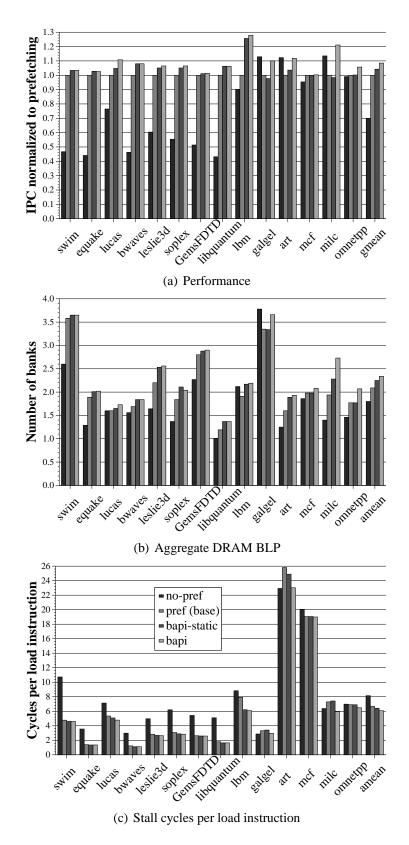

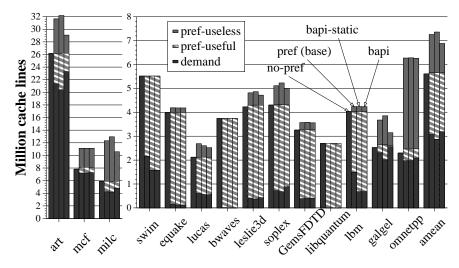

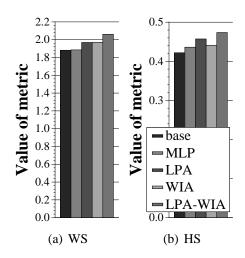

| 7.8    |        | imental Evaluation and Analysis on DRAM-Aware Replace-Policies        | 141 |

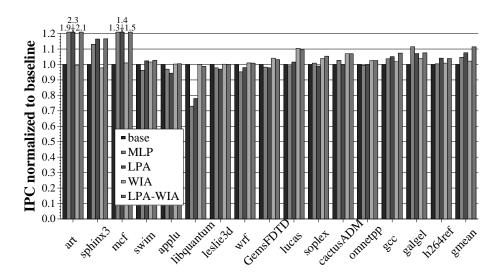

|        | 7.8.1  | Single-Core Results                                                   | 142 |

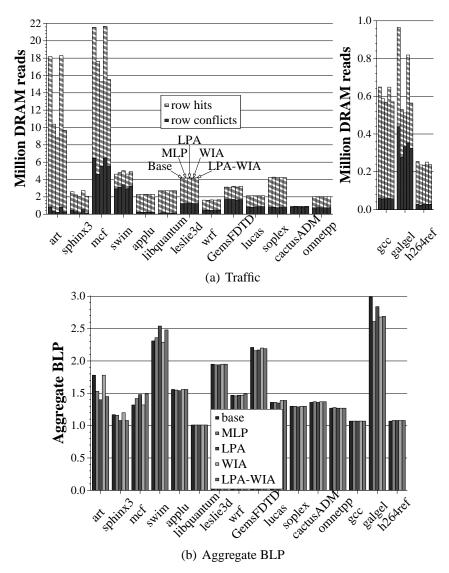

|        |        | 7.8.1.1 Why Does LPA Policy Perform Well?                             | 144 |

|        |        | 7.8.1.2 Why Is Write-Caused Interference Awareness Desirable?         | 145 |

|        |        | 7.8.1.3 Combining LPA and WIA                                         | 147 |

|        |        | 7.8.1.4 Effect on System with Prefetching                             |     |

|        | 7.8.2  | 4-Core Results                                                        |     |

| 7.9    | Summ   | nary                                                                  | 150 |

| Chapte | r 8. I | Last-Level Cache Management for Reducing Write-Caused Interference 153        | 1 |

|--------|--------|-------------------------------------------------------------------------------|---|

| 8.1    | Write- | -Caused Interference in the DRAM System                                       | 1 |

|        | 8.1.1  | Performance Impact of Write-Caused Interference in Today's DRAM System        | 3 |

|        | 8.1.2  | Performance Impact of Write-Caused Interference in the Future 155             | 5 |

| 8.2    | Motiv  | ation                                                                         | 7 |

|        | 8.2.1  | Reducing Read-to-Write and Write-to-Read Penalties 15                         | 7 |

|        | 8.2.2  | Last-Level Cache Writeback: A Way to Further Reduce Write-Caused Interference | 0 |

| 8.3    | Mech   | anism: DRAM-Aware Writeback                                                   | 3 |

|        | 8.3.1  | Does Last-Level Cache Have Sufficient Bandwidth for DRAM-Aware Writeback?     | 5 |

|        | 8.3.2  | Dynamic Optimization for Frequent Rewrites 166                                | 6 |

| 8.4    | Comp   | arison to Eager Writeback                                                     | 8 |

| 8.5    | Exper  | imental Methodology                                                           | 9 |

|        | 8.5.1  | Metrics                                                                       | 9 |

|        | 8.5.2  | System Model                                                                  | 9 |

|        | 8.5.3  | Workloads                                                                     | 9 |

| 8.6    | -      | mentation and Hardware Cost of DRAM-Aware Writeback 170                       |   |

| 8.7    | Exper  | imental Evaluation                                                            | 1 |

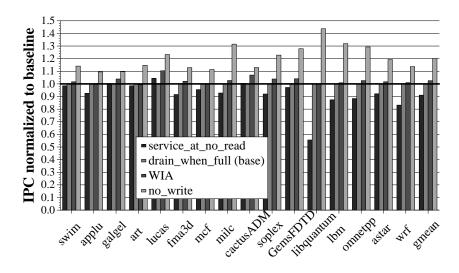

|        | 8.7.1  | Performance of Write Buffer Management Policies 17                            |   |

|        | 8.7.2  | Single-Core Results                                                           | 4 |

|        |        | 8.7.2.1 Why Does Eager Writeback Not Perform Well? 177                        | 7 |

|        |        | 8.7.2.2 Why Does DRAM-Aware Writeback Perform Better? 179                     | 9 |

|        |        | 8.7.2.3 When is Dynamic DRAM-Aware Writeback Required?18                      |   |

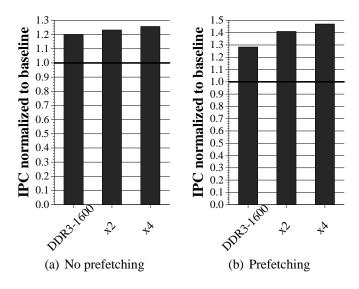

|        | 8.7.3  | Multi-Core Results                                                            |   |

|        | 8.7.4  | Effect on Systems with Prefetching                                            | 3 |

| 8.8    | Summ   | nary                                                                          | 5 |

| Chapte | r 9. ( | Combining All DRAM-Aware Mechanisms 180                                       | 6 |

| 9.1    | DRAN   | M-Aware Mechanisms Are Complementary                                          | 6 |

| 9.2    | Metho  | odology                                                                       | 7 |

|        | 9.2.1  | System Model                                                                  | 7 |

|        | 9.2.2  | Workloads                                                                     | 7 |

| 9.3    | Exper  | imental Evaluation                                                            | 8 |

| Chapter 10.  | Conclusion and Futu   | re Resea | arch Di | rections    | 192     |

|--------------|-----------------------|----------|---------|-------------|---------|

| 10.1 Conc    | lusion                |          |         | . <b></b> . | <br>192 |

| 10.2 Futur   | e Research Directions |          |         |             | <br>194 |

| Bibliography |                       |          |         |             | 196     |

| Vita         |                       |          |         |             | 207     |

# **List of Tables**

| 5.1 | Baseline configuration of each core for PADC                                                                                                                                                                                                                |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.2 | Baseline configuration of shared CMP resources for PADC 46                                                                                                                                                                                                  |

| 5.3 | Characteristics of 18 SPEC benchmarks for PADC: IPC, MPKI (last-level cache misses per 1K instructions), RBH (Row Buffer Hit rate), ACC (prefetch accuracy), COV (prefetch coverage), class 47                                                              |

| 5.4 | Hardware storage cost of PADC: $N_{cache}$ : number of cache lines per core $N_{core}$ : number of cores, $N_{req}$ : number of DRAM request buffer entries)                                                                                                |

| 5.5 | Dynamic <i>drop_threshold</i> values for Adaptive Prefetch Dropping based on prefetch accuracy                                                                                                                                                              |

| 5.6 | Row buffer hit rate of PADC for useful requests                                                                                                                                                                                                             |

| 5.7 | Effect of prioritizing urgent requests in PADC                                                                                                                                                                                                              |

| 5.8 | Effect of PADC on four identical prefetch-friendly applications 64                                                                                                                                                                                          |

| 5.9 | Effect of PADC on four identical prefetch-unfriendly applications . 64                                                                                                                                                                                      |

| 6.1 | Baseline configuration of each core for BLP-aware issue policies 104                                                                                                                                                                                        |

| 6.2 | Baseline shared resource configuration for BLP-aware issue policies 104                                                                                                                                                                                     |

| 6.3 | DRAM timing specifications for BLP-aware issue policies 105                                                                                                                                                                                                 |

| 6.4 | Characteristics of 14 memory-intensive SPEC benchmarks for BLP-aware issue: IPC, MPKI (last-level cache misses per 1K instructions), BLP, ACC (prefetch accuracy), COV (prefetch coverage) 106                                                              |

| 6.5 | Dynamic prefetch_send_threshold values for BAPI 106                                                                                                                                                                                                         |

| 6.6 | Hardware storage cost of BAPI and BPMRI ( $N_{line}$ , $N_{core}$ , $N_{MSHR}$ , $N_{buffer}$ , $N_{channel}$ , $N_{bank}$ : number of last-level cache lines, cores, MSHR entries, prefetch request buffer entries, DRAM channels, DRAM banks per channel) |

| 6.7 | Average IPC performance of BAPI with various MSHR sizes 112                                                                                                                                                                                                 |

| 7.1 | Baseline configuration for DRAM-aware replacement policies 139                                                                                                                                                                                              |

| 7.2 | DDR3-1600 DRAM timing specifications for DRAM-aware replacement policies                                                                                                                                                                                    |

| 7.3 | Characteristics of 16 SPEC benchmarks for DRAM-aware replacement: IPC, MPKI (last-level cache misses per 1K instructions), WPKI (last-level cache Writebacks Per 1K Instructions), row hit rate (RHR), BLP                                                  |

| 7.4 | Hardware storage cost for DRAM-aware replacement policies ( $N_{core}$ , $N_{line}$ , $N_{bank}$ , $N_{buffer}$ : number of cores, last-level cache lines, DRAM banks, cache fill buffer entries)          |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8.1 | Last-level cache bank idle cycles (%) on single core system 166                                                                                                                                            |

| 8.2 | Average last-level cache bank idle cycles (%) on single, 4, and 8-core systems                                                                                                                             |

| 8.3 | Baseline configuration for DRAM-aware writeback                                                                                                                                                            |

| 8.4 | Characteristics for 18 SPEC benchmarks for DRAM-aware write-back: IPC, MPKI (last-level cache misses per 1K instructions), WPKI (last-level cache Writebacks Per 1K Instructions), DRAM row hit rate (RHR) |

| 8.5 | Number of write buffer drains and number of writes per drain for various policies                                                                                                                          |

| 8.6 | Number of DRAM-aware writebacks generated, reread cache lines and rewritten cache lines, and rewrite rate                                                                                                  |

| 9.1 | Baseline configuration for all combined DRAM-aware mechanisms 188                                                                                                                                          |

# **List of Figures**

| 1.1  | system with no prefetching and a stream prefetcher (with the peak DRAM bandwidth of 12.8, 25.6, 25.6GB/s for single, 4, and 8-core systems respectively) | 4  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | Row conflict and row hit in modern DRAM system                                                                                                           | 11 |

| 2.2  | DRAM bank-level parallelism                                                                                                                              | 13 |

| 2.3  | Read-to-write and write-to-read latencies                                                                                                                | 15 |

| 2.4  | Write-to-precharge (write recovery time) latency                                                                                                         | 17 |

| 3.1  | Overview of proposed DRAM-aware mechanisms                                                                                                               | 20 |

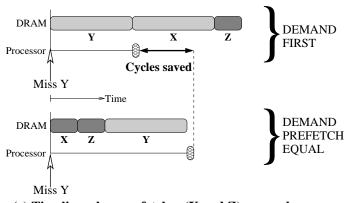

| 5.1  | Example illustrating the performance impact of demand-first and demand-prefetch-equal policies                                                           | 34 |

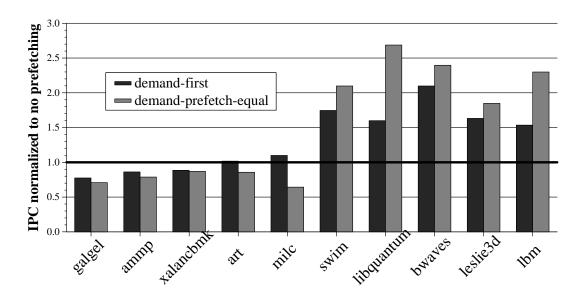

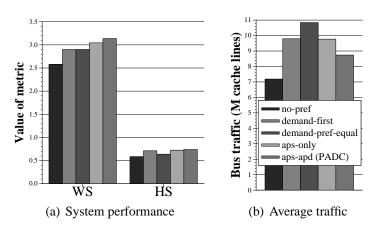

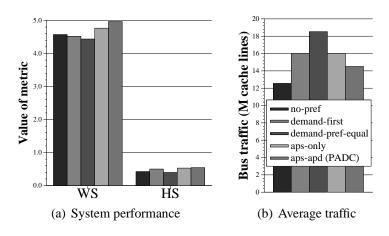

| 5.2  | Performance of two rigid prefetch scheduling policies                                                                                                    | 36 |

| 5.3  | Prefetch-Aware DRAM Controller                                                                                                                           | 38 |

| 5.4  | Example of behavior of prefetches for <i>milc</i>                                                                                                        | 43 |

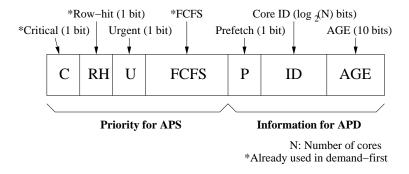

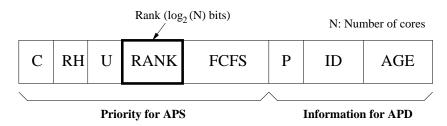

| 5.5  | DRAM request field for PADC                                                                                                                              | 48 |

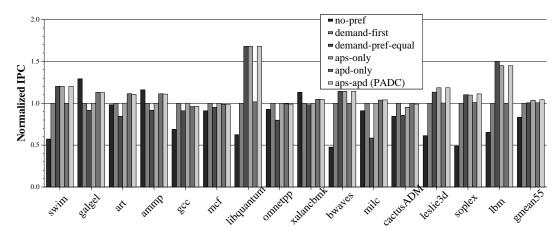

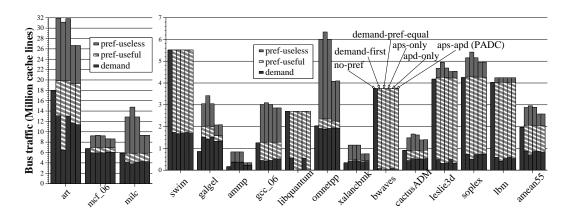

| 5.6  | Performance of PADC on single-core system: Normalized IPC for 15 benchmarks and average for all 55 (gmean55)                                             | 50 |

| 5.7  | Stall time per load (SPL) of PADC on single-core system                                                                                                  | 52 |

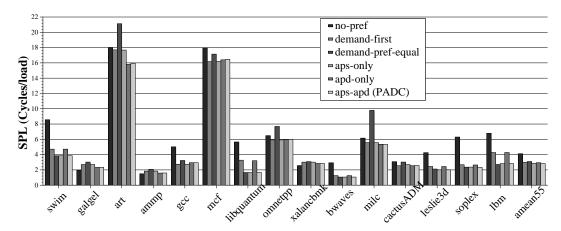

| 5.8  | Bus traffic of PADC on single-core system                                                                                                                | 53 |

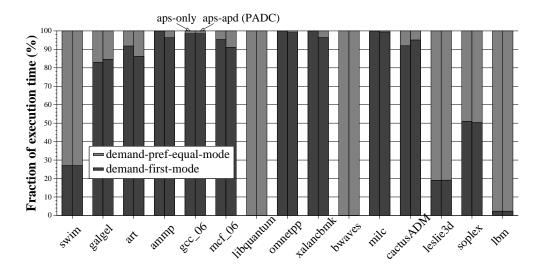

| 5.9  | Fraction of execution time in different PADC scheduling modes on single-core system                                                                      | 54 |

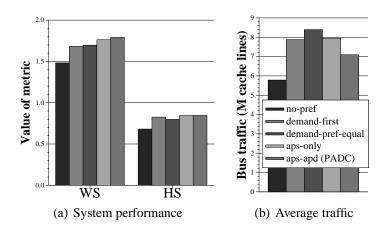

| 5.10 | Performance of PADC on 2-core system                                                                                                                     | 56 |

| 5.11 | Performance of PADC for prefetch-friendly 4-core workload                                                                                                | 57 |

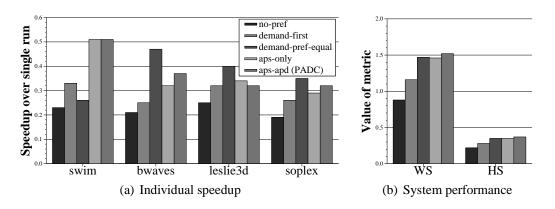

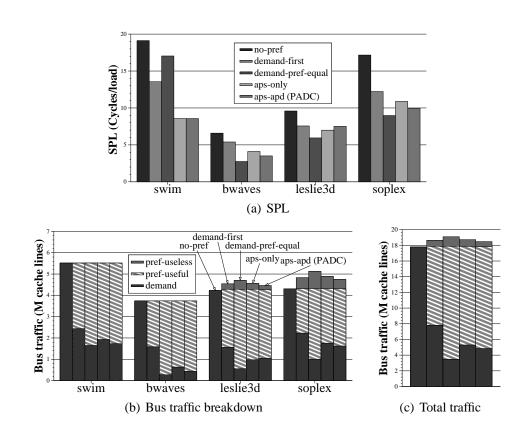

| 5.12 | SPL and bus traffic of PADC for prefetch-friendly 4-core workload .                                                                                      | 57 |

| 5.13 | Performance of PADC for prefetch-unfriendly 4-core workload                                                                                              | 59 |

| 5.14 | SPL and bus traffic of PADC for prefetch-unfriendly 4-core workload                                                                                      | 60 |

| 5.15 | Performance of PADC for mixed 4-core workload                                                                                                            | 61 |

| 5.16 | SPL and bus traffic of PADC for mixed 4-core workload                                                                                                    | 61 |

| 5.17 | Performance of PADC on 4-core system                                                                                                                     | 65 |

| 5.18 | Performance of PADC on 8-core system                                                                                                                     | 66 |

| 5.19 | DRAM request fields for PADC with ranking                                                                                                                | 69 |

| 5.20 | Optimized PADC with ranking on 4-core system                                    | 70 |

|------|---------------------------------------------------------------------------------|----|

| 5.21 | Optimized PADC using ranking mechanism on 8-core system                         | 71 |

| 5.22 | Performance of PADC on 4-core system with two DRAM controllers                  | 72 |

| 5.23 | Performance of PADC on 8-core system with two DRAM controllers                  | 72 |

| 5.24 | Effect of PADC with various DRAM row buffer sizes on 4-core system              | 73 |

| 5.25 | Effect of PADC on closed-row scheduling policy                                  | 75 |

| 5.26 | Effect of PADC on shared last-level cache on 4-core system                      | 77 |

| 5.27 | Effect of PADC on shared last-level cache on 8-core system                      | 77 |

| 5.28 | Effect of PADC on various cache sizes on 4-core system                          | 79 |

| 5.29 | PADC on stride, C/DC, and Markov prefetchers                                    | 81 |

| 5.30 | Effect of PADC on runahead execution                                            | 83 |

| 5.31 | Comparison of PADC with DDPF and FDP with demand-first                          | 86 |

| 5.32 | Comparison of PADC to DDPF and FDP with demand-prefetch-equal                   | 87 |

| 5.33 | Effect of PADC on permutation-based page interleaving                           | 88 |

| 6.1  | How prefetching can increase DRAM BLP (libquantum)                              | 91 |

| 6.2  | FIFO vs. DRAM BLP-aware prefetch issue policy                                   | 93 |

| 6.3  | Hardware structures for BLP-Aware Prefetch Issue (BAPI)                         | 96 |

| 6.4  | Round-robin vs. BLP-preserving request issue policy                             | 00 |

| 6.5  | Performance, BLP, and SPL of BAPI on single-core system 1                       | 09 |

| 6.6  | Bus traffic of BAPI on single-core system                                       | 10 |

| 6.7  | Performance of BLP-aware issue policies for prefetch-friendly workload          | 14 |

| 6.8  | Performance of BLP-aware issue policies on 4-core system 1                      | 16 |

| 6.9  | Performance of BLP-aware issue policies on 8-core system 1                      | 17 |

| 6.10 | BLP-aware issue policies with stride and C/DC prefetchers 1                     | 18 |

| 6.11 | Comparison of BLP-aware issue policies with PAR-BS 1                            | 20 |

| 6.12 | Combination of PADC and BLP-Aware Issue Policies                                | 21 |

| 7.1  | DRAM and processor performance for two different mixtures of outstanding misses | 24 |

| 7.2  | Low-cost estimation for LPA                                                     | 26 |

| 7.3  | Conventional vs. write-caused interference-aware replacement policies           | 32 |

| 7.4  | Dirty row-hit search for WIA                                                    | 34 |

| 7.5  | Performance of DRAM-aware replacement policies on single-core system            | 43 |

| 7.6  | DRAM read traffic and aggregate BLP of DRAM-aware replacement policies                                       |

|------|--------------------------------------------------------------------------------------------------------------|

| 7.7  | DRAM write traffic and aggregate BLP of DRAM-aware replacement policies                                      |

| 7.8  | Performance of DRAM-aware replacement policies on single-core system with prefetching                        |

| 7.9  | Performance of DRAM-aware replacement policies on 4-core system 150                                          |

| 8.1  | Potential (simulated) performance of intelligently handling write-<br>caused interference in the DRAM system |

| 8.2  | Performance potential by eliminating all writes as memory bus clock frequency increases                      |

| 8.3  | Service_at_no_read vs. drain_when_full write buffer policies 158                                             |

| 8.4  | Write-cause interference-aware replacement vs. DRAM-aware write-back                                         |

| 8.5  | Writeback mechanism in last-level cache                                                                      |

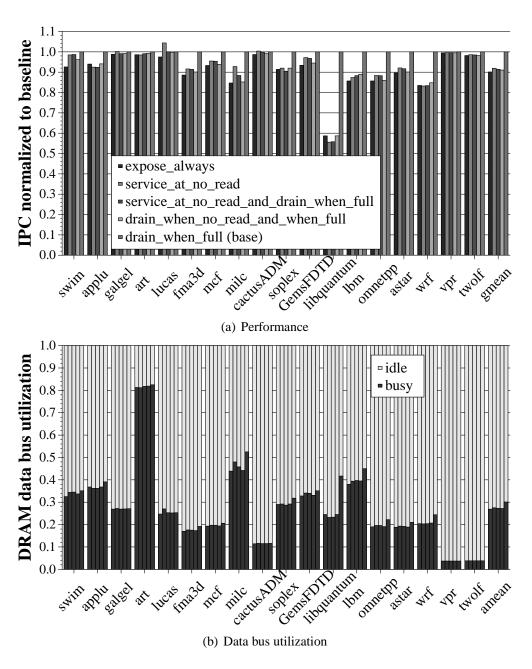

| 8.6  | Performance and DRAM bus utilization of various write buffer policies                                        |

| 8.7  | Performance and DRAM bus utilization of DRAM-aware write-back on single-core system                          |

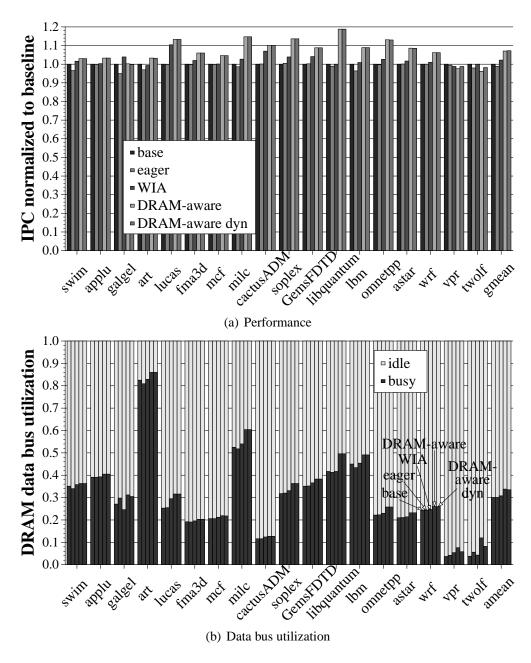

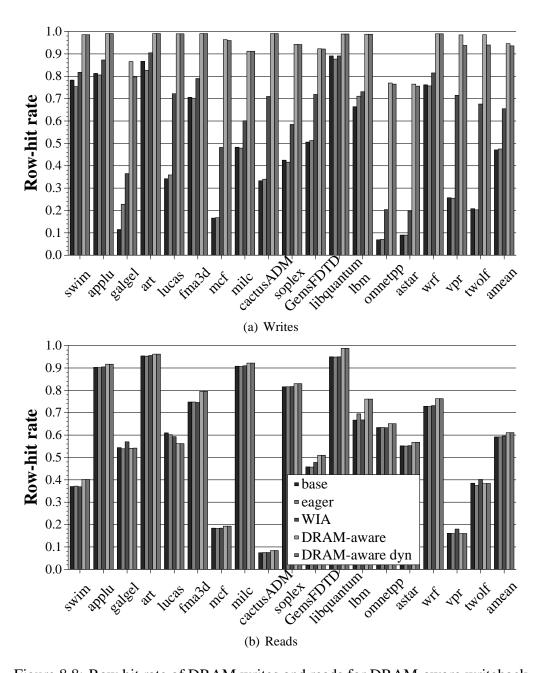

| 8.8  | Row hit rate of DRAM writes and reads for DRAM-aware writeback 178                                           |

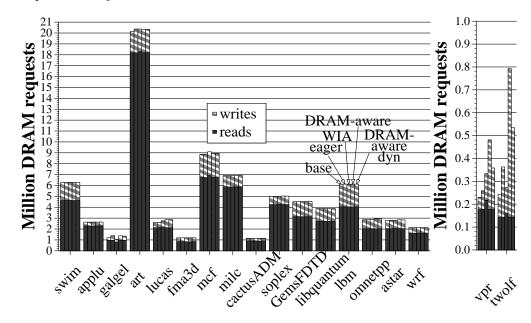

| 8.9  | Number of DRAM requests for DRAM-aware writeback 181                                                         |

| 8.10 | Performance of DRAM-aware writeback on 4-core system 183                                                     |

| 8.11 | Performance of DRAM-aware writeback on 8-core system 183                                                     |

| 8.12 | Performance of DRAM-aware writeback on 4-core system with prefetching                                        |

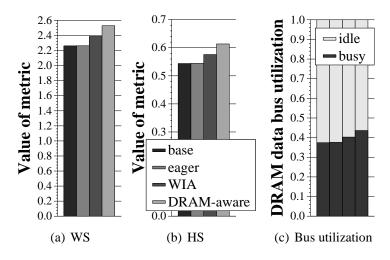

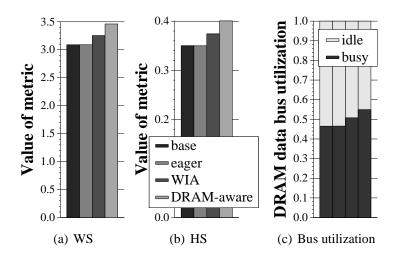

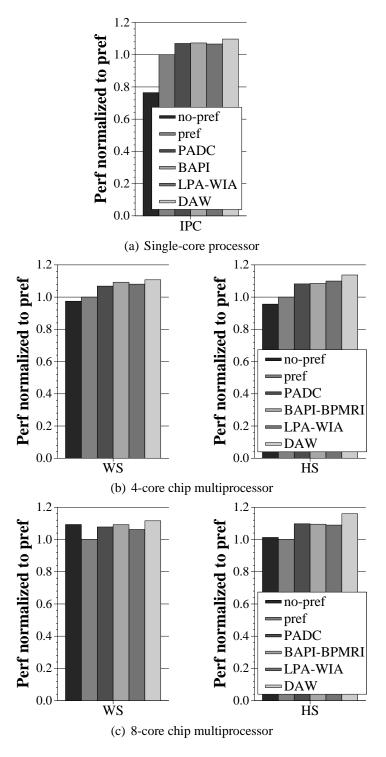

| 9.1  | Performance of individual DRAM-aware mechanisms on single, 4, and 8-core systems                             |

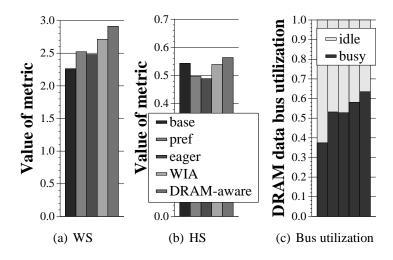

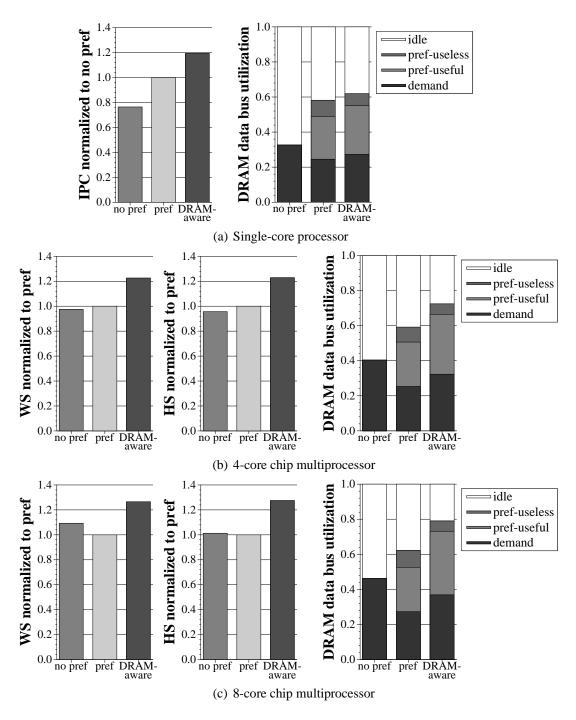

| 9.2  | Performance and DRAM bus utilization of combined DRAM-aware mechanisms                                       |

## **Chapter 1**

## Introduction

#### 1.1 Problem

Memory system performance is crucial for high performance computing. Dynamic Random Access Memory (DRAM) is the most commonly used technology for building the main memory system in modern computer systems. Therefore, computer architects need to understand the characteristics of DRAM in order to build high performance memory systems. There are three main performance-related characteristics associated with DRAM: bank-level parallelism, row buffer locality, and write-caused interference.

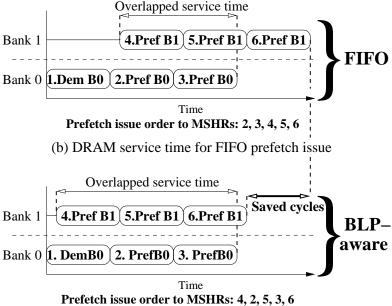

- Bank-Level Parallelism: A modern DRAM chip consists of multiple banks that can be accessed independently. Memory requests to different DRAM banks can proceed concurrently. Therefore, the requests' access latencies can be overlapped, thereby increasing DRAM throughput. The notion of servicing multiple requests in parallel in different DRAM banks is called DRAM Bank-Level Parallelism (BLP).

- Row Buffer Locality: Each DRAM bank consists of rows and columns of DRAM cells. A row contains a fixed-size block of data (usually several Kbytes). Each bank has a row buffer (or sense amplifier), and a DRAM access can be made only by reading (writing) data from (to) the row buffer using a column address. To perform a complete access, 1) a row is loaded into the row buffer and 2) the data in the row buffer is read (written to). The row buffer keeps the most recently accessed row in the DRAM bank. A subsequent access to the last accessed row can be serviced significantly faster than

an access to a different row. This concept is referred to as *row buffer locality*. Prioritizing a request among multiple memory requests to the currently open row results in higher DRAM throughput.

• Write-Caused Interference: Write requests interfere with read requests in the DRAM system by causing idle cycles on the DRAM data bus. Once a write is serviced, subsequent reads and even some writes (e.g., writes to different rows in the same bank) cannot be started for a certain amount of time even after the write is fully serviced. This introduces idle cycles on the data bus and in turn degrades DRAM throughput. We call this write-caused interference in the DRAM system.

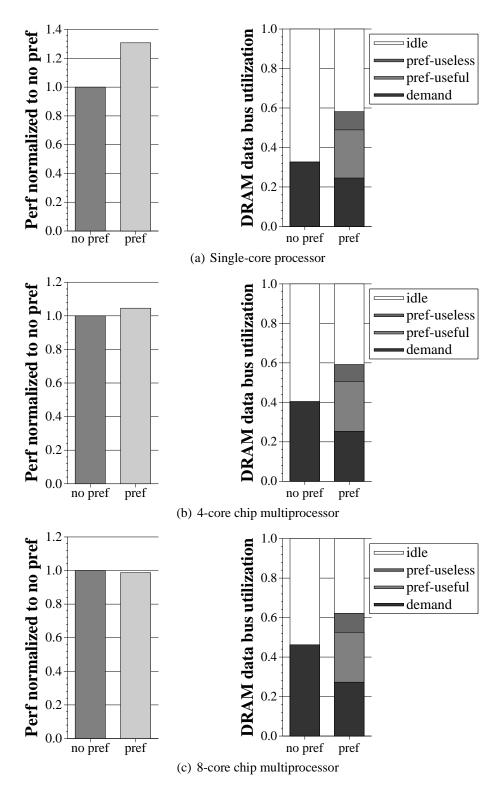

We define a processor's on-chip memory system as the collection of the following: 1) the memory controller, 2) the structures that generate main memory requests (e.g., last-level cache and prefetcher structures), 3) the buffer structures which memory requests go through until they are serviced by the DRAM system, and 4) the corresponding management policies associated with 1), 2), and 3). If the on-chip memory system takes into account bank-level parallelism, row buffer locality, and write-caused interference, DRAM performance and in turn system performance can be significantly improved. However, conventional on-chip memory systems do not fully consider these DRAM system characteristics and therefore often do not provide the best system performance. This problem becomes more significant for Chip MultiProcessor (CMP) systems where the DRAM system is shared by multiple cores on a chip. Figure 1.1 shows the average system performance and DRAM data bus utilization for single, 4, and 8-core systems. In this experiment, we used a DDR3 DRAM system [49] and aggressive 4.8 GHz x86 microprocessors <sup>1</sup> with and without an aggressive stream prefetcher [77, 73, 36]. We ran the 20 most memory-intensive SPEC CPU 2000/2006 benchmarks on the

<sup>&</sup>lt;sup>1</sup>We deliberately chose an aggressive processor frequency to account for future technology advancements. The performance and DRAM bus utilization trends shown here do not change significantly with less aggressive frequencies (e.g., 3.2GHz).

single-core system. We simulated 30 and 20 pseudo-randomly chosen multiprogrammed workloads [39] on the 4-core and 8-core CMP systems respectively. <sup>2</sup> We make four observations from Figure 1.1.

First, with no prefetching, as the number of cores increases DRAM bus utilization increases. This is because multiple applications run together on different cores on the chip and generate more memory requests to the DRAM system.

Second, the DRAM data bus is not fully utilized for any of the three systems even with prefetching. For the single and 4-core systems, when the stream prefetcher is employed, bus utilization increases and performance improves (by 30.8% and 4.5%) compared to no prefetching. However, there are still a significant number of idle data bus cycles. One of the main reasons is that conventional on-chip memory systems do not fully take advantage of the DRAM system. They sometimes limit the amount of row buffer locality and bank-level parallelism exploited by the DRAM controller or do not try to minimize write-caused interference. System performance can be improved by exploiting or reducing those idle cycles for useful requests.

Third, even though prefetching increases bus utilization in the 4 and 8-core systems, the performance improvement is not very significant. In fact, the 8-core system suffers performance degradation (by 1.3%) compared to no prefetching even though more DRAM bandwidth is consumed. This is because the increased memory request contention due to the increased number of cores is not managed efficiently by conventional memory systems since they do not take into account the DRAM system's characteristics and applications' behavior together. For example, contention between memory requests from applications A and B running together can cause application B to close a row buffer that was opened by application A. This results in longer DRAM latency for application A's later memory access to the closed row since the closed row must be reopened. Also, memory requests to different banks from application A that could potentially be serviced in parallel in

<sup>&</sup>lt;sup>2</sup>Chapter 9 explains the system configurations and the workloads in detail.

Figure 1.1: Performance and DRAM bus utilization for a conventional memory system with no prefetching and a stream prefetcher (with the peak DRAM bandwidth of 12.8, 25.6, 25.6GB/s for single, 4, and 8-core systems respectively)

multiple DRAM banks may end up being serviced serially due to interference from application B's memory requests. Both examples can result in poor performance even though data bus utilization has increased compared to no prefetching.

Finally, a significant number of cycles are spent for useless prefetch requests (brought from DRAM but not used). Useless prefetches consume DRAM bandwidth without contributing to performance. Even worse, they sometimes even hurt performance as shown in Figure 1.1(c). Removing useless prefetches results in more efficient data bus utilization, allowing useful requests to be serviced faster.

We would like to develop a comprehensive on-chip memory system design that can efficiently exploit or reduce the idle DRAM data bus cycles for high performance. To this end, this dissertation proposes new low-cost on-chip memory system (i.e., prefetcher, buffer, and cache structures) designs that take into account DRAM characteristics. The proposed mechanisms significantly improve system performance by reducing DRAM access latency and increasing DRAM access parallelism for useful memory requests for both single-core and chip multiprocessor systems.

#### 1.2 Thesis Statement

Performance of microprocessors can be improved significantly by taking into account the main memory system's characteristics in their on-chip memory system designs.

#### 1.3 Contributions

This dissertation makes the following contributions.

This dissertation introduces the notion of main memory (DRAM)-aware design of a microprocessor's on-chip memory system. It identifies three major DRAM characteristics in state-of-the-art DRAM systems which significantly affect performance: row buffer locality, bank-level parallelism, and

write-caused interference. It shows that conventional on-chip memory system designs that do not take into account these characteristics result in underutilization of the DRAM system, thereby limiting overall system performance. To overcome this problem, this dissertation proposes and evaluates DRAM characteristic-aware prefetch scheduling/issuing and cache management techniques.

- This dissertation identifies problems of the conventional DRAM controller design in the presence of prefetching. It presents a prefetch-aware DRAM controller design that aims to maximize row buffer locality only for demand and useful prefetch memory requests and to minimize the negative effect of useless prefetch requests. The proposed technique significantly improves performance by reducing the latency of useful requests and removing useless prefetches.

- This dissertation shows that conventional request issue policies to resource-limited on-chip buffers can limit the amount of Bank-Level Parallelism (BLP) realized by the DRAM controller. This reduces the effectiveness of prefetching and out-of-order execution. This dissertation presents and analyzes on-chip request issue policies that aim to maximize DRAM BLP. The evaluations show that the proposed BLP-aware policies significantly increase BLP and therefore improve system performance.

- This dissertation demonstrates that due to the DRAM characteristics, not all misses and evictions of the last-level cache incur the same cost. It proposes a DRAM-aware last-level cache replacement policy that favors the replacement of low-cost cache lines that will likely take advantage of row buffer locality and BLP and lines that can reduce write-caused interference. The evaluations show that the DRAM-aware replacement policy can improve performance by exploiting all DRAM characteristics.

- This dissertation identifies limitations of our DRAM-aware replacement policy that aims to reduce write-caused interference in the DRAM system. It

proposes a more aggressive writeback technique for the last-level cache to further reduce write-caused interference. The proposed writeback mechanism proactively sends writebacks from dirty lines that can be serviced fast due to row buffer locality. The results presented in this dissertation show that this mechanism allows the DRAM controller to service more writes quickly, thereby resulting in less write-caused interference than our DRAM-aware replacement policy.

This dissertation evaluates the performance and DRAM efficiency of all the

proposed DRAM-aware techniques when employed together. The results

show that the techniques work synergistically and increase DRAM utilization

significantly. The proposed mechanisms significantly improve performance

on both single-core and chip multiprocessor systems.

## 1.4 Dissertation Organization

This dissertation is organized into ten chapters. Chapter 2 provides background information on the three DRAM performance-related characteristics based on the industry standards. Chapter 3 provides an overview of four proposed mechanisms that aim to improve DRAM performance. Chapter 4 discusses related work. In the following four chapters, we propose and evaluate four mechanisms. Chapter 5 presents and analyzes a prefetch-aware DRAM controller that tries to maximize row buffer locality for demand and useful prefetches and minimize the negative effect of useless prefetches. Chapter 6 proposes and discusses two Bank-Level Parallelism (BLP)-aware memory request issue policies in order to improve BLP. Chapter 7 presents and evaluates a DRAM-aware last-level cache replacement policy that aims to improve all three DRAM characteristics. Chapter 8 proposes and analyzes a DRAM-aware last-level cache writeback mechanism that can significantly reduce write-caused interference. Chapter 9 evaluates and discusses performance and DRAM efficiency when all four proposed DRAM-aware mechanisms are employed together on both single-core and multi-core systems. Chapter 10 con-

cludes this dissertation.

# Chapter 2

# Background: DRAM Performance-Related Characteristics

In this chapter, we provide background on three DRAM characteristics based on the Double Data Rate 3 (DDR3) SDRAM Joint Electron Device Engineering Council (JEDEC) standard. We follow the abbreviations of the standard. We refer readers to the DDR standard documentations and product datasheets [22, 49] for further detailed information. We accurately model all these performance-related timing constraints in our DRAM simulation model for our experimental evaluations of the proposed mechanisms.

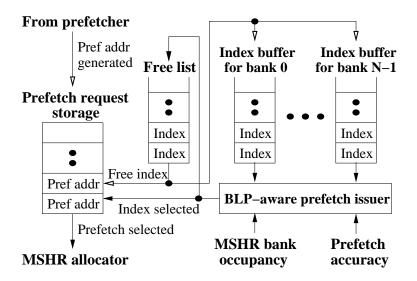

## 2.1 Row Buffer Locality

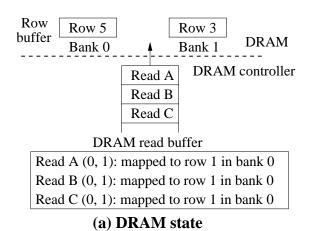

Each DRAM bank is arranged in rows and columns of DRAM cells. The size of a row is several Kbytes (1 or 2 Kbytes in each bank per DRAM chip) in modern DRAM systems. To perform a complete access to a data element, three steps are required for the DRAM controller. First, a *precharge* command is sent to precharge the bank's bitlines. Second, an *activate* command is sent to open the source/destination row through the sense amplifier (which we call row buffer throughout this dissertation) in the bank. Finally, a *read* or *write* command is scheduled to access the appropriate columns from the row data in the row buffer. Every access can be performed only by reading from or writing to the row buffer. Therefore, if a subsequent access to the bank is mapped to a different row, these three steps (i.e., precharge, activate, and read/write) must be performed again. We call an access to a different row a *row conflict*. On the other hand, a subsequent access which is mapped to the same row as the previous row can be performed simply by

accessing the appropriate column from the currently open row. We call this access a *row hit*. Since a row hit requires only the third of the three steps, its DRAM service time is much less than that of a row conflict.

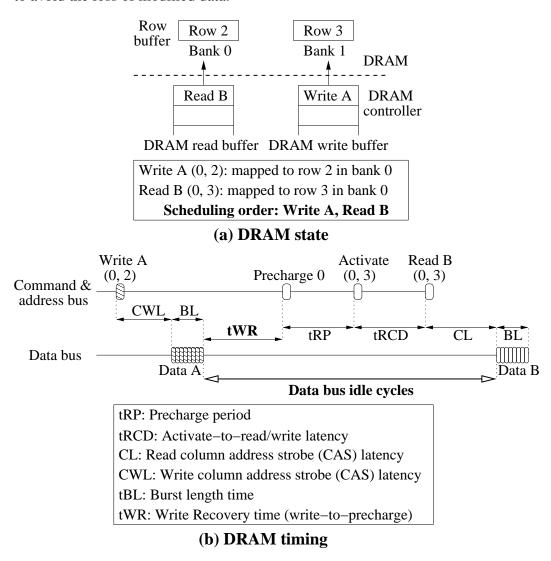

Figure 2.1 illustrates exactly how the DRAM system works for these accesses. Figure 2.1(a) shows that three reads (A, B, and C) are waiting in the DRAM read buffer for DRAM scheduling. Figure 2.1(b) shows the resulting DRAM timing when these reads are serviced. The DDR3 DRAM's *prefetch buffer* enables a burst mode of up to eight (burst length, BL = 8) by bringing (eight) consecutive columns from the row buffer to the prefetch buffer. <sup>1</sup> Each command (e.g., read, write, or precharge) takes a DRAM bus cycle and every data transfer is done in burst mode at twice the rate of the clock (i.e., double data rate, 4 DRAM clock cycles for BL = 8). <sup>2</sup>

In this example, all reads are mapped to the same row (Row 1) in Bank 0. Currently Row 5 is open in the row buffer of bank 0. Read A has to go through all three steps since it is a row conflict. The total service time for Read A is the sum of the latencies for the three steps (precharge period + Activate-to-read/write delay + column address strobe latency,  $t_{RP} + t_{RCD} + CL$ ) as shown in Figure 2.1(b). After this latency, the data required by Read A is put onto the data bus. Since the burst length is eight, eight bursts of data are sent to the data bus. The subsequent two reads can simply access the row opened by Read A. Even though accessing a given column within a row takes only column address strobe latency (CL), consecutive row-hit reads are serviced even faster. This is because the DDR3 system allows row-hit latencies (CLs) to overlap in order to support back-to-back data transfers among row-hit reads (even among row-hit reads in different banks). Therefore the effective latency of a row hit can be simply data burst latency from the processor's

<sup>&</sup>lt;sup>1</sup>This is called the 8*n-bit prefetch architecture* in the DDR3 technology, where n is the number of data pins in a DDR3 DRAM chip. The DRAM prefetch buffer is shared by all sense amplifiers (i.e., row buffers, each of which is in a bank).

<sup>&</sup>lt;sup>2</sup>Throughout this dissertation, we assume that the DRAM system has a DRAM Dual Inline Memory Module (DIMM) with a 64-bit wide data bus per DRAM channel. Therefore, the data transfer for a 64-byte cache line can be completed with a burst length of eight.

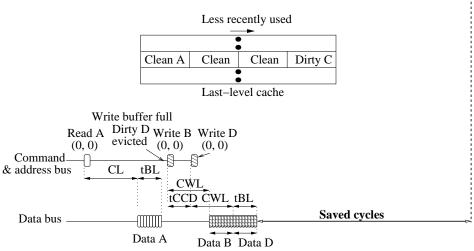

tRP: Precharge period

tRCD: Activate-to-read/write delay in the bank

CL: Read column address strobe (CAS) latency

tBL: Burst length time

tCCD: CAS-to-CAS delay

## (b) DRAM timing

Figure 2.1: Row conflict and row hit in modern DRAM system

point of view. This makes a row-hit request much faster than a row-conflict request (up to 9 times faster in a DDR3-1600 chip [49]). Note that such back-to-back data transfers are supported among row-hit writes as well by overlapping write column address strobe latencies (CWLs).

Since row hits can be serviced (effectively  $3 \sim 9$  times) faster than row conflicts, many DRAM controllers prioritize row hits over row conflicts in their scheduling decisions [92, 66, 48].

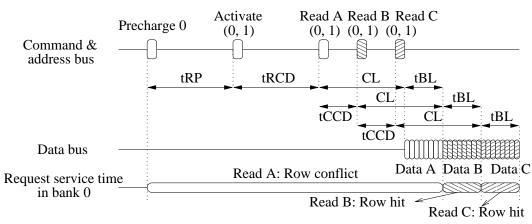

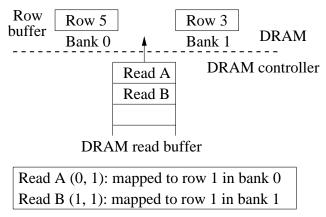

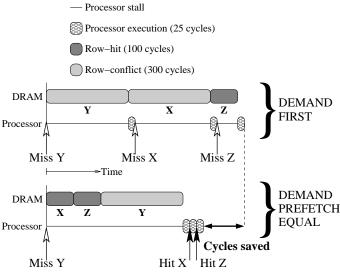

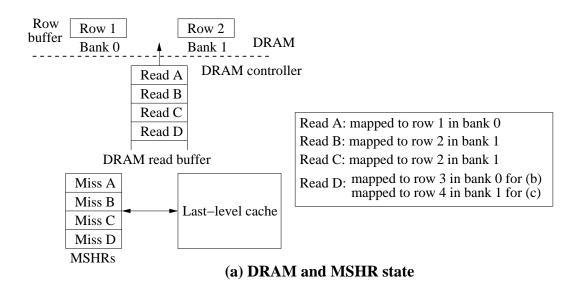

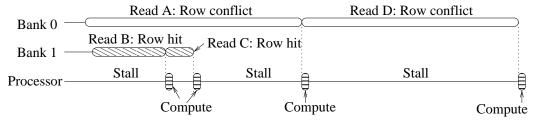

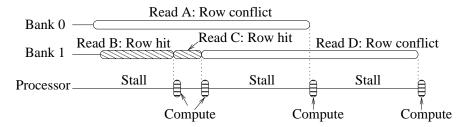

#### 2.2 Bank-Level Parallelism

A DRAM chip consists of multiple ( $4 \sim 8$ ) independent banks and accesses to different banks can be serviced concurrently. Figure 2.2 shows the DRAM behavior of two row conflict accesses to different banks. Read A is mapped to Row 1 in Bank 0 and Read B is mapped to Row 1 in Bank 1 as shown in Figure 2.2(a). Even though they are row conflicts (i.e., the current open rows are different from the rows they access), their DRAM service times can be significantly overlapped as shown in Figure 2.2(b). Therefore the effective stall time of the processor for these two requests is much less than the sum of the two access latencies. Note that if two row conflicts are mapped to different rows in the same bank, they are serviced completely serially and the processor experiences the sum of two row-conflict accesses.<sup>3</sup>

### 2.3 Write-Caused Interference

Write-caused interference in DRAM comes from read-to-write, write-to-read, and write-to-precharge latency penalties. Read-to-write and write-to-read latencies dictate the minimum latencies between a read command and a write command regardless of what DRAM banks they belong to. In contrast, write-to-precharge

$<sup>^3</sup>$ To be precise, the total service time of two consecutive row conflicts in the same bank is more than the sum of two row conflict latencies due to other DRAM timing constraints such as the activate-to-activate command period ( $t_{RC}$ ) and the activate-to-precharge command period ( $t_{RAS}$ ).

#### (a) DRAM state

## (b) DRAM timing

Figure 2.2: DRAM bank-level parallelism

specifies the minimum latency between a write burst and a subsequent precharge command to the same bank. We first describe read-to-write and write-to-read latencies.

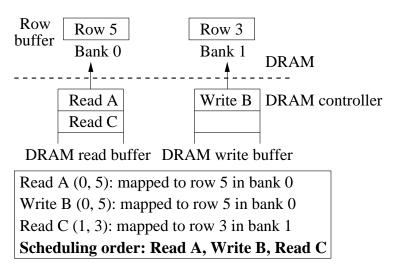

#### 2.3.1 Read-to-write and write-to-read latencies

Read-to-write latency is the minimum latency from a read data burst to a write data burst. This latency is required to change the data bus I/O pins' state from read state to write state. Therefore, during this latency the bus has to be idle. This latency must be satisfied regardless of whether the read and the write access the same bank or different banks. In DDR3 DRAM systems, read-to-write latency is **two DRAM clock cycles**.

Write-to-read ( $t_{WTR}$ ) latency is the minimum latency from a write burst to a subsequent read command. In addition to the time required for the I/O state change from write to read, this latency also includes the time required to guarantee that modified data (in the DRAM's prefetch buffer) can be safely written to the row buffer (i.e., sense amplifier). A common internal bidirectional bus connects the prefetch buffer and the row buffers of all DRAM banks. All read and write transfers use this bidirectional bus. Therefore, a subsequent read cannot use the common internal bus to bring data into the prefetch buffer until the current write's modified data is completely written back to the corresponding bank's row buffer. Therefore  $t_{WTR}$  is much larger (e.g., **six DRAM clock cycles** for DDR3-1600) than read-to-write latency and introduces more idle DRAM data bus cycles. Also, write-to-read latency must be satisfied regardless of whether the write and the read are to the same bank or different banks.

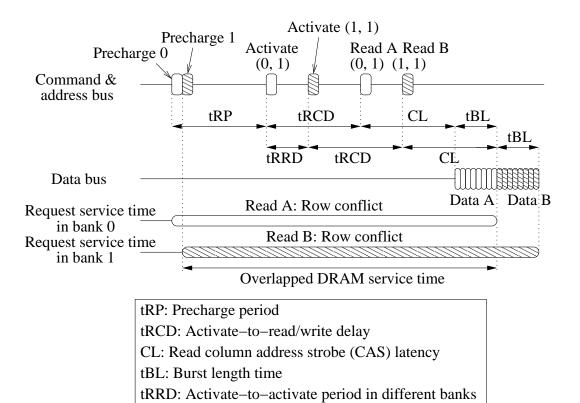

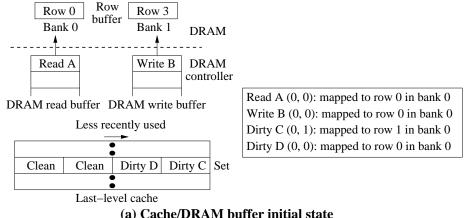

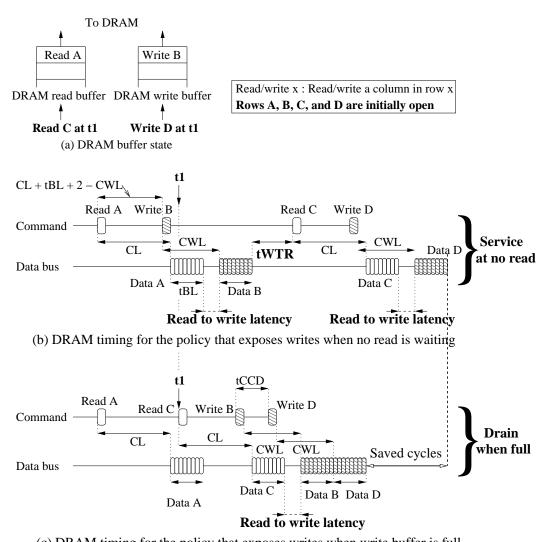

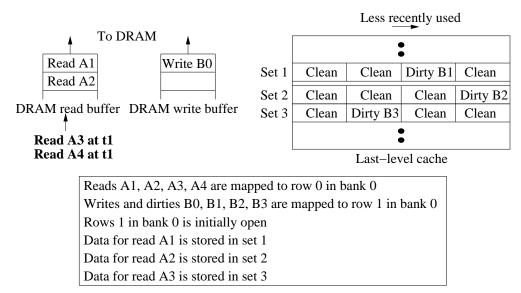

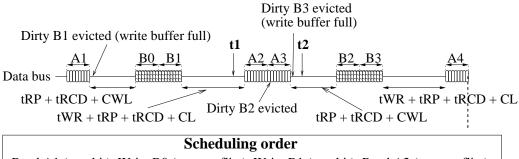

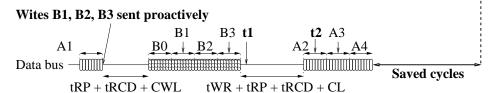

We demonstrate these penalties using an example in Figure 2.3. Figure 2.3(a) shows the initial state of the DRAM read/write buffer and the row buffer state of two banks. Two reads (A and C) and one write (B) are in the read and write buffer respectively. Read A and Write B are mapped to the currently open row in Bank 0 whereas Read C is mapped to the currently open row in Bank 1. Hence they are

### (a) DRAM state

(b) DRAM timing

Figure 2.3: Read-to-write and write-to-read latencies

all row hits. Let us assume that the underlying DRAM controller schedules these requests in the order of Read A, Write B, and Read C. Figure 2.3(b) shows the resulting DRAM timing diagram.

The command for Write B after Read A must be scheduled such that the read-to-write latency between the corresponding data bursts is satisfied. In order for the write burst to be on the bus two DRAM cycles after the read burst, the command for Write B has to be scheduled by the DRAM controller at least  $CL + t_{BL} + 2 - CWL$  DRAM clock cycles after the read command is scheduled [22]. <sup>4</sup> Also, Read C after Write B satisfies  $t_{WTR}$  (i.e., write-to-read latency). Read C can only be scheduled  $t_{WTR}$  cycles after the data burst for Write B is completed. In contrast to read-to-write latency, the data bus must be idle for  $t_{WTR} + CL$  cycles since the subsequent read command cannot be scheduled for  $t_{WTR}$  cycles.

Due to read-to-write and write-to-read penalties, switching service between reads and writes frequently in the DRAM system results in many idle cycles. This problem can be mitigated by a good write buffer policy as we will discuss in Chapter 8. However a write buffer policy cannot solve the problem completely due to write-to-precharge (or write recovery time,  $t_{WR}$ ) penalties as we show below.

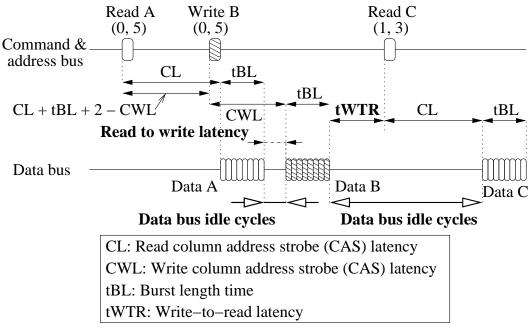

#### 2.3.2 Write-to-precharge latency

Write-to-precharge latency (write recovery time, tWR) comes into play when a subsequent precharge command is scheduled to open a different row after a write to a bank. Write-to-precharge latency specifies the minimum latency from a write data burst to a precharge command in the same DRAM bank. This latency is very large (12 DRAM clock cycles for DDR3-1600) because the written data in the DRAM's prefetch buffer must be written back to the corresponding DRAM row through the row buffer before precharging the DRAM bank. This needs to be done

$<sup>^4</sup>$ We assume that the additive latency (AL) is zero in this dissertation. If a non-zero AL is considered, the subsequent write command can be scheduled  $CL+AL+t_{CCD}+2-(CWL+AL)$  cycles after the read command, where  $t_{CCD}$  is the minimum column strobe to column strobe latency). To maximize bandwidth we set up  $t_{BL}$  to eight, therefore  $t_{CCD}$  is equal to (tBL) [22].

to avoid the loss of modified data.

Figure 2.4: Write-to-precharge (write recovery time) latency

Figure 2.4 illustrates write-to-precharge penalty in a DRAM bank. Write A and Read B access different rows in the same bank (Bank 0). Therefore, after Write A is serviced, a precharge command is required to open the row for Read B (i.e., row conflict). Subsequent to the scheduling of Write A, the precharge command must wait until write-to-precharge latency is satisfied before it can be scheduled. Note that this penalty must be satisfied regardless of whether the subsequent precharge command is for a read or a write. The resulting data bus idle cycles is  $t_{WR} + t_{RP} +$

$t_{RCD} + CL$  DRAM clock cycles unless there are other requests that are being read or written in different banks.

Since the write-to-precharge latency must be satisfied even for a precharge for a subsequent write, row conflicts among writes degrade DRAM throughput for writes. For example, a write to Row 1 after a write to Row 3 in the same bank must still satisfy this write-to-precharge penalty before the precharge command for the write to Row 3 can be scheduled. This problem cannot be solved by the DRAM write buffer and its policy. If writes in the write buffer access different rows (row-conflict writes) in the same bank, the total amount of write-to-precharge penalty becomes very large. This degrades DRAM throughput for writes and eventually results in delaying the service of reads, thereby degrading application performance.

# Chapter 3

## **Overview of the Solutions**

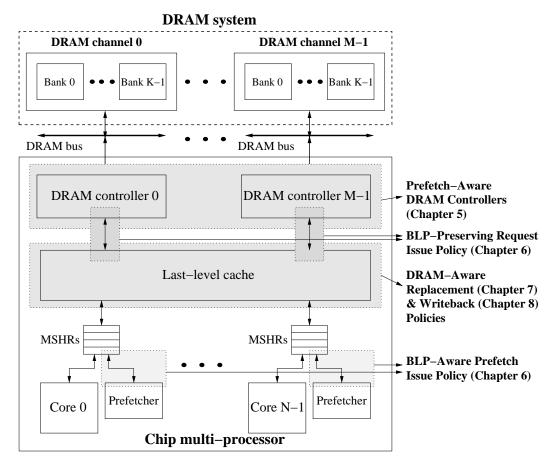

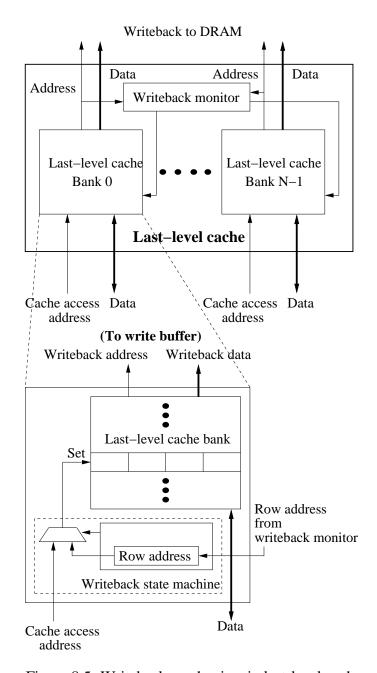

The dissertation makes a case for DRAM-aware on-chip memory system design. We propose DRAM characteristic-aware prefetching and cache management mechanisms that aim to maximize DRAM row buffer locality and bank-level parallelism and to minimize write-caused interference. We propose four different mechanisms, each of which works on a different on-chip memory resource structure to improve DRAM performance. Figure 3.1 illustrates where our mechanisms (shown in highlighted areas) would be employed in a conventional microprocessor. We briefly overview each of these mechanisms as follows.

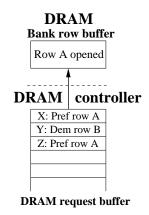

The first mechanism is a prefetch-aware DRAM controller that tries to minimize DRAM access latencies for useful memory requests (demand and accurate prefetches) by exploiting row buffer locality when prefetching. We make the DRAM controller(s) prefetch-aware and take advantage of low latencies for row-hit prefetches when the prefetches are estimated as useful. To minimize the negative effect of useless prefetches, the DRAM controller delays and drops prefetches predicted to be useless. Chapter 5 analyzes this mechanism.

The second mechanism is DRAM bank-level parallelism-aware memory request issue policies in on-chip buffer structures that aim to maximize BLP in the presence of prefetching. They determine the order in which requests are sent from one on-chip buffer to another buffer so that requests to different banks are eventually exposed together to the DRAM controller. We discuss a BLP-aware prefetch issue policy from the prefetch request buffer to the Miss Status/Information Holding Registers (MSHRs) in order to maximize the BLP of requests (demands and useful prefetches) exposed to the DRAM controller. We also propose a BLP-preserving

Figure 3.1: Overview of proposed DRAM-aware mechanisms

memory request issue policy from the last-level cache to the DRAM controller's buffers (DRAM request buffer). This policy tries to make sure that requests from each core can be serviced together by the DRAM controller without destroying the BLP of each core in CMP systems. Chapter 6 discusses and evaluates these BLP-aware issue policies.

The third mechanism is a DRAM-aware last-level cache replacement policy that tries to improve all three DRAM characteristics. It leverages the fact that a last-level cache replacement policy can fundamentally change the mixture/property of outstanding memory requests, which can affect DRAM performance due to the DRAM characteristics. The DRAM-aware replacement policy favors the eviction of cache lines that would be refetched in quickly due to row buffer locality or serviced

together with other misses in different DRAM banks, when they are refetched. It also evicts dirty lines that can be written back to DRAM quickly by exploiting row buffer locality, in order to reduce write-caused interference in the DRAM system. Since row-hit writes are serviced quickly (back-to-back), the DRAM controller can resume servicing reads sooner, which in turn improves DRAM performance. We discuss and analyze the DRAM-aware replacement policy in Chapter 7.

The fourth mechanism is a DRAM-aware last-level cache writeback policy that aims to further reduce write-caused interference in the DRAM system. In contrast to the DRAM-aware replacement, it proactively sends writebacks that are expected to hit in the DRAM row buffers even before a replacement happens. This significantly reduces write-caused interference because it allows more writes to be written back faster than the DRAM-aware replacement would. Chapter 8 studies and analyzes this DRAM-aware writeback policy.

Note that each of the four mechanisms manages a different on-chip memory system management policy to improve DRAM utilization. Therefore the four mechanisms are complementary. We evaluate and analyze the combination of all four mechanisms in Chapter 9.

# Chapter 4

## **Related Work**

How memory requests are managed in the on-chip memory system (DRAM controller, buffers, caches, and prefetching) of a processor significantly affects main memory (DRAM) performance. This chapter discusses studies that are relevant to on-chip memory system designs with respect to DRAM system, memory-level parallelism, prefetching, and last-level cache management.

## 4.1 Research in DRAM System Management

#### 4.1.1 DRAM Access Scheduling

A number of DRAM scheduling policies have been proposed. McKee et al. proposed DRAM scheduling policies that exploit row buffer locality and bank-level parallelism for streaming applications in a page mode DRAM system [46, 45, 47]. Zuravleff and Robinson patented a DRAM scheduling policy similar to McKee et al.'s [92]. Carter et al. proposed an off-chip memory controller that aims to reduces wasteful memory bandwidth consumption by remapping physical addresses [3]. Their mechanism also prefetches data from DRAM into an SRAM buffer in the memory controller to hide DRAM access latency. Rixner et al. proposed and evaluated DRAM scheduling policies in a stream processor [66]. Zhang and McKee evaluated a stride (stream) prefetcher combined with a scheduling policy that reorders memory requests such that multiple requests can be serviced together in different banks in a Rambus DRAM system [86, 48]. Since then, many other scheduling policies have been proposed in single-threaded [18, 68] and multithreaded [65, 89, 57, 85] systems. In addition, several recent studies [58, 53, 54, 20, 30, 31] proposed techniques for fairness (quality of service) and/or high performance across different

applications sharing the DRAM system. These prior proposals have the following limitations.

First, some DRAM scheduling policies [46, 45, 47, 92, 66, 57, 18, 89, 58, 68, 53, 54, 20, 85, 30, 31] do not consider hardware prefetching. Hardware prefetching is an important memory latency-tolerance technique already employed in most commercial processors [77, 17, 80, 68, 34]. It is very important to intelligently manage demand and prefetch requests to the DRAM system, since the performance with a prefetcher can significantly differ depending on how the DRAM controller handles prefetch requests compared to demand requests. In contrast to these prior prefetch-unaware scheduling policies, the prefetch-aware DRAM controller proposed in Chapter 5 adaptively prioritizes demand and prefetch requests based on prefetch usefulness to maximize row buffer locality for useful requests and minimize the negative effect of useless prefetches. The concept of adaptive prefetch handling can be applied to the existing prefetch-unaware DRAM access scheduling policies.

Second, the DRAM controller proposals that do consider hardware prefetching take two different approaches to handling prefetch requests. Some proposals [42, 18, 19, 73] always prioritize demand requests over prefetch requests. Other proposals [86, 48, 65, 3] and some commercial processors [76, 28] treat prefetch requests the same as demand requests. Neither of these approaches works best for all types of applications. This is because they do not take into account both the DRAM characteristics and prefetch usefulness for their scheduling decisions. The prefetch-aware controller outperforms these two rigid prefetch handling policies in DRAM scheduling, as we show in Chapter 5.

Third, the performance of the DRAM scheduling policies is limited by the number and composition of requests in the DRAM controller's buffers, i.e., the DRAM request buffers. If requests in the DRAM request buffers are not mapped to different DRAM banks, bank-level parallelism will be low regardless of the DRAM scheduling policy. Similarly, if multiple requests that are mapped to the same row

are not present in the DRAM request buffer, high row buffer locality cannot be exploited by a DRAM scheduling policy. The BLP-aware request issue (in Chapter 6), DRAM-aware last-level cache replacement (in Chapter 7), and DRAM-aware last-level cache writeback (in Chapter 8) mechanisms send out requests that can expose more BLP and row buffer locality in the DRAM request buffers. This allows the underlying DRAM scheduling policy to exploit higher BLP and row buffer locality.

#### 4.1.2 DRAM Write Buffer Management

Some previous proposals [40, 57, 68] discuss DRAM write buffer management polices to reduce write-caused interference in the main memory system. Writes in the write buffer are not considered for scheduling until the underlying write buffer policy decides to do so. Lee et al. [40] employed a write buffer management policy that allows the Rambus DRAM controller to schedule a write when the data bus is idle. Natarajan et al. [57] discussed different write buffer management policies that also opportunistically allow writes to be scheduled in a DDR2 DRAM system when there are no pending reads or when the write buffer is almost full (i.e., the number of writes is more than a threshold). Their policies also make sure that a certain number of writes are serviced, even when a new read comes while servicing the writes. Shao and Davis [68] proposed a DRAM scheduling policy in a DDR2 system which services writes when there are no reads in the DRAM read buffer, when the write buffer is full, or when a write hits the currently open row. If a new read comes into the DRAM request buffer, their mechanism allows the read to preempt writes that are being serviced.

Even though there are small differences among these write buffer policies, they are essentially based on the principle that scheduling writes when the bus is idle (no pending reads) can reduce the contention between reads and writes. However, we show in Chapter 8 that this principle is not the best with today's high-bandwidth DDR (DDR3) DRAM systems because of their large write-caused latency penalties. We show that the policy which services all writes present in the write buffer only when the write buffer becomes full (which we call the *drain\_when\_full* policy)

outperforms prior policies. This is because it 1) reduces the frequency of read-to-write/write-to-read switching, and 2) allows the DRAM controller to better exploit row buffer locality and bank-level parallelism exposed by more writes. We use this drain\_when\_full policy in our baseline memory system. Also, the aggressive DRAM-aware writeback policy in Chapter 8 further reduces write-caused interference by leveraging the benefits of this baseline drain\_when\_full policy.

## 4.2 Research in Improving Memory-Level Parallelism

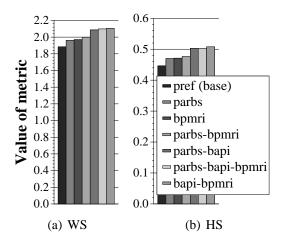

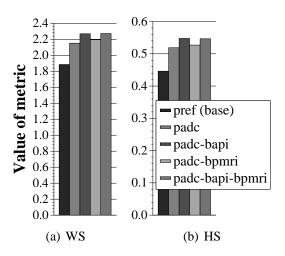

Many memory latency-tolerant techniques exploit Memory-Level Parallelism (MLP) by increasing the number of outstanding memory requests in the on-chip memory system [15]. Out-of-order execution [78] and non-blocking caches [33] allow generating concurrent memory requests. Prefetching techniques [32, 50, 14, 27, 1, 26] also increase MLP by issuing concurrent memory requests that are predicted to be used by the program.