Copyright by Yang-Yu Fan 2002

# The Dissertation Committee for Yang-Yu Fan certifies that this is the approved version of the following dissertation:

## Voltage and Temperature Dependent Gate Capacitance and Current Model for High-K Gate Dielectric Stack

| Committee:                         |

|------------------------------------|

|                                    |

| Sanjay K. Banerjee, Supervisor     |

| Leonard F. Register, Co-Supervisor |

|                                    |

| Jack C. Lee                        |

| Dim-Lee Kwong                      |

| Graham F. Carev                    |

## Voltage and Temperature Dependent Gate Capacitance and Current Model for High-K Gate Dielectric Stack

by

Yang-Yu Fan, B.S., M.S.E.

#### DISSERTATION

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

#### DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN

December 2002

### Acknowledgments

I would like to express my great gratitude to the many people who helped make this dissertation possible. First, I would like to thank my supervisors Professor Sanjay K. Banerjee and Leonard F. Register for their guidance and the freedom and independence they encourage in the device modeling group at University of Texas at Austin. Under such environment, I was able to explore this research work to the extent that I never imagined. Those efforts would not have resulted in any fruitful outcome without their insightful and timely guidance. I am thankful to Professor Jack C. Lee, Dim-Lee Kwong, and Gerald Lucovsky, and their students for the assistance in experiment and the discussion. I am also indebted to George A. Brown at International SE-MATECH. My gratitude goes to my doctoral committee and to the professors, students, and staff at Microelectronics Research Center. Especially, I would like to thank Jean Toll, Renee Nieh, Wen-Jie Qi, Siva Mudanai, Xin Wang, Mukund Swaminathan, Dong-Won Kim, and Katsunori Onishi. I am thankful to Douglas Roberts at Motorola, Inc., Judy An and Qi Xiang at AMD, Inc. for their guidance during the summer projects. I am grateful to my friends for the encouragement, advice, and the unforgettable times we spent together. I would like to thank Yi-Chang, Amy, Lai, Maga, Hung-Ming, I-Chi, and Daisy for their time and energy to endure everything I dumped to them. Finally, I dedicate this dissertation and everything I ever accomplished to my parents.

Voltage and Temperature Dependent Gate Capacitance and Current Model for High-K Gate Dielectric Stack

Publication No.

Yang-Yu Fan, Ph.D. The University of Texas at Austin, 2002

Supervisors: Sanjay K. Banerjee Leonard F. Register

High-dielectric-constant (High-K) materials are being pursued as alternative gate dielectrics to SiO<sub>2</sub> for next-generation Metal-Oxide-Silicon Field-Effect Transistors (MOSFETs). Great efforts are being made to optimize these materials for transistor applications. However, a major hurdle arises from the uncertainties about material properties, especially those of the thin films, and the physical mechanisms that affect the gate capacitance and gate current. In this work, based on the energy-dispersion relation in different regions of the Gate-Dielectric-Silicon system, a tunneling model is developed to understand the gate current as a function of voltage and temperature. A Franz 2-band dispersion relation is assumed in the bandgap to characterize the gate dielectric for tunneling. Quantum confinement effects in the silicon channel, direct and Fowler-Nordheim tunneling, and thermionic emission gate currents are considered simultaneously. The gate capacitance is self-consistently calculated from

the Schrodinger and Poisson equations subject to Fermi-Dirac statistics, using the same band structure in the silicon as used for tunneling injection. A self-consistent gate capacitance-current vs. voltage/temperature model is thus established. The model is implemented for both the silicon conduction and valence bands, and both gate- and substrate-injected currents. SiO<sub>2</sub> devices and multi-layer high-K gate dielectric stack structures such as ZrO<sub>2</sub> and HO<sub>2</sub> are studied by an integrated simulation and experimental investigation. A gate capacitance-current analysis method is explored for understanding the gate current mechanisms and extracting device structure parameters. A trend study for tradeoffs between low equivalent oxide thickness (EOT) and low gate current is performed qualitatively based on reasonable experimental data. Write/Erase/Retention time-dependent characteristics of non-volatile floating gate devices are modeled. Tend study on scaling the control and tunnel oxide is performed for SiO<sub>2</sub> and ZrO<sub>2</sub>.

## Table of Contents

| Ackno        | vledgments                                                                       | $\mathbf{v}$ |

|--------------|----------------------------------------------------------------------------------|--------------|

| ${f Abstra}$ | ct                                                                               | vi           |

| List of      | Tables                                                                           | x            |

| List of      | Figures                                                                          | xi           |

| Chapt        | r 1. Introduction                                                                | 1            |

| 1.1          | MOSFET Scaling                                                                   | 1            |

| 1.2          | $SiO_2$ Scaling and its Challenges                                               | 3            |

| 1.3          | Alternative Gate Dielectric: High-K Dielectric Stack                             | 6            |

| 1.4          | Scope and Organization                                                           | 8            |

| Chapt        | r 2. Fundamental Issues on High-K Gate Capacitance and Current Modeling          | 9            |

| 2.1          | Introduction                                                                     | 9            |

| 2.2          | Models                                                                           | 11           |

|              | 2.2.1 Energy Dispersion                                                          | 11           |

|              | 2.2.2 Gate Current Calculation                                                   | 14           |

|              | 2.2.3 Gate Current vs. Voltage/Temperature Behavior                              | 19           |

| 2.3          | $ZrO_2$ and $HfO_2$ NMOSCAP $C_g, I_g$ - $V_g$ Analysis                          | 21           |

|              | 2.3.1 $C_g$ vs. $V_g$                                                            | 21           |

|              | $2.3.2~~I_g~{ m vs.}~V_g/{ m Temperature}~.~.~.~.~.~.~.~.~.~.~.~.~.~.~.~.~.~.~.$ | 23           |

| 2.4          | Summary and Conclusions                                                          | 31           |

| Chapter 3.       |        | Impact of Interfacial Layer and Transition Region on<br>Gate Current: Its Tradeoff with Gate Capacitance                        | 33 |

|------------------|--------|---------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1              | Intro  | luction                                                                                                                         | 33 |

| 3.2              | Theor  |                                                                                                                                 | 36 |

| 3.3              | Resul  | ts and Discussion                                                                                                               | 42 |

| 3.4              | Sumn   | nary and Conclusions                                                                                                            | 51 |

| Chapt            | er 4.  | Conduction Mechanisms and Parameter Extraction from C-V and I-V Simulations and Experiments                                     | 53 |

| 4.1              | Intro  | luction                                                                                                                         | 53 |

| 4.2              | Mode   | l and Observations                                                                                                              | 54 |

| 4.3              | Resul  | ts and Discussion                                                                                                               | 56 |

|                  | 4.3.1  | $\rm SiO_2$ NMOSFETs vs. $\rm SiO_2$ PMOSCAPs: Substrate-Injected Electron Currents from p-Si Substrate and n-Si Substrate      | 56 |

|                  | 4.3.2  | SiO <sub>2</sub> NMOSFET vs. SiO <sub>2</sub> PMOSFET: Conduction-Band<br>Component and Valence-Band Component of Gate Currents | 60 |

|                  | 4.3.3  | $SiO_2$ NMOSFETs : $C_g, I_g$ - $V_g$ vs. Thickness and Temperature                                                             | 63 |

|                  | 4.3.4  | $k_{  }$ -Conservation in SiO <sub>2</sub> MOS Devices                                                                          | 66 |

|                  | 4.3.5  | $ZrO_2$ Metal Gate NMOSCAPs                                                                                                     | 70 |

| 4.4              | Concl  | usions and Summary                                                                                                              | 72 |

| Chapt            | er 5.  | Scaling ${\rm ZrO_2}$ Control/Tunnel Oxide for Floating-Gate Nonvolatile Memory Devices                                         | 73 |

| 5.1              | Intro  | luction                                                                                                                         | 73 |

| 5.2              | Mode   | ling                                                                                                                            | 74 |

| 5.3              | Discu  | ssion and Conclusions                                                                                                           | 80 |

| $\mathbf{Chapt}$ | er 6.  | Conclusions and Recommendations                                                                                                 | 86 |

| 6.1              | Sumn   | nary and Conclusions                                                                                                            | 86 |

| 6.2              | Recor  | nmendations for Future Work                                                                                                     | 89 |

| Biblio           | graphy | <b>V</b>                                                                                                                        | 91 |

| Vita             |        |                                                                                                                                 | 99 |

## List of Tables

| 1.1 | Experimental values of conduction band offsets of several high K materials with Si, obtained by Robertson et al [43]. $\varepsilon_{\infty}$ is obtained as the square root of the refractive index | 7   |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.1 | Material parameters of SiO <sub>2</sub> and ZrO <sub>2</sub> for calculating leakage currents in floating gate devices                                                                              | 7.5 |

# List of Figures

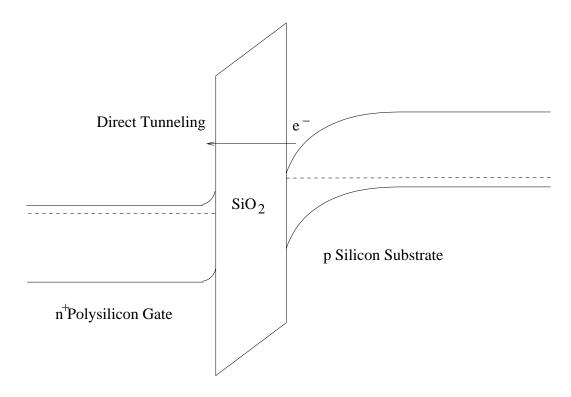

| 1.1  | Direct tunneling currents in a NMOSFET                                                                                                                                                                                                     | 5  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

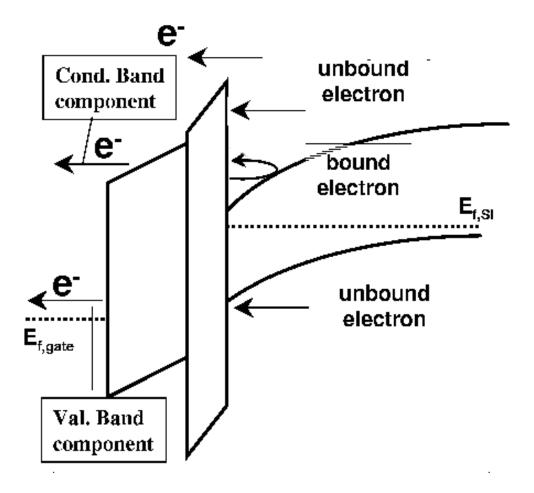

| 2.1  | Gate current model band diagram of a Gate-Dielectric-Silicon system being biased in the inversion region. Direct, Fowler-Nordheim tunneling, and thermionic emission gate currents are simultaneously considered                           | 12 |

| 2.2  | Gate capacitance model band diagram of a Gate-Dielectric-Silicon system being biased in the inversion region                                                                                                                               | 13 |

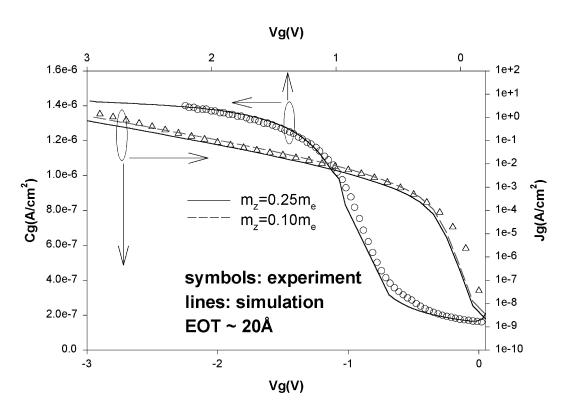

| 2.3  | Comparison of gate current and gate capacitance simulation with the experimental data for a SiO <sub>2</sub> -PMOSFET with EOT of $\sim 20 \text{Å}$ . Area = $10^{-4} \text{cm}^2$                                                        | 17 |

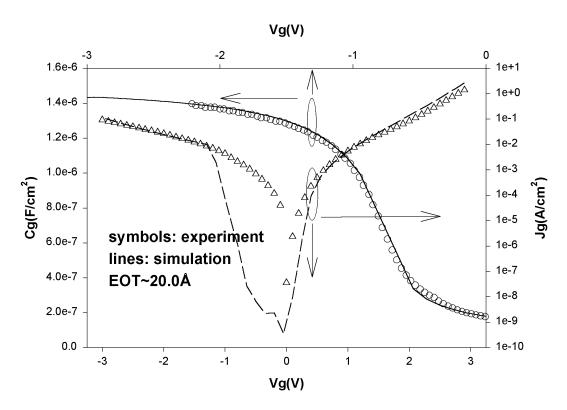

| 2.4  | Comparison of gate current and gate capacitance simulation with the experimental data for a $SiO_2$ -NMOSFET with EOT of $\sim 20 \text{Å}$ . Area = $10^{-4} \text{cm}^2$                                                                 | 18 |

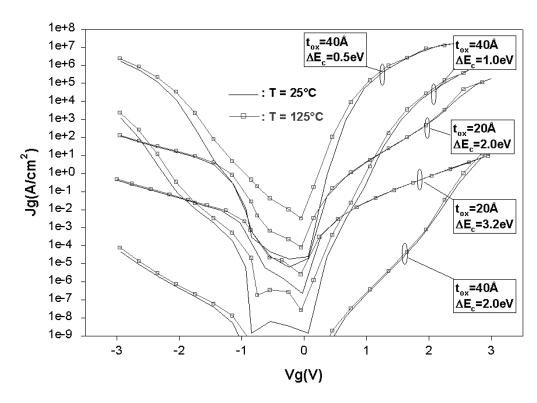

| 2.5  | Simulated $I_g$ -V <sub>g</sub> at 25°C and 125°C for n-channel MOSFETs with different dielectric thicknesses and conduction band offsets with silicon. Single layer of dielectric of dielectric constant of 3.9 is assumed in the devices | 20 |

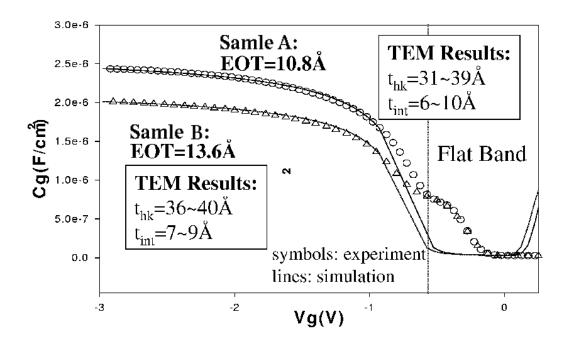

| 2.6  | Comparison of $C_g$ - $V_g$ simulation with the experimental data in accumulation for $\text{ZrO}_2$ -NMOSCAPs with different dielectric thicknesses, samples A and B                                                                      | 22 |

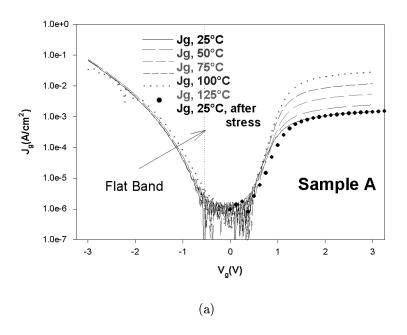

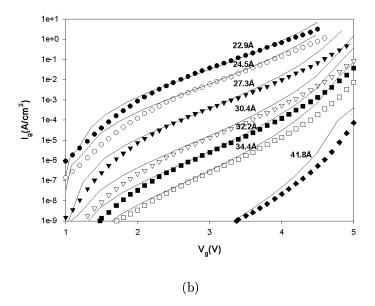

| 2.7  | Experimental gate current vs. voltage at different temperatures for (a) Sample A and (b) Sample B                                                                                                                                          | 24 |

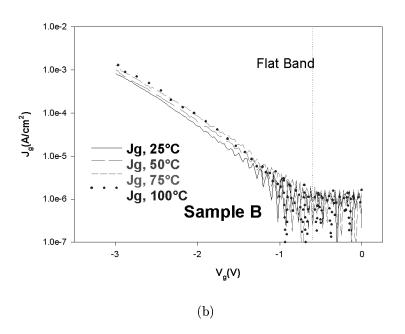

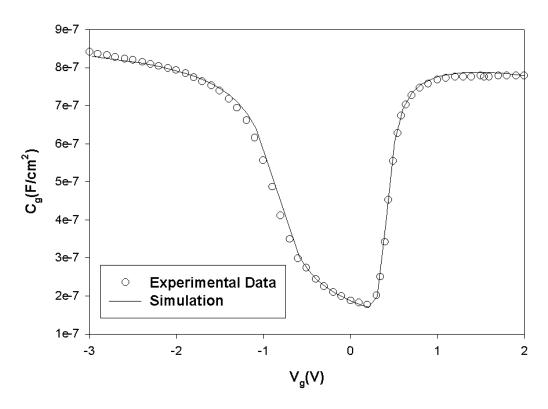

| 2.8  | Comparison of gate current and gate capacitance simulations with the experimental data for samples A and B                                                                                                                                 | 26 |

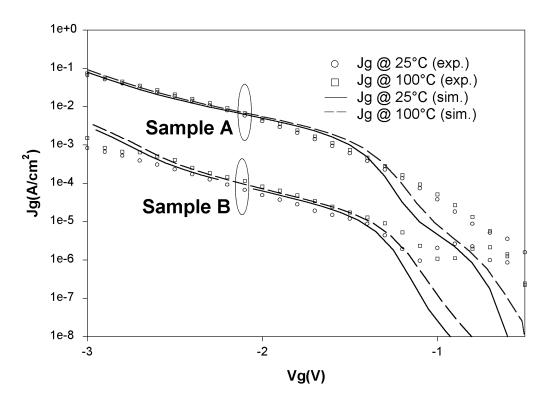

| 2.9  | Comparison of simulation and experiment for gate currents at different temperatures for samples A and B                                                                                                                                    | 28 |

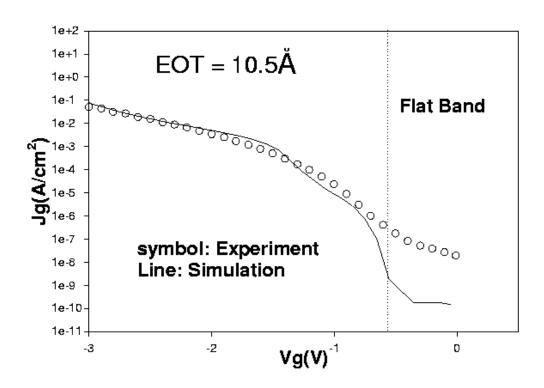

| 2.10 | Comparison of gate current simulation with experimental data for a $\rm TaN/HfO_2/p\text{-}Si$ capacitor                                                                                                                                   | 30 |

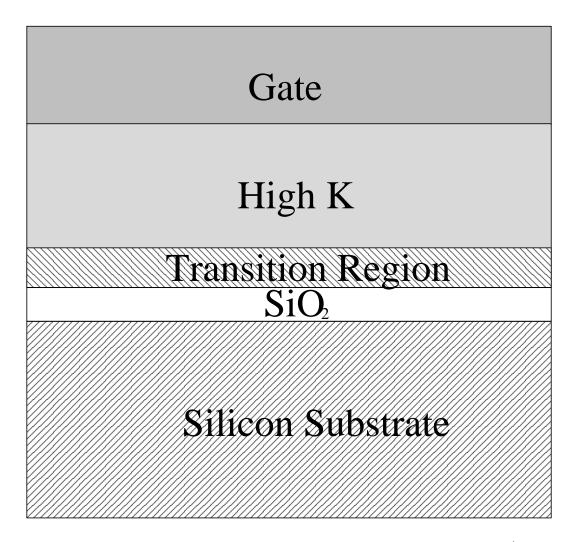

| 3.1  | Stacked gate dielectric structure that consists of Gate/High- $K/Transition \ Region/SiO_2/Si.$                                                                                                                                            | 35 |

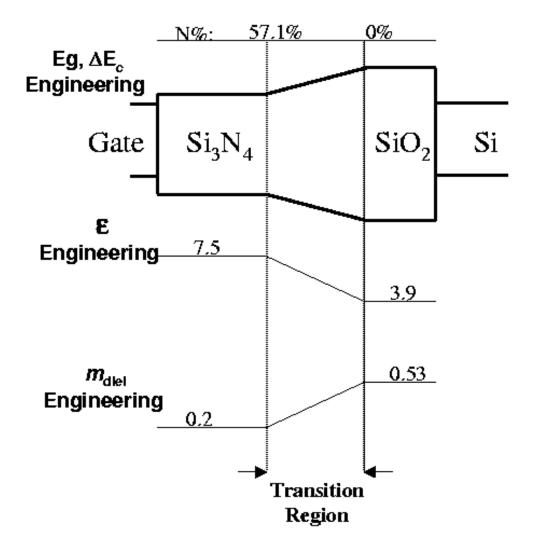

| 3.2 | Profiles of physical parameters in a Si <sub>3</sub> N <sub>4</sub> /SiO <sub>2</sub> stack. $\varepsilon$ , $E_g$ , $\Delta E_c$ , and $m_{\rm diel} (= m_c = m_v)$ are considered to affect gate capacitance and gate current. Values assumed for Si <sub>3</sub> N <sub>4</sub> are only for qualitative study                                                                                                                                                                                                                                                                 | 38 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

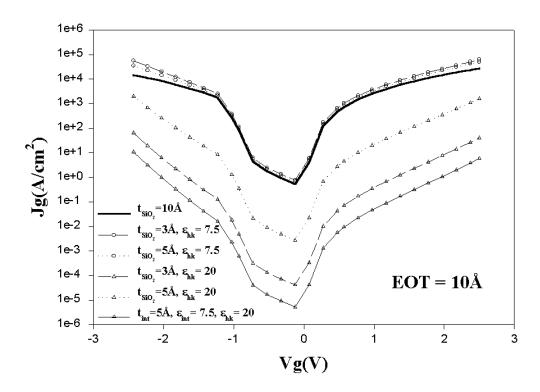

| 3.3 | Effects of interfacial layer in stacked gate dielectrics without a transition region on gate currents. EOT= $10\text{Å}$ is maintained                                                                                                                                                                                                                                                                                                                                                                                                                                            | 39 |

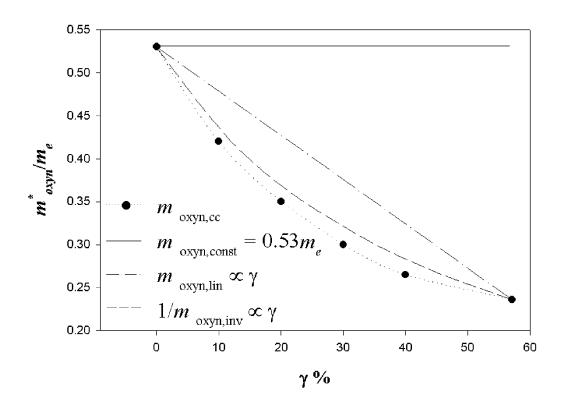

| 3.4 | $m_{\rm oxyn,cc}$ vs. $\gamma$ . $m_{\rm oxyn,cc}$ are chosen to provide similar gate currents $(10^{-1}{\rm A/cm^2})$ at $V_g \sim 1{\rm V}$ in simulation of different nitrogen atomic concentrations $(\gamma\%)$ in oxynitride. $m_{\rm oxyn,lin}$ and $m_{\rm oxyn,inv}$ represent linear variation of the mass and inverse of the mass, respectively, in relation with $\gamma$ between the endpoints of $m_{\rm oxyn,cc}$ . $m_{\rm oxyn,const}$ represents nitrogen-independent band-edge mass. EOT=20Å is maintained. Single-layer oxynitride gate dielectric is assumed | 45 |

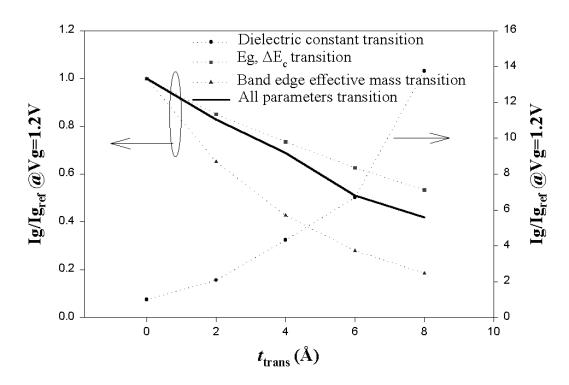

| 3.5 | Individual and collective effects of linear variation of each parameter in the transition layer on gate currents for $\mathrm{Si}_3\mathrm{N}_4/\mathrm{SiO}_2$ stacks, benchmarked by the transition layer thickness. The reference is gate current at $V_g=1.2V$ of a $\mathrm{Si}_3\mathrm{N}_4/\mathrm{SiO}_2$ stack without a transition layer. EOT=10Å is maintained                                                                                                                                                                                                        | 47 |

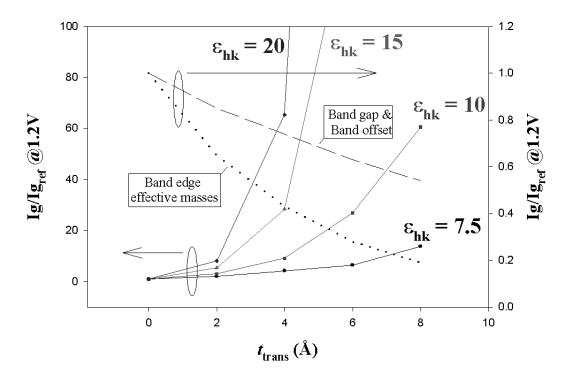

| 3.6 | Individual and collective effects of linear variation of each parameter in the transition layer on gate currents for High-K/SiO <sub>2</sub> stacks, benchmarked by the transition layer thickness. The reference is gate current at $V_g = 1.2V$ of a Si <sub>3</sub> N <sub>4</sub> /SiO <sub>2</sub> stack without a transition layer. EOT=10Å is maintained                                                                                                                                                                                                                   | 49 |

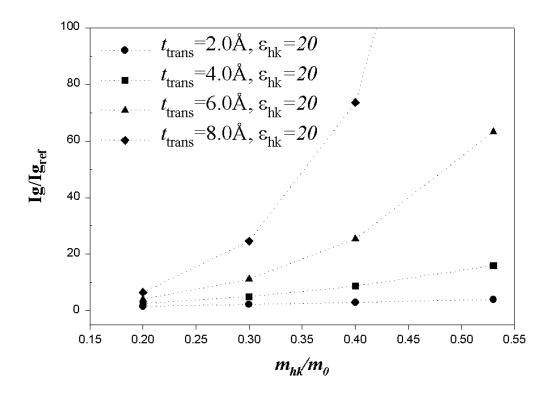

| 3.7 | Band-edge effective masses of high-K layer on effects of the transition region. The more insulating (higher $m_{\rm diel}$ ) high-K layer results in more importance of the transition layer. EOT=10Å is maintained.                                                                                                                                                                                                                                                                                                                                                              | 50 |

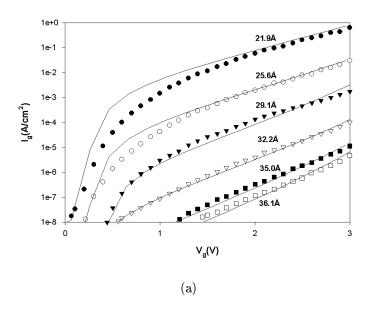

| 4.1 | Gate current simulation compared with experimental data for (a) n+poly/SiO <sub>2</sub> / p-Si MOSFETs and (b) p+poly/SiO <sub>2</sub> / n-Si MOSCAPs. The experimental data are from [33]. The thicknesses shown in the figures are used in simulation as reported in [33]                                                                                                                                                                                                                                                                                                       | 58 |

| 4.2 | Gate capacitance simulation compared with experimental data for a $n^+$ gate $SiO_2$ NMOSFETs fabricated by IBM (1.8V and 0.20- $\mu$ m technology) [33]. The $SiO_2$ thickness was reported 35.1Å, which is used in simulation in this work                                                                                                                                                                                                                                                                                                                                      | 59 |

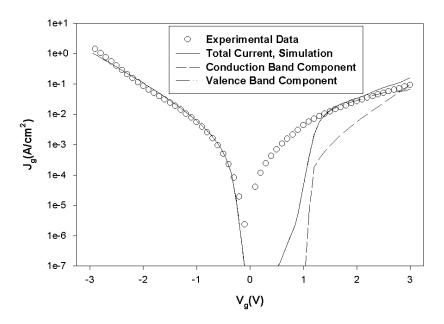

| 4.3 | Gate current simulation compared with experiment in both the inversion and accumulation for a SiO <sub>2</sub> poly-PMOSFET. $t_{ox} \sim$                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|     | 20Å                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 61 |

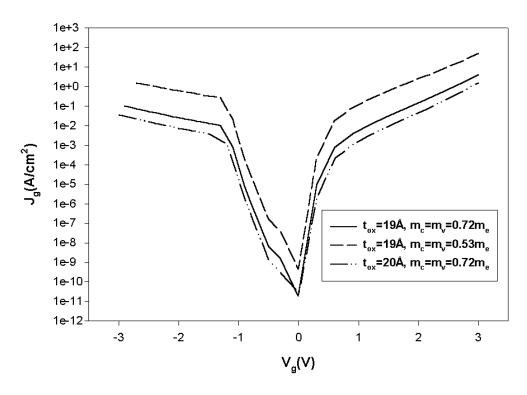

| 4.4 | Comparison of gate current simulation for small changes in $t_{ox}$ , $m_c$ and $m_v$ with $m_c/m_v = 1$ . The simulated device is a SiO <sub>2</sub> n <sup>+</sup> poly NMOSFET                                                                                                                     | 62 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

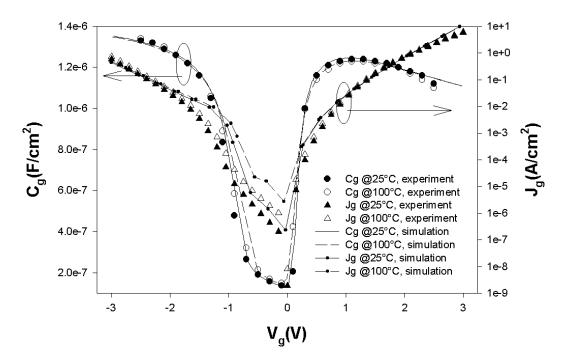

| 4.5 | Comparison of $C_g$ , $I_g$ - $V_g$ at different temperatures for a SiO <sub>2</sub> poly NMOSFET (sample I). EOT was found to be 20.0Åfrom $C_g$ - $V_g$ simulation                                                                                                                                  | 65 |

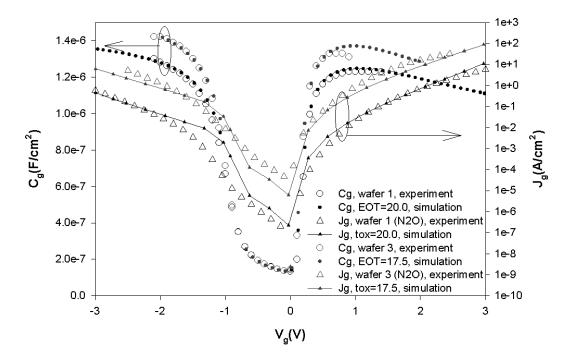

| 4.6 | Comparison of $C_g$ , $I_g$ - $V_g$ simulation with experiment for SiO <sub>2</sub> poly NMOSFETs with different thicknesses. EOTs of sample I and II are 20Å and 17.5Å, respectively, which were obtained from $C_g$ - $V_g$ simulation. The temperatures in experiment and simulation are both 25°C | 66 |

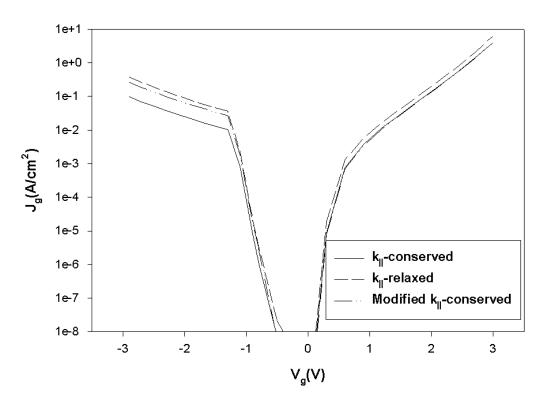

| 4.7 | Gate currents are calculated with three assumptions: $k_{\parallel}$ -conserved, $k_{\parallel}$ -relaxed, and modified $k_{\parallel}$ -conserved. The simulated device is a $n^+$ poly SiO <sub>2</sub> NMOSFET fabricated on Si(100) with SiO <sub>2</sub> thickness of 19Å                        | 69 |

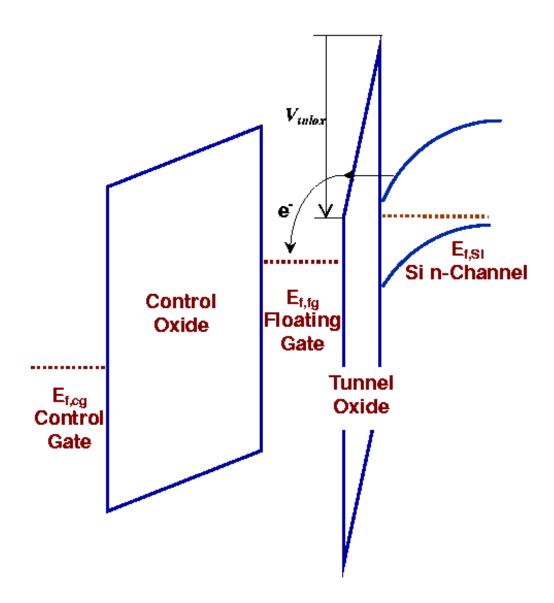

| 5.1 | Device structure of the modeled floating gate nonvolatile memory device                                                                                                                                                                                                                               | 77 |

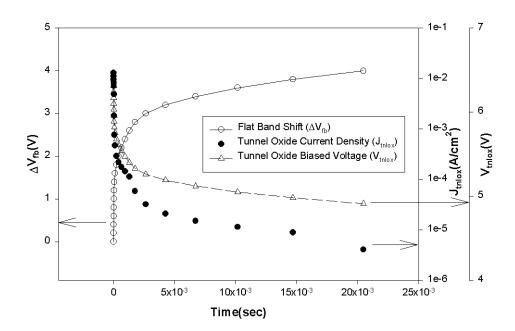

| 5.2 | Time-dependent characteristics of a floating gate nonvolatile memory device biased at a constant $V_{cg} = 18V$                                                                                                                                                                                       | 79 |

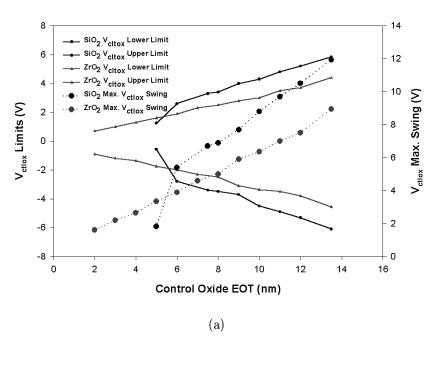

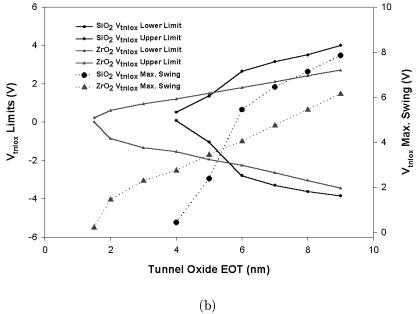

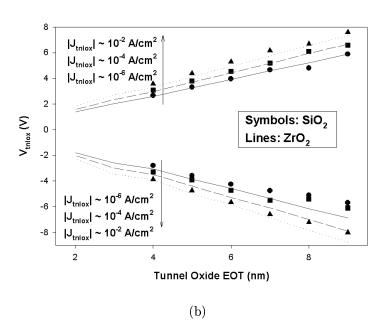

| 5.3 | Retention scaling trend for $SiO_2$ and $ZrO_2$ as (a) control oxide and (b) tunnel oxide                                                                                                                                                                                                             | 81 |

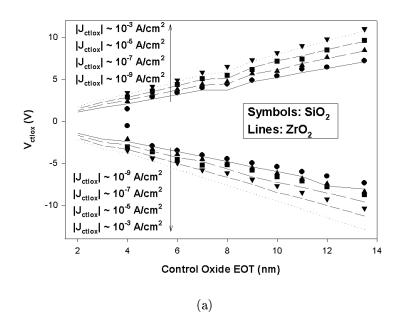

| 5.4 | Write/Erase scaling trend for $SiO_2$ and $ZrO_2$ as (a) control oxide and (b) tunnel oxide                                                                                                                                                                                                           | 83 |

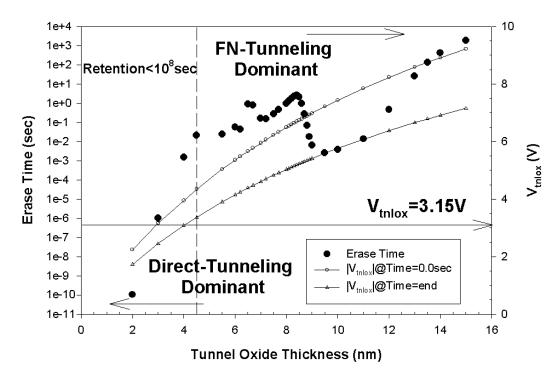

| 5.5 | Erase time vs. Tunnel oxide thickness.                                                                                                                                                                                                                                                                | 84 |

### Chapter 1

### Introduction

The purpose of this research is to study the leakage current through high-dielectric-constant (high-K) stacked gate dielectric structures. The intent is to establish a general physical model for Metal-Oxide-Silicon (MOS) transistor device design issues. Through simulation and experimental analysis, the device behavior will be studied.

#### 1.1 MOSFET Scaling

Continued MOSFET scaling is the primary driving force that boosts the semiconductor industry [38, 47, 54]. As paced by Moore's Law, consistent improvements in the density, power, and performance have been achieved for more than 30 years. Such a successful scaling mandates that the following rule be satisfied: while the device performance is improved as a result of a shorter channel length, the characteristics of the long-channel MOSFETs such as low off-state leakage currents and good sub-threshold characteristics must be retained [1, 5, 40].

Regardless of the challenges in fabrication, adverse device behavior which is not seen in long channel devices, generally regarded as short channel effects (SCE), require careful consideration of the device design. Concerns of the device reliability should also be considered. Two of these are hot carrier effects and gate leakage currents. The hot carrier effects degrade the device performance and shorten the device operating lifetime; gate leakage currents can cause the gate dielectric breakdown and increase the power consumption rate. With the demands of more-functionality and faster microprocessors and the application of mobile appliances, power consumption becomes a major concern for both device engineering and circuit design. Thus, the ability to overcome current physical technology limits as well as tradeoffs in circuit design will determine if MOS transistors can continue to be scaled down in the future.

To suppress short channel effects and to obtain maximum performance MOSFETs concurrently, one needs to take into account the tradeoffs among critical parameters such as critical channel length  $L_c$ , gate dielectric thickness  $t_{ox}$ , channel doping  $N_a$ , and junction depth  $X_j$  [1, 5, 40]. One scaling formula suggested as a design rule is [40],

$$L_c = 2.2\mu m^{-2} \left(\frac{\delta V_t}{\delta V_{ds}}\right)^{-0.37} (t_{ox} + 0.012\mu m) (W_{sd} + 0.15\mu m) (X_j + 2.9\mu m)$$

(1.1)

where  $\delta V_t/\delta V_{ds}$ , representing the drain-induced barrier lowering (DIBL) effect, is obtained from the parallel shift of the  $\log I_d$  vs.  $V_{gs}$  curves at a given drain current level;  $W_{sd}$  is the sum of the depletion widths of the source and drain which is a function of channel doping,  $N_a$ ; the gate dielectric is silicon dioxide.

The success of scaling down MOSFETs has been achieved by aggressive engineering of the source/drain and well regions and decreasing gate oxide thickness as well as the development of new lithography tools, masks, photoresist materials and critical dimension etch processes. However, despite these advances in crucial process technologies and the resultant smaller feature sizes, it has become clear that the scaled device performance has been compromised [1]. The reason is that the traditional materials, silicon (Si), silicon dioxide (SiO<sub>2</sub>), and polysilicon (Poly-Si) have been pushed to their fundamental limits. Further device scaling thus requires new materials and device structures.

#### 1.2 SiO<sub>2</sub> Scaling and its Challenges

Traditionally, SiO<sub>2</sub> has been used as the gate dielectric due to its process advantages and good interfacial properties with Si [2, 16, 29, 30]. With increasing channel doping concentration to suppress short channel effects, the SiO<sub>2</sub> thickness has been reduced, which results in a larger gate capacitance, to maintain gate control over the channel. Large gate capacitance is needed to invert the silicon surface to a sufficient sheet charge density to obtain the desired drive current for the given supply voltage. This requirement is further demanded for deep-sub-micron or even-smaller MOSFETs.

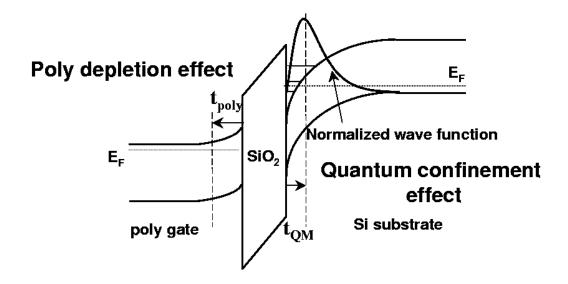

In the deep-submicron or smaller regime, quantum confinement effects of carriers in the channel and polysilicon depletion effects in the poly gate become more important. These effects cause the gate charge and inversion layer charge centroids be located further away from the  ${\rm SiO_2/poly\textsc{-}Si}$  and  ${\rm SiO_2/Si}$

interfaces, respectively. As a result, fewer carriers are induced in the channel to contribute to the drive current. In Intel's 0.25 or  $0.18\mu\text{m}$ -generation technology, the increase between the two centroids in addition to the SiO<sub>2</sub> physical thickness is  $\sim 7\text{Å}$  in inversion at the operating voltage. A SiO<sub>2</sub> physical thickness of 16Å thus is utilized to achieve an effective oxide thickness of 23Å in order to obtain sufficiently high drive currents required in such generations [48].

Higher gate capacitance may become crucial to obtain high drive currents for even smaller devices. It has been reported that the drive (drain) current is ultimately limited by the thermal injection current from the source into the channel [34]. The velocity overshoot in the channel does not extend such a limit. As a result, increasing the gate capacitance, i.e. increasing the carriers in the channel, becomes one important key to further scaling the MOS transistor to obtain better performance.

If the increased gate capacitance is solely obtained by decreasing the oxide thickness, in the year 2004 [1] the required oxide thickness is projected to be  $\sim 10\text{Å}$ , which is about three atomic layers. MOS devices fabricated with a SiO<sub>2</sub> physical thickness of 15Å have been reported [39]. However, concerns of their manufacturability for ULSI should be considered. Those include thickness variation, penetration of impurities from the gate through the gate dielectric, and the reliability and lifetimes of devices made with such thin films [6].

Another concern is the gate leakage current, which is the most detri-

Figure 1.1: Direct tunneling currents in a NMOSFET.

mental effect of further SiO<sub>2</sub> scaling and which poses the fundamental limit upon scaling SiO<sub>2</sub> thickness [21]. Figure 1.1 shows the band diagram of a MOS structure and the direct tunneling mechanism. Since the barrier height between conduction bands of Si and SiO<sub>2</sub> is finite,  $\sim 3.15 \,\mathrm{eV}$ , direct tunneling becomes non-negligible for SiO<sub>2</sub> thickness less than 30Å. In the region where direct tunneling dominates, the gate leakage current is exponentially dependent upon the SiO<sub>2</sub> thickness [36]. In fact, at a gate bias  $\sim 1 \,\mathrm{V}$ , the gate leakage current changes from  $\sim 10^{-5} \,\mathrm{A/cm^2}$  at SiO<sub>2</sub> thickness of 30Å to  $\sim 10^2 \,\mathrm{A/cm^2}$  at 15Å [21, 39].

#### 1.3 Alternative Gate Dielectric: High-K Dielectric Stack

The capacitance is proportional to the dielectric constant and inversely proportional to the thickness of a thin film. Thus, by using high-K materials as the gate dielectric, the required large gate capacitance can still be obtained while the direct tunneling current can be reduced as a result of the greater physical thickness. For a given equivalent oxide thickness (EOT), the required physical thickness of the high-K film is

$$t_{\rm hk} = {\rm EOT} \cdot \frac{\varepsilon_{\rm hk}}{\varepsilon_{\rm ox}},$$

(1.2)

where  $\varepsilon_{hk}$  and  $\varepsilon_{ox}$  are the dielectric constants of the high-K material and SiO<sub>2</sub>, respectively.

Many high-K materials have been suggested as alternative gate dielectrics. Metal oxides such as ZrO<sub>2</sub>, HfO<sub>2</sub>, Ta<sub>2</sub>O<sub>5</sub>, TiO<sub>2</sub>, Y<sub>2</sub>O<sub>3</sub>, and Al<sub>2</sub>O<sub>3</sub> [3,7,17,27,31,41], and ferroelectric materials such as BST (barium strontium titanate) [25] have been suggested as potential candidates. However, the challenge of integrating these materials with the current CMOS process still remains. These include thermal stability, compatibility with the gate, and interfacial properties with silicon. One important process issue is that a silicate layer is generally found between the high-K layer and the silicon substrate. This interfacial layer usually has a lower dielectric constant, and hence degrades the capacitance of the gate stack. Furthermore, the band gaps of these materials along with their band offsets with silicon are important material properties for reducing the gate leakage current. Unfortunately, smaller band

|                                 | Band Gap(eV) | $\varepsilon_{\infty}$ | Conduction Band Offset(eV) |

|---------------------------------|--------------|------------------------|----------------------------|

| $\mathrm{SiO}_2$                | 9            | 2.25                   | 3.5                        |

| $\mathrm{Si}_{3}\mathrm{N}_{4}$ | 5.3          | 4.1                    | 2.4                        |

| $Ta_2O_5$                       | 4.4          | 4.84                   | 0.3                        |

| $\mathrm{BaTiO}_3$              | 3.3          | 6.1                    | -0.1                       |

| $\mathrm{BaZrO_3}$              | 5.3          | 4                      | 0.8                        |

| ${ m TiO_2}$                    | 3.05         | 7.8                    | 0.05                       |

| $ m ZrO_2$                      | 5.8          | 4.8                    | 1.4                        |

| $\mathrm{HfO}_{2}$              | 6            | 4                      | 1.5                        |

| $Al_2O_3$                       | 8.8          | 3.4                    | 2.8                        |

| $Y_2O_3$                        | 6            | 4.4                    | 2.3                        |

| $\mathrm{La_2O_3}$              | 6            | 4                      | 2.3                        |

| $ZrSiO_4$                       | 6            | 3.8                    | 1.5                        |

| $SrBi_2Ta_2O_9$                 | 4.1          | 5.3                    | 0                          |

Table 1.1: Experimental values of conduction band offsets of several high K materials with Si, obtained by Robertson et al [43].  $\varepsilon_{\infty}$  is obtained as the square root of the refractive index.

gaps are usually observed in materials with higher dielectric constants [7]. This generally indirectly implies that lower potential barriers are expected for high-K materials, and thicker high-K films are required to reduce the gate current. Table 1.1 lists the band gaps and band offsets of several high K materials, which were obtained by a charge-neutrality-level method [43].

The requirement of a greater physical thickness has another impact on the MOSFET electrical characteristics. In parallel-plate capacitor theory, as the ratio of the distance between the plates to the length or width of the plates becomes large, fringing fields can no longer be neglected. With this high fringing field, the short channel effects will be aggravated due to the thick high-K film [22]. Thus tradeoffs between the gate leakage current and

short channel effects are required in designing next-generation MOSFETs if a higher-K gate dielectric is used [22, 24].

#### 1.4 Scope and Organization

Low EOT (high gate capacitance) and gate currents are simultaneously pursued in device design. However, compromises are required because electrical property trends of high-K materials do not favor such a pursuit. Through simulation, optimum device design can be achieved with low cost and short technology development cycle times.

To achieve such a goal, simultaneous matching of gate capacitance and current simulation with experiment is a key. In this work, an energy-dispersion-based self-consistent gate capacitance and current model will be first established and applied to study gate capacitance and current behavior of ZrO<sub>2</sub> devices (Chapter 2). Dielectric stack engineering is explored by considering parameters to vary the energy dispersion; thus, tradeoffs between the EOT and gate current is qualitatively studied (Chapter 3). Through integrated simulation and experimental analysis, the gate capacitance-current behavior will be studied. Device structure parameters will be extracted and compared with those values obtained by other methods (Chapter 4). Using the established gate capacitance and current model, a trend study on scaling the control and tunnel oxide in floating-gate nonvolatile devices will be performed (Chapter 5). Time-dependent characteristics for write, erase, and retention voltages are also modeled. Finally, conclusion swill be drawn in Chapter 6.

### Chapter 2

## Fundamental Issues on High-K Gate Capacitance and Current Modeling

A voltage- and temperature-dependent gate capacitance and current model is presented and applied to study ZrO<sub>2</sub> NMOSCAPs to illustrate the fundamental issues regarding the high-K gate stack structures.

#### 2.1 Introduction

Gate capacitance has been used for extracting the EOT [32, 42, 55], but the capacitance-voltage behavior should be considered concurrently with current-voltage calculation. The charge redistribution in the Gate-Dielectric-Silicon structure must be determined self-consistently by solving the Poisson-Schrodinger equations. The gate capacitance provides an experimental probe of the charge distribution at different gate voltages, and this is key to modeling the gate current. Temperature-dependence study of gate currents and gate capacitance of MOS capacitors with SiO<sub>2</sub> shows this correlation: the temperature-dependent region of the gate capacitance, which is near the flatband, is the same as that of the gate current, (Figure 4.5). Such temperature dependence is attributed to temperature dependence of the charge distribu-

tion or "supply function" instead of the temperature-dependence of the carrier transport in the SiO<sub>2</sub>. In this work, the *simultaneous* agreement of gate capacitance and gate current simulation with experiment has been obtained.

High-K materials generally have smaller band gaps and smaller band offsets with silicon than SiO<sub>2</sub> [7,9]. In addition to direct tunneling, Fowler-Nordheim (FN) tunneling can be important because of the smaller band offsets. The thermionic emission also needs to be considered for materials with extremely small band offsets and for transistors in which hot carriers are of concern. Gate currents from the silicon conduction band and valence band may be non-negligible at the same time. Furthermore, an interfacial layer is generally found between the high-K layer and the silicon substrate. These all impose difficulties in terms of understanding the experimental gate currents.

With increasing normal fields as a result of high doping concentrations and reduced EOTs, quantum confinement effects can no longer be neglected [13, 32, 42, 55]. Based on the energy-dispersion (E versus k) in different regions of the Gate-Dielectric-Silicon system, a gate current model is established to consider quantum confinement effects in the silicon channel, direct, FN tunneling, and thermionic emission gate currents. Such a gate current model is applied to the inversion and accumulation regions and both the conduction and valence band components [12].

#### 2.2 Models

The independent particle approach [19] is adopted to model the tunneling currents through the gate dielectric. If the energy dispersion relation in each region is available, the tunneling probability is obtained by a WKB method. In the originally proposed approach, the wave number vector parallel to region interfaces,  $k_{||}$ , is required to be conserved. However, well-known inconsistencies between the assumption and experiment are found between gate currents in SiO<sub>2</sub>-MOS devices fabricated on Si(110) and Si(111) [51], and this issue has not been resolved. In this work, simultaneous agreement of gate current simulation with experiment in inversion and accumulation is achieved for SiO<sub>2</sub> devices fabricated on Si(100) with  $k_{||}$  conserved.

A physical picture of this model can be described in terms of electrons tunneling from the silicon substrate to the gate, (Figure 2.1, 2.2). The incident component of the electron wave function, subject to the band structure,  $(E, k_x, k_y, k_z)$ , tunnels through the barrier and contributes to the transmitted currents. The energy-dispersion relation in the dielectric bandgap and available states in the gate determine the transmission probability. The continuity of electron flux allows the gate-injected electron current to be calculated by the transmission of electrons into the silicon at silicon-dielectric interface.

#### 2.2.1 Energy Dispersion

The carrier states in the silicon channel are roughly divided into bound states and unbound states. Bound states are quantized states inside the quan-

Figure 2.1: Gate current model band diagram of a Gate-Dielectric-Silicon system being biased in the inversion region. Direct, Fowler-Nordheim tunneling, and thermionic emission gate currents are simultaneously considered.

Figure 2.2: Gate capacitance model band diagram of a Gate-Dielectric-Silicon system being biased in the inversion region.

tum well formed by the silicon band edge. Subband structures and envelope functions are obtained by solving the Schrodinger equation in k-space using a full-band formalism [23, 49]. Those states outside the quantum well are approximated as free and unbound, and the energy-dispersion at the silicon-dielectric interface is approximated by the bulk-silicon band structure. The same charge distribution and subband structures in the silicon channel are used both for gate capacitance and gate current calculation.

The apparent energy dispersion "seen" by the tunneling electron in the dielectric band gap is approximated by Franz's two-band model [14],

$$\frac{1}{k^2} = \frac{\hbar^2}{2m_c(E - E_c)} + \frac{\hbar^2}{2m_v(E_v - E)},\tag{2.1}$$

where E is the total energy of the electron,  $m_c$  and  $m_v$  are band-edge effective

masses for the conduction and valence bands, respectively, of the dielectric, and  $E_c$  and  $E_v$  are the energies of the respective band edges. Such dispersion relation has previously been shown to be effective approximation for conventional oxides [35, 37].  $m_c$  and  $m_v$  are unknown parameters to be extracted by comparing gate current simulation with experiment.

#### 2.2.2 Gate Current Calculation

The tunneling probability,  $T(E, k_{||})$ , through the dielectric is calculated by the WKB method [26] when  $k_z^2 < 0$ ,

$$-\ln T(E, k_{||}) = \int_{\text{dielectric}} |k_z| \, dz, \tag{2.2}$$

with

$$k_z^2 = k^2 - k_{||}^2, (2.3)$$

where  $k^2$  is calculated from Franz dispersion, and  $k_{||}$ -conservation is applied.

The total energy E is used, thus direct, FN tunneling, and thermionic emission are considered simultaneously:

- $\bullet\,$  Direct tunneling:  $k_z^2<0$  across the whole dielectric

- FN tunneling:  $k_z^2$  passes through 0 within the dielectric.

- $\bullet\,$  Thermionic emission:  $k_z^2>0$  across the whole dielectric

These mechanisms are all considered elastic as the total energy and  $k_{||}$  are conserved during transport through the dielectric. The image force is lower in

higher-K materials and reduced by the quantum mechanical repulsion of both bound and unbound carriers from the interface. Thus, its effect on barrier lowering is not considered.

Finally, the total gate current density,  $J_g$ , is calculated as

$$J_g = J_{\text{Si-conduction}} + J_{\text{Si-valence}}, \tag{2.4}$$

where  $J_{\text{Si-conduction}}$  is from the conduction-band longitudinal valleys. With  $k_{||}$ conservation, the effective barrier for transverse valleys is higher and tunneling

from them is negligible.

Each component  $J_i$ , where i designates the band, is calculated separately for unbound states and bound states. For unbound states in the conduction band

$$J_{i,\text{unbound}} = \frac{2q}{(2\pi)^3} \int_{E_{z,\text{min,c}}}^{\infty} dE_z \int_{k_{||}=k_{||,min}}^{\infty} dk_{||}^2 T(E,k_{||}) (f_{FD,\text{gate}} - f_{FD,\text{Si}}), \quad (2.5)$$

and for unbound states in the valence band

$$J_{i,\text{unbound}} = \frac{2q}{(2\pi)^3} \int_{-\infty}^{E_{z,\text{max,v}}} dE_z \int_{k_{||}=(0,0)}^{\infty} dk_{||}^2 T(E,k_{||}) (f_{FD,\text{gate}} - f_{FD,\text{Si}}), \quad (2.6)$$

where  $f_{FD,gate}$  and  $f_{FD,Si}$  are the Fermi-Dirac distribution functions for the gate and silicon substrate, respectively;  $E_{z,\min,c}(E_{z,\max,v})$  is the lowest (highest) unbound state in the conduction (valence) band; q is the charge of electron. While for bound states,

$$J_{i,\text{bound}} = \frac{2q}{(2\pi)^2} \sum_{\mu} \tau_{\mu}^{-1} \cdot \int_{k_{||}=k_{||,min}}^{\infty} dk_{||}^2 T(E, k_{||}) (f_{FD,\text{gate}} - f_{FD,\text{Si}}), \qquad (2.7)$$

where  $\tau_{\mu}^{-1}$  is approximated by the surface impact frequency for a 2D subband  $\mu$  [46],

$$\tau_{\mu}^{-1} = \left(\frac{\partial I}{\partial E}\right)_{\text{subband }\mu}^{-1} \tag{2.8}$$

with the action integral between the classical turning points

$$I = \oint k_z^{(\mu)} dz, \tag{2.9}$$

and

$$k_z^{(\mu)}(z) = \frac{1}{\hbar} \sqrt{2m_z(E_\mu - E_{\text{band min.}}(z))},$$

(2.10)

where the contour integral is around the quantum well formed in the channel;  $E_{\mu}$  is the minimum energy of  $\mu^{\text{th}}$  subband,  $E_{\text{band min}}$  the band edge in which the subbands formed, and  $m_z$  the effective mass along the tunneling direction z.

$m_z=0.2m_e$  and  $m_z=0.9m_e$  are used for the conduction-band longitudinal and transverse valleys, respectively, where  $m_e$  is the free electron mass. Because the effective mass approximation is not very accurate for the valence band,  $m_z$  then is treated as a subband-independent adjustable parameter. From comparison of gate current simulation with experiment for a SiO<sub>2</sub>-PMOSFET in inversion, it is found that  $m_z=0.10\sim0.25m_e$  gives good agreement, (Figure 2.3). The SiO<sub>2</sub> thickness is extracted by comparison of  $C_g$ - $V_g$  simulation with experiment in accumulation, (Figure 2.3). Similar agreement is also achieved for a SiO<sub>2</sub>-NMOSFET, which was fabricated on Si(100), (Figure 2.4). The gate current simulation agrees well with experiment both in inversion and accumulation. The band gap and conduction band

Figure 2.3: Comparison of gate current and gate capacitance simulation with the experimental data for a SiO<sub>2</sub>-PMOSFET with EOT of  $\sim$ 20Å. Area =  $10^{-4} \rm cm^2$ .

Figure 2.4: Comparison of gate current and gate capacitance simulation with the experimental data for a SiO<sub>2</sub>-NMOSFET with EOT of  $\sim$ 20Å. Area =  $10^{-4} \mathrm{cm}^2$ .

offset with silicon of SiO<sub>2</sub> are 9.0eV and 3.15eV, respectively. The band-edge effective masses are adjustable parameters but remain the same for the silicon conduction band and valence band components, respectively, whether for substrate-injected or gate-injected currents. More about SiO<sub>2</sub> devices will be discussed in Chapter 4.

#### 2.2.3 Gate Current vs. Voltage/Temperature Behavior

Near the flat-band region,  $V_g \sim -0.8 \mathrm{V}$  in Figure 2.4, the quantum well is wide and shallow. Quantization effects due to the quantum well formed by the band edge become less important. Thus, a clear division between the bound and unbound states can cause significant errors in gate current calculation, which result in abnormal  $I_g$ - $V_g$  behavior in simulation. The error may originate from either the impact frequency or the supply of carriers. Below flat-band, only energetic carries can tunnel elastically, greatly reducing the calculated current. In practice, other mechanisms may dominate. A possible mechanism might be related to the interface states, which is not considered in the model. Near flat-band, the carrier density is much lower than in accumulation or inversion. The trapped charges can contribute appreciably to the total gate currents; empty traps may assist the carrier tunneling into/out of the silicon substrate. Contribution from the overlap regions with the source and drain may also be important in that region.

Gate current characteristics at different temperatures are shown in Figure 2.5. NMOSFETs with single-layer dielectric of 3.9 with different thicknesses and barrier heights are simulated. The flat band voltages of these devices are  $\sim -0.8 \text{V}$ . When the potential barrier of dielectric is high and/or thin, direct tunneling prevails. However, when the potential barrier is low, transition from direct to FN tunneling is seen. With the potential barrier of 1.0eV high and 40Å wide, such transition occurs around  $V_g = -2 \text{V}$  in accumulation and  $V_g = 0.8 \text{V}$  in inversion.

Figure 2.5: Simulated  $I_g$ -V $_g$  at 25°C and 125°C for n-channel MOSFETs with different dielectric thicknesses and conduction band offsets with silicon. Single layer of dielectric of dielectric constant of 3.9 is assumed in the devices.

More energetic carriers see a relatively small barrier. Therefore, the hotter the carrier distribution, the greater the tunneling. This field-assisted thermionic effect is particularly significant when the barrier is low and/or thick, (Figure 2.5). Polarity effects are also seen in the temperature dependence of gate current, which is stronger in accumulation than in inversion. Such effects are not due to the transport in the dielectric but the charge supply and asymmetry of the gate stack.

### 2.3 $ZrO_2$ and $HfO_2$ NMOSCAP $C_q, I_q$ - $V_q$ Analysis

Different materials such as  $ZrO_2$  and  $HfO_2$  have shown promise for transistor application [20, 28, 41]. Owing to the complex fabrication process of transistors, most study has been conducted on MOSCAPs. The uncertainty of the material properties, especially for the thin films, imposes another difficulty in terms of understanding the experimental results. In this work, through  $C_g$ - $V_g$  and  $I_g$ - $V_g$  simulations, the material properties of  $ZrO_2$ -NMOSCAPs are extracted in the accumulation region.

## **2.3.1** $C_g$ vs. $V_g$

Two samples of different thicknesses of  $\rm ZrO_2$  were fabricated, labeled as A and B. According to TEM analysis, an interfacial Zr-silicate layer exists between the  $\rm ZrO_2$ -layer and the silicon substrate as reported in [52]. The physical thickness of each layer is found as: for sample A,  $t_{\rm ZrO_2}=31\sim39{\rm \AA}$ , and  $t_{\rm int}=6\sim10{\rm \AA}$ ; for sample B,  $t_{\rm ZrO_2}=36\sim40{\rm \AA}$ , and  $t_{\rm int}=7\sim9{\rm \AA}$ , where  $t_{\rm ZrO_2}$  and  $t_{\rm int}$  are physical thicknesses of the  $\rm ZrO_2$  and interfacial silicate layers, respectively. Because of the thickness variation, the experimental data being analyzed for either sample were measured from the same device.

To analyze the devices,  $C_g$ - $V_g$  simulation is first compared with the experimental data to extract the related device structural parameters, (Figure 2.6). At this step, EOT is the only physical parameter that can be extracted and is required for the dielectric stack. The interface state effects are neglected. Effects of fixed charges are compensated by adjusting the metal work function

Figure 2.6: Comparison of  $C_g$ - $V_g$  simulation with the experimental data in accumulation for  $\text{ZrO}_2$ -NMOSCAPs with different dielectric thicknesses, samples A and B.

to fit the experimental data. For the fabrication process described above, it was found that the substrate doping concentration is  $5 \times 10^{15} \mathrm{cm}^{-3}$ , the metal work function is 4.50eV for sample A and 4.45eV for sample B, the EOT of sample A is 10.8Å, and 13.6Å for sample B. The difference of metal work functions indicates slightly different fixed charge densities at the dielectric-silicon interfaces for A and B. The flat-band voltages are  $\sim -0.55\mathrm{V}$  and and  $\sim -0.60\mathrm{V}$  for samples A and B, respectively.

If abrupt interfaces are assumed, the EOT of the dielectric stack can

be calculated by

$$EOT = t_{ZrO_2} \times \frac{\epsilon_{SiO_2}}{\epsilon_{ZrO_2}} + t_{int} \times \frac{\epsilon_{SiO_2}}{\epsilon_{int}}, \qquad (2.11)$$

where  $\epsilon_{SiO_2}$ ,  $\epsilon_{ZrO_2}$ , and  $\epsilon_{int}$  are dielectric constants of SiO<sub>2</sub>, ZrO<sub>2</sub>, and Zr-silicate, respectively;  $\epsilon_{SiO_2} = 3.9$ .

From ranges of dielectric-layer thicknesses, EOTs from  $C_g$ - $V_g$  simulation,  $\epsilon_{\rm ZrO_2}=20$ , and to satisfy Equation (2.11) for both samples A and B,  $\epsilon_{\rm int}\sim5.5$  is found. The physical thickness of each layer is determined as:  $t_{\rm ZrO_2}=33.6{\rm \AA}$  and  $t_{\rm int}=6.0{\rm \AA}$  for sample A, and  $t_{\rm ZrO_2}=38.5{\rm \AA}$  and  $t_{\rm int}=8.6{\rm \AA}$  for sample B. These values are within ranges obtained from TEM but are not the medium values. To satisfy Equation (2.11) with the medium values will result in negative  $\varepsilon_{\rm int}$  and small  $\varepsilon_{\rm ZrO_2}$  ( $\sim4.18$ ). With limited experimental information available, the above approximation is the most reasonable. These parameters, along with the ones obtained from  $C_g$ - $V_g$  simulation, are used later for gate current simulation.

### 2.3.2 $I_g$ vs. $V_g/$ Temperature

Temperature-dependence of gate current is shown in Figure 2.7. Sample A, with  $t_{\rm ZrO_2} + t_{\rm int} = 39.6 \text{Å}$ , shows temperature-independence in accumulation but temperature-dependence in inversion. Sample B, with  $t_{\rm ZrO_2} + t_{\rm int} = 47.1 \text{Å}$ , shows weak temperature-dependence in accumulation.

In principle, the temperature-dependence could be contributed from either the transport mechanism, or by the charge distribution in the system, or both. In an NMOSCAP, electrons in the conduction band are minority

Figure 2.7: Experimental gate current vs. voltage at different temperatures for (a) Sample A and (b) Sample B.

carriers in the silicon channel. Without a source/drain as external supply, its concentration cannot be maintained at the thermodynamic-equilibrium value. As the temperature is increased, substantially more minority carriers are available, and, as a result, the gate currents show strong temperature-dependence in inversion. This strong temperature dependence contrasts markedly to the much weak temperature dependence for the field-assisted thermionic current for accumulation shown in Figure 2.5, thus is attributed to the temperature-dependence of the charge distribution. The strong temperature-dependence in inversion also indicates that the gate current is primarily from the conduction band.

Yamaguchi et al reported that band gaps of  $ZrO_2$  and Zr-silicate layers are 5.7eV and 4.5eV, respectively, from XPS analysis for sputter-deposited films [52]. Using these values in Franz dispersion, the gate current simulation agrees well with experiment for both samples, (Figure 2.8). The conduction band offsets of  $ZrO_2$  and Zr-silicate are found as 1.45eV and 1.0eV, respectively. The band-edge effective masses are  $m_c = m_v = 0.35 m_e$  for both  $ZrO_2$  and Zr-silicate.

Yamaguchi assumed Frenkel-Poole conduction through the dielectric stack and reported the conduction band offsets with silicon of the ZrO<sub>2</sub> and Zr-silicate layers as 1.5eV and 1.0eV, respectively. For Frenkel-Poole conduction [15], the conducting electrons are thermally emitted out of the traps in the dielectric. The trapping potential barrier will be reduced if an electric field is applied. As a result, the current will be increased by a factor proportional

Figure 2.8: Comparison of gate current and gate capacitance simulations with the experimental data for samples A and B.

to  $\exp(\frac{\Delta E_i}{k_B T})$ , where  $k_B T$  is the thermal energy, and  $\Delta E_i$  is the decrease of the trapping potential barrier due to the electric field. The barrier is further decreased if the electric field is increased. Thus, stronger field/voltage dependence of current is to be expected at low temperatures. Such characteristic was not observed in the gate currents of ZrO<sub>2</sub>-NMOSCAPs in our experiments. We believe, therefore, the temperature dependence observed in sample B is not primarily attributed by the the Frenkel-Poole mechanism.

Although simulation and experiment agree quite well, it is not conclusively clear that direct tunneling or FN tunneling, which are the temperature-independent conductions being modeled in this work, is the primary transport mechanism. This is due to the uncertainties about the device structural information, especially those of the dielectric stack. Other temperature-insensitive or weakly dependent transport mechanisms such as trap-assisted tunneling remain possibilities.

Comparison between simulation and experiment of gate currents at different temperatures is shown in Figure 2.9. In simulation, the gate current of sample B has stronger temperature dependence than sample A, consistent with the model for thicker barriers, (Figure 2.5). However, the temperature dependence predicted by the model is weaker than experiment. Thus, some thermally assisting process(es) should be involved, but its influence is weak. Such thermal processes can either be related to the transport through the dielectric or the supply of carriers. If it is related to the transport, it should be weakly dependent on the electric field in the dielectric.

Figure 2.9: Comparison of simulation and experiment for gate currents at different temperatures for samples A and B.

At low gate voltages, oscillations of gate currents were observed near the flat-band and depletion region. Kinks in  $C_g$ - $V_g$  were also observed. These might be caused by the interface states between regions (Gate/Dielectric or Dielectric/Silicon). The high-density of interface states might significantly affect the gate capacitance and gate current by trapping or de-trapping the electrons in the absence of inversion or accumulation layers.

The  $I_g$ - $V_g$  characteristics from sample A were measured at 25°C before and after thermal and electrical stresses. Gate voltages from -3V to 3V were applied at temperatures of 25°C to 125°C. The measured gate current is similar to that of the fresh device, (Figure 2.7(a)). This implies good quality of the thin films and few charges are trapped or fresh traps are created within the dielectric stack. This is yet another piece of circumstantial evidence of the unimportance of Frenkel-Poole transport in these samples, at least in accumulation.

The comparison of gate current simulation with experiment for a TaN / HfO<sub>2</sub> / p-Si capacitor is shown in Figure 2.10. The simulation agrees well with experiment in accumulation. The EOT is  $\sim 10.5 \text{Å}$  obtained from  $C_g$ - $V_g$  simulation.  $E_g = 5.7 \text{eV}$ ,  $\Delta E_c = 1.6 \text{eV}$ , and  $m_c = m_v = 0.32 m_e$  are used in the Franz dispersion for the HfO<sub>2</sub> layer, and  $E_g = 4.5 \text{eV}$ ,  $\Delta E_c = 1.2 \text{eV}$ , and  $m_c = m_v = 0.5 m_e$  for the interfacial layer.

Figure 2.10: Comparison of gate current simulation with experimental data for a TaN/HfO<sub>2</sub>/p-Si capacitor.

## 2.4 Summary and Conclusions

A gate current model has been developed taking into account the quantum confinement effects in the silicon channel, direct and Fowler-Nordheim tunneling, and thermionic emission transport through the gate dielectric. Both gate- and substrate-injected currents are modeled for the silicon conduction- and valence-band components. Subject to the energy dispersion relation in each region of the Gate-Dielectric-Silicon system and available carriers and empty states in either side of the dielectric, the gate current is determined. The energy dispersion in the dielectric band gap is approximated by Franz dispersion. The subband structures and carrier distribution in energy and position in the silicon channel are obtained by solving the Schrodinger and Poisson equations self-consistently, both for gate capacitance and gate current calculations. A self-consistent  $C_g, I_g - V_g$  model thus is established. This model was validated using SiO<sub>2</sub> dielectric devices, and good agreement with experiment is achieved.

Device structure information of  $\text{ZrO}_2$  NMOSCAPs is extracted in accumulation using  $C_g$ - $V_g$  and  $I_g$ - $V_g$  simulation. The simulation agrees well with the experiment for different thicknesses of dielectric stack, using consistent parameters. The extracted band gaps and band offsets with silicon are comparable with those that have been reported. The gate current simulation of a  $\text{HfO}_2$  NMOSCAP also agrees well with the experiment.

Characteristics of gate current transport mechanism were studied for ZrO<sub>2</sub> NMOSCAPs. The temperature-dependence study shows that the gate

current is primarily contributed from the silicon conduction band, and tunneling is the most likely primary transport mechanism. However, other tunneling processes such as trap-assisted tunneling may be possible. More temperature-dependent processes are also not completely excluded, but their effects are weak. Interface states between different regions might significantly affect the gate capacitance and gate current at low voltages. Kinks in gate capacitance-voltage and oscillations of gate currents were observed. The gate current does not change much after the device is stressed electrically and thermally. This indicates good quality of the film and few charges or traps created in the dielectric stack as a result of the stress.

## Chapter 3

# Impact of Interfacial Layer and Transition Region on Gate Current: Its Tradeoff with Gate Capacitance

Stacked gate dielectrics are modeled with respect to the impact on leakage current of interfacial layers and transition regions. Using Franz model, the gate dielectric stack is characterized for considering gate capacitance and current performance. Low-EOT and low-gate-current regimes are explored theoretically using reasonable estimates guided by experimental data. Transition layer values of each parameter are qualitatively explored for oxynitride,  $Si_3N_4/SiO_2$ , and high-K stacks.

#### 3.1 Introduction

High-K materials such as  $HfO_2$  and  $ZrO_2$  ( $\varepsilon \sim 20$ ) are being considered as alternative gate dielectrics to  $SiO_2$  [28,41] to obtain the same EOT with a greater physical thickness. High gate capacitance or low EOT thus can be achieved simultaneously with low gate currents. High gate capacitance allows good gate control over the channel and increases the drive current; low gate currents reduce standby power dissipation for low-power application [1,21].

However, an interfacial layer generally found between the high-K layer and silicon substrate can have an opposing effect on this pursuit of low EOTs and low gate currents. This layer can be an unavoidable silicate layer created during processing [52] or an intentionally deposited/grown layer such as SiO<sub>2</sub> to improve interface properties with silicon [7]. Its dielectric constant is generally lower than that of the high-K layer; thus the EOT of the dielectric stack will be increased. On the other hand, since the band gap is generally inversely proportional to the dielectric constant [9], this layer can lower the gate current if its band offset with silicon is also proportionally larger.

Although an abrupt interface between the high-K layer and interfacial layer is usually assumed, a gradual transition may occur, (Figure 3.1). Yet its role in the gate dielectric stack has not been extensively explored. In this work, effects of the transition regions between the high-K layer and silicon substrate on the tradeoff between EOTs and gate currents are investigated theoretically, based on reasonable assumptions guided by experimental data.

A major hurdle to this study arises from uncertainties of material properties, especially those of the thin films, and the physical mechanisms that affect the gate capacitance and gate current. A self-consistent gate-capacitance and gate-current model which simultaneously considers quantum confinement effects in the silicon channel, direct tunneling, Fowler-Nordheim tunneling and thermionic emission gate currents has been reported and shows good simulation results compared with experiment [12]. Although uncertainties about the physical mechanisms involved still exist, a semi-quantitative investigation can

Figure 3.1: Stacked gate dielectric structure that consists of Gate/High-K/Transition  $\rm Region/SiO_2/Si.$

be derived from such work with additional physically-based assumptions.

It has been reported that there is a linear relation between the nitrogen/oxygen concentration ratio in the oxynitride, its dielectric constant, and the potential barrier for electrons in the silicon conduction band [18]. If such linear relation can also be assumed for other physical parameters, effects of the nitrogen concentration profile in the Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub> stack on the EOT and gate current can be theoretically studied. Furthermore, unless specified otherwise, we assume (1) gate dielectric stack consisting of High-K(or Si<sub>3</sub>N<sub>4</sub>)/Transition-Layer/SiO<sub>2</sub>, as shown in Figure 3.1, (2) linear variation of physical parameters in the transition layer, and (3) no free charges trapped in the dielectric stack in the quasi-static state for the purpose of simplicity and qualitative trend study.

In section 3.2, the gate-capacitance and gate-current models are described. The emphasis is on the characterization of the dielectric stack with the interfacial layer and transition region considered. The tradeoff between the EOT and gate current for oxynitride, Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub>, and high-K gate dielectric stacks is analyzed for NMOSFETs in section 3.3. Finally, conclusions are drawn in section 3.4.

## 3.2 Theory

The charge distribution in the Gate-Dielectric-Silicon system and E-k dispersion in the silicon channel are determined by solving Schrodinger and Poisson equations self-consistently subject to Fermi-Dirac statistics [23, 49].

The gate capacitance as well as EOT is obtained by assuming quasi-static-thermodynamic equilibrium in the system. Using the same charge distribution and E-k dispersion relation, the gate current can be obtained by a WKB-based method [12].

Linear transition of physical parameters is assumed between the high-K layer and interfacial layer in this work. Figure 3.2 shows assumed variations of those parameters that are considered to affect the gate capacitance and gate current for a Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub> stack. Conduction and valence band-edge effective masses of the dielectric are set equal to each other in this work for simplicity  $(m_{\rm diel} = m_c = m_v)$ .  $\varepsilon = 3.9$ ,  $m_{\rm diel} = 0.53 m_e$ ,  $E_g = 9.0 \, {\rm eV}$ , and  $\Delta E_c = 3.15 \, {\rm eV}$ are used for SiO<sub>2</sub>, where  $m_e$  is the free electron mass;  $\varepsilon = 7.5$ ,  $m_{\rm diel} = 0.2 m_e$ ,  $E_g=5.0 {

m eV}, {

m and} \ \Delta E_c=2.2 {

m eV}$  for Si<sub>3</sub>N<sub>4</sub>. For the high-K study,  $\varepsilon_{

m hk}=20$ is assumed and other values are assumed to be the same as for Si<sub>3</sub>N<sub>4</sub>, unless specified otherwise.  $m_{\rm diel}=0.2m_e$  is chosen to model less insulating high-K materials as compared with SiO<sub>2</sub> and only serves as a qualitative study. In fact, it will be seen from the oxynitride study that if  $m_{\rm diel} < 0.236 m_e$ , Si<sub>3</sub>N<sub>4</sub> would be unappealing as a gate dielectric. The gate current of a Si<sub>3</sub>N<sub>4</sub> device becomes higher than that of a SiO<sub>2</sub> device with the same EOT, as can also be concluded from Figure 3.3. Further discussion of Figure 3.3 is presented in section 3.3.

From Gauss' Law, assuming no free charges within the dielectric stack,

Figure 3.2: Profiles of physical parameters in a  $\mathrm{Si_3N_4/SiO_2}$  stack.  $\varepsilon$ ,  $E_g$ ,  $\Delta E_c$ , and  $m_{\mathrm{diel}} (= m_c = m_v)$  are considered to affect gate capacitance and gate current. Values assumed for  $\mathrm{Si_3N_4}$  are only for qualitative study.

Figure 3.3: Effects of interfacial layer in stacked gate dielectrics without a transition region on gate currents. EOT=10Å is maintained.

$\nabla \cdot \mathbf{D} = 0$ , the EOT of the dielectric stack is determined as

$$EOT = t_{SiO_2} + t_{hk} \cdot \frac{\varepsilon_{SiO_2}}{\varepsilon_{hk}} + \varepsilon_{SiO_2} \cdot \int_{trans} \frac{1}{\varepsilon_{trans}(z)} dz,$$

(3.1)

where  $t_{\rm SiO_2}$  and  $t_{\rm hk}$  are physical thicknesses of SiO<sub>2</sub> and high-K layers, respectively;  $\varepsilon_{\rm SiO_2}$ ,  $\varepsilon_{\rm hk}$ , and  $\varepsilon_{\rm trans}(z)$  are the dielectric constants of SiO<sub>2</sub>, high-K, and the transition layer, respectively; the integration is performed between transition region interfaces with SiO<sub>2</sub> and high-K; z is the normal direction to the silicon substrate along which the external electric field is applied. With the assumption of linear variation of the dielectric constant in the transition layer, the EOT of the dielectric stack becomes

$$EOT_{stack} = t_{SiO_2} + t_{hk} \cdot \frac{\varepsilon_{SiO_2}}{\varepsilon_{hk}} + t_{trans} \cdot \frac{\varepsilon_{SiO_2}}{\varepsilon_{av}},$$

(3.2)

where the final term represents contribution of the transition layer to the EOT with

$$\frac{1}{\varepsilon_{\rm av}} \equiv \frac{1}{\varepsilon_{\rm hk} - \varepsilon_{\rm SiO_2}} \cdot \ln \frac{\varepsilon_{\rm hk}}{\varepsilon_{\rm SiO_2}},\tag{3.3}$$

where  $t_{\rm trans}$  and  $\varepsilon_{\rm av}$  are the physical thickness and average dielectric constant of the transition region, respectively.

A key to the gate current modeling is the apparent energy dispersion (E-k) in the dielectric band gap seen by the tunneling electrons. The Franz 2-band dispersion model is used for approximating such energy dispersion

$$\frac{1}{k^2} = \frac{\hbar^2}{2m_c(E - E_c)} + \frac{\hbar^2}{2m_v(E_v - E)},\tag{3.4}$$

where E is the total energy of the electron,  $m_c$  and  $m_v$  are band-edge effective masses for the conduction and valence bands, respectively, of the dielectric, and  $E_c$  and  $E_v$  are the energies of the respective band edges [14]. The tunneling probability,  $T(E, k_{||})$ , through the dielectric is calculated by WKB when  $k_z^2 < 0$  [26],

$$-\ln T(E, k_{||}) = \int_{\text{dielectric}} |k_z| \, dz, \tag{3.5}$$

with

$$k_z^2 = k^2 - k_{||}^2, (3.6)$$

where  $k^2$  is calculated from the Franz dispersion with  $k_{||}$  being conserved through the dielectric stack and across region interfaces in the Gate-Dielectric-Silicon system.  $k_{||}$  is the wave vector component parallel to the region interfaces. The total energy, E, and parallel wave vector,  $k_{||}$ , are constant in Equation (3.5) when only elastic tunneling is considered. The band edge effective masses,  $m_c$ ,  $m_v$ , are intrinsic material properties.  $E_c$  and  $E_v$  profiles "seen" by the tunneling electrons are adjusted by both the external electric field and dielectric constant profiles in addition to the intrinsic band structure. As a result, the energy dispersion relation in the dielectric band gap determines the tunneling probability in a non-trivial way, especially when an external electric field is applied.

Within the context of the work presented here, the dielectric stack is characterized by the physical thickness of each layer  $(t_{hk}, t_{trans}, t_{SiO_2})$ , the

profiles of its dielectric constant  $(\varepsilon(z))$ , band gap  $(E_g(z))$ , band offset  $(\Delta E_c(z))$  with silicon, band-edge effective masses  $(m_{\rm diel}(z)(=m_c(z)=m_v(z)))$ , for the purpose of assessing capacitance/current vs. voltage performance. In the next section, tradeoffs between EOTs and gate currents for oxynitride,  ${\rm Si_3N_4/SiO_2}$  and high-K stacked gate dielectrics are studied.

### 3.3 Results and Discussion

Ma et al. [18] reported that the dielectric constant and potential barrier of oxynitride vary linearly with the oxygen/nitrogen concentration ratio. In their work, WKB and effective mass approximations (parabolic band structure of dielectric) were applied to study such dependence of tunneling gate currents. A nitrogen concentration independent effective mass was used. However, in this work, the potential effects of variation of the oxynitride effective mass, whatever that may be, are also explored.

Using a scheme similar to Ma's, the dielectric constants, conduction band offsets, and band gaps of the oxynitride are calculated, in the spirit of Vegard's law [50], as

$$\varepsilon_{\text{oxyn}}(\gamma) = 3.9 + 0.063\gamma, \tag{3.7}$$

$$E_{g,\text{oxyn}}(\gamma) = 9.0 - 0.07\gamma,$$

(3.8)

$$\Delta E_{c,\text{oxyn}}(\gamma) = 3.15 - 0.017\gamma,$$

(3.9)

where  $\gamma\%$  is the atomic nitrogen concentration in the oxynitride;  $\gamma=57.14$  and  $\gamma=0$  correspond to Si<sub>3</sub>N<sub>4</sub> and SiO<sub>2</sub>, respectively. According to Equation

(3.4), the parameter yet to be determined for the tunneling probability is the band-edge effective mass,  $m_{\text{oxyn}}(\gamma)$ . A direct approach is to find  $m_{\text{oxyn}}(\gamma)$  to fit the simulated gate current with experiments. However, this effort is impeded by experimental difficulties, especially the accurate determination of the composition of an ultra-thin film. Therefore, the actual values of  $m_{\text{oxyn}}(\gamma)$  remain unknown and the best we can do is to characterize the effects of possible  $m_{\text{oxyn}}(\gamma)$  variations.

For the above purpose, a reference band-edge effective mass  $m_{\text{oxyn,cc}}(\gamma)$ is chosen to provide similar gate currents ( $\sim~10^{-1} \rm A/cm^2~@\sim~1.0V)$  in simulation for NMOSFETs with the same EOT (20Å) but different nitrogen concentrations, (Figure 3.4). Thus, the variation in  $m_{\text{oxyn,cc}}(\gamma)$ , in turn, is that required to balance changes in the gate current due to changes in the other parameters—physical thickness, dielectric constant, band gap, and band offset—while holding the EOT constant. Variations in the actual mass from this reference mass,  $m_{\text{oxyn}}(\gamma) - m_{\text{oxyn,cc}}(\gamma)$ , will be indicative of an exponential reduction, if positive, or increase, if negative, of gate currents due to introduction of nitrogen for a given EOT. The device structure considered in simulation consists of a single-layer oxynitride gate dielectric. Assuming the same models for the gate and silicon substrate, with the same EOT, the tunneling probability is only affected by the thin film thickness and composition. Also shown for comparison in Figure 3.4 are  $m_{\text{oxyn,lin}}(\gamma)$  and  $m_{\text{oxyn,inv}}(\gamma)$  that represent a linear variation of the mass and the inverse of the mass, respectively, between the shown endpoints of  $m_{\text{oxyn,cc}}(\gamma)$ . Finally,  $m_{\text{oxyn,const}} = 0.53 m_e$  is also

included as a nitrogen-concentration-independent band-edge mass. It is seen that the constant-current  $m_{\text{oxyn,cc}}(\gamma)$  exhibits neither a linear nor an inverse relation with  $\gamma$ .

In the following study, multi-layer gate dielectric systems are considered.  $m_{\rm diel}=0.2m_e$  is assumed for both  ${\rm Si_3N_4}$  and high-K materials to manifest the less insulating alternative gate dielectrics for qualitative study. Such a value is lower than  $m_{\rm oxyn,cc}(57.14)=0.236$ , which corresponds to  ${\rm Si_3N_4}$ . As can be seen, it will result in higher gate current for a  ${\rm Si_3N_4(K=7.5)/SiO_2}$  device but lower gate current for a high-K(K=20)/SiO<sub>2</sub> device (Figure 3.3). Gate dielectric stacks consisting of  ${\rm Si_3N_4/SiO_2}$  are first studied.

The transition region between the  $\mathrm{Si}_3\mathrm{N}_4$  layer and  $\mathrm{SiO}_2$  layer consists of a oxynitride layer of variable nitrogen concentration. A continuous transition is assumed, i.e.  $\gamma=0$  at the oxynitride/ $\mathrm{SiO}_2$  interface and  $\gamma=57.14$  at the oxynitride/ $\mathrm{Si}_3\mathrm{N}_4$  interface. An accurate description of the effects of such a region requires knowledge of  $m_{\mathrm{oxyn}}(\gamma)$ . Linear variation of  $\gamma$  in the transition layer will lead to linear variation of  $\varepsilon$  and  $\Delta E_c$  [18], but not necessarily  $E_g$  and  $m_{\mathrm{diel}}$ . For simplicity and qualitatively theoretical study, linear variation of each parameter from the  $\mathrm{SiO}_2$ -layer to the  $\mathrm{Si}_3\mathrm{N}_4$ -layer is assumed. Gate currents of NMOSFETs with different transition layer thicknesses but the same EOT (10Å) and  $t_{\mathrm{SiO}_2}(3\text{Å})$  are studied in simulation. Effects for each parameter in terms of gate current as a function of the transition layer thickness are analyzed individually, using the profile of each parameter shown in Figure 3.2 with the other parameters held constant through the dielectric stack: