Copyright

By

Siddarth A. Krishnan

2005

The Dissertation Committee for Siddarth A. Krishnan certifies that this is the approved version of the following dissertation:

# CHARACTERIZATION AND RELIABILITY OF HFO<sub>2</sub> AND HFSION GATE DIELECTRICS WITH TIN METAL GATE

| Committee               |

|-------------------------|

|                         |

| Jack C. Lee, Supervisor |

|                         |

| Leonard F. Register     |

|                         |

| Dean P. Neikirk         |

|                         |

| Paul S. Ho              |

|                         |

## CHARACTERIZATION AND RELIABILITY OF HFO<sub>2</sub> AND HFSION GATE DIELECTRICS WITH TIN METAL GATE

by

#### Siddarth A. Krishnan, B.Tech., M.S.

#### **Dissertation**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

**Doctor of Philosophy**

The University of Texas at Austin

December 2005

#### Dedicated to

Jack Lee, whose faith in me surpassed my own

My parents, whose values they passed on to me in strength

and

Shobha, whose boundless encouragement inspired and motivated me

#### Acknowledgements

"For knowest thou what argument Thy like to thy neighbor's creed has lent, All are needed by each one; Nothing is fair or good alone"

- Ralph Waldo Emerson.

Several people have been enablers in the successful completion of this work. I would like to first acknowledge the contribution of my parents and sister, whose faith in me was unflinching, and encouragement, unending. For providing me every possible resource affordable to them, for educating me, for encouraging me at the successes along the way and standing by me at the failures, I stand indebted to them. At every faltering step, I drew inspiration from their completely selfless support.

I would also like to thank Professor Jack Lee, for his guidance and encouragement. He helped me identify my strengths and weaknesses and supported me through all the roadblocks that I had to overcome. His enthusiastic approach to not just research, but to also teaching undergraduate and graduate classes has stemmed a desire to teach in me. I cannot thank him enough for his decision to aid me through periods of uncertainty in my research.

A constant source of support, during my time in Austin has been my friend, Shobha Vasudevan, a doctoral student at UT. Without her, I can safely assert, I would not have been successful in my pursuit of this dream. A formidable intellectual with an indomitable will, her encouragement and wise guidance at various

٧

junctures helped me immeasurably. Her ever-cheerful and positive disposition has inspired in me the desire to cultivate that spirit in myself. She, along with Vinod provided the support framework for my tenure in Austin, making this professional endeavor a thoroughly enjoyable experience. I would like thank her for her invaluable counsel and her selfless support.

Another significant influence on my life has been my friend and erstwhile roommate, Vinod Viswanath, another doctoral student at UT. His determination and moral rectitude cannot help but inspire his acquaintances to emulate him, and I am no different. A selfless leader, he helped me formulate my goals in both my personal and professional bearings. I have learnt much from his expansive technical expertise at topics that varied from digital electronics to health and nutrition. I would also like to thank Kunal Punera, another erstwhile roommate of mine for being a great friend and for providing innumerable fun outings, along with some very insightful guidance on various technical issues.

I would like to thank Dr. Paul Kirsch, my manager at Sematech, for the technical guidance and support through my sojourn as an intern there. He has what I perceive to be great managerial qualities, combined with a very deep understanding of device and material physics and I am thankful that he let me draw upon his technical expertise. I would also like to thank Dr. Manuel Quevedo-Lopez, whose industry has contributed heavily to many of Sematech's deliverables. He helped fabricate many of the samples I utilized for my reliability measurements, without which this research would never have been completed. He has also been a great friend and mentor. Dr. Jeff Peterson, with

whom I collaborated on various projects, while at Sematech is another person I would like to offer thanks to. He helped me by providing samples and also in setting up experiments and analyzing the data. He mentored me through several projects, during which time I learnt much of what I was to apply to the bulk of my research.

I thank my committee members, Prof. Dean Neikirk, Prof. Frank Register and Prof. Paul Ho, for mentoring this dissertation.

I would also like to thank Dr. Rino Choi, Dr. Rusty Harris, Dr. Byoung Hun Lee, Dr. Gennadi Bersuker, Dr. Hong-Jyh Li, Dr. Chadwin Young and Dr. Sundar Gopalan for some very fruitful technical debates and insightful advice.

Kenneth Matthews, of ATDF, helped steepen my learning curve with various test equipment in the lab and continues to help set up experiments and I would like to express my gratitude to him. Several graduate students have helped in various capacities and I would like to acknowledge their contribution to this work: Changyoung, Sejong, Changwan, Injo, Hyoungsub, Feng are some of the current students. Amongst former graduate students in the group, I would like to thank Katsu, Young-Hee, Renee, Changseok and Hag-Ju.

I would also like to thank Prof. Bob Wallace and Gaurang Pant for providing assistance with XRD measurements.

## CHARACTERIZATION AND RELIABILITY OF HFO<sub>2</sub> AND HFSION GATE DIELECTRICS WITH TIN METAL GATE

Publication No.

Siddarth A. Krishnan, Ph.D.

The University of Texas at Austin

Supervisor: Jack C. Lee

"Give me a place to stand, and I will move the Earth" – Archimedes (235 B.C.)

Since the invention of the integrated circuit in 1958, the semiconductor industry has progressed at a fiery pace, through aggressive shrinking of the transistor channel length and associated device dimensions. The problems associated with such aggressive scaling are many-fold and have been dealt with by clever modifications or additions to existing process technology. However, as the 65 nm technology node nears production, the semiconductor industry hits a fundamental physical limitation: The thickness of the gate dielectric, Silicon Dioxide (SiO<sub>2</sub>) has been reduced to such an extent that the tunneling leakage current through the gate stack is reaching untenable levels. High permittivity dielectrics or high-κ dielectrics are being investigated to replace SiO<sub>2</sub> in order to preserve the capacitance while maintaining larger physical thickness to keep the leakage

current down. However, the introduction of high-κ materials into the conventional process flow is rendered difficult by various issues. It has been shown that gate stacks with high-κ materials have severely degraded mobility, while possessing large densities of charge traps. Additional concerns include the pinning of Fermi level at the midgap of the silicon bandgap, yielding undesirable threshold voltages, dielectric phase separation in ternary high-κ materials, high interface state density, low crystallization temperature and growth of a low-κ interfacial layer. We present a systematic study of the reliability aspects of hafnium based dielectrics with TiN gate electrode, and propose a robust and reliabile dielectric for introduction into CMOS product flow. Stress induced leakage current or SILC is studied in thick HfO<sub>2</sub> dielectrics with TiN gate electrode and it has been observed that significant low voltage SILC-like behavior is exhibited when nMOSFETs and pMOSFETs are stressed under positive biased stress. Such SILC behavior is also shown to be reversible when a negative voltage is applied after the stress, or if the devices are relaxed with a 0V bias. This reversible low-voltage SILC is attributed to electrons being trapped during the stress, which subsequently detrap during the I-V sweeps, leading to the appearance of SILC-like behavior. Mobility degradation in high-κ gate stacks is studied and it is proposed that the mobility degradation is a combination of remote coulomb scattering, due to fixed charges in the dielectric and phonon scattering. Thinning the high-κ dielectric down is offered as a solution to reduce the mobility degradation. Positive bias temperature instability is studied, and it is shown that the threshold voltage instability can be reduced to insignificant levels by reducing the thickness of the dielectric. However, the threshold voltage instability of thick high-k dielectrics remains problematic and will need to be solved before high- $\kappa$  gate stacks can be incorporated into low power applications. It is shown that incorporating nitrogen into the dielectric through plasma nitridation or thermal nitridation could be used to reduce charge trapping in thick dielectrics. Negative bias temperature instability is shown to be a combination of electron detrapping from the high- $\kappa$  layer and interface state creation due to hole injection into the interfacial layer. Although the interface state creation is made slightly worse by thinning the dielectric down, the threshold voltage shift is still less significant in thin dielectrics.

While the introduction of high- $\kappa$  dielectrics can now be considered viable, caution needs to applied while integrating metal gates into the product flow, for the problem of fermi-level pinning still remains unsolved. An outline of all the remaining issues with such high- $\kappa$  / metal gate gate stacks is presented at the end of this report.

#### Table of Contents

| CHAPTER 1                                                                                                                                                                                                                                                              | 1                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 1.1 Motivation for High-κ Dielectrics                                                                                                                                                                                                                                  | 1                          |

| <ul><li>1.2 High-κ Dielectrics: The Road So Far</li><li>1.2.1 "Higher-κ" Materials</li><li>1.2.2 Other high-κ materials</li></ul>                                                                                                                                      | 6<br>6<br>7                |

| 1.3 Hafnium Based Dielectrics with Metal Gates                                                                                                                                                                                                                         | 9                          |

| <ul> <li>1.4 High-κ dielectrics: Primary concerns</li> <li>1.4.1 Mobility Degradation</li> <li>1.4.2 Charge Trapping in high-κ gate stacks</li> <li>1.4.3 Negative Bias Temperature Instability</li> <li>1.4.4 Breakdown and Stress Induced Leakage Current</li> </ul> | 11<br>11<br>13<br>14<br>15 |

| 1.5 Outline                                                                                                                                                                                                                                                            | 16                         |

| 1.6 References                                                                                                                                                                                                                                                         | 18                         |

| CHAPTER 2                                                                                                                                                                                                                                                              | 26                         |

| 2.1 Introduction                                                                                                                                                                                                                                                       | 26                         |

| <ul><li>2.2 Experiment</li><li>2.2.1 Device Fabrication</li><li>2.2.2 Stress Set-up</li></ul>                                                                                                                                                                          | 26<br>26<br>28             |

| 2.3 Results and Discussion 2.3.1 nMOS: 2.3.2 pMOS:                                                                                                                                                                                                                     | 29<br>29<br>40             |

| 2.4 Conclusions                                                                                                                                                                                                                                                        | 42                         |

| 2.5 References:                                                                                                                                                                                                                                                        | 43                         |

| CHAPTER 3                                                                                                                                                                                                                                                              | 45                         |

| 3.1 Introduction                                                                                                                                                                                                                                                       | 45                         |

| 3.2 Experiment and Results                                                                                                                                                                                                                                             | 46                         |

| 3.2.1 Screening effect of Interfacial Oxides                                                                        | 46       |

|---------------------------------------------------------------------------------------------------------------------|----------|

| 3.3 Interface Effect on Mobility                                                                                    | 49       |

| <ul><li>3.4 Mobility Degradation Study</li><li>3.4.1 Mobility Vs Temperature: Effect of phonon Scattering</li></ul> | 49<br>49 |

| 3.5 Mobility Improvement Techniques                                                                                 | 56       |

| 3.6 Summary and Conclusions:                                                                                        | 57       |

| 3.7 References                                                                                                      | 59       |

| CHAPTER 4                                                                                                           | 61       |

| 4.1 Introduction                                                                                                    | 61       |

| 4.2 Sample Fabrication and Experiment                                                                               | 62       |

| 4.3 PBTI in HfSiON 4.3.1 Theoretical Analysis:                                                                      | 65<br>69 |

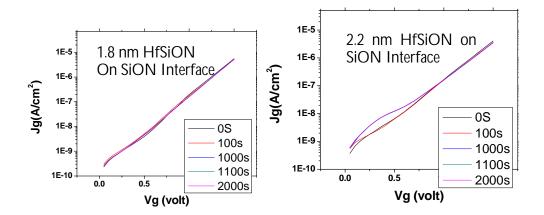

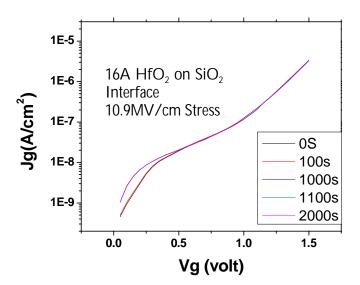

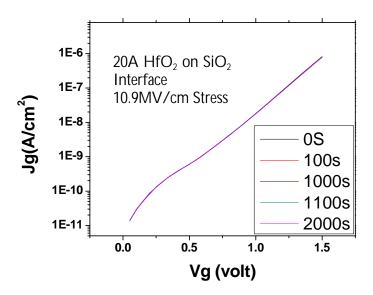

| 4.4 Stress Induced Leakage Current (SILC) in HfSiON                                                                 | 77       |

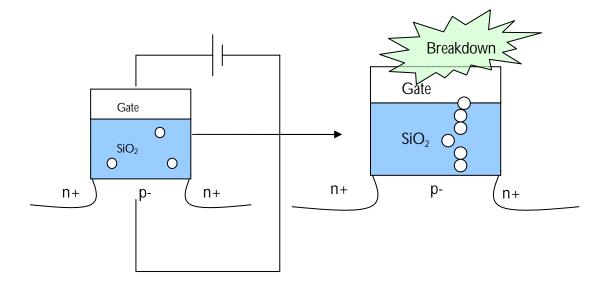

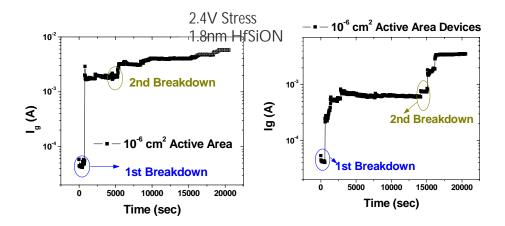

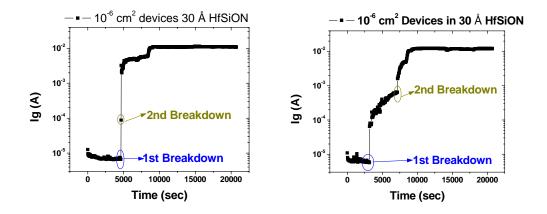

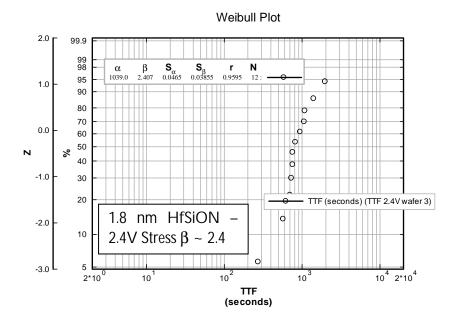

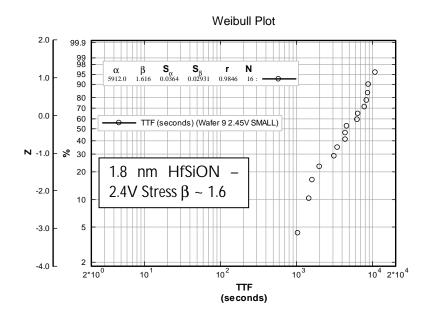

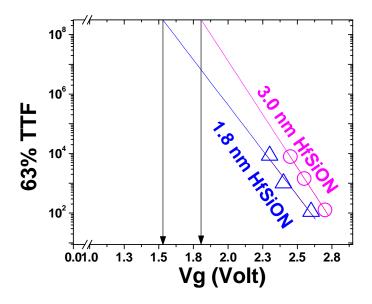

| 4.5 Time Dependent Dielectric Breakdown (TDDB) dependence on thickness                                              | 78       |

| 4.6 PBTI in HfO <sub>2</sub>                                                                                        | 83       |

| 4.7 SILC in HfO <sub>2</sub>                                                                                        | 86       |

| 4.8 Conclusions                                                                                                     | 88       |

| 4.9 References                                                                                                      | 90       |

| CHAPTER 5                                                                                                           | 94       |

| 5.1 Introduction                                                                                                    | 94       |

| 5.2 Sample Fabrication and Experimental Details                                                                     | 96       |

| 5.3 Results and Discussion                                                                                          | 98       |

| 5.4 Conclusions                                                                                                     | 109      |

| 5.5 References                                                                                                      | 110      |

| CHAPTER 6                                                       | 112 |

|-----------------------------------------------------------------|-----|

| 6.1 Introduction                                                | 112 |

| 6.2 Sample Fabrication and Experimental Details                 | 112 |

| 6.2.1 Plasma Nitridation:                                       | 112 |

| 6.2.1.1 Electrical Parameters                                   | 113 |

| 6.2.2 Thermal Nitridation vs. Plasma Nitridation:               | 115 |

| 6.3 Results and Discussion                                      | 116 |

| 6.3.1 Plasma Nitridation in ALD HfSiON                          | 116 |

| 6.3.2 Thermal Nitridation and Plasma Nitridation:               | 122 |

| 6.4 NBTI in Plasma Nitrided HfSiON                              | 125 |

| 6.5 Conclusions                                                 | 127 |

| 6.6 References                                                  | 129 |

| CHAPTER 7                                                       | 133 |

| 7.1 Summary and Conclusions                                     | 133 |

| 7.2 Suggestions for Future Work                                 | 135 |

| 7.2.1 Metal Gates                                               | 135 |

| 7.2.2 "Higher-κ" Dielectrics                                    | 135 |

| 7.2.3 High-κ and Higher-κ materials on high mobility substrates | 136 |

| Bibiography                                                     | 137 |

| Vita                                                            | 152 |

### Chapter 1

#### Introduction

#### 1.1 Motivation for High-κ Dielectrics

The performance of integrated circuits has been improving continuously primarily due to the shrinkage of Metal-Oxide-Semiconductor (MOS) transistors[1]. The reduction of channel length, called scaling, is accompanied by reduction in size of most of the other features, consequent to which, the entire circuit scales in size. Figure 1.1 shows the increase in performance due to scaling, over the years. This performance increase over the years occurs at a rate predicted by Intel co-founder Gordon Moore and is called Moore's law in his honour.

Figure 1.1: Moore's law – Increase in performance due to scaling [2].

Minimum feature size has shrunk more than ten-fold and the number of transistors has increased by more than three orders of magnitude in the last 20 years. There have been

many fundamental problems that have been posed over the technology generations, like hot carrier reliability and drain induced barrier lowering. It was possible to overcome these barriers with innovative technology solutions like halo-doping and LDDs [3]. For the first time, however, technological evolution in the near-future nodes is facing a fundamental roadblock. The thickness of the gate dielectric, Silicon dioxide has been scaled to the extent that only a few atomic layers remain. Silicon dioxide (SiO<sub>2</sub>) has many qualities that has made it the dielectric of choice for decades in MOS processing, namely[4]:

- a) Excellent thermal stability, on contact with silicon substrate.

- b) Good interface with silicon substrate, with low interface trap density.

- c) Low bulk fixed charges.

- d) Good lattice match with Silicon.

- e) Easy to grow or deposit in a wide variety of techniques.

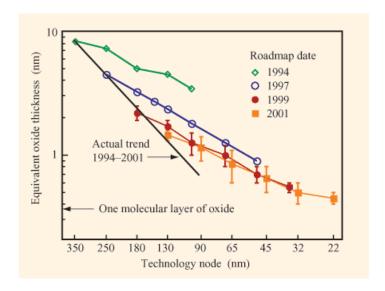

Indeed, SiO<sub>2</sub> has been one of the primary reasons for the industry to sustain silicon technology over decades. The electrical thickness or equivalent oxide thickness (EOT) of the gate dielectric needs to be scaled along with channel length for the scaling rules to apply[5]. Figure 1.2 shows Equivalent Oxide Thickness scaling with technology node[6].

Figure 1.2: EOT scaling with technology – Current technologies[6].

The tunneling leakage current, increases exponentially with decreasing  $T_{ox}$  [7], as shown in equation 1.1.

$$I_{\text{ox}} = K_2 W \left(\frac{V}{T_{\text{ox}}}\right)^2 e^{-\alpha T_{\text{ox}}/V}$$

......Equation 1.1[8].

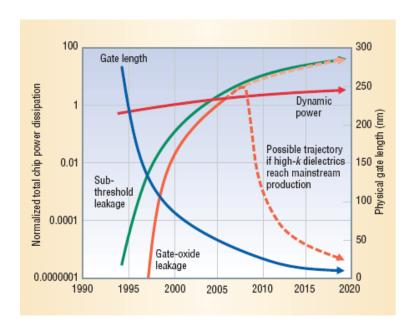

The gate leakage current, along with subtreshold leakage current, leads to off state static power consumption in the circuits [8]. Figure 1.3 illustrates the increase of power consumption over the years[8].

Figure 1.3: Normalized total chip power consumption over the years – large increase in the near future [8].

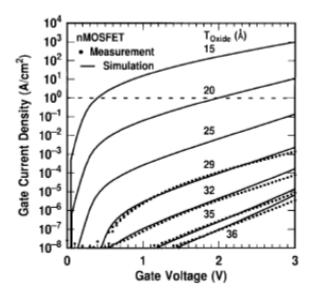

The leakage current density as a function of gate voltage for different  $SiO_2$  thicknesses is shown in figure 1.4 [9]. The reliability of  $SiO_2$  dielectrics of such low thicknesses is another concern [10].

Figure 1.4: Leakage current density vs. gate voltage – for different thicknesses of SiO<sub>2</sub>

Thinner gate dielectrics are required in order to facilitate the achievement of higher capacitance [5]. As the channel length is reduced, higher capacitance is needed to attain better control over the channel, thereby suppressing short channel effects and achieving higher drive current. The gate capacitance is given by equation 1.2.

$$C_{\text{ox}} = (\epsilon_0 \kappa) / T_{\text{phys}} \qquad \qquad \text{.....} Equation 1.2$$

Where  $\varepsilon_0$  is the vacuum permittivity,  $\kappa$  is the relative dielectric constant or dielectric constant (also referred to as  $\varepsilon_R$ ). It can be seen that the capacitance can be increased decreasing the thickness  $\mathit{or}$  increasing  $\kappa$ . The materials for which the dielectric constant is higher than that of  $SiO_2$  ( $\kappa_{SiO2}=3.9$ ) are called "high- $\kappa$ " materials. The equivalent thickness of  $SiO_2$  needed to achieve the same capacitance as the capacitance of a high- $\kappa$  material of a given physical thickness  $t_{phy}$  is called Capacitance Equivalent thickness (CET). CET can be defined as:

$$CET = (\epsilon_{SiO2}/\kappa_{high-k}) * T_{phys.}$$

Various high- $\kappa$  materials have been studied over the last decade and this dissertation deals with reliability issues associated with hafnium based high- $\kappa$  materials.

#### 1.2 High-κ Dielectrics: The Road So Far

#### 1.2.1 "Higher-k" Materials

There has been frenetic activity in the research community in the last decade in the area of high permittivity dielectrics. Dielectric materials with  $\kappa$  values between 7-30 are defined as high- $\kappa$  dielectrics, while materials with  $\kappa$  values between 30-100 are termed "higher- $\kappa$ " dielectrics. Indeed, higher- $\kappa$  dielectrics like Barium Strontium Titanate (BST) and Lead Zirconium Titanate (PbZrTiO) were amongst the first to be investigated. However, the capacitance values offered by these dielectrics are too high for the near-future technology [11] besides which, the bandgap of these materials is too small for electrical viability [12, 13]. Due to the availability of materials with more desirable qualities, the consideration of higher- $\kappa$  materials was abandoned (at least temporarily). Figure 1.5 shows electrical properties of various dielectric materials that have been investigated [12].

|                                                  | Gap<br>(eV) | CNL<br>(eV) | $\epsilon_{\infty}$ | S'<br>calculated | EA<br>(eV) | Calculated CB<br>offset (eV) |

|--------------------------------------------------|-------------|-------------|---------------------|------------------|------------|------------------------------|

| Si                                               | 1.1         | 0.2         | 12                  |                  | 4.0        |                              |

| SiO <sub>2</sub>                                 | 9           |             | 2.25                | 0.86             | 0.9        | 3.5 (exp)                    |

| Si <sub>3</sub> N <sub>4</sub>                   | 5.3         |             | 3.8                 | 0.51             | 2.1        | 2.4 (exp)                    |

| SrTiO <sub>3</sub>                               | 3.3         | 2.60        | 6.1                 | 0.28             | 3.9        | -0.1                         |

| PbTiO <sub>3</sub>                               | 3.4         | 1.90        | 6.25                | 0.31             | 3.5        | 0.6                          |

| BaZrO <sub>3</sub>                               | 5.3         | 3.7         | 4                   | 0.53             | 2.5        | 0.8                          |

| PbZrO <sub>3</sub>                               | 3.7         | 2.6         | 4.8                 | 0.4              | 3.2        | 0.2                          |

| Ta <sub>2</sub> O <sub>5</sub>                   | 4.4         | 3.3         | 4.84                | 0.40             | 3.2        | 0.36                         |

| SrBi <sub>2</sub> Ta <sub>2</sub> O <sub>9</sub> | 4.1         | 3.3         | 5.3                 | 0.35             | 3.3        | 0.15                         |

| TiO <sub>2</sub>                                 | 3.05        | 2.2         | 7.8                 | 0.18             | 3.9*       | 0                            |

| $ZrO_2$                                          | 5.8         | 3.6         | 4.8                 | 0.41             | 2.5*       | 1.4                          |

| $HfO_2$                                          | 6           | 3.7         | 4                   | 0.53             | 2.5*       | 1.5                          |

| $A1_2O_3$                                        | 8.8         | 5.5         | 3.4                 | 0.63             | 1*         | 2.8                          |

| $Y_2O_3$                                         | 6           | 2.4         | 4.4                 | 0.46             | 2*         | 2.3                          |

| La <sub>2</sub> O <sub>3</sub>                   | 6*          | 2.4         | 4                   | 0.53             | 2*         | 2.3                          |

| ZrSiO <sub>4</sub>                               | 6*          | 3.6         | 3.8                 | 0.56             | 2.5*       | 1.5                          |

| HfSiO <sub>4</sub>                               | 6*          | 3.6         | 3.8                 | 0.56             | 2.5*       | 1.5                          |

Table 1.1: Electrical properties of various materials [12].

#### 1.2.2 Other high-k materials

As focus settled on high- $\kappa$  materials with  $\kappa$  values ~ 10-30, tantulum pentoxide (Ta<sub>2</sub>O<sub>5</sub>) was studied extensively [14-16]. Although MOS capacitors and short channel transistors with excellent electrical properties and CETs below 10Å were reported [14], it was generally agreed that Ta<sub>2</sub>O<sub>5</sub> is thermally unstable in contact with silicon and forms tantulum silicide pockets in the gate stack. Titanium oxide was another material [17] that was investigated because of the high  $\kappa$  value that it offers. Similar to Ta<sub>2</sub>O<sub>5</sub>, TiO<sub>2</sub> was also found to be thermally unstable in contact with silicon. Moreover, both Ta<sub>2</sub>O<sub>5</sub> and TiO<sub>2</sub> have low barrier heights for electron conduction, leading to high leakage currents [17].

Indeed, these drawbacks formed the basis for further investigation into high- $\kappa$  dielectrics for MOS applications. The rules formulated for high- $\kappa$  dielectrics were as follows [18]:

- a) High dielectric constant ~ 10-30.

- b) Bandgap > 5eV.

- c) Good thermal stability in contact with silicon.

- d) Amorphous after high temperature processing Defect density in poly-crystalline materials is generally high.

- e) Good interface with top electrode (Poly-si or metal gate).

- f) Scalable to EOT < 10Å.

- g) Form good interface with silicon Low interface trap density.

- h) Good mechanical properties.

Two lanthanide materials emerged from a careful consideration of the above specified rules – hafnium oxide (HfO<sub>2</sub>) and zirconium oxide (ZrO<sub>2</sub>) (and subsequently, their silicates) [18, 19]. Both of these oxides exhibited excellent thermal and electrical properties and capacitors and transistors with sub-nm EOTs were demonstrated. While HfO<sub>2</sub> was found to have good electrical qualities with both poly-silicon (poly-Si) gate electrode [20]and metal gates [21], ZrO<sub>2</sub> was found to be unstable with poly-Si gate electrode, due to silicide formation during the poly-Si deposition [22]. Zirconium Oxide was therefore abandoned in favor of HfO<sub>2</sub> and hafnium silicate. Subsequently, however,

owing to many of poly-silicon's drawbacks as the gate electrode (see next section), metals like titanium Nitride and tantalum Nitride have become strong contenders for the gate electrode, in conjunction with hafnium based dielectrics, thereby rendering the reason to avoid ZrO<sub>2</sub> irrelevant.

#### 1.3 Hafnium Based Dielectrics with Metal Gates

Poly-silicon, the gate electrode which has been used with SiO<sub>2</sub> dielectrics, is also running into roadblocks. As the scaling heads towards sub-nm EOTs, poly-depletion becomes a significant deterrent to the use of this gate electrode [23]. Poly-depletion occurs due to the formation of a thin depletion layer in the poly-electrode, despite the high dopant densities. This causes an increase in EOT (loss in capacitance) due to an increase in physical thickness, and consequently, causes drain current loss. This additional EOT is in the order of a few Å and cannot be ignored as the EOT targets are scaled down to below 10Å.

As the technologies scale down, the dopant densities in poly-Si need to be increased in order to avoid the poly depletion effect. In the case of pMOS transistors, this is achieved by increasing the dose of Boron dopant (p-type). Boron, however, has high diffusivity in SiO<sub>2</sub> [23] (and even higher diffusivity in HfO<sub>2</sub> [24]) and diffuses down to the substrate, causing faulty devices. Metal gate electrodes have therefore attracted a lot of attention over the years. Several metals like titanium [25], tungsten (W) [26], titanium nitride (TiN) [27], tantalum nitride (TaN)[27], titanium silicon nitride (TiSiN), molybdenum [28], molybdenum nitride (BfN) [29] and hafnium silicide (HfSi) [30] have been investigated. Like

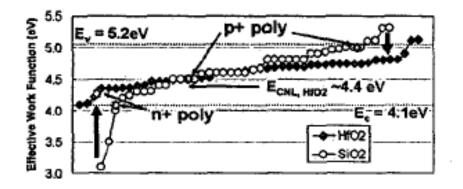

in the case of SiO<sub>2</sub>, attempts are underway to identify metal gates with work functions which can provide nMOS and pMOS transistors with appropriate threshold voltages [31]. Attempts have also been made to integrate two different metals with nMOS and pMOS type work function into the standard cMOS flow [32]. Schaeffer et al investigated a variety of metals and reported that most metals on hafnium based dielectrics have work functions close to the mid-gap of silicon [31]. Figure 1.5 shows all the works functions of various metal gates that investigated by schaeffer et al.

Figure 1.5: Effective work function of various metals on  $HfO_2$  and  $SiO_2$ [31].

This phenomenon is due to the pinning of the fermi level to the mid-gap of silicon, due to dipoles formed at the interface between the metal and the hafnium based dielectric. The effect of fermi-level pinning is also seen in poly-silicon gate electrodes on hafnium based dielectrics (figure 1.5). There have been attempts to modify the top interface with a different dielectric, with both metal gates and poly-silicon gates in order to achieve the correct effective work function. Aluminum oxide has been studied as the top interface dielectric, for pMOS work function metals on hafnium based dielectrics

[33]. The search for the appropriate metals and integration techniques still continues as we get closer to the 65nm and 45nm technology nodes.

#### 1.4 High-κ dielectrics: Primary concerns

#### 1.4.1 Mobility Degradation

The timing delay through VLSI circuits is scaled down by increasing the drain current in successive generations. The drain current is given by:

$$I_{D} = \mu C_{ox}(W/2L) \ (2(V_{G}-V_{TH}) \ V_{DS} - V_{DS}^{\ 2}) \ for \ V_{DS} < V_{G} - V_{T} \ ..... Equation \ 1.3 \ (a)$$

$$I_D = \mu C_{ox}(W/2L) (V_G-V_{TH})^2 \text{ for } V_{DS} > V_G - V_T \dots Equation 1.3 (b)$$

The intrinsic mobility of the carrier needs to be preserved as the drain current is increased by scaling L (channel length) and oxide capacitance ( $C_{ox}$ ). In hafnium based dielectrics, however, the mobility has been reported to be severely degraded, as compared to  $SiO_2$  dielectrics, which follows a universal curve. There are many fundamental phenomena responsible for carrier mobility degradation in hafnium based dielectrics:

- a) Remote coulomb scattering from fixed charges in the bulk high-κ dielectric [34, 35].

- b) Soft optical phonons that couple with phonons in the silicon substrate to provide addition scattering [35-37].

- c) Remote roughness scattering: Due to roughness in the top interface layer [34].

- d) Loss of inversion charge in the channel due to "trapping" in trap sites in the highκ layer – this leads to the appearance of mobility degradation [38, 39].

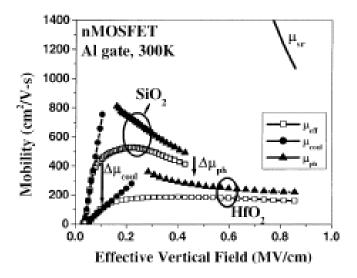

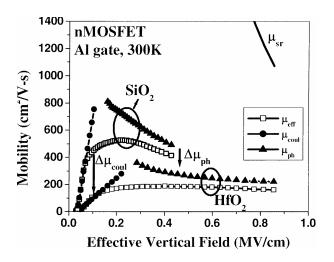

Zhu et al [35] proposed that the mobility degradation in HfO<sub>2</sub> is due to a combination of phonon scattering, coulomb scattering and remote phonon scattering, especially at high fields. Figure 1.6 illustrates the different degradation mechanisms and the fields at which they dominate.

Figure 1.6: Scattering in mechanisms with  $HfO_2$  – Mechanisms dominant at different fields [35].

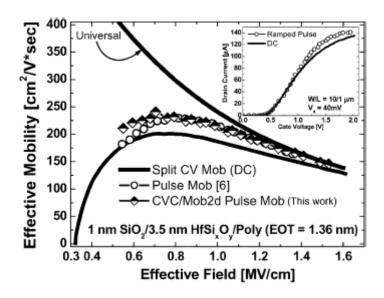

Scattering mechanisms and their mitigation are some of the issues addressed in the following chapters. Andy kerber et al [38] and Chadwin young [39] showed that the effect of charge trapping on "apparent" mobility degradation could be eliminated by performing fast  $I_d$ - $V_g$  measurement in the microsecond regime, thereby eliminating the trapping of electrons, which trap on the order of a 100  $\mu$ sec. Figure 1.7 shows the fast  $I_d$ - $V_g$  curves that Young et al [39] performed.

Figure 1.7: Pulsed Id-Vg vs. DC Id-Vg – Increased drain current in fast Id-Vg [39].

#### 1.4.2 Charge Trapping in high-kgate stacks

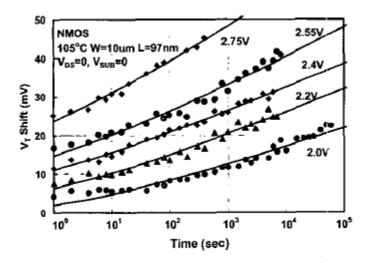

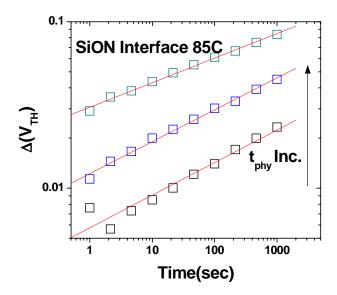

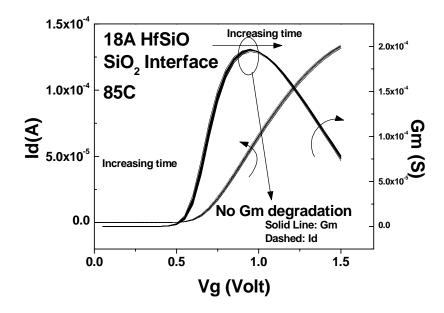

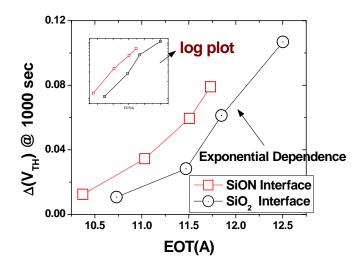

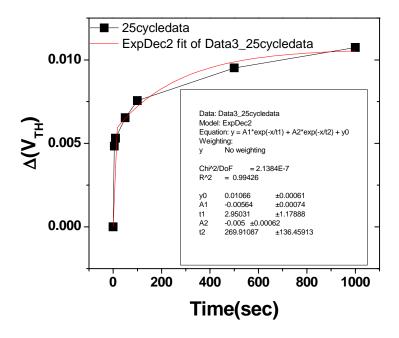

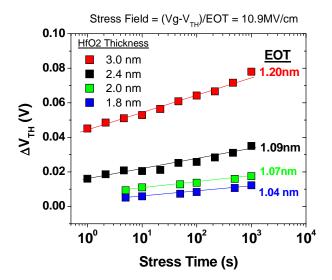

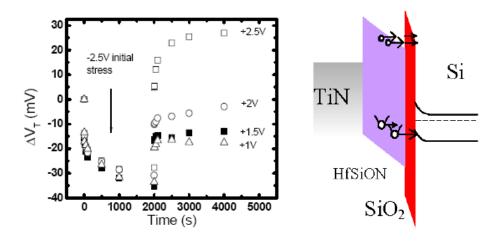

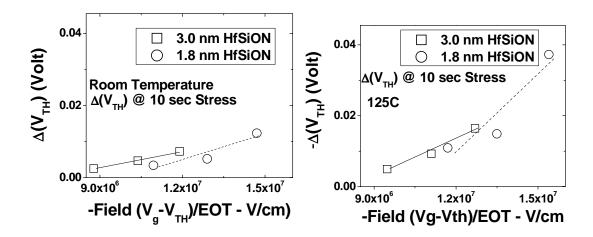

In the previous section, we briefly touched upon the effect of charge traps on mobility. The high trap density in high- $\kappa$  dielectrics has the effect of significant threshold voltage instability as well. The trapping of electrons into charge traps at low voltages (<2V) has the consequence of shifting the threshold voltage in nMOSFETs. This shift in threshold voltage is unique to high- $\kappa$  dielectric gate stacks and has been reported to be > 50mV [40-42]. Figure 1.8 shows the V<sub>TH</sub> shift with time reported by Shanware et al [42].

Figure 1.8: V<sub>TH</sub> in HfSiON gate stacks [42]

There have been various reports speculating that the high- $\kappa$  charge traps are neutral or positively charged oxygen vacancies and are intrinsic to the high- $\kappa$  dielectrics [43, 44]. It was also reported that it is possible to "passivate" such oxygen vacancies by introducing nitrogen into the gate stacks, by various techniques [43].

The metal gate electrode also has a profound effect the charge trapping dynamics of the gate stack [45]. Solving the problem of threshold voltage instability in high- $\kappa$  gate stacks is of paramount importance, as circuits are designed with threshold voltage error specifications < 10 mV.

#### 1.4.3 Negative Bias Temperature Instability

Negative Bias Temperature Instability or NBTI in pMOSFETs is a controversial topic in SiO<sub>2</sub>/Poly-Si, spawning a decade of research and many viable, yet unprovable theories. Hydrogen-Reaction-Diffusion or H°-R-D is the most popular theory offered in the literature. In H°-R-D, negative threshold voltage shift is reported to be due to the

creation of interface traps by the breakage of hydrogen bonds, caused by hole trapping during negative biased stress and the subsequent diffusion of hydrogen through the dielectric [46].

NBTI in hafnium based high- $\kappa$  gate stacks is complicated by the presence of various types of charge traps, which trap and detrap under electrical stress. R. Harris et al [47] reported that the presence of the charge traps renders the effect of H°-R-D negligible in these gate stacks and the threshold voltage shift is largely due to electron detrapping from existing trap sites.

#### 1.4.4 Breakdown and Stress Induced Leakage Current

Time Dependent Dielectric Breakdown (TDDB) and its indicative precursor Stress Induced Leakage Current (SILC) have been reported to be mechanisms of failure in SiO<sub>2</sub> gate stacks. The catastrophic failure of the dielectric leads to large increases in leakage current through the dielectric, reducing the inversion charge significantly [5]. This reduction in inversion charge leads to drain current loss, which causes the circuit to fail. The operating voltage for ten years of device operation in HfO<sub>2</sub> has been reported by several groups to be within the voltage scaling limits [48, 49]. However, the TDDB studies are complicated by

- a) Charge trapping Electron trapping reduces the leakage current in the initial stages of stress.

- b) Soft Breakdown or Progressive Breakdown [50, 51]: Progressive breakdown is

the wearout of the dielectric during stress, resulting in slow increase in current –

This is typically seen in thin dielectrics (EOT <10Å).</li>

c) Polarity dependence: The breakdown in high-κ dielectrics is heavily polarity dependent and is not easily modeled and no consensus has been reached on the exact mechanism of breakdown in the dielectric.

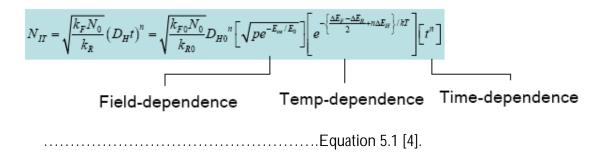

Stress induced leakage current increase or SILC is another important phenomenon that is often considered a pre-cursor to breakdown. SILC is conventionally thought to occur due to stress-generated traps that increase the leakage current [4]. The high trap density in high- $\kappa$  gate stacks also complicates the issues associated with stress induced leakage current.

#### 1.5 Outline

This dissertation deals primarily with the said reliability issues, the mechanism, physical modeling and possible resolutions.

Chapter 2 deals with Stress Induced Leakage Current (SILC) in HfO<sub>2</sub> with TiN gate electrode. After a brief description of the sample fabrication and stress methodology, the influence of high trap density in the dielectric on SILC and threshold voltage instability is discussed, with particular emphasis on pre-existing defects and stress generated defects.

Chapter 3 discusses the mobility degradation mechanisms in high- $\kappa$  gate stacks. Mobility dependence on the thickness of the interfacial layer is investigated, after an introduction to previous methodologies employed in discussion of mobility degradation. The effect of coulombic, phonon and remote phonon scattering are investigated in detail.

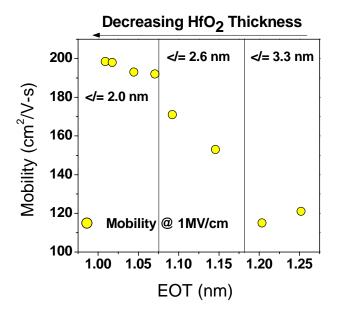

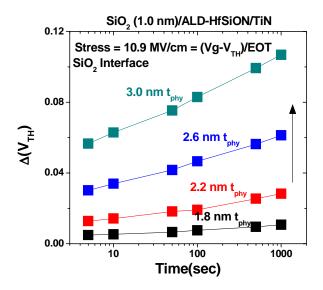

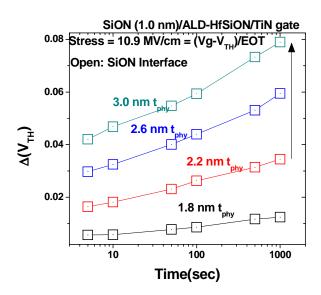

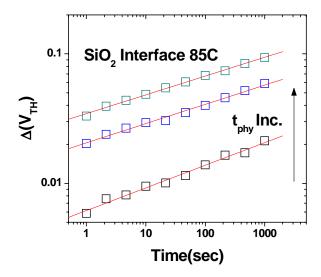

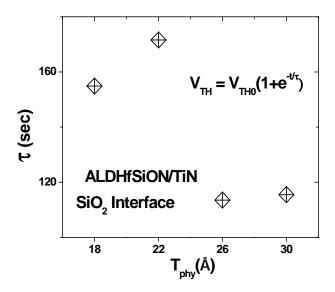

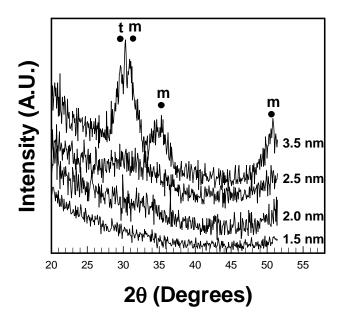

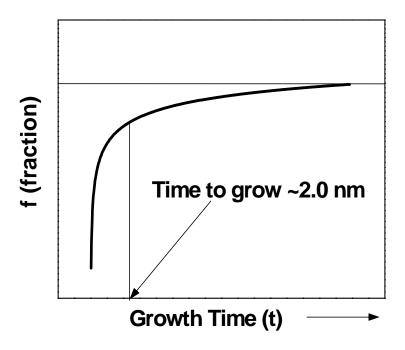

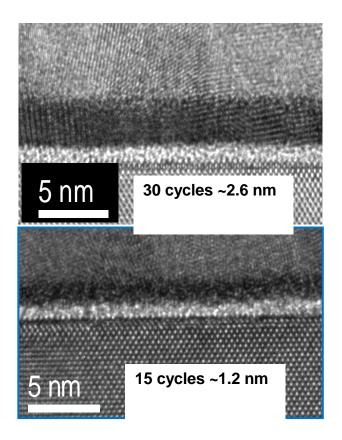

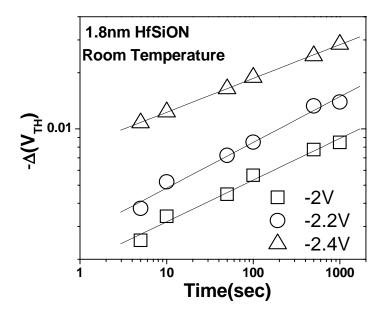

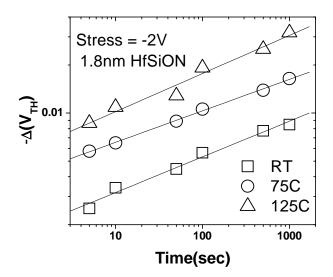

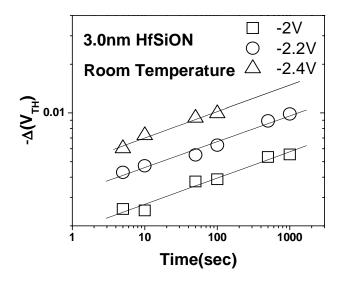

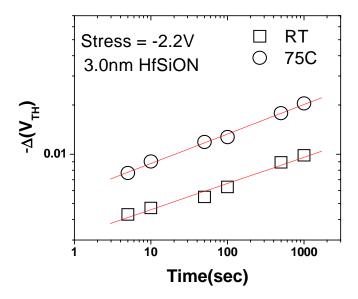

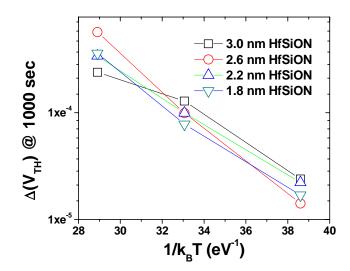

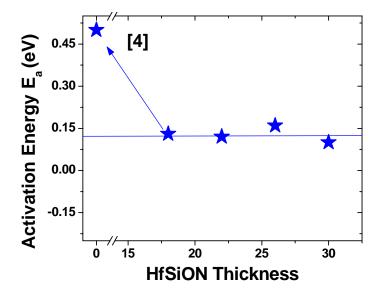

The thickness dependence of the high-k layer on carrier mobility and threshold voltage instability is reported in chapter 4. It is shown that threshold voltage instability

can be mitigated by reducing the thickness of the high- $\kappa$  layer to < 2.0 nm. A possible correlation between the morphology of the dielectric and threshold voltage instability is also discussed. A new mathematical model is proposed for threshold voltage instability in high- $\kappa$  gate stacks.

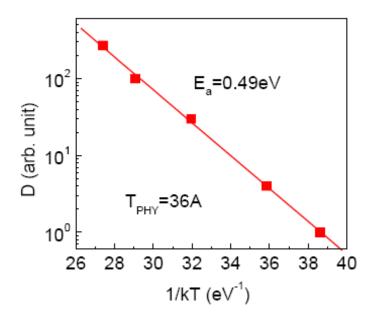

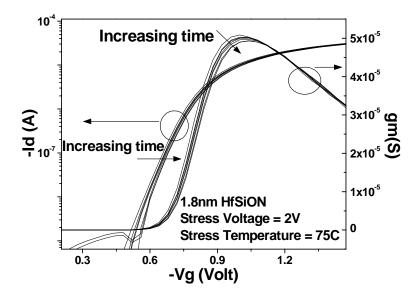

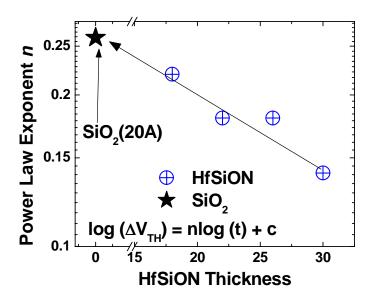

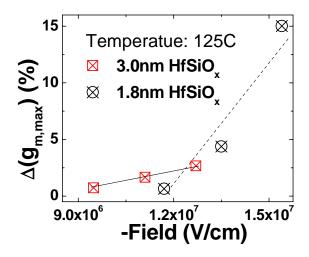

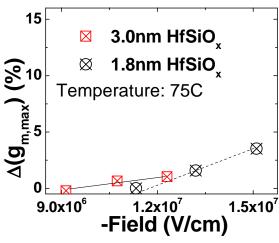

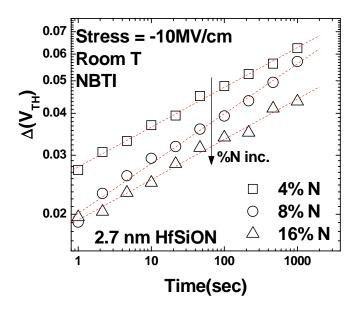

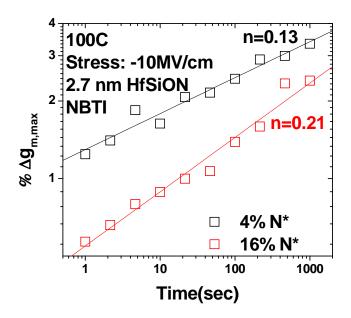

Negative Bias Temperature Instability in ultra-thin high-κ gate stacks is investigated in chapter 5. From an examination of the evolution of the power law exponent "n" with the thickness of the dielectric layer, NBTI is concluded to be a combination of charge trapping and Hydorgen-Reaction-Diffusion model. The activation energy for trap creation and the degradation of peak transconductance are also examined.

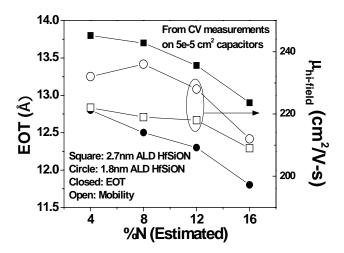

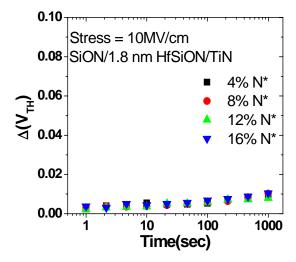

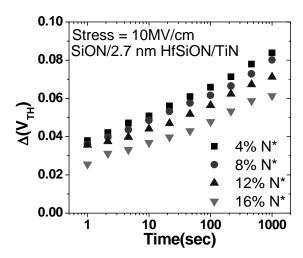

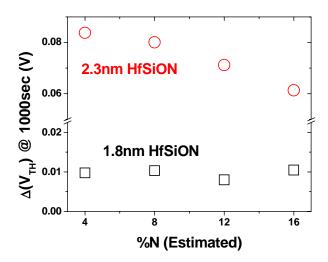

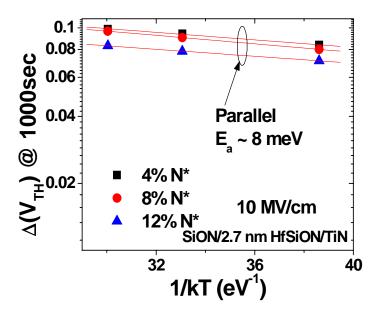

Chapter 6 discusses the influence of the presence of nitrogen in high- $\kappa$  dielectrics on threshold voltage instability in nMOSFETs and pMOSFETs. Nitrogen incorporated through plasma nitridation technique is shown to reduce charge trapping in thick dielectrics, while thin dielectrics are insensitive to the presence of nitrogen in the film. A comparison of different nitridation techniques with respect to threshold voltage instability, EOT and mobility is presented.

In chapter 7, all the reliability characteristics and dielectric properties in high- $\kappa$  gate stacks reported in this dissertation are summarized. Some relevant outstanding issues and suggestions for future research are also presented.

#### 1.6 References

- 1. Internation Technology Roadmap for Semiconductors

- 2. Intel: Craig Barret's Keynote speech on IDF. In: www.anandtechcom. 2005.

- 3. Wolf S: Silicon Processing for the VLSI era, vol. 2: Lattice Press; 1990.

- 4. Hori T: **Gate Dielectrics and MOS ULSIs**. Berlin: Springer-Verlag 1997.

- 5. B. Streetman SB: **Solid State Electronic Devices**: Prentice Hall; 2001.

- 6. **Technology Scaling**

- 7. A. Chandrakasan WB, and F. Fox: **Design of High-Performance Microprocessor Circuits**: IEEE press; 2001.

- 8. N.S. Kim TA, D. Blaauw, T. Mudge, K. Flautner, J.S. Hu, M.J. Irwin, M. Kandemir, and V. Narayanan: **Leakage Current: Moore's law meets static power**. *computer* 2003, **36**(12).

- 9. S.-H. Lo DAB, Y. Taur, and W. Wang: Quantum-mechanical modeling of electron tunneling current from the inversion layer of ultra-thinoxide nMOSFET's. *IEEE Trans Electron Devices* 1997, **18**:209-211.

- DiMaria JHSaDJ: Reliability projection for ultra-thin oxides at low voltage. IEDM Tech Dig 1998:167-170.

- 11. T.-S. Chen DH, V. Valu, V. Jiang, S.-H. Kuah, P. C. McIntyre, S. R., Summerfelt JMA, and J. C. Lee: Ir-electroded BST thin film capacitors for 1 giga-bit DRAM application. *IEDM Tech Dig* 1996:797-800.

- 12. Robertson J: **Band offsets of wide-band-gap oxides and implications for future electronic devices**. *Journal of Vaccuum Society B* 2000, **18**:1785.

- 13. Scott JF: High-Dielectric Constant Thin Films for Dynamic Random Access

Memories. Annual Review of Materials Science 1998.

- 14. D. Park Y-CK, Q. Lu, T.-J. King, C. Hu, A. Kalnitsky, S.-P. Tay, and, Cheng C-C: Transistor characteristics with Ta2O5 gate dielectric. *IEEE*

Electron Device Lett 1998, 19:441-443.

- 15. M. Saito MY, K. Asaka, H. Goto, N. Fukuda, M. Kawano, M. Kojima, M. Suzuki, K. Ogaya, H. Enomoto, K. Hotta, S. Sakai, H. Asakura, T. Fukuda TS, T. Takakura, and N. Kobayashi: Advanced thermally stable silicide S/D electrodes for high-speed logic circuits with large-scale embedded Ta2O5-capacitor DRAMs. IEDM Tech Dig 1999:805-808.

- P. K. Roy and I. C. Kizilyalli: Stacked high-ε gate dielectric for gigascale integration of metal–oxide–semiconductor technologies. Appl Phys Lett 1998, 72:2835-2837.

- 17. Campbell SA, Gilmer DC, Xiao-Chuan W, Ming-Ta H, Hyeon-Seag K, Gladfelter WL, Jinhua Y: MOSFET transistors fabricated with high permittivity TiO<sub>2</sub> dielectrics. Electron Devices, IEEE Transactions on 1997, 44(1):104-109.

- 18. Lee BH: Technology Development and process integration of alternative gate dielectric material; Hafnium Oxide. Dissertation. Austin: The University of Texas; 2001.

- 19. Qi W-J: Study on high-k dielectrics as alternative gate insulators for 0.1 micron and beyond ULSI applications. Austin: The University of Texas; 2000.

- 20. Onishi K, Chang Seok K, Rino C, Hag-Ju C, Gopalan S, Nieh R, Krishnan S, Lee JC: Effects of high-temperature forming gas anneal on HfO/sub 2/ MOSFET performance. In: VLSI Symposium: 2002; 2002: 22-23.

- 21. Rino C, Onishi K, Chang Scok K, Renee N, Gopalan S, Hag-Ju C, Krishnan S, Lee JC: High quality MOSFETs fabrication with HfO/sub 2/ gate dielectric and tan gate electrode. In: Device Research Conference, 2002 60th DRC Conference Digest: 2002: IEEE; 2002: 193-194.

- 22. Nieh R, Krishnan S, Hag-Ju C, Chang Seok K, Gopalan S, Onishi K, Choi R, Lee JC: Comparison between ultra-thin ZrO/sub 2/ and ZrO/sub x/N/sub y/ gate dielectrics in TaN or poly-gated NMOSCAP and NMOSFET devices. In: VLSI Symposium: 2002; 2002: 186-187.

- 23. Wong CY, Sun JY, Taur Y, Oh CS, Angelucci R, Davari B: Doping of n<sup>+</sup> and p<sup>+</sup> polysilicon in a dual-gate CMOS process. In: Electron Devices Meeting, 1988 Technical Digest, International 1988; 1988: 238-241.

- 24. Onishi K, Kang L, Choi R, Dharmarajan E, Gopalan S, Yongjoo J, Chang Seok K, Byoung Hun L, Nieh R, Lee JC: Dopant penetration effects on polysilicon gate HfO<sub>2</sub> MOSFET's. In: VLSI Technology, 2001 Digest of Technical Papers 2001 Symposium on 2001; 2001: 131-132.

- 25. Ching-Huang L, Wong GMT, Deal MD, Tsai W, Majhi P, Chi On C, Visokay MR, Chambers JJ, Colombo L, Clemens BM *et al*: **Characteristics and mechanism of**

- tunable work function gate electrodes using a bilayer metal structure on SiO/sub 2/ and HfO/sub 2. Electron Device Letters, IEEE 2005, 26(7):445-447.

- 26. Narayanan V, Callegari A, McFeely FR, Nakamura K, Jamison P, Zafar S, Cartier E, Steegen A, Ku V, Nguyen P et al: Dual work function metal gate CMOS using CVD metal electrodes. In: VLSI Technology, 2004 Digest of Technical Papers 2004 Symposium on 2004: IEEE; 2004: 192-193.

- 27. Majhi P, Young C, Bersuker G, Wen HC, Brown GA, Foran B, Choi R, Zeitzoff PM, Huff HR: Influence of metal gate materials and processing on planar CMOS device characteristics with high-k gate dielectrics. In: Solid-State Device Research conference, 2004 ESSDERC 2004 Proceeding of the 34th European: 2004; 2004: 185-188.

- 28. Qiang L, Lin R, Ranade P, Tsu-Jae K, Chenming H: Metal gate work function adjustment for future CMOS technology. In: VLSI Technology, 2001 Digest of Technical Papers 2001 Symposium on 2001; 2001: 45-46.

- 29. Kang JF, Yu HY, Ren C, Wang XP, Li MF, Chan DSH, Liu XY, Han RQ, Wang YY, Kwong DL: Characteristics of sub-1 nm CVD HfO/sub 2/ gate dielectrics with HfN electrodes for advanced CMOS applications. In: Solid-State and Integrated Circuits Technology, 2004 Proceedings 7th International Conference on 2004; 2004: 393-398 vol.391.

- 30. Chang Seo P, Byung Jin C, Dim-Lee K: **Thermally stable fully silicided Hf-silicide** metal-gate electrode. *Electron Device Letters*, *IEEE* 2004, **25**(6):372-374.

- 31. Schaeffer JK, Capasso C, Fonseca LRC, Samavedam S, Gilmer DC, Liang Y, Kalpat S, Adetutu B, Tseng HH, Shiho Y et al: Challenges for the integration of metal gate electrodes. In: Electron Devices Meeting, 2004 IEDM Technical Digest IEEE International 2004; 2004: 287-290.

- 32. Samavedam SB, La LB, Smith J, Dakshina-Murthy S, Luckowski E, Schaeffer J, Zavala M, Martin R, Dhandapani V, Triyoso D *et al*: **Dual-metal gate CMOS with HfO/sub 2/ gate dielectric**. In: *Electron Devices Meeting*, 2002 *IEDM '02 Digest International 2002*; 2002: 433-436.

- 33. Hong-Jyh L, Gardner MI: Dual high-/spl kappa/ gate dielectric with poly gate electrode: HfSiON on nMOS and Al/sub 2/O/sub 3/ capping layer on pMOS. Electron Device Letters, IEEE 2005, 26(7):441-444.

- 34. Weber O, Andrieu F, Casse M, Ernst T, Mitard J, Ducroquet F, Damlencourt JF, Hartmann JM, Lafond D, Papon AM et al: Experimental determination of mobility scattering mechanisms in Si/HfO/sub 2//TiN and SiGe:C/HfO/sub 2//TiN surface channel n- and p-MOSFETs. In: Electron Devices Meeting, 2004 IEDM Technical Digest IEEE International 2004; 2004: 867-870.

- 35. Zhu WJ, Ma TP: Temperature dependence of channel mobility in HfO/sub 2/gated NMOSFETs. Electron Device Letters, IEEE 2004, 25(2):89-91.

- 36. Chau R, Datta S, Doczy M, Doyle B, Kavalieros J, Metz M: High-/spl kappa//metal-gate stack and its MOSFET characteristics. *Electron Device Letters, IEEE* 2004, 25(6):408-410.

- 37. Ren Z, Fischetti MV, Gusev EP, Cartier EA, Chudzik M: Inversion channel mobility in high-/spl kappa/ high performance MOSFETs. In: Electron Devices Meeting, 2003 IEDM '03 Technical Digest IEEE International 2003; 2003: 33.32.31-33.32.34.

- 38. Kerber A, Cartier E, Ragnarsson LA, Rosmeulen M, Pantisano L, Degraeve R, Kim Y, Groeseneken G: Direct measurement of the inversion charge in MOSFETs: application to mobility extraction in alternative gate dielectrics. In: VLSI Technology, 2003 Digest of Technical Papers 2003 Symposium on 2003; 2003: 159-160.

- 39. Young CD, Bersuker G, Brown GA, Lysaght P, Zeitzoff P, Murto RW, Huff HR: Charge trapping and device performance degradation in MOCVD hafniumbased gate dielectric stack structures. In: Reliability Physics Symposium Proceedings, 2004 42nd Annual 2004 IEEE International: 2004; 2004: 597-598.

- 40. Onishi K, Rino C, Chang Seok K, Hag-Ju C, Young Hee K, Nieh RE, Jeong H, Krishnan SA, Akbar MS, Lee JC: Bias-temperature instabilities of polysilicon gate HfO/sub 2/ MOSFETs. Electron Devices, IEEE Transactions on 2003, 50(6):1517-1524.

- 41. Sa N, Kang JF, Yang H, Liu XY, He YD, Han RQ, Ren C, Yu HY, Chan DSH, Kwong DL: Mechanism of positive-bias temperature instability in sub-1-nm TaN/HfN/HfO/sub 2/ gate stack with low preexisting traps. Electron Device Letters, IEEE 2005, 26(9):610-612.

- 42. Shanware A, Visokay MR, Chambers JJ, Rotondaro ALP, Bu H, Bevan MJ, Khamankar R, Aur S, Nicollian PE, McPherson J *et al*: **Evaluation of the positive**

- biased temperature stress stability in HfSiON gate dielectrics. In: *Physics Symposium Proceedings*, 2003 41st Annual 2003 IEEE International 2003; 2003: 208-213.

- 43. J. L. Gavartin ALS, A. S. Foster and G. I. Bersuker: The role of nitrogen-related defects in high-k dielectric oxides: Density-functional studies. *JOURNAL OF APPLIED PHYSICS* 2005, 97:13.

- 44. Nobuyuki Ikarashi MM, Koji Masuzaki, and Toru Tatsumi: **Electron energy-loss** spectroscopy analysis of the electronic structureof nitrided Hf silicate films. *APPLIED PHYSICS LETTERS* 2004, **84**(18).

- 45. Xuguang W, Peterson J, Majhi P, Gardner MI, Dim-Lee K: Impacts of gate electrode materials on threshold voltage (V/sub th/) instability in nMOS HfO/sub 2/ gate stacks under DC and AC stressing. Electron Device Letters, IEEE 2005, 26(8):553-556.

- 46. Alam MA: A critical examination of the mechanics of dynamic NBTI for PMOSFETs. In: Electron Devices Meeting, 2003 IEDM '03 Technical Digest IEEE International 2003; 2003: 14.14.11-14.14.14.

- 47. Harris HR, Choi R, Lee BH, Young CD, Sim JH, Mathews K, Zeitzoff P, Majhi P, Bersuker G: Comparison of NMOS and PMOS stress for determining the source of NBTI TiN/HfSiON devices. In: Reliability Physics Symposium, 2005 Proceedings 43rd Annual 2005 IEEE International: 2005; 2005: 80-83.

- 48. Sungjoo L, Kwong DL: **TDDB and polarity-dependent reliability of high-quality,** ultrathin CVD HfO/sub 2/ gate stack with TaN gate electrode. *Electron Device Letters*, *IEEE* 2004, **25**(1):13-15.

- 49. Young Hee K, Onishi K, Chang Seok K, Hag-Ju C, Rino C, Krishnan S, Akbar MS, Lee JC: Thickness dependence of Weibull slopes of HfO/sub 2/ gate dielectrics.

Electron Device Letters, IEEE 2003, 24(1):40-42.

- 50. Kauerauf T, Degraeve R, Zahid MB, Cho M, Kaczer B, Roussel P, Groeseneken G, Maes H, De Gendt S: Abrupt breakdown in dielectric/metal gate stacks: a potential reliability limitation? Electron Device Letters, IEEE 2005, 26(10):773-775.

- 51. Young Hee K, Onishi K, Chang Seok K, Hag-Ju C, Nieh R, Gopalan S, Choi R, Jeong H, Krishnan S, Lee JC: **Area dependence of TDDB characteristics for HfO/sub 2/gate dielectrics**. *Electron Device Letters, IEEE* 2002, **23**(10):594-596.

# Chapter 2

## **Stress Induced Leakage current**

#### 2.1 Introduction

Stress Induced Leakage current (SILC) is a precursor to hard breakdown in SiO<sub>2</sub> dielectrics. The leakage current increases due to the gradual creation of new defect centers, which provide leakage paths for the electrons. Breakdown occurs when a set of newly created defect centers line up, leading to catastrophic leakage increase (Percolation Path theory). Although several studies have focused on this issue [1, 2], the extent of stress-induced degradation in Hi-K dielectrics is still not clear. In traditional SiO<sub>2</sub>/Poly-Si gate stacks, almost all oxide degradation is attributed to trap generation leading to percolation model type failure, while pre-existing defects are believed to contribute to extrinsic mode failure [3]. For the HfO<sub>2</sub>/TiN gate stack, it has been reported that a similar mechanism was at work[1]. In this study, we have investigated SILC characteristics of HfO<sub>2</sub> / TiN gate nMOS and pMOS transistors in conjunction with the trapping/de-trapping processes in the high-k dielectric.

# 2.2 Experiment

#### 2.2.1 Device Fabrication

The process flow of 70nm TiN gate MOSFET devices fabrication is shown in Table 2.1. The experimental devices consist of  $T_{phy}$ =3.0nm HfO<sub>2</sub>. On the HF cleaned 200 mm wafer, a thin high quality SiO<sub>2</sub> layer of 10Å is grown using an O<sub>3</sub> (Ozone)

oxidant [8]. The ALD HfO<sub>2</sub> is then deposited using HfCl<sub>4</sub> precursor and O<sub>3</sub> oxidant. In this flow, HfO<sub>2</sub> layer is removed after gate patterning with minimal damage in the extension region. A thin nitride layer is then deposited to protect the HfO<sub>2</sub> layer. LDD and Halo implants were implanted through this thin nitride layer. LDD and halo are optimized to ensure a proper overlap of LDD and control of short channel behavior. TiN/HfO<sub>2</sub> showed an EOT of 14.4Å (without quantum mechanical effect deduction) excellent wafer uniformity, both in threshold voltage and leakage current.

- o HF cleaning

- o  $O_3 SiO_2 Interface (10Å)$

- o ALD HfO<sub>2</sub> 30Å deposition

- o PDA (700°C, 1min in NH3 ambient)

- o TiN / Polysilicon 1500 Å deposition

- o Gate predoping

- o N LDD/halo

- o Nitride spacer (90nm)

- o N SD (Source and Drain)

- o SD RTA (1000°C, 5sec)

- Metallization

- o Forming Gas anneal (480°C, 30min)

Table 2.1: Process Flow of 70nm O3/HfO2/TiN gate stack [8].

#### 2.2.2 Stress Set-up

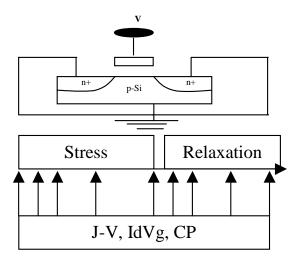

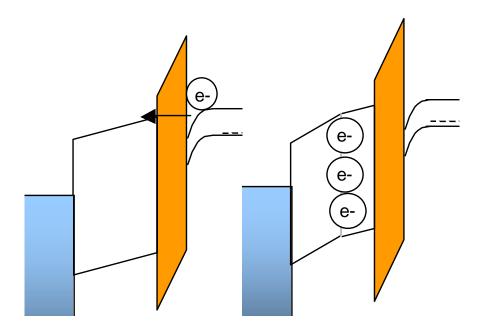

Figure 2.1: SILC Stress setup

The devices used in this setup were  $10x1~\mu m~(10^{-7}~cm^2)$  and  $10x0.5~\mu m~(5x10^{-8}~cm^2)$  nMOS and pMOS transistors. The EOT of the fabricated gate stack was 14.4~Å, with excellent across-the-wafer uniformity. The measurement setup is shown in fig. 2.1. For inversion SILC (positive gate bias in NMOS) study, the leakage current characteristics (J-V) were measured on fresh devices (Vg sweep from 0 to 1.75V), with the source, drain and substrate grounded. On the same device, the  $I_d$ -Vg characteristics were then measured, with  $V_d = 50~mV$ . Then the gate was stressed at various voltages (2.0 V, 2.4V, 2.6V and 2.8V) for 1000 sec (with source, drain and substrate grounded) and the stress was interrupted at various intervals for J-V and Id-Vg measurements. Once the stress cycle was complete, a gate stress of the opposite polarity and various magnitudes (0V, -1V, -2V and -2.6V) was applied for 1000 sec, interrupted for J-V and Id-Vg

measurements. A similar methodology was used for negative gate stress on nMOS, and negative and positive gate stress on pMOS, as well.

### 2.3 Results and Discussion

#### 2.3.1 nMOS:

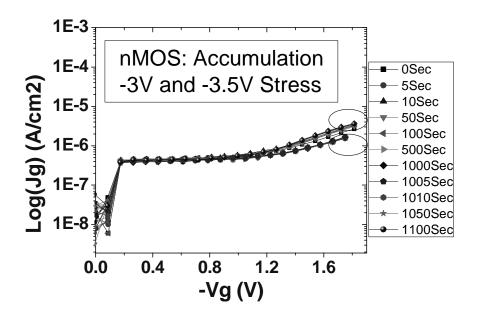

Figure 2.2: SILC under accumulation stress in nMOS - Accumulation Stress of - 3V and -3.5V show no increase in leakage current till 1100 seconds

Accumulation and Inversion SILC was investigated in nMOS transistors For this study, 10x1um transistors (1e-7 cm<sup>2</sup>) and 10x0.5um (5e-8 cm<sup>2</sup>) transistors were used. In all devices tested under negative gate bias conditions (Accumulation), there was almost no detectable SILC observed (fig. 2.2): therefore, this study focussed on the effects of substrate injection stress.

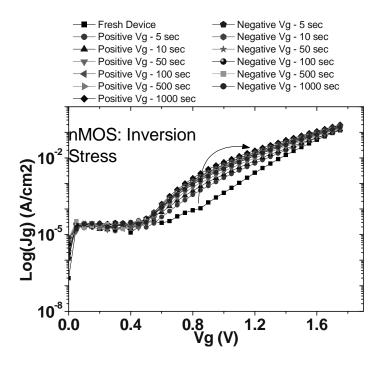

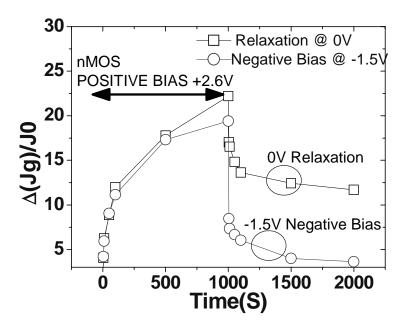

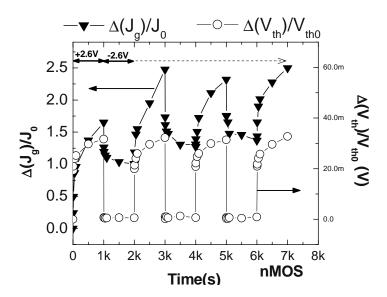

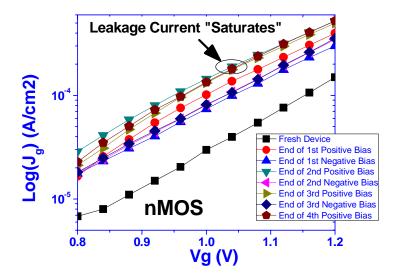

Figure 2.3 (a): SILC in nMOS under Inversion Stress – For a 2.6V stress voltage and 0V relaxation bias, SILC is reversible.

The nMOSFETs were then stressed under substrate bias condition, in order to quantify the SILC under inversion stress of various magnitudes. During the substrate injection stress, both leakage current and threshold voltage increased, while the subthreshold swing remained constant. During the negative bias portion of the stress cycle, however, the leakage current decreased significantly (even for 0V relaxation stress – fig. 2.3 (a)), indicating that SILC increase is not exclusively due to irreversible trap generation.

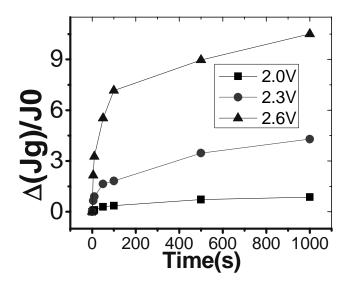

Figure 2.3 (b): SILC at different stress voltages

The magnitude of the increase in leakage current increases with increase in stress voltage, as we would expect (Figure 2.3 (b)). As the negative or recovery bias is increased, the amount of leakage current recovered increased significantly. Indeed, at a recovery bias of -1.5V, nearly all of the leakage current is recovered (figure 2.4).

Figure 2.4: nMOS: The amount of recovered leakage current increased with magnitude of negative bias.

Such SILC reduction was accompanied by the almost complete recovery of the transistor threshold voltage. This recovery in SILC in conjunction with threshold voltage recovery indicates that the mechanism for the two phenomena might be similar. The subthreshold swing remained constant during the stressing cycle (fig. 2.5). The subthreshold swing is an indicator of interface trap density.

$$S \cong kT/q \text{ (In 10)} (1+C_D/C_i) \dots Equation 2.1$$

where  $C_D$  is the depletion capacitance and can be expressed as  $C_{D, ideal} + qD_{it}$ , where  $C_{D, ideal}$  is the depletion capacitance with no interface traps and  $D_{it}$  is the interface trap density[4]. As expressed earlier, during inversion stress, the subthreshold swing does not

change, indicating that the interface trap density remains constant, which we would expect in the case of electron trapping. We therefore rule out hole trapping and the corresponding interface bond breakage as possible mechanisms under inversion stress conditions.

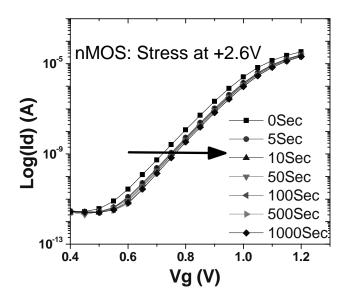

Figure 2.5: No Subthreshold Swing degradation is seen for a stress of 2.6V done for 1000 Sec.

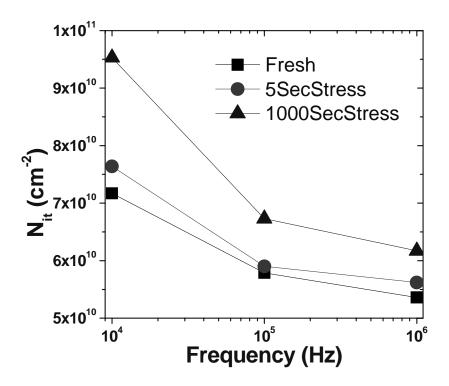

That the subthreshold swing remains constant is not indicative of trap generation free stress. Trap generation could occur in other parts of the dielectric. In order to quantify the trap generation, charge pumping measurements were done before and after the stress at three frequencies (10KHz, 100KHz and 1MHz). Stress-induced N<sub>it</sub> increase is greater at 10 KHz than at 1MHz (fig. 2.6), indicating significant trap generation away

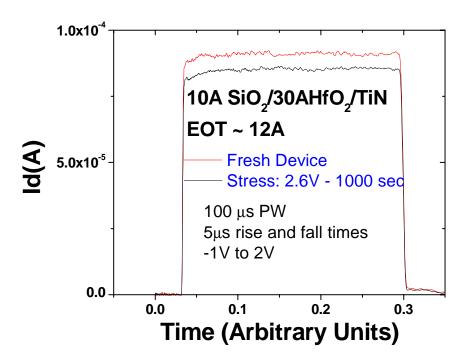

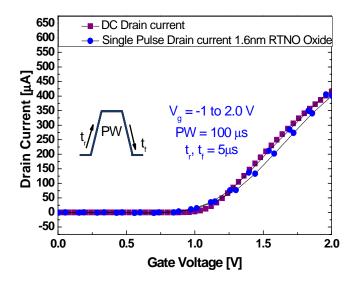

from the gate stack interface with the substrate, which is consistent with the unchanged sub-threshold swing [5]. Charge trapping has been described to be a transient process in high-κ gate stacks, wherein, electrons from the inversion layer are trapped into charge centers in the bulk of the high-κ dielectric, in the usec time range [6]. This leads to a loss in the drain current. In addition, the carrier mobility in the channel, which is generally extracted from the DC drain current – gate voltage measurement (I<sub>d</sub>-V<sub>g</sub>) appears to diminish due to this charge trapping phenomenon, because of the drain current loss. In order to address this issue, kerber et al [6] suggested that the Id-Vg characteristics be collected during the rise time (~5 µsec) of a fast single pulse (100 µsec). The rise time is fast enough that the Id-Vg characteristics are devoid of any inversion charge loss and the drain current loss during the 100 µsec pulse width is indicative of the bulk trap density in the high-k dielectric. Single pulse Id-Vg measurements in the usec range, in the gate stacks under study, do not show any trap generation (fig. 2.7). This suggests that the generated defects affecting CP measurements may be located near the high-k/SiO2 interface and not in the bulk high-K film.

Figure 2.6: Charge pumping vs. frequency: Lower frequencies show higher increase in  $N_{it}$  after stress indicating trap generation away from the interface, but within the interface layer (  $\sim \! 10$  Å from interface)

Figure 2.7: Single Pulse Id-Vg shows no change after a 1000sec stress, indicating minimal bulk trap creation.

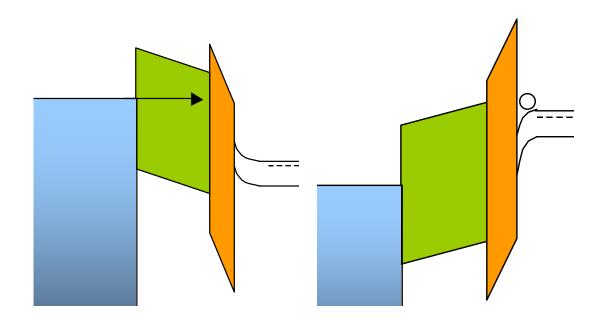

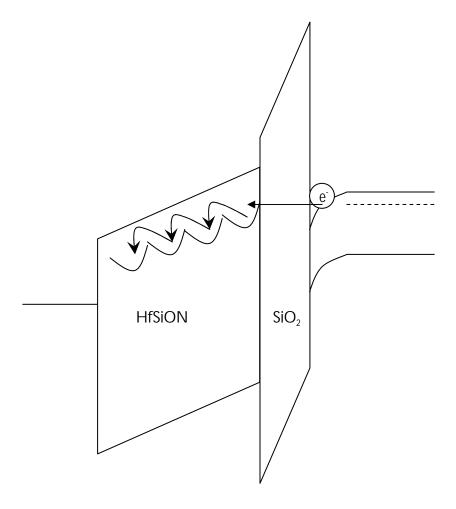

The band diagrams for nMOSFET transistors are drawn to scale in fig. 2.8 (using an estimated dielectric constant of 18 for HfO<sub>2</sub>). Since there is no interface degradation, we ruled out contribution from hole injection and assume that the observed parameter changes occur primarily due to electron injection. For a +2.6V stress (fig. 2.8), electron injection occurs near the high-k conduction band edge; electron trapping near the high K/SiO<sub>2</sub> interface causes the threshold voltage to increase while causing non-uniformity of the electric field across the HfO<sub>2</sub> layer and corresponding distortion of the conduction band bending. However, when the stress is removed, the trapped electrons start to de-trap

under the built-in electric field, under no external bias. The SILC characteristics are measured from 0 to 1.5V, during which time, de-trapping continues to occur, leading to increase in leakage current. The increase is more evident in the lower voltages when the current due to the de-trapping is comparable to the leakage current from the inversion layer. In summary, the leakage current measured during the J-V measurement is due to two sources:

- a) The inversion charge leakage through the oxide due to tunneling from the substrate [7].

- b) The trapped charge de-trapping At low voltages this is comparable to the leakage current from the inversion charge, as the inversion layer has not yet formed. At high voltages, the inversion layer leakage is much higher and therefore the effect is not evident.

At higher voltages (~1.5V), the leakage current from the inversion layer dominates and the increase due to the detrapping is not so evident. During the negative bias portion of the stress cycle, the electrons are de-trapped quickly and the J-V characteristics are reduced to their original levels.

Figure 2.8: a) Schematic of the energy band diagram (in scale) for 2.6V stress before and b) After electron trapping.

Alternatively stressing the sample with positive and negative biases for several cycles shows that the threshold voltage is entirely recovered at the end of every relaxation cycle (with no interface degradation), pointing to complete electron de-trapping while the leakage current shows "permanent" degradation after the first stress cycle, which probably indicates defect generation in or near the interfacial sub-oxide layer (fig. 2.9 & 2.10). This degradation, however, seems to saturate after the first stress cycle, indicating that permanent trap generation happens in the initial stages of the stress and gradually reduces.

Figure 2.9: When alternatively stressed between positive and negative biases, leakage current seems to saturate

Figure 2.10: Saturation of Leakage Current after the first cycle of stress, indicating damage in the first cycle.

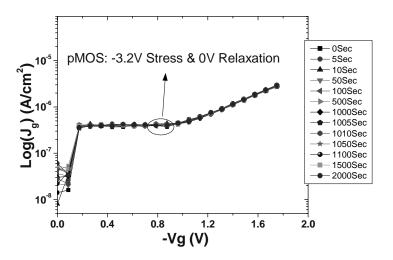

### 2.3.2 pMOS:

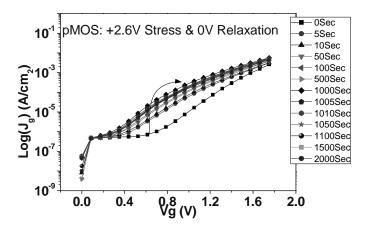

The SILC behavior during the negative bias stress is similar to negative bias stress in nMOS transistors. There is no detectable SILC until breakdown (fig. 2.11). This indicates that SILC in nMOS or pMOS is due to the same phenomenon, electron trapping and detrapping.

Effects of the positive bias stress are similar to the nMOS transistor - partially recoverable "low voltage" SILC is observed (fig. 2.12). Fig. 2.13 shows the band diagrams for pMOS.

Figure 2.11: pMOS in Inversion (Negative Bias).

Figure 2.12: pMOS in Accumulation (Positive Bias).

Figure 2.13: Band diagram for a) pMOS in accumulation at 2.6V b) pMOS in Inversion (-2.6V)

### 2.4 Conclusions

SILC behavior in 1.0 nm SiO<sub>2</sub>/3.0 nm HfO<sub>2</sub>/TiN nMOS and pMOS transistors was investigated. SILC dependence on stress time and polarity was found to closely correlate to the one of the threshold voltage in both nMOS and pMOS transistors. This suggests that the stress-induced reversible changes in both parameters are mostly determined by the same mechanism - reversible electron trapping in pre-existing defects. Small amount of traps are believed to be generated within or near the interfacial sub-oxide layer during the initial stages of stressing. Since electron trapping is much more efficient under the substrate injection stress, NMOS devices are expected to exhibit greater SILC degradation at normal operating conditions. However, most of this leakage current increase is due to trapping in charge traps in the bulk of the dielectric and as such, cannot be taken to indicate degradation of the film.

### 2.5 References:

- Crupi F, Degraeve R, Kerber A, Kwak DH, Groeseneken G: Correlation between Stress-Induced Leakage Current (SILC) and the HfO/sub 2/ bulk trap density in a SiO/sub 2//HfO/sub 2/ stack. In: Reliability Physics Symposium, 2004 Proceedings 42nd Annual 2004 IEEE International 2004; 2004: 181-187.

- Garros X, Leroux C, Reinibold G, Mitard J, Guillaumot B, Martin F, Autran JL: Reliability assessment of ultra-thin HfO/sub 2/ oxides with TiN gate and polysilicon-n/sup +/ gate. In: 2004; 2004: 176-180.

- 3. Ernest W. Yu JS: **Ultra-Thin Oxide Reliability**. In: *Reliability Physics Symposium*, 2005 Proceedings 43rd Annual 2005 IEEE International San Jose, Ca: IEEE; 2005.

- 4. Sze SM: **physics of semiconductor devices**, 2 edn. New Jersey: John Wiley and sonds; 1999.

- 5. Young CD, Bersuker G, Brown GA, Lysaght P, Zeitzoff P, Murto RW, Huff HR: Charge trapping and device performance degradation in MOCVD hafnium-based gate dielectric stack structures. In: 2004; 2004: 597-598.

- 6. Kerber A, Cartier E, Ragnarsson LA, Rosmeulen M, Pantisano L, Degraeve R, Kim Y, Groeseneken G: Direct measurement of the inversion charge in MOSFETs: application to mobility extraction in alternative gate dielectrics. In: 2003; 2003: 159-160.

- 7. Mizubayashi W, Yasuda N, Ota H, Hisamatsu H, Tominaga K, Iwamoto K, Yamamoto K, Horikawa T, Nabatame T, Toriumi A: Carrier separation analysis for clarifying leakage mechanism in unstressed and stressed HfAlO/sub x//SiO/sub 2/

- stack dielectric layers. In: Reliability Physics Symposium Proceedings, 2004 42nd Annual 2004 IEEE International: 2004; 2004: 188-193.

- 8. Jeff J. Peterson et al, **The Role of Interfacial Oxides in Mobility Improvement in HfO<sub>2</sub> Gate Stacks**. In: Semiconductor Interface Specialists Conference, 2004, 35<sup>th</sup>

Annual 2004 IEEE International: 2004.

## Chapter 3

## Mobility Issues in High-κ Dielectrics

#### 3.1 Introduction

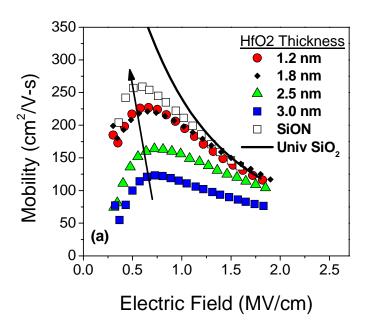

Mobility degradation in high κ gate stacks is a major concern. As the required EOT reaches sub-nm levels, the mobility is severely degraded to 50-60% of the universal mobility at room temperature. The presence of fixed charge in high-k dielectrics is known to have a negative effect on the mobility of high-k gate stacks through carrier scattering [1]. Additionally, charge trapping in the high-k dielectric has been shown to contribute to inversion charge loss in the channel, giving the appearance of mobility degradation[2]. Soft optical phonons were also suggested to contribute to mobility reduction in high-k gate stacks [3]. These mechanisms may be mitigated through the introduction of a bottom interfacial screening oxide between the high-k gate dielectric and the transistor channel[4]. In relation to the fixed high-k charge, the screening oxide increases the distance between the fixed charge in the high-k dielectric and the carriers, thereby reducing the scattering effect of the fixed charge [4]. In the case of soft optical phonons, the screening oxide acts as a barrier to dampen the phonon penetration and likewise reduce their scattering effect. On the other hand, it was shown that the properties of the interfacial oxide layer, in particular its oxygen content, might have significant impact on carrier mobility. Although high-k deposition on top of the oxide layer results in increase of its k-value, the screening oxide still constitutes a significant portion of the high-k gate stack equivalent oxide thickness (EOT). It is, therefore, critical to optimize thickness and quality of the screening oxide to achieve the required mobility.

## 3.2 Experiment and Results

### 3.2.1 Screening effect of Interfacial Oxides

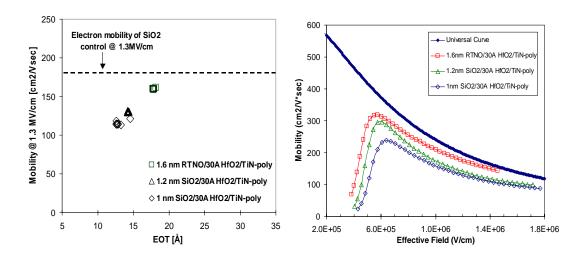

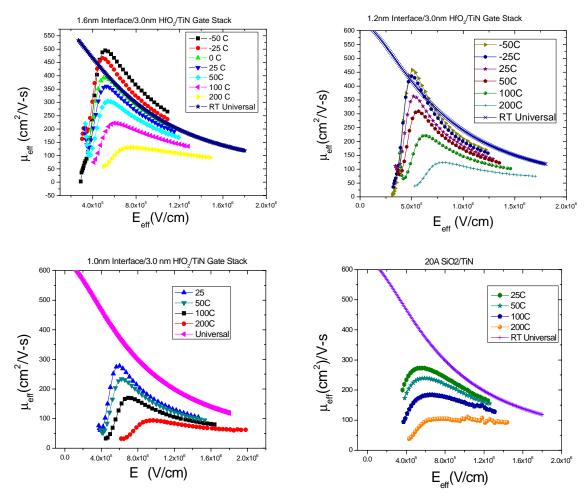

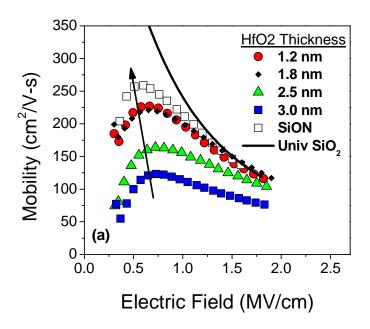

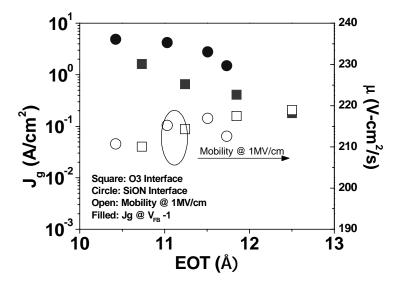

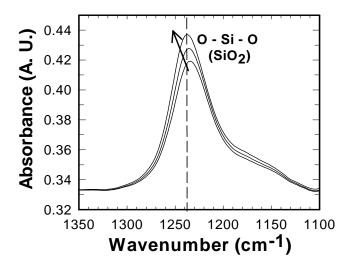

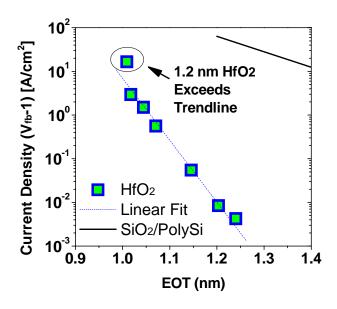

This study used 30Å ALD-HfO<sub>2</sub> gate dielectric transistors and capacitor structures on 200 mm Si <100> wafers, fabricated using a standard CMOS process with 1000°C/10s dopant activation and TiN gate electrode (Table 1 shows the complete transistor process) [11]. In order to evaluate the oxide thickness screening effect on transistor mobility, several bottom interface oxides are compared: a 1 nm ozonated oxide, a 1.2 nm thermal oxide, and a 1.6 nm rapid thermal nitrided oxide. After completion of CMOS processing, standard C-V and I-V analysis was done to evaluate EOT, CET, Vfb, Jg, and Vt. Mobility was extracted using the mob2d methodology. The data demonstrates that both the peak and high-field mobilities are increased through the incorporation of thicker screening oxides (fig. 3.1). Fig 3.1 (right) shows the high field mobility improvement.

Figure 3.1: The Effective Mobility of electrons in nMOS transistors increase with thinner interfacial layers.

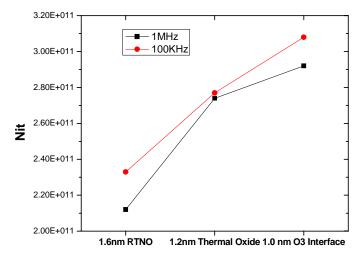

Fast transient single pulse Id-Vg measurements [5] were performed using a short voltage pulse at 2.5 V (from a minimum of –1 V), with a pulse width of 100 μs. The single pulse Id-Vg plots show absolutely no discrepancy from the DC Id-Vg plots, for all the three samples. This indicates that the screening effect of the oxide interfaces (1.0 nm, 1.2 nm and 1.6 nm) is sufficient to bring trapping down to a minimum (fig. 3.2). Charge pumping measurements, done at both 1 MHz and 100 KHz, show that N<sub>it</sub> values decreased monotonically with the thickness of the interfacial oxide (fig. 3.3). This indicates that part of the mobility degradation comes from fixed charge in the interface layer. The fixed charge increase could be due to hafnium incorporation inside the interface layer. The hafnium incorporation inside a thin interface layer would be more than that in thick interface layers.

Figure 3.2: Single Pulse Drain current for the 1.6nm RTNO oxide lies exactly on top of DC Id-Vg

Figure 3.3: The Interface State density increases as the interface thickness grows thinner.

## 3.3 Interface Effect on Mobility

The screening effect of the interface thickness on mobility was investigated. It was shown that both high field and peak mobility progressively increase as we increase the thickness of the interface from 1.0nm to 1.6nm. Interface thickness of 1.6nm is enough to make the interface sufficiently like SiO<sub>2</sub>, so that the high field mobility is the same as that of SiO<sub>2</sub> with TiN. The N<sub>it</sub> values increase as the thickness of the interface is decreased. Charge trapping properties were investigated and it was found that DC Id-Vg curves coincide with the single-pulse Id-Vg curves, indicating that the charge trapping effect was minimized due to the presence of even a 10Å Interface.

## 3.4 Mobility Degradation Study

### 3.4.1 Mobility Vs Temperature: Effect of phonon Scattering

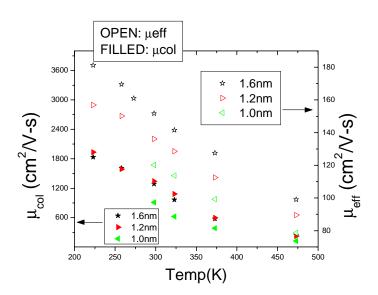

To qualitatively and quantitatively assess the degradation effects of the high K on the electron intrinsic mobility, electron mobility in nMOSFETs was measured as a function of temperature. There is no significant apparent mobility degradation in the samples due to charge trapping. Therefore, the DC mobility curves are used for the calculations (fig 3.2). Both peak mobility and high-field mobility (at 1MV/cm) decreased with temperature (fig 3.4). However, there were subtle differences in the high-field mobility-temperature relationships between the different interfaces.

Figure 3.4: Mobility vs. temperature measurements for the different interfaces

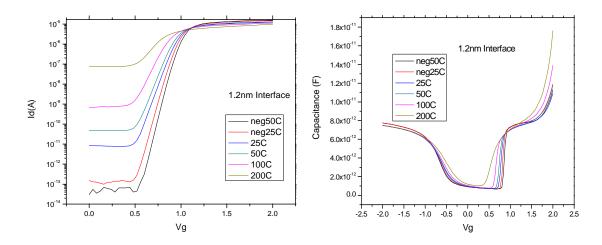

Fig. 3.5 shows  $I_d$  vs.  $V_g$  and capacitance vs.  $V_g$  for different temperatures for the 1.2nm Interface. As can be seen, the interface state effects on CV and IdVg measurements are lower at lower temperatures (the curve "slewouts" are lesser at lower temperatures)

Figure 3.5: (a) Subthreshold swing improvement with temperature (b) CV "slewout" with temperature

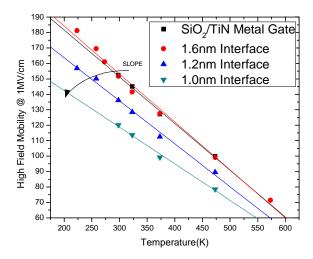

In the high-field region (1MV/cm), the mobility dependence on temperature is maximum for the 1.6nm Interface, which lies exactly on top of the  $SiO_2/TiN$  mobilities (fig 3.6). This indicates that the degradation mechanisms for both are identical and a 1.6nm interfacial layer is enough to make the gate stack sufficiently  $SiO_2$ -like, as far as mobility is concerned.

Figure 3.6: High field mobility dependence on temperature reduces steadily with thinner interface.

Quantitative assessment of the mobility is proposed to be investigated. Zhu *et al* [6] used Matthiesen's rule to approximately estimate the effect of coulombic, phonon and surface roughness scattering on HfO<sub>2</sub> samples with metal gates. According to Matthiesen's rule:

$$\frac{1}{\mu_{eff}} = \frac{1}{\mu_{phonon}} + \frac{1}{\mu_{coulomb}} + \frac{1}{\mu_{SurfaceRoughness}} \dots$$

Equation 3.1

: Matthiesen's rule

The surface roughness term can assumed to be constant with temperature and furthermore,

it can be assumed that the surface roughness is approximately the same as it is with a  $SiO_2/Poly-Si$  gate stack [7]

Numerical calculation of  $\mu_{SR}$  can be done using the equation for SiO<sub>2</sub>:

$$\mu_{SR} = B.E_{eff}^{-2.6}$$

Equation 3.2

:Surface Roughness

$B = 4.5 \times 10^{19}$ : all the parameters are in S.I units.

This different scattering mechanisms are dominant at different field regimes in tradition SiO<sub>2</sub> gate stacks and are illustrated in fig. 3.7 [6].

Figure 3.7: Figure illustrating different scattering modes [6]

The coulomb scattering component is illustrated in Fig. 3.7. The coulomb scattering component is extracted, as explained by extrapolating the low field mobility to 1MV/cm, by the fitting the mobility curve in that region to a straight line. This assumes that coulomb

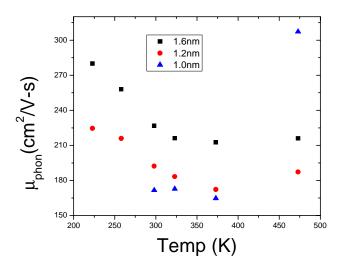

scattering is the dominant scattering mechanism in the low field region and depends linearly on the field. As can be seen, the coulomb scattering term is not insignificant at room temperature and higher temperatures, especially in the thin films. Using matthiesen's rule and substituting for the coulomb scattering term and the surface roughness term, we can extract the phonon scattering term at 1MV/cm [3, 8]. This has been plotted in fig. 3.8 and fig. 3.9. As can be seen the phonon mobility is lower than the coulombic mobility and therefore is more dominant than coulomb scattering. The phonon mobility is independent on temperature in the high temperature regime and for all three interface thicknesses. This leads to the lower temperature dependence of effective mobility in the thinner interfaces.

Figure 3.8:  $\mu_{coulomb}$  reduces with temperature and is a significant portion of the scattering in HfO<sub>2</sub> gate stacks.

Figure 3.9: Phonon scattering reduces with temperature in the low temperature regime and flattens out in the high temperature regime

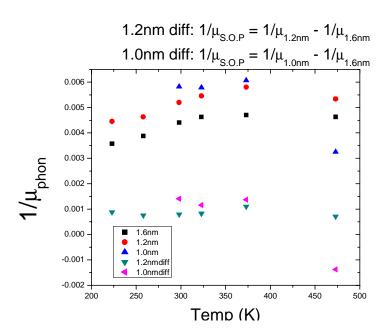

In order to estimate the soft optical phonon contribution in the high- $\kappa$  devices, the phonon mobility of the thinner interface devices is subtracted from the 1.6 nm interface devices, assuming that the soft optical phonon mode is insignificant in the thick interface device (the mobility response to temperature is similar to that of SiO<sub>2</sub>). We see in fig. 3.10 that there is a substantial soft optical phonon scattering in high- $\kappa$  devices and as expected, this scattering is independent of the temperature [9].

Figure 3.10: The soft optical mode is small in the 1.2nm and 1.0nm interface devices and is not comparable to the regular phonon mode.

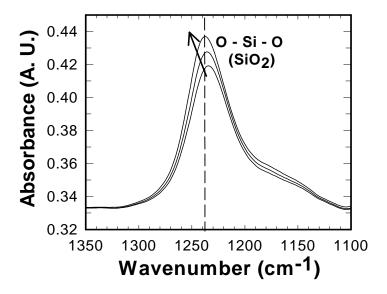

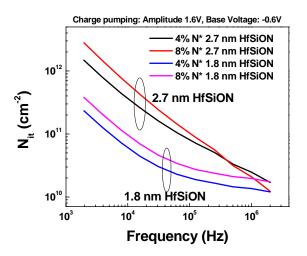

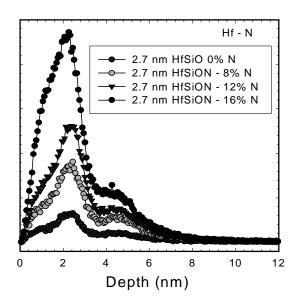

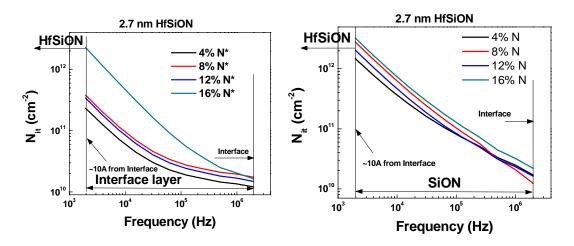

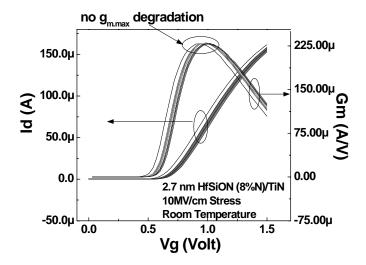

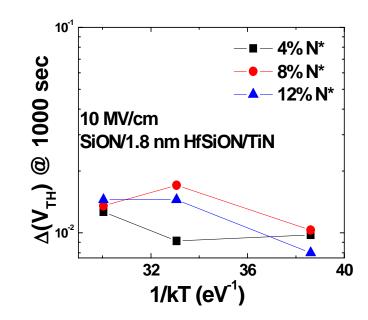

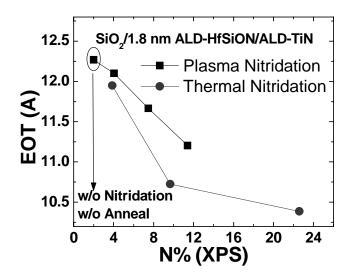

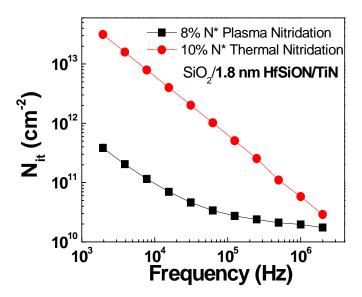

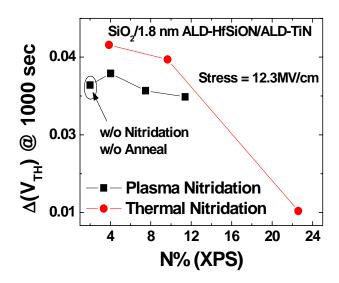

# 3.5 Mobility Improvement Techniques