Copyright

by

Xuliang Han

2003

# The Dissertation Committee for Xuliang Han certifies that this is the approved version of the following dissertation:

## Fan-Out Equalized Shared Optical Backplane Bus

| Committee:              |  |

|-------------------------|--|

| Ray T. Chen, Supervisor |  |

| Joe C. Campbell         |  |

| G. Jack Lipovski        |  |

| Michael F. Becker       |  |

| Paul S. Ho              |  |

## **Fan-Out Equalized Shared Optical Backplane Bus**

by

Xuliang Han, B.S., M.S.E.

#### **Dissertation**

Presented to the Faculty of the Graduate School of

the University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

**Doctor of Philosophy**

The University of Texas at Austin

December 2003

## Acknowledgements

I would like to thank the faculty and staff of the Microelectronics Research Center and the Department of Electrical and Computer Engineering at The University of Texas at Austin for providing me with such an intellectually stimulating environment to conduct my research and pursue my graduate education. I greatly appreciate my advisor, Dr. Ray T. Chen, for his support and guidance in my research work. Many thanks also go to my committee members, Dr. Joe C. Campbell, Dr. G. Jack Lipovski, Dr. Michael F. Becker, and Dr. Paul S. Ho, for their insightful advices on my dissertation.

I would like to acknowledge the productive collaborations with Dr. Gicherl Kim, a former student in the Optical Interconnect Group and now a research engineer at Omega Optics. With his agreement, some figures and experimental results in this dissertation are adapted from his publications. I also want to thank other group members for their help over the years.

Finally, I would like to express my gratitude to my parents and brother for their lifetime support and encouragement.

### Fan-Out Equalized Shared Optical Backplane Bus

| Publication | No. |  |  |  |

|-------------|-----|--|--|--|

|             |     |  |  |  |

Xuliang Han, Ph.D.

The University of Texas at Austin, 2003

Supervisor: Ray T. Chen

Optics is distinguished for its interconnect capability. A variety of optical interconnect technologies have been successfully employed in the real applications where the conventional implementations that are exclusively based on electrical interconnects have become insufficient, and the boundary demarcating the electrical and optical domain is being further pushed down in the interconnect hierarchy. Many researches have projected an imminent bottleneck throttling the board-to-board data transfers. Accordingly, an opportunity exists for the continuing exploitation of optics to complement or even replace the conventional electrical backplanes. The most prominent benefit of utilizing optics is the tremendous gain in the bandwidth capacity. From the architecture point of view, however, three fundamental optical methodologies, optical waveguide interconnects, free-space optical interconnects, and substrate-guided optical interconnects, have a huge discrepancy in how effectively the obtained bandwidth gain would improve the overall system performance. The approaches that are based on optical waveguide or free-space interconnects provide only the point-to-point topology, in turn the various proposed architectures are essentially an optical point-to-point switched backplane. In contrast, the approaches that are based on substrate-guided optical interconnects can effectively fulfill

the shared bus topology, and thus an optical backplane bus can be implemented. In this dissertation, the comparative examinations specifically point out that optical backplane bus has many considerable advantages over optical point-to-point switched backplane. An innovative optical backplane architecture, optical centralized shared bus, is created based on substrate-guided optical interconnects, which utilizes the beneficial physical characteristics of optics while retaining the desirable architectural properties of the shared bus topology. Therefore, it is projected that the bandwidth gain would be maximized. Superior to other optical shared bus architectures, this innovatively designed optical backplane bus can accomplish equalized fan-outs across the entire architecture in an elegant manner. This significant merit can substantially ease the overall system integration. In this dissertation, the equalized bus fan-outs are successfully established on the fabricated optical interconnect layer. To further verify the feasibility of optical centralized shared bus architecture in the practical scenarios, two research prototypes, a microprocessor-to-memory interconnect demonstrator and a centralized shared-memory multiprocessing emulator, are constructed with the physically characterized optical centralized shared bus.

## **Table of Contents**

|           |                                                                     | Page |

|-----------|---------------------------------------------------------------------|------|

| Acknowled | gements                                                             | V    |

| Abstract  |                                                                     | vi   |

| Chapter 1 | Introduction                                                        | 1    |

| 1.1       | Interconnect Hierarchy                                              | 1    |

| 1.2       | Overview of Backplane Topologies                                    | 3    |

| 1.3       | Interconnect Bottleneck                                             | 5    |

| 1.4       | Advantages of Optical Interconnects                                 | 8    |

| 1.5       | Overview of Optical Interconnect Methodologies                      | 11   |

| 1.6       | Advantages of Optical Backplane Bus vs. Optical Point-to-Point      |      |

|           | Switched Backplane                                                  | 18   |

| 1.7       | Research Contributions                                              | 19   |

| 1.8       | Dissertation Outline                                                | 21   |

| Chapter 2 | Optical Centralized Shared Bus Architecture                         | 22   |

| 2.1       | Overview of Optical Shared Bus Architectures                        | 22   |

| 2.2       | Architectural Description of Optical Centralized Shared Bus         | 24   |

| 2.3       | Characteristics of Optical Centralized Shared Bus Architecture      | 26   |

| 2.4       | Summary                                                             | 30   |

| Chapter 3 | Optical Interconnect Layer Implementation                           | 31   |

| 3.1       | Configuration of Optical Interconnect Layer                         | 31   |

| 3.2       | Overview of Volume Holographic Gratings                             | 32   |

| 3.3       | Theoretical Analysis of Grating Formation Procedure within          |      |

|           | Dry Photopolymer Films                                              | 37   |

| 3.4       | Experimental Characterization of Grating Formation Procedure within |      |

|           | Dry Photopolymer Films                                              | 39   |

| 3.5       | Fabrication of Waveguide Holograms                                | 47  |

|-----------|-------------------------------------------------------------------|-----|

| 3.6       | Demonstration of Equalized Bus Fan-Outs                           | 48  |

| 3.7       | Power Budget Evaluation                                           | 50  |

| 3.8       | Bandwidth Characterization of Optical Interconnect Layer          | 52  |

| 3.9       | Summary                                                           | 54  |

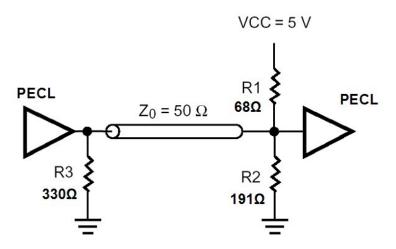

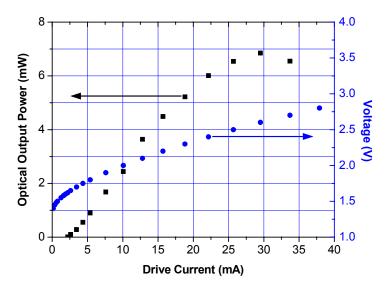

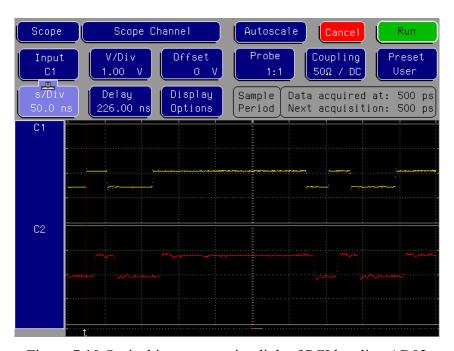

| Chapter 4 | Electro-Optical Interface Implementation                          | 55  |

| 4.1       | Introduction                                                      | 55  |

| 4.2       | Overview of High-Speed PCB Layout Design Techniques               | 55  |

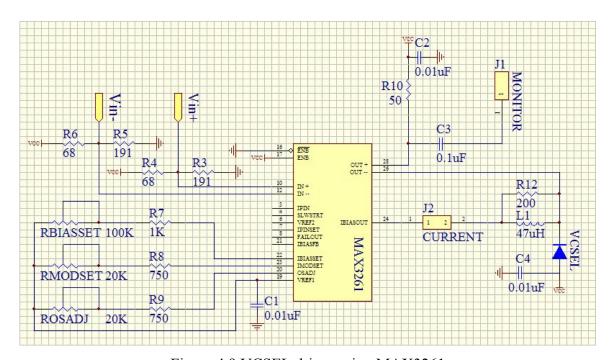

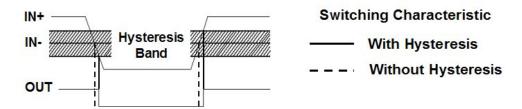

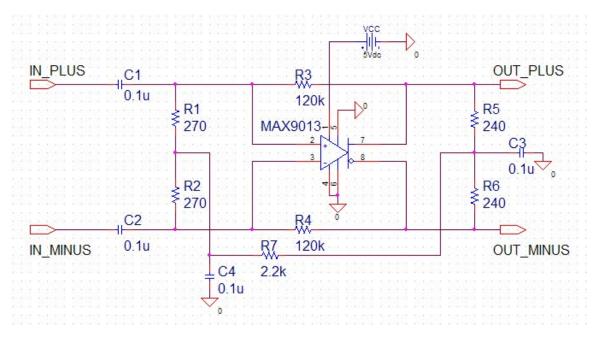

| 4.3       | Transmitter Implementation Examples                               | 60  |

| 4.4       | Receiver Implementation Examples                                  | 63  |

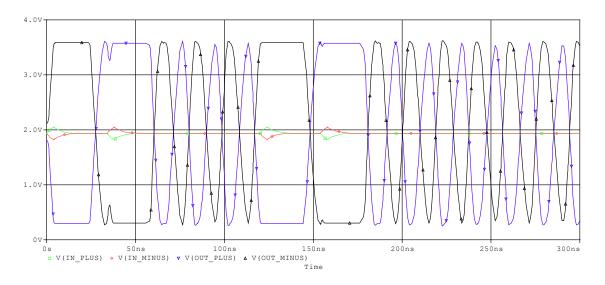

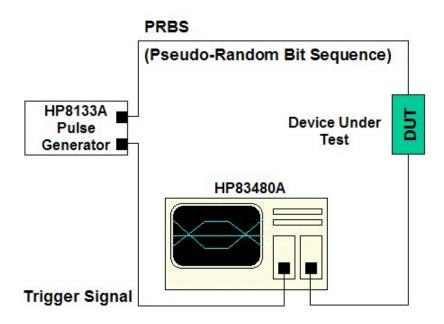

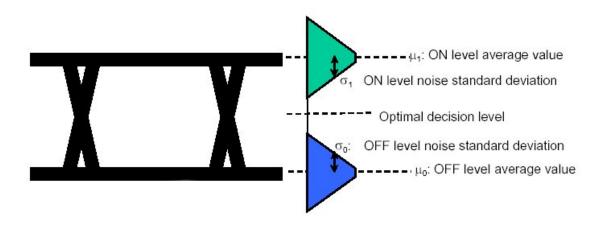

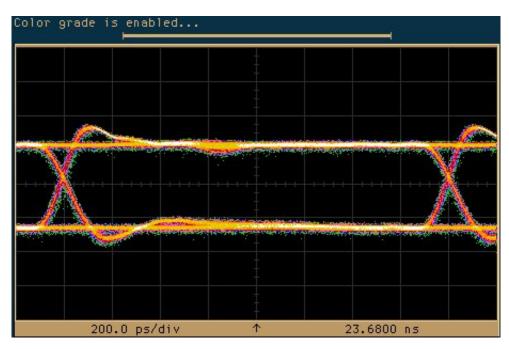

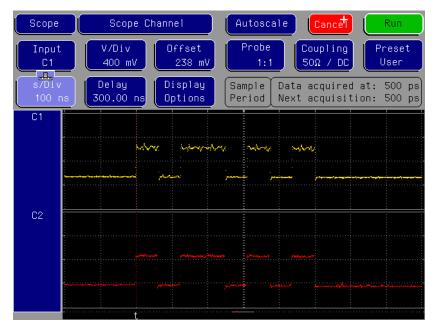

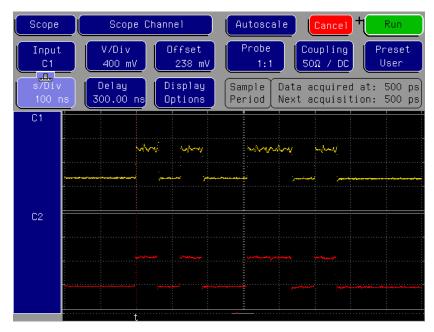

| 4.5       | Eye Diagram Measurement                                           | 67  |

| 4.6       | Summary                                                           | 75  |

| Chapter 5 | System Demonstration Strategy                                     | 76  |

| 5.1       | Introduction                                                      | 76  |

| 5.2       | Uniprocessing System                                              | 77  |

| 5.3       | Multiprocessing System                                            | 78  |

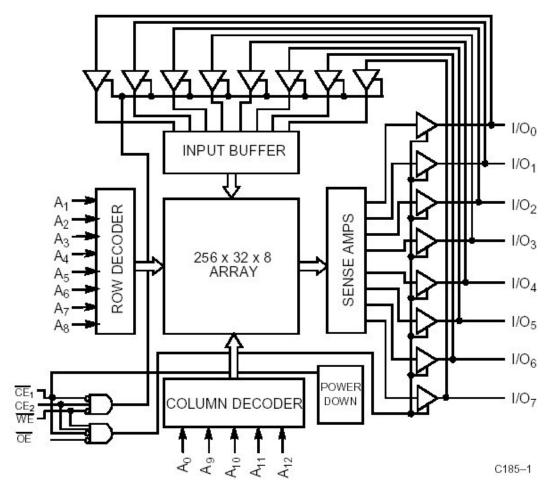

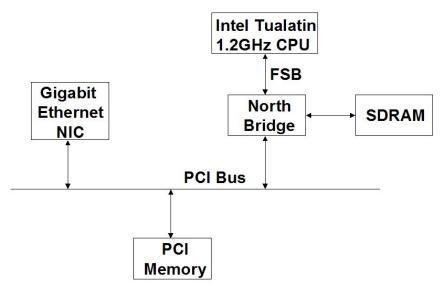

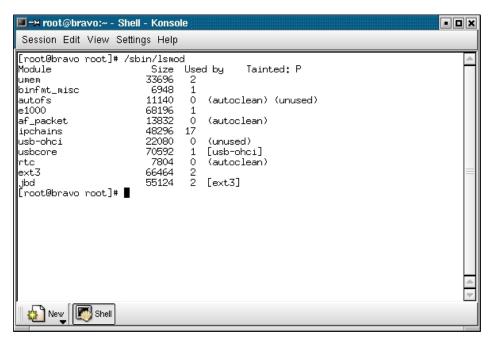

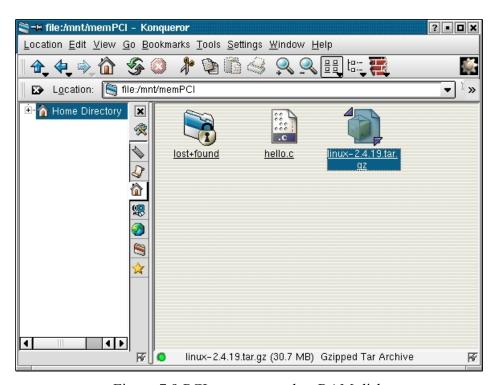

| Chapter 6 | Microprocessor-to-Memory Interconnect Demonstration               | 79  |

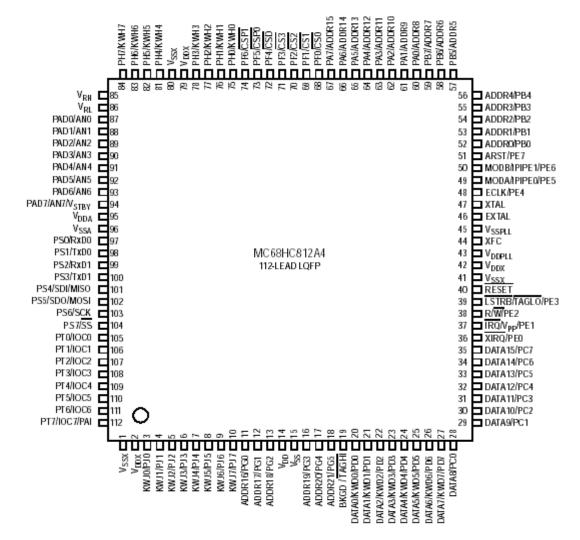

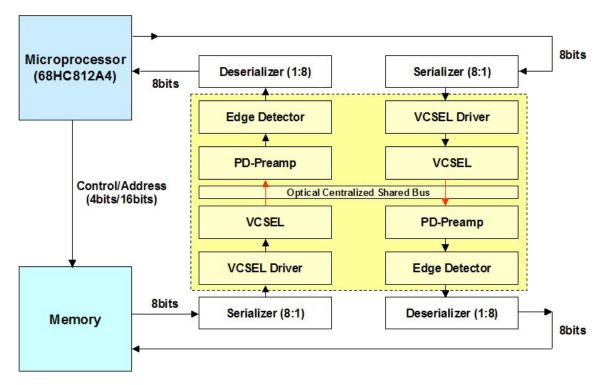

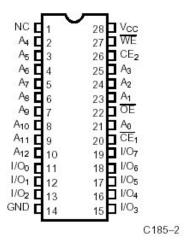

| 6.1       | Introduction                                                      | 79  |

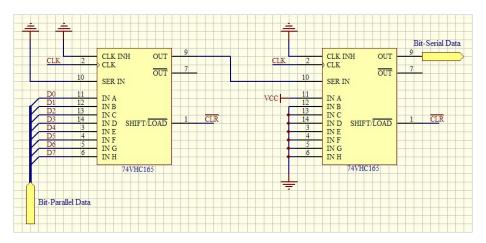

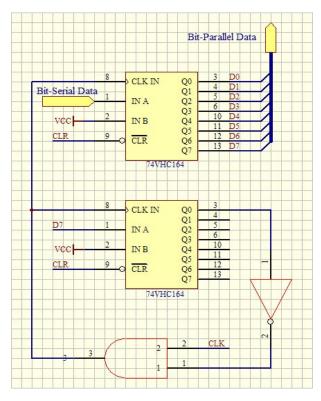

| 6.2       | Microprocessor-to-Memory Interface Design                         | 81  |

| 6.3       | Microprocessor-to-Memory Interconnect Demonstration               | 86  |

| 6.4       | Discussions                                                       | 89  |

| 6.5       | Summary                                                           | 89  |

| Chapter 7 | Centralized Shared-Memory System Demonstration                    | 90  |

| 7.1       | Overview of Multiprocessor Programming Models                     | 90  |

| 7.2       | Centralized Shared-Memory System on Optical Centralized Shared Bu | s92 |

| 7.3       | PCI over Optical Centralized Shared Bus Architecture              | 92  |

| 7.4       | Centralized Shared-Memory System Demonstration                    | 98  |

| 7.5       | Discussions                                                       | 101 |

| 7.6       | Summary                                                           | 102 |

| Chapter 8   | 103                             |     |

|-------------|---------------------------------|-----|

| 8.1         | Summary                         | 103 |

| 8.2         | Recommendations for Future Work | 105 |

| Bibliograph | ny                              | 107 |

| Vita        |                                 | 115 |

## **Chapter 1 Introduction**

#### 1.1 Interconnect Hierarchy

Interconnects become an even more dominant factor in telecommunication backbones, broadband local data networks, high performance computing (HPC) systems, and state-of-the-art signal processing engines. Table 1.1 represents a hierarchical perspective on interconnects and the pertinent implementation technologies [1], [2]. Distinguished by the widely discrepant distance, the interconnect hierarchy may be coarsely divided into four levels: telecommunications, data communications, board-to-board interconnects, and chip-to-chip interconnects.

|                              | Chip-to-<br>Chip        | Board-to-<br>Board                              | Data Links                | Telecom           |

|------------------------------|-------------------------|-------------------------------------------------|---------------------------|-------------------|

| Electrical<br>Implementation | РСВ                     | Backplane                                       | TP/Coax                   | TP/Coax           |

| Optical<br>Implementation    | Waveguide<br>Free-Space | Waveguide<br>Free-Space<br>Substrate-<br>Guided | SM/MM Fiber<br>Free-Space | SM Fiber          |

| Optical Source               | 850nm<br>VCSEL          | 850nm<br>VCSEL                                  | 1.3/1.55μm<br>LD          | 1.3/1.55μm<br>LD  |

| Interconnect<br>Distance     | <1cm                    | <10cm                                           | <1km                      | >1km              |

|                              | -                       |                                                 |                           | Optical<br>Domain |

Table 1.1 Interconnect hierarchy and pertinent implementation technologies

Since the interconnect distance has a considerable influence on the bandwidth capacity of the physical layer, the continuous revolution of the interconnect solutions is clearly reflected by the optical/electrical domain boundary that is being further pushed down in the interconnect hierarchy. The most significant benefit of utilizing optical interconnects is the tremendous gain in the bandwidth capacity. To meet the ever-increasing demand on

bandwidth, a variety of optical interconnect technologies have been explored, and some of them have been successfully employed in the real applications where the conventional implementations that are exclusively based on electrical interconnects have become insufficient. In telecommunications, there is no argument about the success of optics. The approaches that are based on optical fibers have become the dominant solutions. The extremely low attenuation of optical fibers has a major influence on their replacement of coppers as the interconnect media. Now optical rack-to-rack interconnects are emerging on the horizon, e.g., in HPC clusters [3] and core network routers [4]. Many researches have projected an imminent bottleneck throttling the board-to-board data transfers [1], [5], [6]. Accordingly, an opportunity exists for the continuing exploitation of optical interconnects to complement or even replace the conventional electrical backplanes. Below the chip-to-chip level where latency is at a premium, optical interconnects might not be competitive with their electronic counterparts [7]. But it is rather early at this stage to predict how far down in the interconnect hierarchy optics would penetrate.

In both electrical and optical domains, with the dramatically decreasing distance down in the interconnect hierarchy, system requirements such as bandwidth, latency, fan-out quality, power consumption, heat dissipation, complexity, cost, reliability, and so on are widely discrepant. In turn, the matched interconnect solutions vary from one hierarchical level to another. For example, the distance involved in telecommunications and data communications is so long that attenuation and dispersion are of major concerns. As a result, the 1.3/1.55µm lasers are selected as the primary optical sources since a normal optical fiber has the lowest attenuation at 1.55µm and the lowest dispersion at 1.3µm. On the other hand, the distance involved at and below the board-to-board level is so short that attenuation and dispersion are of minor concerns, and the choice of the wavelength is mainly dependent on the intrinsic properties of the laser sources themselves, including thermal sensitivity, quantum efficiency, and so on. Thus, the 850nm lasers, especially the VCSELs (vertical-cavity surfacing-emitting lasers), are singled out for use [8]. Moreover, many proven optical implementation technologies in telecommunication backbones, e.g., dense wavelength division multiplexing (DWDM), may not even be viable at the board-

to-board level simply because these approaches might be prohibitively expensive. Thus, one of the most challenging research objectives of the day is to engineer and justify the appropriate optical implementation technologies at each hierarchical level.

#### 1.2 Overview of Backplane Topologies

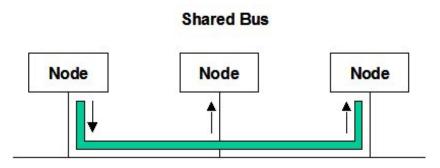

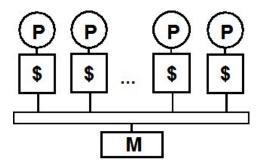

The backplane topologies may be generically categorized into two basic types: shared bus and switched medium, as respectively illustrated in Figure 1.1 and 1.2. By combining these two fundamental blocks in different manners, more sophisticated topologies can be obtained.

#### Shared Bus

Figure 1.1 Schematic of shared bus topology

Certainly the easiest way to connect multiple nodes is to have them share a single interconnect medium, as illustrated in Figure 1.1. By snooping on the shared media, all subscribed daughter boards can simultaneously receive the same information. Thus, the routing functionality is simply fulfilled in a broadcast fashion without involving any explicit routing delay. The shared bus is a direct network, and thus possesses very high connectivity. Each data transfer phase incurs only a single-hop delay. This feature is highly desirable in minimizing the interconnect latency. In a centralized shared-memory multiprocessing system, all cache controllers that are respectively embedded in each microprocessor simultaneously monitor every data transaction proceeding on the shared

memory bus. In this manner, cache coherence can be effectively maintained [9]. The shared bus is inexpensive to implement since a lot of hardware are shared.

In the electrical domain, the prominent bottleneck of the shared bus arises from its low bandwidth capacity. There are many frequency-dependent physical factors, including power loss, transmission line effects, electromagnetic interference (EMI), and so on, that considerably limit the maximum speed of an electrical backplane bus at a given line density. Furthermore, these restrictions aggravate with the extended bus length and the increased number of bus fan-outs. Another topological deficit originates from the medium access control (MAC) manner of the shared bus. Only one daughter board can deliver data on the shared medium at a time, and thus the shared bus topology possesses little parallelism.

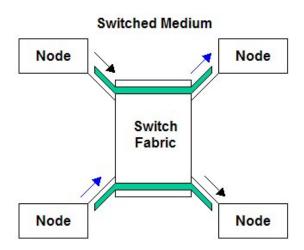

#### Switched Medium

Figure 1.2 Schematic of switched medium topology

The alternative to sharing a single interconnect medium is to have a dedicated line from the source daughter board to a switch that in turn provides a dedicated line to each destination daughter board, as illustrated in Figure 1.2. Thus, the routing functionality is handled in a point-to-point fashion. The switch maintains a routing table that contains the

overall point-to-point connectivity information, and updates this table either on a regular basis or upon receiving the explicit requests [10]. By looking up the routing table with the decoded address information from the received data packet, the switch can identify the correct output port(s) to the intended destination board(s). Better than the shared lines, the dedicated lines do not experience any unnecessary fan-outs, considerably saving the overall power budget. The point-to-point interconnect topology can somewhat relieve the physical restrictions in the electrical domain, and thus allows the dedicated electrical lines to run at a faster speed at a given line density than the shared electrical lines. In some circumstances, with the intelligent traffic scheduling, a switch may coordinate multiple pairs of nodes to communicate simultaneously. This beneficial potential of high topological parallelism gives these interconnections much higher aggregate bandwidth than the speed of one shared bus line to one node.

The switched medium is an indirect network since all data transfers must pass through an intermediate switching node. Each data transfer phase incurs a double-hop delay and a routing delay that mainly consists of the time spent on looking up the routing table. By its nature, the routing overhead increases in proportional to the size of the table, which is directly determined by the total number of the daughter boards subscribed to the switch. Replacing a single switching node with a multi-stage switch network becomes necessary in order to be able to retain the size of the routing table in each individual switch at a moderate scale, in turn, to save the routing delay. With this approach, however, the hop overhead is expected to rise with the increased number of the intermediate switching nodes. Thus, it is rather difficult to minimize the overall interconnect latency. Another significant drawback of the switched medium topology is related with the implementation cost. The additional involvement of many expensive devices, including switches, line transceivers, dedicated lines, and so on, considerably increases the overall system cost.

#### 1.3 Interconnect Bottleneck

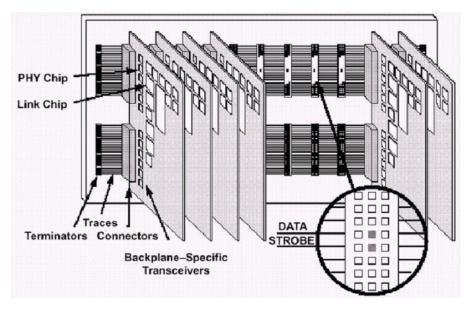

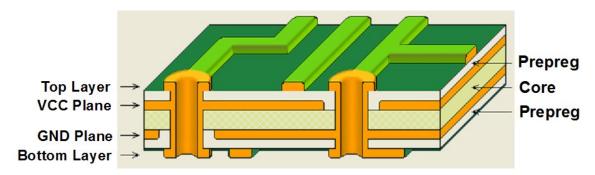

At the board-to-board level, the required interconnects are usually provided by an electrical backplane bus, as illustrated in Figure 1.3. A daughter board can be simply

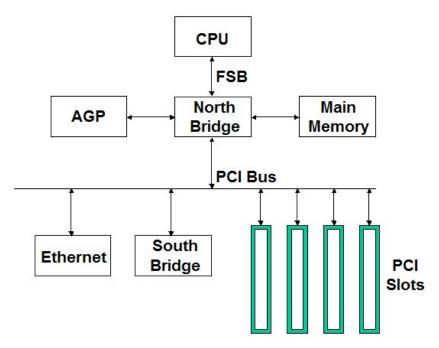

plugged into the designated backplane connector to obtain the access to the shared media, i.e., the electrical bus lines on the backplane. As previously pointed out, there are many frequency-dependent physical factors that considerably limit the maximum speed of an electrical backplane bus at a given line density. Furthermore, these restrictions aggravate with the extended bus length and the increased number of bus fan-outs. In consequence, a typical electrical backplane bus operates at a frequency of less than 200MHz. Still in the electrical domain, many new techniques are being sorted to either overcome this speed hurdle or circumvent it by making more efficient use of the available bandwidth. For example. Intel is targeting at a physical signaling technique quad-pumping the data transfers over a 200MHz clocked system bus and a buffering scheme allowing for the sustained data transfers at 800Mbps [11]. Although at the considerable expense of the sophisticated digital signal processing facilities, the fundamental physical frequency is still not likely to exceed 500MHz in the practical implementations. This bandwidth deficit severely diminishes other merits of the shared bus topology, and will definitely throttle the data transfers at the board-to-board level in the interconnect hierarchy. Below this level, the performance of the advanced microprocessors continues to improve at a rapid pace. For example, the on-chip frequency of the Intel Pentium 4 microprocessor has surpassed 3GHz in 2003. In contrast, although the maximum front side bus (FSB) speed can reach the so-called 800Mbps at the considerable expense of the sophisticated quadpumping and buffering scheme, the physical off-chip clock frequency is still not able to exceed 200MHz. This problem of computing speed outpacing interconnect capacity is becoming more and more severe in the electrical domain. Meanwhile, as multiprocessing comes into the mainstream, the demand on board-to-board interconnects becomes even more critical. In the design of a multiprocessing system, one significant challenge is to effectively provide the communications among several processes that are simultaneously executing on multiple microprocessors. Above the board-to-board level, the rapid development of local data communications, including 10 Gigabit Ethernet [12], Fiber Channel [13], RapidIO [14], InfiniBand [15], PCI Express [16], and so on, is flushing more and more data into a single linecard within a shorter and shorter time interval. Consequently, in the electrical domain, an imminent throttling bottleneck is projected at the board-to-board level in the interconnect hierarchy.

Figure 1.3 Typical electrical backplane bus

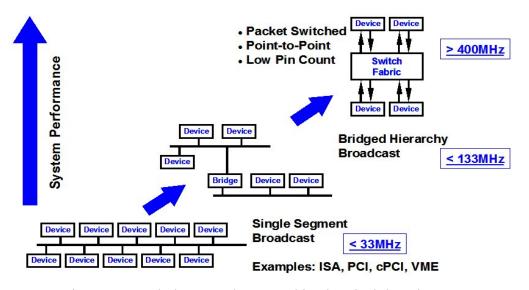

The electrical backplane topology has been changed from the simple shared bus to the complicated switched medium, as illustrated in Figure 1.4 [14]. Employing a switched medium allows a backplane to operate at a higher frequency at a given line density than an electrical backplane bus, because the dedicated point-to-point lines are in some degree less prone to the frequency-dependent physical restrictions than the shard bus lines. Also, with the intelligent traffic scheduling in some circumstances, a switch may coordinate multiple pairs of nodes to communicate simultaneously. This topological parallelism gives these interconnections much higher aggregate bandwidth than the speed of one shared bus line to one node. These two benefits are the essential rationales behind the backplane topology trend in the electrical domain. As previously discussed, however, the switched medium is an indirect network, so it cannot carry out multicast/broadcast as effectively as the shared bus. From the architecture point of view, this topological deficit critically restricts the overall gain brought from the increased aggregate bandwidth. Each

data transfer phase inevitably incurs a routing overhead, which makes it rather difficult to minimize the overall interconnect latency. In [17], the statistics of the memory read latency, respectively, in a medium and a large size switch-based multiprocessing system (Sun Fire 12K and 15K) shows that the wire delay is only moderate fraction of the total memory read latency, while the transactions through switches and the multicast/broadcast actions to maintain cache coherence are a significant fraction, also, the delay associated with switching and cache coherence increases with the system scale more rapidly than the wire delay. Meanwhile, the additional involvement of many expensive devices, including switches, line transceivers, dedicated lines, and so on, considerably increases the overall system cost. Therefore, an innovative technology that can provide sufficient bandwidth capacity while at the same time retaining the essential merits of the shared bus topology is highly desirable.

Figure 1.4 Backplane topology trend in electrical domain [14]

#### 1.4 Advantages of Optical Interconnects

Optics has been well known for its interconnect capability. To meet the everincreasing demand on bandwidth, a variety of optical interconnect solutions have been explored, and some of them have been successfully employed in the real applications where electrical interconnect solutions have become insufficient. As shown in Table 1.1, the continuous revolution of the implementation technologies is clearly reflected by the optical/electrical domain boundary that is being further pushed down in the interconnect hierarchy. Accordingly, optical interconnects are being actively investigated as a primary complement or even alternative to electrical interconnects with the purpose to prevent the projected bottleneck from throttling the data transfers at the board-to-board level. From one hierarchical level to another, system requirements, including bandwidth, latency, fanout quality, power consumption, heat dissipation, complexity, cost, reliability, and so on, undergo considerable changes. In consequence, an implementation technology may have widely discrepant effects at different hierarchical levels. Pertinent to the interconnections at the board-to-board hierarchical level, the physical merits of optics mainly include [1], [18], [19], [20], [21]:

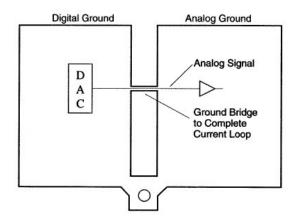

- (1) No current-loop associated problems. Whenever an electrical signal switches, an AC current is introduced at the signal switching edge. A current return path, which is dictated for least impedance, is required to complete the loop. In the electrical domain, one of the most important concerns in the high-speed board design is to minimize various current-loop associated problems. If not appropriately handled, the interaction among these dynamic current loops may aggravate ringing, crosstalk, and radiation. In turn, these current-loop associated problems can severely degrade the single integrity. In contrast, there are no such current loops in the optical domain, and thus no current-loop associated problems present in the optical interconnection links either.

- (2) Intrinsic immunity to electromagnetic interference (EMI). EMI is detrimental to nearly any electronic device, and the impact becomes more critical with the increased frequency. Meanwhile, the high-speed electrical wires can generate severe EMI as the harmful high-frequency noise in the surrounding environment. In contrast, the optical interconnection links are naturally insensitive to EMI, and do not radiate any EMI.

- (3) Little liability to the transmission line effects. On the high-speed board, all signal wires are practically transmission lines. To provide the best medium for the transfers of electrical signals on the board, the impedance along the entire electrical transmission line

must remain unchanged. However, the essential functionality of an electrical backplane is to provide a large number of fan-outs. In such a scenario, it is nearly impossible to obtain an electrical transmission line with constant impedance in the practical implementations. Along a transmission line with physical discontinuities, the original signal is subject to reflections wherever the impedance changes. If not properly controlled, these electrical reflections may interfere with signaling, resemble ring, cause false clocking, or destroy system functionality. In order to suppress the disturbing reflections, a bus line must be properly terminated at every stub. At each termination, however, considerable power is consumed to bring the voltage above the predefined logic threshold level. In contrast, because of the enormous carrier frequency of optical signals, the transmission line effects have little negative impacts in the optical interconnection links.

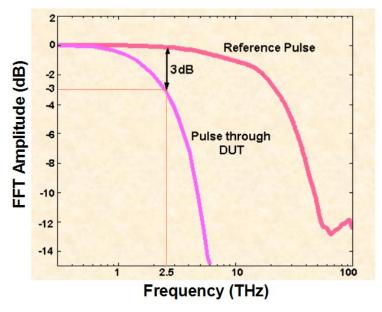

These physical merits make optics a competitive candidate to provide the required interconnects at the board-to-board level. The most significant benefit of utilizing optical interconnects is the tremendous gain in the bandwidth capacity. In particular, the bandwidth capacity of a single optical interconnect line was experimentally characterized to be approximately 2.5THz [22]. Meanwhile, less power consumption per line is expected [23]. Because optics does not involve any current-loop associated problem or EMI, the crosstalk among the adjacent optical channels is largely reduced. Therefore, much higher interconnection density can be achieved by utilizing optical interconnects. Furthermore, the prominent progress in the fabrication of the two-dimensional (2-D) vertical-cavity surface-emitting laser (VCSEL) array devices and the 2-D photodiode array devices initiates the exploitation of real three-dimensional (3-D) interconnects. By adding another dimension for the data transfers, the haunting problem associated with pin-out may be relieved. By stacking multiple levels of active devices directly on top of one another, the interconnect distance can be minimized. This real 3-D approach opens many new areas of research. A low-threshold high-efficiency single-transverse-mode 2-D VCSEL array device with a high degree of uniformity was demonstrated [24]. The output of a VCSEL has much smaller beam divergence than an edge-emitting laser, and more importantly, is circular symmetric, which largely eases the integration of a VCSEL array

device with a microlens array to further reduce the beam divergence [25]. The planar structure of a VCSEL array makes it easy to integrate with a CMOS laser driver array [26]. Meanwhile, the individual cost per VCSEL is considerably reduced through wafer-scale fabrication and on-wafer testing. Also, VCSELs have proven to be robust devices [27]. With these desirable features, the VCSEL technology has been credited as a key enabling solution to the high-performance board-to-board interconnects.

#### 1.5 Overview of Optical Interconnect Methodologies

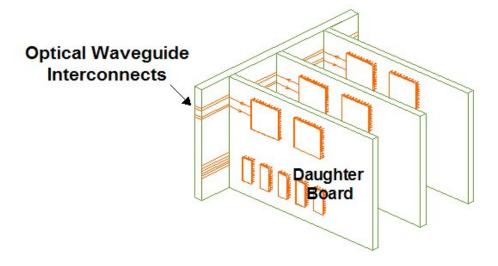

There have been many research work devoted to investigate how to effectively utilize optical interconnects to expedite the data transfers among all daughter boards within a box. As respectively illustrated in Figure 1.5, 1.8, and 1.10, the optical implementation solutions at the board-to-board level that have been explored so far may be categorized into three basic types: optical waveguide interconnects, free-space optical interconnects, and substrate-guided optical interconnects, without counting the hybrid approaches that are based on the various combinations involving these fundamental methodologies.

#### Optical Waveguide Interconnects

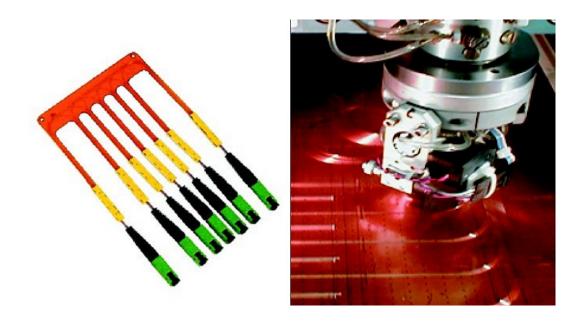

Figure 1.5 Optical waveguide interconnects

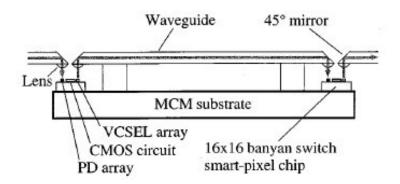

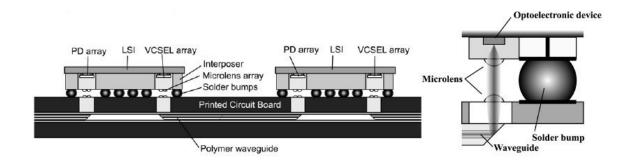

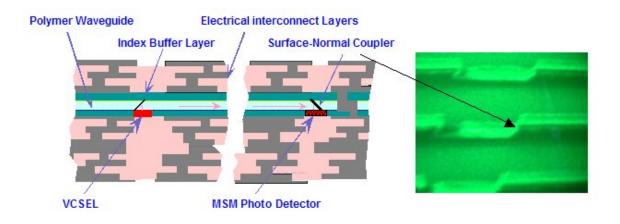

In a similar fashion to electrical lines, optical waveguides can be laid out on a board to provide the required interconnects among all daughter boards, as illustrated in Figure 1.5. Data can be transferred in optical waveguides at a much higher speed at a given line density than in electrical lines. As a result, the overall system performance may be considerably improved. A major concern in the approaches that are based on optical waveguide interconnects is the signal loss during the propagation. Optical polymers offer a versatile material for the fabrication of high-quality optical waveguides on a variety of types of substrates. A polymer waveguide device with very low attenuation of 0.03dB/cm at 840nm and good thermal stability was demonstrated [28]. Another critical issue is to couple the light that carries the information into and out of optical waveguides in an efficient and reliable manner. A 45° planar micromirror can simply function as an optical waveguide coupler, as suggested for use in the open waveguide layers in Figure 1.6 (a) [29] and (b) [30], and the fully embedded waveguide layer in Figure 1.6 (c) [31]. The 45° micromirror structure is naturally insensitive to wavelength and relatively easy to fabricate with high coupling efficiency and low scattering loss at the end of an optical waveguide. In addition to optical polymer waveguides, the regular optical fibers can be routed within a flexible film, as shown in Figure 1.7 (a) [32], and then the fabricated optical circuitry can function as a flexible backplane, as illustrated in Figure 1.7 (b).

Figure 1.6 (a) 45° micromirror as waveguide coupler in [29]

Figure 1.6 (b) 45° micromirror as waveguide coupler in [30]

Figure 1.6 (c) 45° micromirror as waveguide coupler in [31]

Figure 1.7 (a) STRATOS optical flex circuitry [32]

Figure 1.7 (b) Flexible optical backplane

The approaches that are based on optical waveguide interconnects provide only point-to-point interconnects, since it is exceptionally difficult for optical waveguides to deliver multiple high-quality bus fan-outs. For the data transfers between a pair of daughter boards that are not directly connected by optical waveguides, signal switching is required. From the architecture point of view, this topological deficit critically restricts the overall gain obtained by utilizing optical interconnects. Meanwhile, not as convenient as the free-style electrical signal lines, optical waveguides cannot be simply laid out on a board at demand due to the concern on the bending loss. In consequence, the routing scheme of optical waveguides is considerably subject to the geometrical constrictions.

#### Free-Space Optical Interconnects

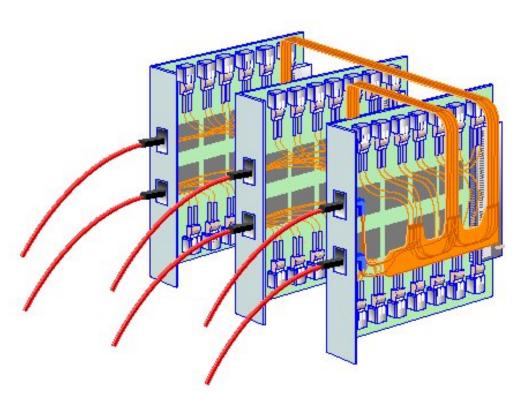

Figure 1.8 Free-space optical interconnects

The data transfers between two face-to-face daughter boards can be directly fulfilled through the free space in a point-to-point fashion, as illustrated in Figure 1.8. Data can be transferred in free-space optical links at a much higher rate at a given line density than in electrical lines. In turn, the overall system performance may be considerably improved.

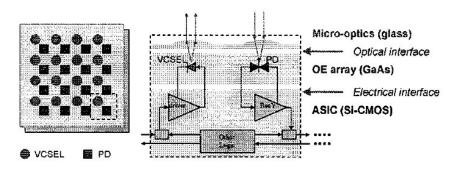

With the remarkable progress in the fabrication of the active optoelectronic array devices, especially the smart pixel array (SPA) devices as shown in Figure 1.9 (a) [33] and (b) [34], high-density parallel free-space optical interconnects are becoming attractive. Also, the routing scheme is fairly flexible because all optical interconnects proceed in the third dimension rather than on the original 2-D planar board. Moreover, because there is little interaction among multiple crossing optical beams in the free space, more radical 3-D interconnect architectures may be explored.

Figure 1.9 (a) Packaged smart pixel array (SPA) in [33]

Figure 1.9 (b) Packaged smart pixel array (SPA) in [34]

Same as the optical waveguide methodology, the approaches that are based on free-space optical interconnects provide only the point-to-point connectivity. For the data transfers between two daughter boards that are not directly facing each other, signal relay and/or switching is required. From the architecture point of view, this topological deficit critically restricts the overall gain obtained by utilizing optical interconnects. Meanwhile, the optical signal links in the free space are open to the environmental noise, and the critical alignments can be easily disturbed. This packaging reliability shortfall makes the high-integrity data transfers in the harsh environment practically impossible.

#### Substrate-Guided Optical Interconnects

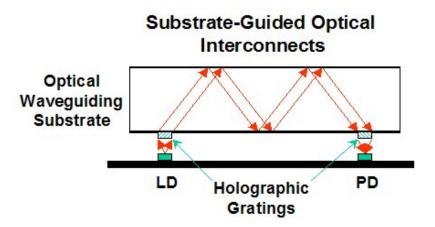

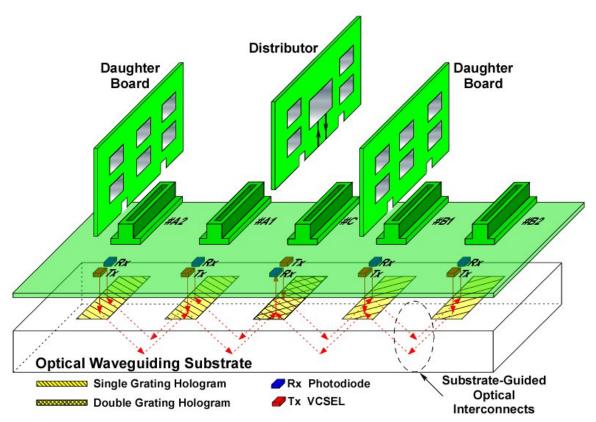

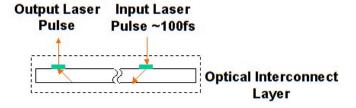

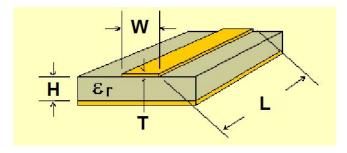

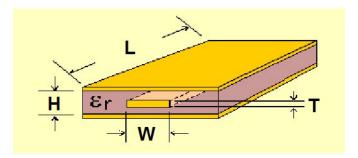

Figure 1.10 Substrate-guided optical interconnects

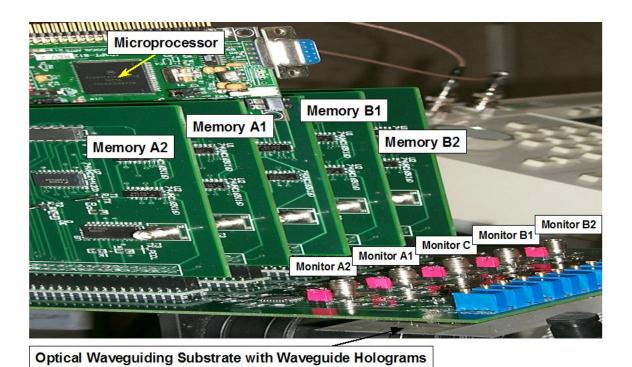

As illustrated in Figure 1.10, in the approaches that are based on substrate-guided optical interconnects [35], the light that carries the information is confined within an optical waveguiding substrate that has the properly designed volume holographic gratings integrated on its top surface. The substrate provides a turbulence-free medium for optical interconnects, and the waveguide holograms function as optical fan-in/fan-out devices. For a data transfer, the light emitted from the source laser diode is diffracted into the substrate by the source waveguide hologram. Within the substrate, the incident angle at the substrate/air interface is engineered to be larger than the critical angle so as to satisfy

the total internal reflection (TIR) condition. As a result, this light cannot escape from the confinement of the substrate. Then, the destination waveguide hologram couples this confined light out of the substrate and projects it onto the destination photodiode. In this manner, an optical interconnection link is established and adequately protected by the substrate from the noise present in the surrounding environment. The bandwidth capacity per substrate-guided optical interconnection line was experimentally characterized to be approximately 2.5THz [22]. Thus, by utilizing substrate-guided optical interconnects the overall system performance may be considerably improved. Most significantly, with the appropriate design of the types of the waveguide holograms and their relative positions on the top surface of the substrate, a variety of topologies, including the shared bus, can be effectively implemented.

## 1.6 Advantages of Optical Backplane Bus vs. Optical Point-to-Point Switched Backplane

In the optical domain, there have been many research efforts devoted to prevent the projected bottleneck from throttling the data transfers at the board-to-board level. The most significant benefit of utilizing optical interconnects is the tremendous gain in the bandwidth capacity. From the architecture point of view, however, the three fundamental methodologies just compared have a huge discrepancy in how effectively the obtained bandwidth would improve the overall system performance. The approaches that are based on optical waveguide or free-space optical interconnects provide only the point-to-point topology. In turn, the various proposed solutions are essentially an optical point-to-point switched backplane. As previously discussed, this topological deficit critically restricts the gain in the bandwidth capacity. The point-to-point switched backplane is an indirect network, so it cannot carry out multicast/broadcast as effectively as the backplane bus. Besides the hop delay, each data transfer phase inevitably incurs a routing overhead, which makes it rather difficult to minimize the overall interconnect latency. The most crucial device in a switched medium is certainly the switch that coordinates the point-to-point connectivity among all daughter boards, and adjusts the available aggregate

bandwidth according to the real-time traffic behavior. The most important functions of a switch are buffering, routing, and switching. So far, unfortunately, optical solutions have not been able to implement these critical functions as effectively as their electronic counterparts. This fact implies that extra optical-to-electrical and electrical-to-optical conversions must be performed at the interface of the switch if only the interconnection links are optically implemented. This optical-domain overhead introduces additional latency and complexity, and thus further diminishes the gain in the bandwidth capacity. Meanwhile, the additional involvement of many expensive devices, including switches, electrical-optical interface modules, and so on, considerably increases the overall system cost. In contrast, the approaches that are based on substrate-guided optical interconnects can effectively provide a variety of topologies, including the shared bus, and thus an optical backplane bus can be implemented. The backplane bus is a direct network, and thus possesses very high connectivity. Each data transfer phase incurs only a single-hop delay, which is highly desirable in minimizing the interconnect latency. Also, the shared bus is inexpensive to implement since a lot of hardware are shared. In the electrical domain, the major bottleneck of the shared bus topology arises from its low bandwidth capacity. Therefore, one objective of this dissertation is to start up an innovative technology in the optical domain that can provide sufficient bandwidth capacity while at the same time retaining the essential merits of the shared bus topology.

#### 1.7 Research Contributions

Several optical backplane bus architectures have been proposed in the past [36], [37]. As might be expected, in these pervious attempts, substrate-guided optical interconnects were substantially involved in the design with the purpose to engineer the shared bus topology. Unfortunately, none of them could fulfill equalized bus fan-outs across the entire optical backplane layer. This significant drawback can severely affect the overall system integration due to the constraint on the dynamic range. As a result, the feasibility of these previously proposed optical backplane architectures is in doubt. So far, none of them has been able to be really applied in any practical scenarios.

The objectives of this dissertation are:

- To start up an innovative technology in the optical domain that can provide sufficient bandwidth capacity while retaining the essential merits of the shared bus topology.

- To fulfill equalized bus fan-outs across the entire optical interconnect layer.

- To demonstrate the feasibility of the innovatively designed optical backplane bus in the practical scenarios, such as uniprocessing and multiprocessing systems.

The major contributions of this dissertation are summarized below:

- With the comparative examinations from the architecture point of view, the substrateguided optical interconnect methodology is distinguished out because of the beneficial potential of creating an optical backplane bus.

- A new optical interconnect architecture, optical centralized shared bus, is introduced. This innovative optical backplane bus utilizes the beneficial physical characteristics of optics while retaining the desirable architectural properties of the shared bus topology.

- Optical centralized shared bus architecture can fulfill equalized bus fan-outs across the entire backplane layer in an elegant manner. This significant merit can substantially ease the overall system integration in the practical implementations.

- A systematic recording scheme is developed to assure the quality of the fabricated waveguide holograms and the accuracy of their diffraction efficiency.

- The optical interconnect layer specified in optical centralized shared bus architecture is completely implemented, and the equalized bus fan-outs are successfully established across the entire fabricated optical interconnect layer.

- The feasibility of optical centralized shared bus architecture in uniprocessing systems is experimentally verified by applying it to fulfill the critical microprocessor-to-memory interconnects in a research prototype.

- As a preliminary effort, optical centralized shared bus architecture is applied in a multiprocessing research prototype to partially emulate the centralized shared-memory multiprocessing scheme.

#### 1.8 Dissertation Outline

In Chapter 2, optical centralized shared bus architecture is introduced, and its major characteristics, especially the merit to achieve equalized bus fan-outs, are delineated.

In Chapter 3, the detailed procedure of implementing the optical interconnect layer specified in optical centralized shared bus architecture is presented, the equalized bus fan-outs are demonstrated across the entire implemented optical backplane bus, and the bandwidth capacity of the fabricated optical interconnect layer is characterized.

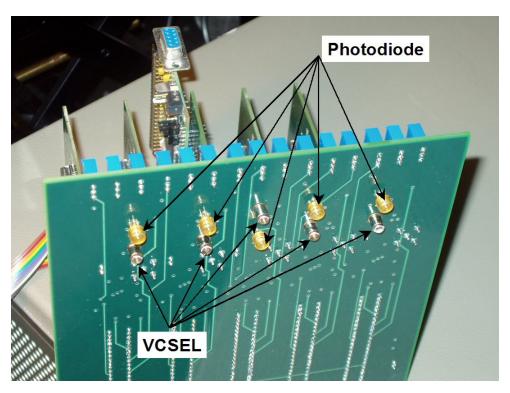

In Chapter 4, the implementation and the high-speed performance characterization of the electro-optical interface modules are described.

In Chapter 5, the strategy of verifying the conceptual feasibility of optical centralized shared bus architecture is addressed.

In Chapter 6, optical centralized shared bus architecture is actually instantiated in a uniprocessing prototype to provide the critical microprocessor-to-memory interconnects.

In Chapter 7, the preliminary attempt of exploiting optical centralized shared bus architecture in a centralized shared-memory multiprocessing prototype is shown.

Finally, in Chapter 8, a summary of this dissertation is given, and the future directions of the research that targets at eliminating the potential bottleneck at the board-to-board hierarchical level are suggested.

## **Chapter 2 Optical Centralized Shared Bus Architecture**

#### 2.1 Overview of Optical Shared Bus Architectures

In any optical shared bus architecture, the interface between the optical and electrical backplane layer imposes the most significant constrictions on the system integration. The uniformity of the bus fan-outs on the shared media is of the most critical concern. The larger the variation, the more difficult the integration of the electro-optical transceivers becomes. Unfortunately, none of the optical shared bus architectures previously proposed by others could successfully manage this crucial issue.

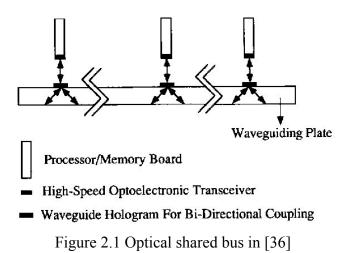

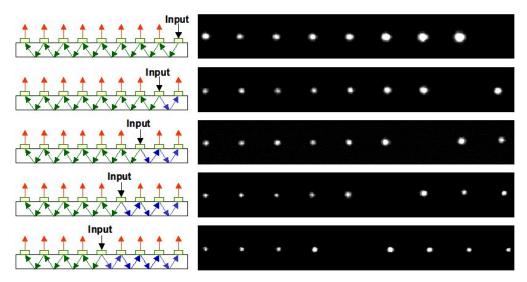

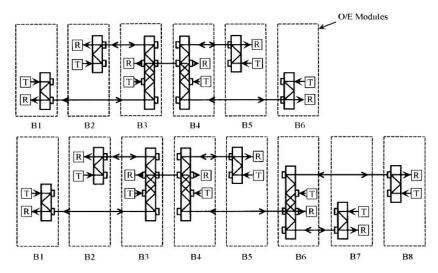

In [36], the shared bus topology was configured in a straightforward way by using double-grating waveguide holograms. As shown in Figure 2.1, the optical interconnect layer consists of an optical waveguiding substrate that provides a turbulence-free medium for optical interconnects, and the double-grating waveguide holograms integrated on its top surface function as optical fan-in/fan-out devices. As exhibited in Figure 2.2, however, this architecture intrinsically cannot fulfill equalized bus fan-outs on the shared media, and the variation among the fan-outs dramatically rises with the increased fan-out count. Moreover, the spatial overlap of the fan-in and fan-out optical beams further complicates the practical implementation of the electro-optical interface modules.

Figure 2.2 Non-uniform bus fan-outs in [36]

In [37], a hybrid approach involving both substrate-guided optical interconnects and free-space optical interconnects was employed to construct the shared bus topology, as illustrated in Figure 2.3. This design comprises the merits of substrate-guided optical interconnects by incorporating unreliable free-space optical signal links. Although the variation among the bus fan-outs can be mitigated in some degree, equalization is still intrinsically impossible. Also, this approach lacks of scalability due to the complicated routing scheme.

Figure 2.3 Optical shared bus in [37]

#### 2.2 Architectural Description of Optical Centralized Shared Bus

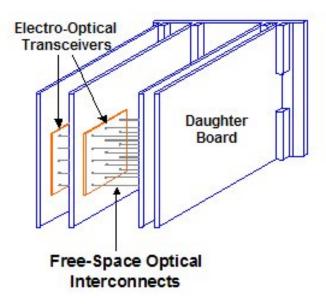

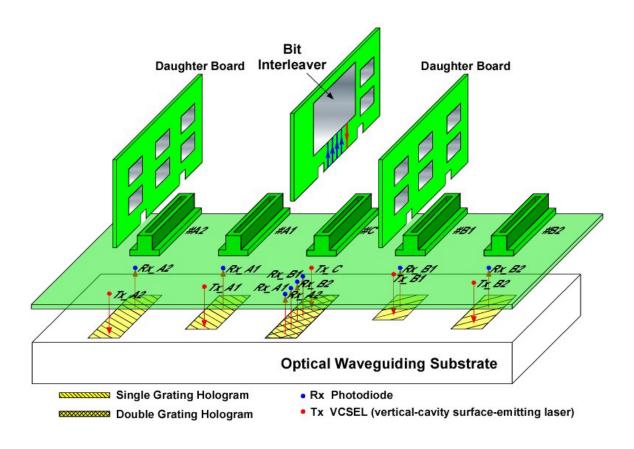

Figure 2.4 Optical centralized shared bus architecture

Figure 2.4 illustrates the architectural concept of the innovation, optical centralized shared bus [38]. For the simplicity, only five slots (#A1, #A2, #B1, #B2, and #C) are drawn in this schematic. Nonetheless, this innovation does not directly impose any restrictions on the total number of daughter boards. The board that is to be inserted into the central slot (#C) plays a pivotal role in this architecture, and is referred to as distributor in this dissertation. The electrical backplane provides interconnects for the non-critical signals. The electro-optical interface modules, including photodiodes and VCSELs, are integrated on the backside of the electrical backplane, and aligned with the underlying optical interconnect layer. Therefore, the insertion/removal of daughter boards during the normal operations does not disturb the critical alignment. In contrast to the other modules, the positions of the central VCSEL and photodiode are swapped. The

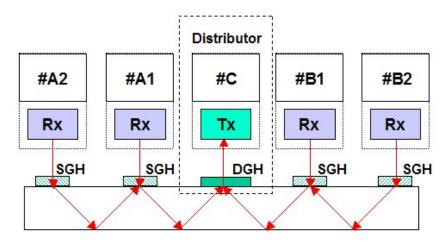

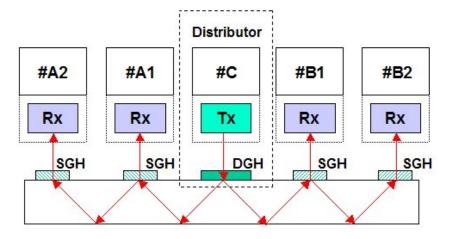

optical interconnect layer consists of an optical waveguiding substrate integrated with the properly designed volume holographic gratings on its top surface. The substrate provides a turbulence-free medium for optical interconnects, and the waveguide holograms function as optical fan-in/fan-out devices. Underlying the distributor is a double-grating waveguide hologram, and the others are single-grating waveguide holograms. Figure 2.5 (a) and (b) illustrate the overall optical connectivity. By employing such an innovative interconnect configuration, this unique optical backplane architecture effectively fulfills both broadcastability and bi-directionality of signal flows on the shared bus [39].

Figure 2.5 (a) Data delivery to distributor

Figure 2.5 (b) Data broadcast from distributor

As indicated in Figure 2.4 and 2.5, there are two optical signal channels in this innovative architecture. One is for the source daughter board to deliver data to the distributor, as illustrated in Figure 2.5 (a), and the other for the distributor to broadcast data to every regular daughter board on the shared bus, as illustrated in Figure 2.5 (b). For a complete data transfer, as the name of this architecture implies, the source daughter board first deliver the data to the distributor. The VCSEL of the source daughter board emits the light that carries the information and projects it surface-normally onto its underlying waveguide hologram. This light is coupled into the optical waveguiding substrate by the grating and propagates within the confinement of the substrate under the total internal reflection (TIR) condition. Then, it is surface-normally coupled out of the substrate by the central double-grating waveguide hologram and detected by the central photodiode. Subsequently, the central VCSEL generates the optical signal that carries the original information and projects it surface-normally onto its underlying double-grating waveguide hologram. This light is coupled into the substrate and diffracted into two beams propagating along the two opposite directions within the confinement of the substrate under the TIR condition. During the propagation, a portion of the light is surface-normally coupled out of the substrate by a regular daughter board's underlying waveguide hologram and detected by its photodiode. This daughter board accepts the retrieved data if the destination header falls within its address range. If the distributor is actually the originating source of the data, the first data delivery process does not happen. If the distributor recognizes that it is the only data recipient, the second data broadcast process is not necessary.

#### 2.3 Characteristics of Optical Centralized Shared Bus Architecture

The most attractive feature of this innovative architecture is its ability to fulfill equalized bus fan-outs on the shared media. This merit can considerably save the overall power budget and substantially ease the practical system integration, because the critical interface between the optical and electrical backplane layer is uniform across the entire architecture. Assuming that the VCSELs in all electro-optical interface modules emit the

same optical power  $P_{in}$ , the criteria of equalized bus fan-outs are (1) the power of the optical signal broadcast from the distributor to every regular daughter board is same; (2) the power of the optical signal delivered from every regular daughter board to the distributor is same; and (3) the power of the optical signal broadcast from the distributor to every regular daughter board is same as that delivered from every regular daughter board to the distributor.

By balancing the diffraction efficiency of the waveguide holograms in use, equalized bus fan-outs can be achieved. As illustrated in Figure 2.5 (a) and (b), in such a symmetric configuration, the central double-grating hologram functions as an equal-strength beam splitter with diffraction efficiency  $\eta_{equal}$  [40], [41], and the diffraction efficiency of the single-grating holograms satisfies

$$\eta_{Ai} = \eta_{Bi} \qquad (2.1)$$

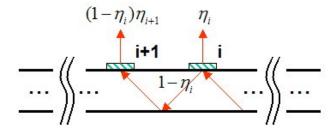

where the subscription i represents the slot number counted in reference to the central slot (#C). Considering the two consecutive fan-outs on the broadcast bus illustrated in Figure 2.6,  $\eta_i$  percent of the light that carries the information is coupled out of the substrate by hologram i, and  $(1-\eta_i)$  percent of the light continues to propagate within the confinement of the substrate under the TIR condition. Then, by hologram i+1,  $\eta_{i+1}$  percent of the remaining light is coupled out of the substrate. These two bus fan-outs are equalized when

$$\eta_i = (1 - \eta_i) \eta_{i+1}$$

(2.2)

Equation (2.2) can be rewritten in a more revealing form of

$$\eta_{i+1} = \frac{\eta_i}{1 - \eta_i} \qquad (2.3)$$

By simply reversing the propagation directions of the optical beams drawn in Figure 2.6, it can be verified that the second criterion of equalized bus fan-outs is also guaranteed by equation (2.3). It follows that the power of the optical signal broadcast from the distributor to every regular daughter board can be expressed as

$$P_{broadcast} = P_{in} \cdot \eta_{equal} \cdot \eta_1 \qquad (2.4)$$

and the power of the optical signal delivered from every regular daughter board to the distributor is

$$P_{delivery} = P_{in} \cdot \eta_1 \cdot \eta_{equal} \qquad (2.5)$$

By comparing equation (2.4) with equation (2.5), the third criterion is also verified. Therefore, the iterative relationship specified by equation (2.3) along with equation (2.1) indicates the required diffraction efficiency balance to equalize all bus fan-outs.

Figure 2.6 Schematic for the derivation of the condition for equalized bus fan-outs

The single-grating holograms at the two ends of the substrate should be able to completely couple the remaining light out of the substrate so as not to introduce reflection waves on the shared bus. Otherwise, the reflected waves may interfere with the successive optical signals to cause signal integrity degradations. Thus, their diffraction efficiency  $\eta_{\text{max}}$  should be as close to 100% as possible. Meanwhile, high  $\eta_{\text{max}}$  also saves the overall power budget. By iterating equation (2.3), the diffraction efficiency of all waveguide holograms can be expressed in an explicit form. It can be derived that

$$\eta_1 = \frac{\eta_{\text{max}}}{1 + (N/2 - 1)\eta_{\text{max}}}$$

(2.6)

where N is the total number of the slots for the regular daughter boards on the electrical backplane (it is always an even integer because of the symmetric configuration). By substituting equation (2.6) into either equation (2.4) or (2.5), bus fan-out coefficient  $\eta_{fan-out}$ , which is a critical factor in the power budget evaluation, can be expressed as

$$\eta_{fan-out} = P_{broadcast} / P_{in} = P_{delivery} / P_{in}$$

$$= \eta_{equal} \cdot \eta_1 = \frac{\eta_{equal} \cdot \eta_{max}}{1 + (N/2 - 1)\eta_{max}} \qquad (2.7)$$

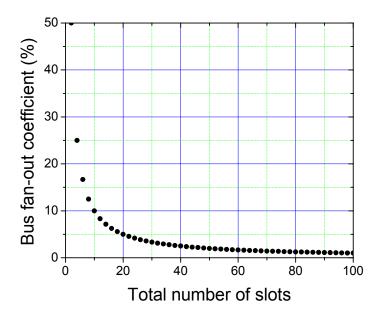

Figure 2.7 shows bus fan-out coefficient as a function of the total number of the slots for the regular daughter boards with the assumptions of  $\eta_{equal} = 50\%$  and  $\eta_{max} = 100\%$ .

Figure 2.7 Bus fan-out coefficient vs. total number of the slots for the regular daughter boards with the assumptions of  $\eta_{equal} = 50\%$  and  $\eta_{max} = 100\%$

It is possible to replace the active distributor with a passive optical component, e.g., a right-angle prism. Although this passive device can fulfill the same function of routing optical signals in optical centralized shared bus architecture, the versatility of an active distributor can bring more desirable features. It has the similar functionality to a repeater employed in the optical fiber telecommunication system for optical signal reamplifying, reshaping, and retiming (3R) [42]. A centralized arbiter that coordinates the media access control (MAC) can be readily embedded into an active distributor. Furthermore, an active distributor can function as an edge router in a hierarchical interconnection network [43]

where the communications within a local cluster are individually carried out on an optical centralized shared bus. By appropriately provisioning daughter boards into local clusters in accordance with the locality characteristic of the traffic behavior, such a hierarchical approach can generate extremely high parallelism, because the non-conflicting intracluster communications can proceed simultaneously.

#### 2.4 Summary

In this chapter, after reviewing the optical shared bus architectures previously proposed by others and realizing the major deficit caused by the non-uniform bus fanouts, a novel backplane architecture, optical centralized shared bus, is introduced. By employing an innovative configuration, this unique optical backplane architecture effectively fulfills both broadcastability and bi-directionality of signal flows on the shared bus. The most attractive feature of this innovation is its ability to achieve equalized bus fan-outs on the shared media. This merit can considerably save the overall power budget, and thus is highly desirable from the system integration point of view. With the appropriate MAC protocols, the innovation described herein is transparent to the higher architectural layers. It shall provide an open solution to high-performance interconnects in existing and future high-end systems.

## **Chapter 3 Optical Interconnect Layer Implementation**

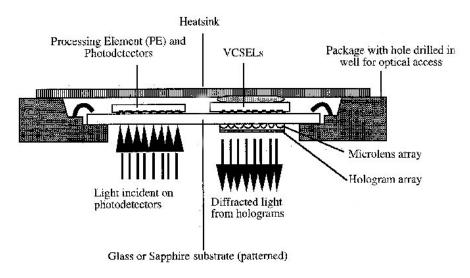

### 3.1 Configuration of Optical Interconnect Layer

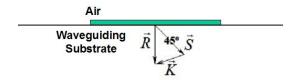

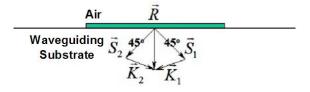

As shown in Figure 2.4 and 2.5, the optical interconnect layer in optical centralized shared bus architecture consists of an optical waveguiding substrate with the properly designed volume holographic gratings integrated on its top surface [38]. The substrate provides a turbulence-free medium for optical interconnects, and the holograms function as optical fan-in/fan-out devices. Underlying the central distributor is a double-grating waveguide hologram, and the others are single-grating waveguide holograms. The singlegrating hologram provides 45° diffraction within the substrate, as illustrated in Figure 3.1 (a), and the double-grating hologram delivers 45° diffraction within the substrate in two directions, as illustrated in Figure 3.1 (b). The substrate in use has a refractive index of approximately 1.5, and thus the critical angle at the substrate/air interface is nearly 42°, i.e., less than 45°. Therefore, the total internal reflection (TIR) condition is guaranteed. The most attractive feature of this innovatively designed optical interconnect layer is its ability to achieve equalized bus fan-outs on the shared media by balancing the diffraction efficiency of the waveguide holograms in use. This merit can considerably save the overall power budget, and thus is highly desirable from the system integration point of view.

Figure 3.1 (a) Wave vector diagram of single-grating waveguide hologram

Figure 3.1 (b) Wave vector diagram of double-grating waveguide hologram

#### 3.2 Overview of Volume Holographic Gratings

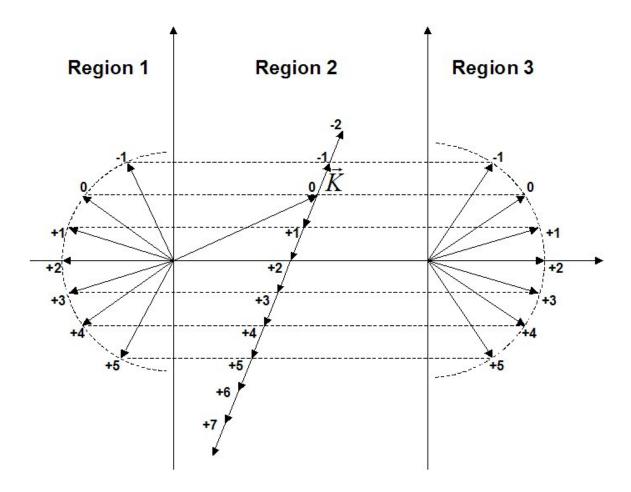

The analysis of the diffraction characteristics of the general dielectric planar gratings has a long and interesting history. Reference [44] provides a detailed review along with a fairly thorough bibliography. The common methods of analyzing diffraction by grating are the modal approach, which is sometimes referred to as Floquet, Floquet-Bloch, or coupled-mode approach, and the coupled-wave approach, which is occasionally called coupled-mode approach too with confusion. Both of these approaches can produce the exact formulations without approximations. In fact, these formulations are completely equivalent in their full rigorous forms. They are merely alternative mathematical representations of the total electromagnetic field inside the grating region, and associated with each representation is a different physical perspective. The most obvious effect of diffraction by grating is the occurrence of multiple propagating backward- and forward-diffracted orders that typically exist outside the grating region, as illustrated by the wave vector diagram in Figure 3.2. In the coupled-wave approach, the total electromagnetic field inside the grating region is expanded in terms of its space-harmonic components, and their wave vectors have the following relationship of

$$\vec{\beta}_i = \vec{\beta}_0 - i\vec{K} \qquad (3.1)$$

where  $\vec{\beta}_i$  represents the wave vector of the i-th space-harmonic field, and  $\vec{K}$  is the grating vector. This equation is often referred to as the Floquet condition. Figure 3.2 intuitively visualizes that the incident homogeneous plane wave may be divided into many diffracted inhomogeneous plane waves that have directions given by equation (3.1), and the i=0 inhomogeneous plane wave corresponds to the refracted incident wave. These inhomogeneous plane waves are not independent. In the grating-modulated medium, energy is coupled back and forth between the adjacent orders. As exhibited by the horizontal dashed lines in Figure 3.2, the i-th space-harmonic component inside the grating region produces a phase matched i-th field, respectively, in region 1 and 3. Outside the grating region, the field whose wave vector can be literally drawn on the semicircle in region 1 or 3 is a propagating wave, otherwise an evanescent wave.

Figure 3.2 Wave vector diagram illustrating phase matching of the space-harmonic components of the total electromagnetic field inside the grating (region 2) with the propagating backward-diffracted orders (region 1), the propagating forward-diffracted orders (region 3), and the evanescent waves outside the grating [44]

Because solving the rigorous coupled-wave equations is enormously time-consuming, the vast majority of the papers on grating diffraction analysis deal with approximate theories. There are a large number of possible approximations and assumptions that can be made. In some scenarios, the simplifications even allow the solutions in analytical forms to be obtained. From the rigorous theory along with a series of fundamental assumptions and simplifications, the exact formulations can be reduced to a variety of approximate theories. Among them, the two-wave first-order coupled-wave theory, which is commonly called Kogelnik theory [45], is of the most interest in holography, and now widely referenced in the analysis of the diffraction characteristics of volume holographic gratings. It assumes that:

- (1) The spatial modulation of the refractive index and the absorption constant is of a sinusoidal form.

- (2) Light incidence is at or near the Bragg angle and only the diffraction orders that obey the Bragg condition at least approximately are retained in the analysis. Other diffraction orders are neglected. This is the two-wave approximation that only takes the refracted incident wave and the i = 1 inhomogeneous plane wave into account.

- (3) There is only a slow energy interchange per wavelength between the retained two coupled waves. This is the first-order approximation that eliminates all second derivatives of the field amplitudes from the coupled-wave equations, and thus some boundary effects are neglected. Consequently, the terminologies of transmission hologram and reflection hologram can be unambiguously used.

These assumptions and approximations limit the validity of this theory to the Bragg regime diffraction by volume holographic gratings. The criteria for Bragg regime and volume hologram are articulated in [46].

By applying the Kogelnik theory, the diffraction efficiency of the single-grating hologram in Figure 3.1 (a) at its Bragg angle ( $0^{\circ}$ ) can be analytically expressed as

$$\eta = \sin^2 \left( \frac{\pi \Delta nd}{\lambda \sqrt{\cos \theta}} \right) \quad (3.2)$$

where d is the thickness of the grating-modulated medium,  $\lambda$  is the wavelength (850nm) of the incident light emitted from a VCSEL,  $\theta$  is the diffraction angle (45°) within the substrate, and  $\Delta n$  is the refractive index modulation. The double-grating hologram in Figure 3.1 (b) functions as an equal-strength beam splitter. It contains two incoherently superimposed phase gratings with a common Bragg angle (0°) and the same refractive index modulation. With the extended analyses based on the Kogelnik theory [40], [41], its diffraction efficiency can be derived as

$$\eta_{equal} = \frac{1}{2} \sin^2 \left( \sqrt{2} \frac{\pi \Delta nd}{\lambda \sqrt{\cos \theta}} \right)$$

(3.3)

when the Bragg condition is satisfied inside the grating region.

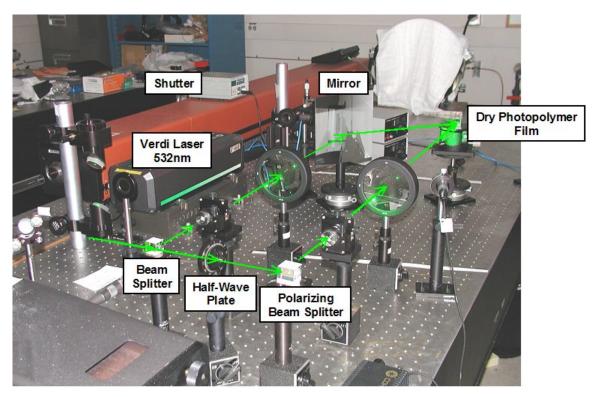

The appropriately defined two-beam interference patterns can be recorded within dry photopolymer films to form the desired grating structures, as shown in Figure 3.3. Dry photopolymer films are well suitable for fabricating high-efficiency holographic gratings. The advantages of photopolymers over other types of emulsion, such as dichromated gelatin and silver halides, include dry-processing capability, long shelf life, and good photo-speed [47]. In the setup as shown in Figure 3.3, the 532nm line from the Verdi laser provides the exposing illuminations, and the shutter controls the exposure time. Two objective lenses paired with a pinhole respectively at their focal points are used for spatial filtering of the Verdi light. Two focusing lenses are employed to collimate the laser beams into plane waves, and expand them large enough to guarantee the uniformity of the formed grating structures. The combination of a half-wave plate with a polarizing beam splitter adjusts the intensity ratio of the two collimated laser beams, in turn, the fringe visibility of their interference pattern. Two rotation stages host, respectively, a right-angle prism and a mirror. Rotating them sets the appropriate recording angles [48]. A device is prepared by laminating dry photopolymer films onto an optical waveguiding substrate. To reduce the Fresnel reflection, the surface of the substrate is completely concealed by black tape except for the areas that are covered by the films. This substrate is put against the right-angle prism, and the appropriate index-matching oil is applied at their interface to reduce the Fresnel reflection.

Figure 3.3 Setup for hologram recording

A dry photopolymer film consists of monomers, polymeric binders, and photo-initiators. The monomers have strong absorption of the light around 530nm, and then become polymers. Thus, the refractive index of the film is accordingly changed. When exposed to a two-beam interference pattern, as shown in Figure 3.3, there are more monomers being polymerized in the bright regions than in the dark regions. The monomer concentration gradients that are introduced by this non-uniform exposure drive the monomers to diffuse from the dark regions to their adjacent bright regions. This procedure leads to a spatial periodic distribution of polymers, and the resulted refractive index modulation within the film conforms to the original illumination pattern. Therefore, a grating structure is formed within the film. A final uniform illumination polymerizes the remaining monomers, and thus stabilizes this grating structure. To obtain double-grating holograms, two sequential exposure steps are to be performed to record two incoherently superimposed phase gratings within the same film.

# 3.3 Theoretical Analysis of Grating Formation Procedure within Dry Photopolymer Films

The dynamic change of the monomer concentration u(x,t) during the exposure can be described by the following one-dimensional (1-D) polymerization/diffusion equation of

$$\frac{\partial u(x,t)}{\partial t} = \frac{\partial}{\partial x} \left[ D(x,t) \frac{\partial u(x,t)}{\partial x} \right] - F_o[1 + V\cos(Kx)]u(x,t)$$

(3.4)

where D(x,t) is diffusion parameter,  $F_o$  is polymerization factor ( $F_o = \kappa I_o$ , where  $\kappa$  is a constant and  $I_o$  is the average irradiance), V is fringe visibility, and K is the magnitude of the grating vector. This equation indicates the dependence of the monomer polymerization and diffusion rate on the monomer concentration gradients formed by the period of the two-beam interference pattern during the exposure, and its solution can be written as a Fourier series as

$$u(x,t) = \sum_{i=0}^{\infty} u_i(t) \cos(iKx)$$

(3.5)

where  $u_i(t)$  represents the amplitude of the i-th order harmonic of the monomer concentration. The initial conditions are

$$u_0(t=0) = U_0$$

(3.6)

$$u_{i\neq 0}(t=0) = 0$$

(3.7)

where  $U_{\scriptscriptstyle o}$  is the initial monomer concentration within the film. Since the mobility of the monomers is affected by the monomer concentration, the diffusion parameter can also be written as

$$D(x,t) = \sum_{i=0}^{\infty} D_i(t) \cos(iKx)$$

(3.8)

where  $D_i(t)$  represents the amplitude of the i-th order harmonic of the diffusion parameter. Usually, retaining a few low grating orders would be sufficient to obtain a satisfactory estimation of the solutions to equation (3.4) [49]. The distribution of the polymer concentration affects the refractive index of the dry photopolymer film, in turn,

the diffraction properties of the formed grating structure. From the solutions to equation (3.4), the dynamic change of the polymer concentration N(x,t) can be obtained as

$$N(x,t) = \int_{0}^{t} F_{o}[1 + V\cos(Kx)]u(x,t')dt' = \sum_{i=0}^{\infty} N_{i}(t)\cos(iKx)$$

(3.9)

where  $N_i(t)$  represents the amplitude of the i-th order harmonic of the polymer concentration. If an approximately linear relationship between the polymer concentration and the refractive index of the film can be assumed, equation (3.9) gives the phase grating profile in terms of its space-harmonic components.

To obtain double-grating holograms with non-parallel grating orientations, two sequential exposure steps are to be performed. During the first exposure, the dynamic change of the monomer concentration can be analyzed by solving equation (3.4). During the second exposure, the further monomer polymerization/diffusion can be described by the following two-dimensional (2-D) equation of

$$\frac{\partial u(\hat{r},t)}{\partial t} = \nabla_t [D(\hat{r},t)\nabla_t u(\hat{r},t)] - F_o[1 + V\cos(\vec{K}_2 \cdot \hat{r})]u(\hat{r},t)$$

(3.10)

where  $\vec{K}_1$  and  $\vec{K}_2$  represent, respectively, the grating vector formed by the first and second exposure. Consequently, its solutions can be written as the sum of two Fourier series as

$$u(\hat{r},t) = \sum_{i=0}^{\infty} u_i(t) \cos(\vec{K}_1 \cdot \hat{r}) + \sum_{k=0}^{\infty} u_k(t) \cos(\vec{K}_2 \cdot \hat{r})$$

(3.11)

If the two multiplexed gratings are orthogonal to each other  $(\vec{K}_1 \perp \vec{K}_2)$ , the 2-D equation can be decomposed into two uncoupled 1-D polymerization/diffusion equations. Thus, the solutions to equation (3.10) can be simply obtained by sequentially solving two single-grating formations described by equation (3.4) with the appropriate connection conditions. In contrast, if the two multiplexed gratings are non-orthogonal, the two 1-D polymerization/diffusion equations obtained by decomposing equation (3.10) are coupled with each other. This non-orthogonality implies that the formation of the second grating is affected by the first grating in a fairly complicated way.

# 3.4 Experimental Characterization of Grating Formation Procedure within Dry Photopolymer Films

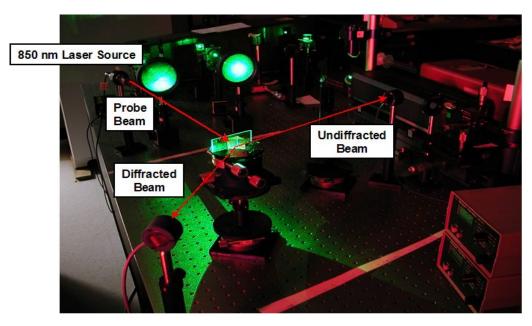

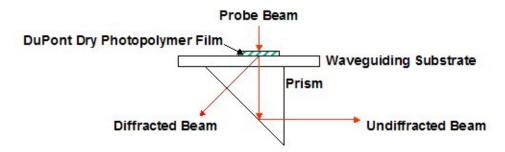

Equation (3.4) and (3.10) involve several material-specific parameters that are not available at this stage. Thus, experimental characterizations of the grating formation procedures within a specific type of dry photopolymer film are necessary to assure the quality of the fabricated waveguide holograms. Figure 3.4 (a) shows the real-time monitoring setup that was employed to evaluate the dynamic characteristics of the grating formation procedures in the 20µm-thick DuPont dry photopolymer films (HRF-600X014-20) [50]. In this setup, the wavelength of the probe beam is 850nm, which is same as the light emitted from a VCSEL. Since the monomers have little response to the light at this wavelength, this probe beam does not affect the grating formation procedures. A right-angle prism, which has the same refractive index as the waveguiding substrate, separates the undiffracted incident probe beam from the beam diffracted by the formed grating structure, as illustrated in Figure 3.4 (b), and their intensity is respectively monitored by an optical power meter. From this monitored dynamic diffraction efficiency, the information on the formed grating structure can be inferred in real time [51].

Figure 3.4 (a) Setup for hologram recording with real-time monitoring

Figure 3.4 (b) Separation of diffracted and undiffracted beam by right-angle prism

As concluded in [46], the criteria for Bragg regime and volume hologram require

$$Q >> 1$$

and  $F >> 1$  (3.12)

The Q factor is

$$Q = \frac{2\pi\lambda d}{n\Lambda^2} \qquad (3.13)$$

where n is the average refractive index of the film,  $\Lambda$  is the spatial period of the formed grating structure. The F factor is

$$F = 16 \frac{n^2}{\Delta n^2} \sin^2(\theta/2)$$

(3.14)

By taking the relevant values of the waveguide holograms in Figure 3.1 into equation (3.13) and (3.14), the criteria for the Kogelnik theory are justified, and thus equation (3.2) and (3.3) are validated for the diffraction efficiency calculation. Rearranging the terms in equation (3.2), it can be derived that

$$\Delta n = \lambda \sqrt{\cos \theta} \sin^{-1}(\sqrt{\eta}) / \pi d \qquad (3.15)$$

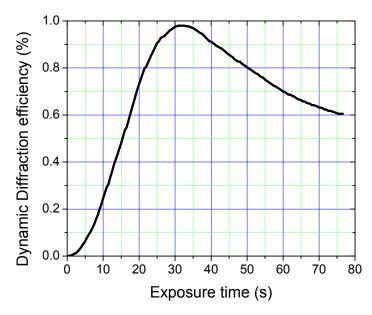

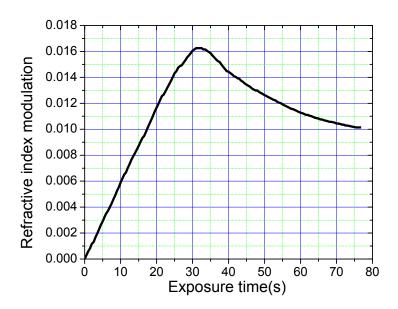

This equation reveals that the information on the refractive index modulation  $\Delta n$  can be obtained from the measured diffraction efficiency  $\eta$ . Since the diffraction properties in Bragg regime of a volume hologram are essentially determined by its first-order grating, it may be assumed that the  $\Delta n$  calculated from equation (3.15) gives a fairly close estimation of the formed first-order grating within the film. Figure 3.5 exhibits such an example with the data from a typical experiment in which a single-grating hologram as illustrated in Figure 3.1 (a) was fabricated by using the DuPont dry photopolymer film.

Figure 3.5 (a) Monitored dynamic diffraction efficiency during grating formation

Figure 3.5 (b) Calculated change of refractive index modulation during grating formation

The second term on the right hand side of equation (3.4),  $F_o[1+V\cos(Kx)]u(x,t)$ , represents the amount of the monomers being polymerized during the grating formation procedure. By substituting u(x,t) with the Fourier series in equation (3.5), this term can be explicitly written as  $F_o[1+V\cos(Kx)][\sum_{i=0}^{\infty}u_i(t)\cos(iKx)]$ , which contains the products of the first-order grating with higher grating orders. These products indicate that the formation of a grating structure within a dry photopolymer film is a non-linear process. As exhibited by the considerable downslides in Figure 3.5 (a) and (b), the consumption of the available monomers by higher grating orders weakens the first-order grating within the film, and thus subdues the diffraction efficiency of the hologram. Therefore, identifying the experimental conditions that can substantially suppress the formation of higher grating orders is crucial to the quality of the fabricated waveguide holograms.

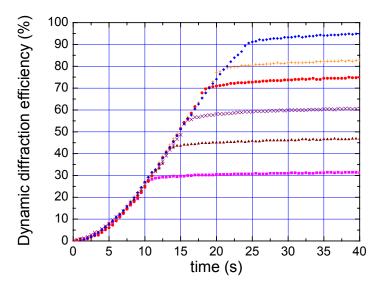

To examine the dynamic characteristics of the single-grating formation procedure in the DuPont dry photopolymer film, a series of single-grating holograms, as shown in Figure 3.1 (a), were fabricated by employing the setup in Figure 3.4 (a) [50]. In these experiments, the exposing illumination was stopped before reaching the maximum diffraction efficiency. Figure 3.6 shows the dynamic diffraction efficiency measured in real time during and after the exposure. As shown in this figure, after terminating the exposure, the dynamic diffraction efficiency continued to increase before reaching a saturation value. This post-exposure increment depended on the diffraction efficiency at which the exposure was stopped ( $\eta_{stop}$ ). The data in Figure 3.6 show that the dynamic diffraction efficiency increased, respectively, 5%, 10%, 13%, 13%, 10%, and 8% after the exposure was stopped at 26%, 37%, 48%, 62%, 73%, and 87%. At relatively low diffraction efficiency, such as 26%, the monomer concentration gradients are too weak to further drive the monomers to diffuse from the dark regions to their adjacent bright regions. When reaching relatively high diffraction efficiency, such as 87%, only a small amount of the available monomers are left for the continuation of the grating formation

procedure. Thus, the post-exposure increments in the dynamic diffraction efficiency are relatively small in these two cases.

Figure 3.6 Dynamic diffraction efficiency measured in real time during and after the exposure. The exposure was stopped, respectively, at 26% ( $\blacksquare$ ), 37% ( $\blacktriangle$ ), 48% ( $\times$ ), 62% ( $\bullet$ ), 73% (+), and 87% ( $\bullet$ ).

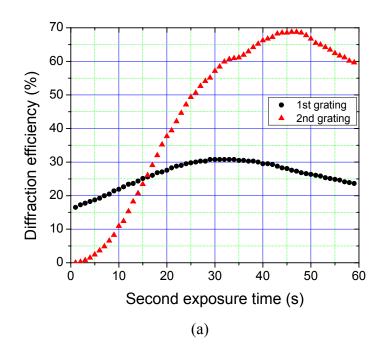

The second term on the right hand side of equation (3.10),  $F_o[1+V\cos(\vec{K}_2\cdot\hat{r})]u(\hat{r},t)$ , can be explicitly written as  $F_o[1+V\cos(\vec{K}_2\cdot\hat{r})][\sum_{i=0}^{\infty}u_i(t)\cos(\vec{K}_1\cdot\hat{r})+\sum_{k=0}^{\infty}u_k(t)\cos(\vec{K}_2\cdot\hat{r})]$ ,

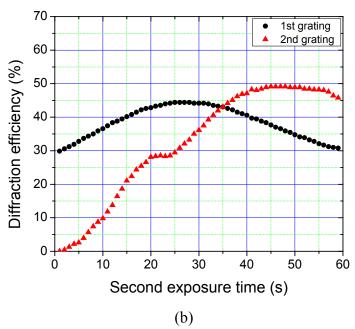

in which the products between the first and second grating represent the interactions between these two grating formation procedures within the same film. To examine the dynamic characteristics of the double-grating formation procedure in the DuPont dry photopolymer film, a series of double-grating holograms, as shown in Figure 3.1 (b), were fabricated by employing the setup in Figure 3.4 (a) [50]. These experiments were conducted in the following order of

(1) A DuPont dry photopolymer film was exposed to an appropriate two-beam interference pattern to form the first grating.

- (2) The first exposure was stopped when the monitored dynamic diffraction efficiency reached a specific value  $\eta_{stop}$ .

- (3) The orientation of the optical waveguiding substrate was rotated 180° in respect to its original position.

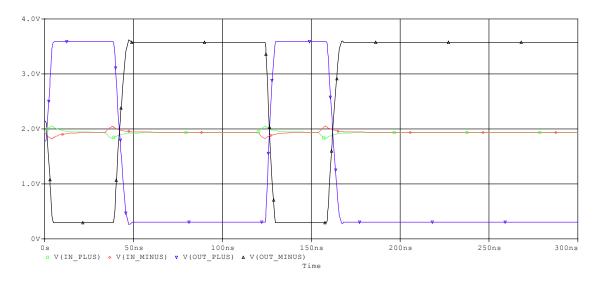

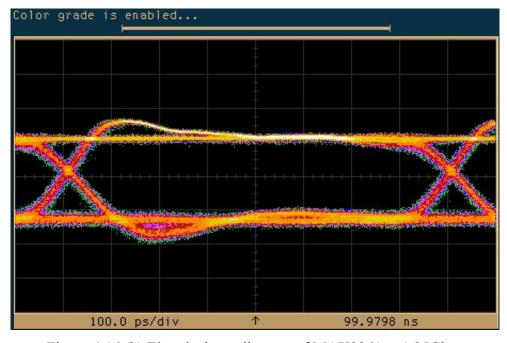

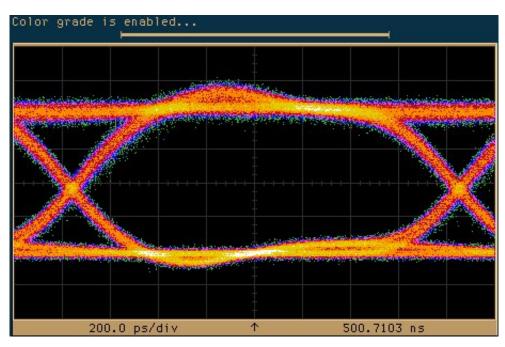

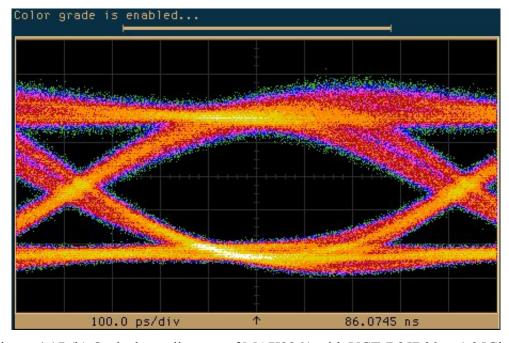

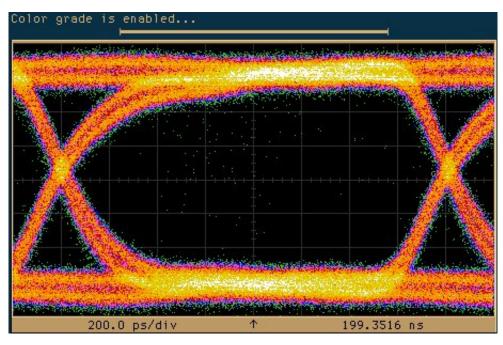

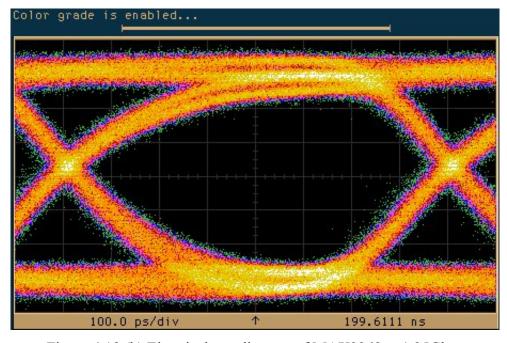

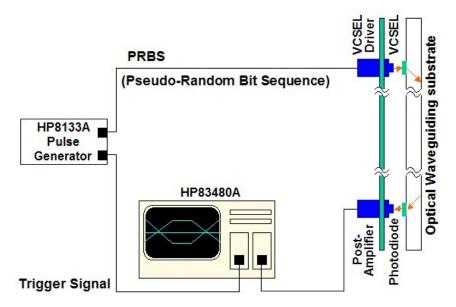

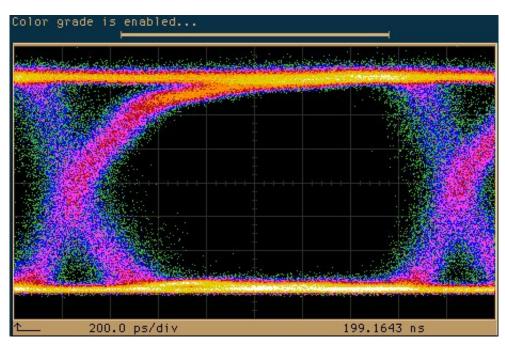

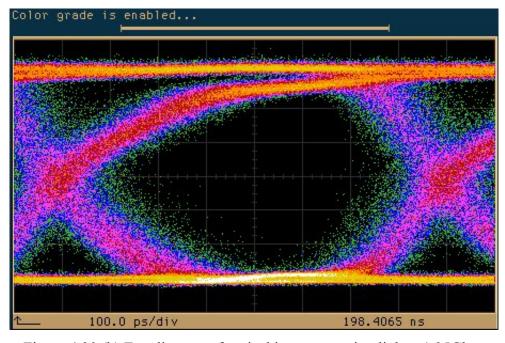

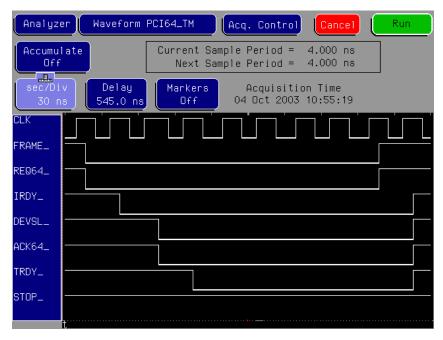

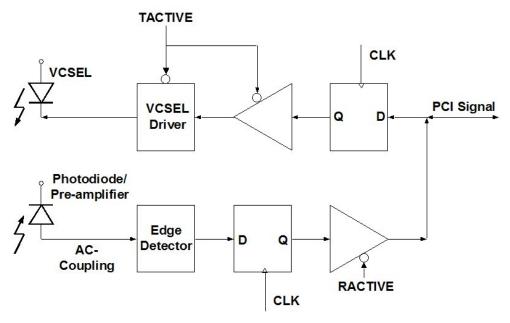

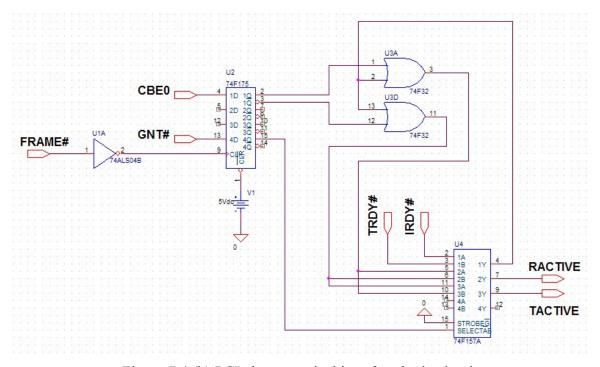

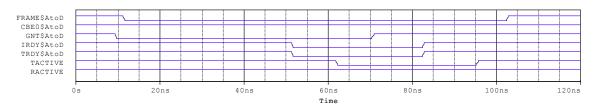

- (4) The same DuPont dry photopolymer film was exposed to the original recording beams again to form the second grating.