Copyright

by

Robin Matthew Tsang

2008

The Dissertation Committee for Robin Matthew Tsang certifies that this is the approved version of the following dissertation:

## High-Performance $\Delta \Sigma$ Analog-to-Digital Conversion

Committee:

Jonathan W. Valvano, Supervisor

Pio Balmelli

Francis Bostick

Robert Flake

Douglas Holberg

Earl Swartzlander

## High-Performance $\Delta\Sigma$ Analog-to-Digital Conversion

by

Robin Matthew Tsang, B.S.E.E.; M.S.E.E.

### Dissertation

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

### Doctor of Philosophy

## The University of Texas at Austin

${\rm May}~2008$

Dedicated to Mom and Dad for their hard work in raising the three of us.

# Acknowledgments

The person I owe all of this to is my supervisor, Professor Jonathan W. Valvano, who believed in me and encouraged me through the ups and downs of my pursuit for the doctoral degree. His teachings are nothing short of the most excellent. I learned a great deal from him both as an engineer and as a person. He always taught us to 'do the right thing', something I will never forget. Since the very first day, never once was he impatient with me, and never did I feel pressured at work. For the four years I have been Professor Valvano's student, I always felt happy and privileged to work for him. He gave me freedom to allocate my time as I like, which allowed me to do exercise and stay healthy and positive. This I believe was the key to the success of this work, and I thank him for that.

I thank Mom and Dad for being so supportive of me for all these years. There are no words that can describe how much I love them and how much they mean to me. Without their unconditional love, none of this would have been possible. There were times when things were difficult because Suzanne, Jason, and I all studied abroad, and money was scarce. But each and every time, with God's grace, we were able to get by just fine. Mom always believed that God will provide for us as long as we truly believed in Him and did the best we could with the talents given to us. I believe my work at this university is a testament to Him being by my side because there were so many obstacles I had to overcome to complete the project. Without anything short of a miracle, this would not have happened. Since a young age, Mom explained to me that everything can be taken away from you e.g., your car, your house, and your money, but no one can ever take away your education. This is at least partially why I continued on to the doctorate degree, and is true for Suzanne and Jason as well. Dad, with his infinite passion for sports, instilled the passion in me at a very young age. He taught me to use my time wisely and to play sports as much as I can. This really helped keep me healthy and happy throughout my life and I am so grateful for that.

I thank Professor Robert Flake for seeing the potential in me and accepting my application to the graduate program. He advised me to take the right classes and introduced me to the world of control systems. Professor Flake made an effort to form my Ph.D. committee, and much is appreciated. Professor Francis Bostick and Professor Earl Swartzlander posed excellent questions and motivated me to do better in every way. I especially thank Professor Swartzlander for editing my dissertation with care. His effort has helped improve this dissertation beyond my capability.

I thank Dr. Pio Balmelli for serving on my committee and for giving me such high quality feedback that ultimately led to much of my dissertation material. His enthusiasm and intelligent questions during my Ph.D. proposal and defense made it a fun and enjoyable experience for everyone. I thank Dr. Doug Holberg for offering to tape-out my chip. Although I was not able to take advantage of his offer, the process of trying to meet his deadline and then failing, led to my discovery of the new modulator topology which I proposed in this dissertation.

Besides my committee members, I thank Dr. Michael D. Cave for teaching me circuit design techniques with an industry perspective. We had stimulating discussions on how to improve yield, clock jitter, floor planning, and ADC characterization. Much of the things he taught me can only be gained through years of experience and I thank him for that. Dr. Byung-Geun Lee, my former research colleague, also contributed to the success of this work. His discipline has indirectly affected me in a very positive way. Him coming to the office at seven in the morning and not leaving until past dinner time, kept my own schedule and progress in check. His methodical circuit analysis techniques made me a better circuit designer. We had fruitful discussions on simulation, amplifier design, layout, and packaging, all of which led to critical circuit design decisions in this project. His help with setting up my simulation and layout tools is also greatly appreciated.

I thank Professor Eric Swanson for introducing me to the world of mixedsignal circuit design and for his teaching efforts at the University. Without his Mixed-Signal and Systems Design and Analysis course, I would have never stumbled onto such a fascinating topic. His help with debugging silicon and finding the root cause of the excess noise source is much appreciated. I also thank him for offering his time to meet with me once a week during the last semester to improve this dissertation. He helped me understand the intricacies and tradeoffs in data converter design like nobody else has.

I thank my research colleague, Nachiket Kharalkar, for his enthusiasm and encouragement. Over the years Nachiket has become a good friend. There were many semesters where we held the same teaching assistant (TA) position and organized laboratory assignments together for large undergraduate classes. His knowledge and hard work helped make my life as a TA enjoyable. Without him, things could have been much more difficult. Nachiket also worked the same hours as I did in the lab, often until the last scheduled shuttle-bus departure. His company during late nights in the lab helped keep me motivated from the circuit-design stage all the way to silicon characterization. I also thank him for his help with photographing my chip using his medical research equipment.

Daryl Goodnight and Paul Landers, two very friendly and knowledgable technicians at the University, offered sound advise for solder rework and reflow. Without their help, my make-shift PCB assembly process would not have operated as smoothly as it did. Robert Chua, the very best analog/mixed-signal test engineer I know, pointed me in the right direction by suggesting the prototype be placed in the smallest package possible, for the highest performance. He also suggested an asymmetrical die placement to reduce the inductance of sensitive pins. Without Robert, the prototype's performance would have been limited by the package, and therefore I am grateful for his help.

Some of my long-time EE friends from my undergraduate days, Khachatur Papanyan, Jon Perry, David Magness, Orson Lo, and Alvaro Garcia, were all supportive of my work. I especially thank Jon Perry for offering to lend me his own money to tape-out my chip. Although I declined his offer, I am sincerely grateful for his most unselfish heartfelt gesture. I thank Michel Azarian for his friendship and for his help with board-level circuit design. I thank Frank Raffaeli for letting me use his RACAL-DANA 9087 RF signal generator. Finally, I thank Professor Archie Holmes and Professor Jack Lipovski for writing my graduate school letterof-recommendation, which was the beginning to all of this.

ROBIN MATTHEW TSANG

The University of Texas at Austin May 2008

### High-Performance $\Delta \Sigma$ Analog-to-Digital Conversion

Publication No. \_\_\_\_\_

Robin Matthew Tsang, Ph.D. The University of Texas at Austin, 2008

Supervisor: Jonathan W. Valvano

This dissertation is about a new  $\Delta\Sigma$  analog-to-digital converter that offers enhanced quantization noise suppression at low oversampling ratios. This feature makes the converter attractive in applications where speed and resolution are simultaneously demanded. The converter exploits double-sampling for speed, and takes advantage of a new loop-filter to pin down passband quantization noise. A prototype is fabricated in 0.18- $\mu$ m CMOS and tested. Results show that at 200-MS/s, the converter achieves an effective number of bits (ENOB) of 12.2-b in a 12.5-MHz signal band while consuming 89-mW from a 1.8-V supply. Using a common performance metric that takes into account of ENOB and signal bandwidth, the prototype outperforms all previously-reported IEEE switched-capacitor  $\Delta\Sigma$  modulators.

# Contents

| Ackno             | wledgments                                                                              | $\mathbf{v}$ |

|-------------------|-----------------------------------------------------------------------------------------|--------------|

| $\mathbf{Abstra}$ | act                                                                                     | ix           |

| List of           | Tables                                                                                  | xiv          |

| List of           | Figures                                                                                 | xvi          |

| Chapt             | er 1 Introduction                                                                       | 1            |

| 1.1               | Overview                                                                                | 1            |

| 1.2               | A quick comparison with the state-of-the-art                                            | 3            |

| 1.3               | Basic operation of feedforward $\Delta\Sigma$ modulators $\ldots \ldots \ldots \ldots$  | 4            |

| 1.4               | Feedforward vs. feedback $\Delta\Sigma$ modulators $\ldots \ldots \ldots \ldots \ldots$ | 12           |

| 1.5               | Discrete-time vs. continuous-time $\Delta\Sigma$ modulators $\ldots \ldots \ldots$      | 14           |

| 1.6               | Basic design methodology for DT feedforward $\Delta\Sigma$ modulators                   | 16           |

| Chapt             | er 2 Existing $\Delta\Sigma$ Loop-Filter Topologies                                     | 18           |

| 2.1               | Conventional feedforward topologies                                                     | 18           |

|                   | 2.1.1 CIFF                                                                              | 19           |

|                   | 2.1.2 CRFF                                                                              | 21           |

|                   | 2.1.3 CIFF vs. CRFF for different OSRs                                                  | 24           |

| 2.2               | Low OSR feedforward $\Delta\Sigma$ modulators                                           | 30           |

|                  | 2.2.1   | Balmelli's $\Delta\Sigma$ modulator                                                                                                                              | 30 |

|------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                  | 2.2.2   | Jiang's $\Delta\Sigma$ modulator                                                                                                                                 | 34 |

| $\mathbf{Chapt}$ | er 3 A  | New and Improved Loop-Filter Topology                                                                                                                            | 36 |

| 3.1              | A new   | $5^{th}$ -order $\Delta\Sigma$ loop-filter                                                                                                                       | 36 |

| 3.2              | Design  | $\mathbf{n} $ methodology $\ldots \ldots \ldots$ | 40 |

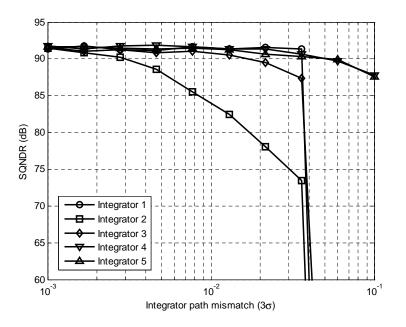

| 3.3              | Coeffic | cient sensitivity                                                                                                                                                | 46 |

| 3.4              | Integra | ator output swing                                                                                                                                                | 50 |

| Chapt            | er 4 I  | Double-Sampled $\Delta \Sigma$ A/D Conversion                                                                                                                    | 54 |

| 4.1              | Basic   | concept and advantages of double-sampling $\ldots$ $\ldots$ $\ldots$                                                                                             | 54 |

| 4.2              | Limita  | tions of double-sampling                                                                                                                                         | 56 |

|                  | 4.2.1   | Sampling-capacitor mismatch $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                   | 56 |

|                  | 4.2.2   | Systematic clock mismatch $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                     | 57 |

| 4.3              | Sender  | rowicz's fully-floating feedback network                                                                                                                         | 60 |

| Chapt            | er 5 A  | A New Double-Sampled $\Delta\Sigma$ Modulator for High-Speed                                                                                                     | d  |

| Lov              | v OSR   | A/D Conversion                                                                                                                                                   | 64 |

| 5.1              | Linear  | ized model                                                                                                                                                       | 65 |

| 5.2              | Design  | $h$ methodology $\dots \dots \dots$                              | 67 |

| 5.3              | Coeffic | cient scaling and quantization                                                                                                                                   | 73 |

| 5.4              | Circui  | t specifications                                                                                                                                                 | 82 |

|                  | 5.4.1   | Amplifier                                                                                                                                                        | 82 |

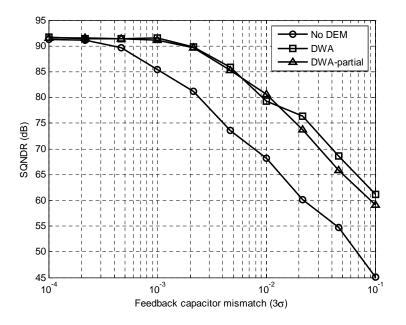

|                  | 5.4.2   | DWA feedback capacitor matching                                                                                                                                  | 85 |

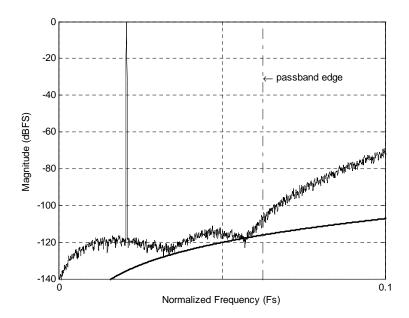

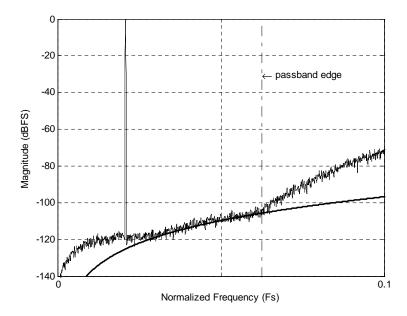

|                  | 5.4.3   | $2^{nd}$ integrator capacitor matching                                                                                                                           | 86 |

|                  | 5.4.4   | Isolation                                                                                                                                                        | 89 |

|                  | 5.4.5   | Clock jitter                                                                                                                                                     | 90 |

|                  | 5.4.6   | Quantizer offset                                                                                                                                                 | 91 |

|                  | 5.4.7   | Summary                                                                                                                                                          | 93 |

| Chapte | er 6 Pro       | ototype Implementation                                               | 97  |

|--------|----------------|----------------------------------------------------------------------|-----|

| 6.1    | $1^{st}$ integ | rator                                                                | 98  |

|        | 6.1.1 N        | Voise analysis                                                       | 98  |

|        | 6.1.2 S        | witch-level design                                                   | 101 |

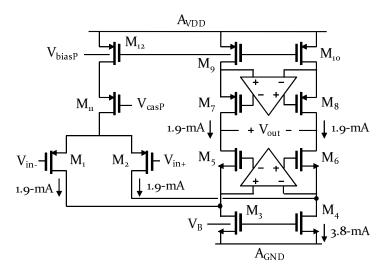

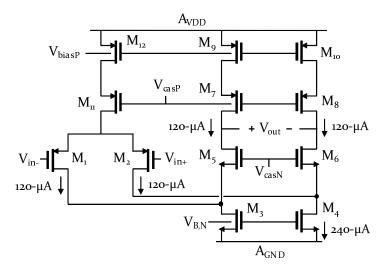

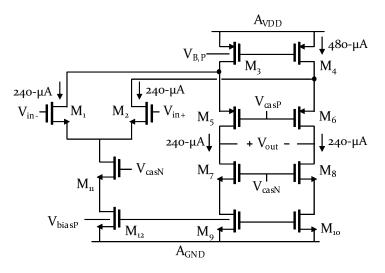

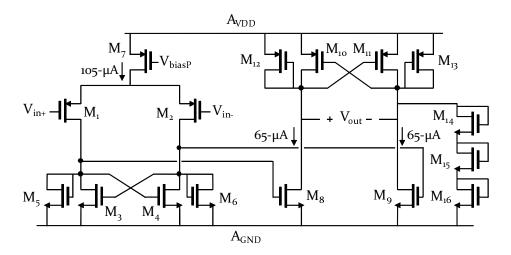

| 6.2    | Gain-boo       | osted folded-cascode amplifier                                       | 106 |

|        | 6.2.1 N        | Iain amplifier                                                       | 106 |

|        | 6.2.2 C        | Gain-boosters                                                        | 109 |

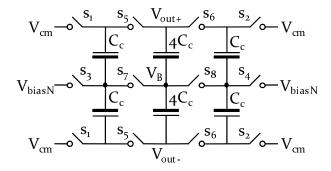

|        | 6.2.3 S        | witched-capacitor common-mode feedback $\ldots \ldots \ldots \ldots$ | 111 |

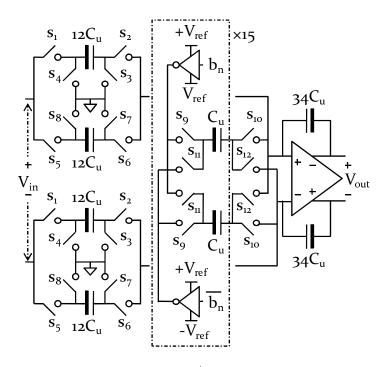

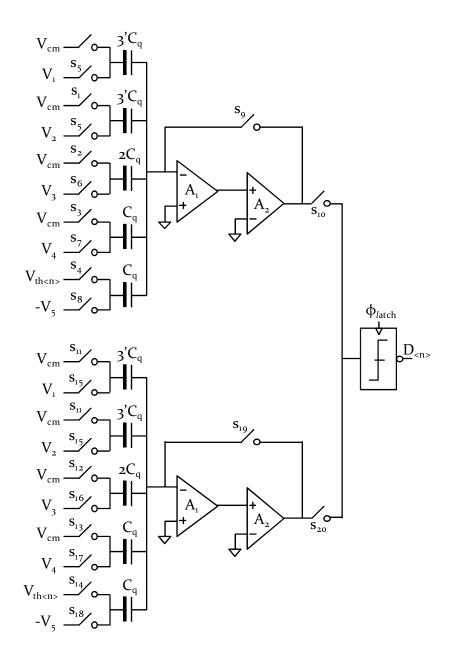

| 6.3    | A 4-b Fl       | as<br>h quantizer with time-interleaved offset-cancelation           | 112 |

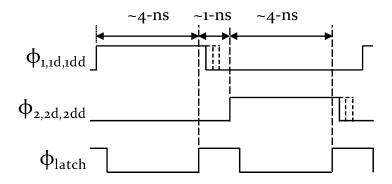

|        | 6.3.1 S        | witch-level implementation                                           | 114 |

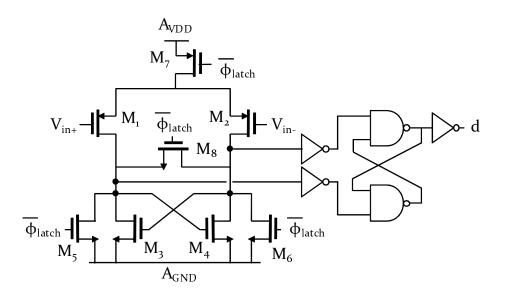

|        | 6.3.2 P        | Preamplifiers                                                        | 118 |

|        | 6.3.3 R        | Regenerative latch                                                   | 119 |

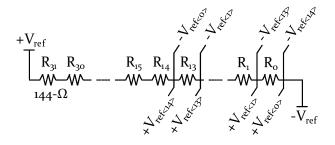

|        | 6.3.4 R        | Reference ladder                                                     | 122 |

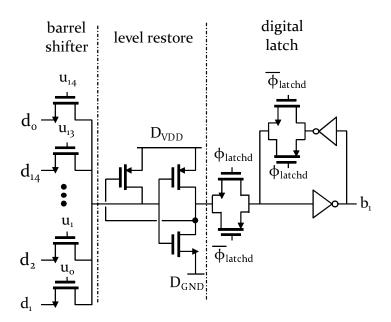

| 6.4    | Data We        | eighted-Averaging                                                    | 122 |

| 6.5    | 4-b DAC        | 9                                                                    | 124 |

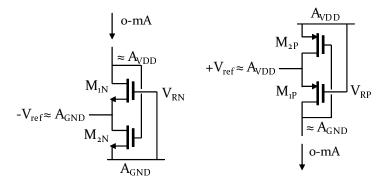

| 6.6    | Referenc       | e buffer                                                             | 124 |

| 6.7    | Bias circ      | cuits                                                                | 125 |

| Chapte | er 7 Pei       | ripheral Circuits                                                    | 128 |

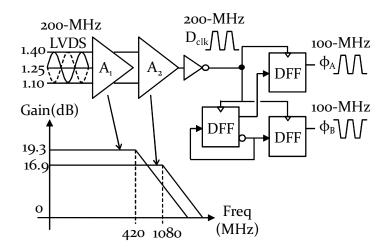

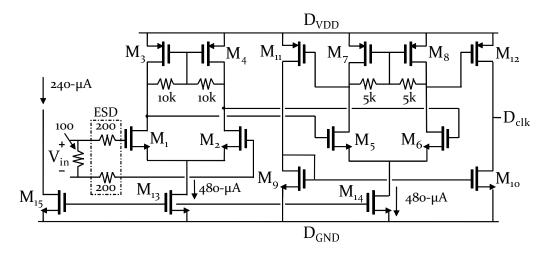

| 7.1    | LVDS cl        | ock amplifier                                                        | 128 |

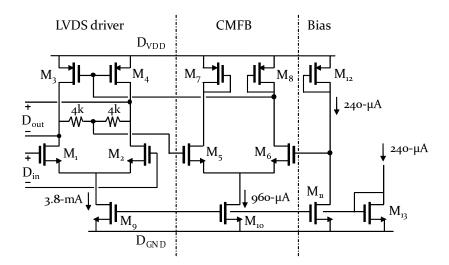

| 7.2    | LVDS tr        | ansmitter                                                            | 132 |

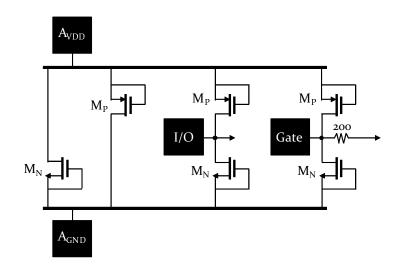

| 7.3    | Electro-s      | static discharge (ESD) circuitry                                     | 135 |

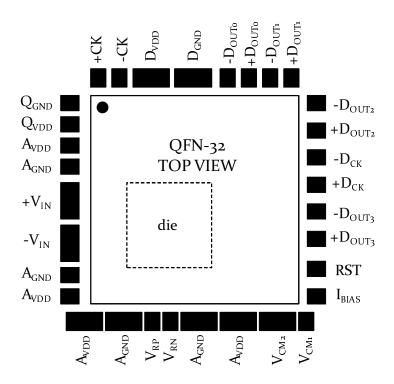

| 7.4    | Packagin       | ıg                                                                   | 136 |

| 7.5    | Pin assig      | gnment                                                               | 138 |

| Chapte | er 8 Pro       | ototype Characterization                                             | 142 |

| 8.1    | Referenc       | e buffer adjustment                                                  | 143 |

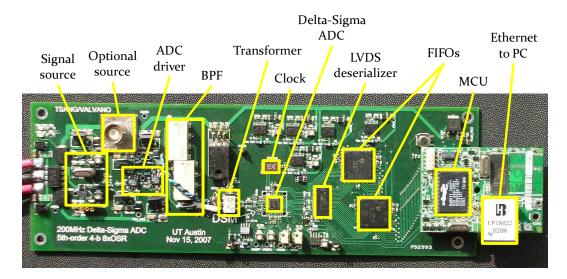

| 8.2    | DUT bo         | ard overview                                                         | 144 |

| 8.3     | Test measurement results                    | 146 |

|---------|---------------------------------------------|-----|

| 8.4     | PCB construction                            | 153 |

|         | 8.4.1 Reflow process                        | 154 |

|         | 8.4.2 Equipment and tools for solder reflow | 154 |

| Chapte  | er 9 Discussion                             | 156 |

| 9.1     | Target SNDR vs. measured SNDR               | 156 |

|         |                                             | 1   |

| Chapte  | er 10 Conclusion                            | 158 |

| 10.1    | Summary                                     | 158 |

| 10.2    | 2 Suggestions for future work               | 159 |

| Bibliog | graphy                                      | 161 |

| Vita    |                                             | 170 |

# List of Tables

| 1.1 | IEEE-published $\Delta\Sigma$ modulators                                               | 7   |

|-----|----------------------------------------------------------------------------------------|-----|

| 2.1 | $16 \times \text{OSR}$ coefficients                                                    | 25  |

| 2.2 | $8 \times \text{OSR coefficients}$                                                     | 29  |

| 3.1 | The proposed modulator                                                                 | 43  |

| 3.2 | The proposed modulator coefficient sensitivity                                         | 47  |

| 3.3 | CIFF coefficient sensitivity                                                           | 48  |

| 3.4 | CRFF coefficient sensitivity                                                           | 49  |

| 3.5 | Balmelli's modulator coefficient sensitivity                                           | 49  |

| 5.1 | The proposed modulator                                                                 | 69  |

| 5.2 | The proposed double-sampled modulator coefficient sensitivity $\ . \ .$                | 73  |

| 5.3 | Amplifier dc gain requirements                                                         | 84  |

| 5.4 | Yield percentage for various $3\sigma$ quantizer offsets $\ldots \ldots \ldots \ldots$ | 93  |

| 5.5 | Circuit specifications chosen for 78-dB SNDR prototype $\ . \ . \ . \ .$               | 96  |

| 6.1 | Half-circuit sampling capacitance for integrators.                                     | 102 |

| 6.2 | $1^{st}$ integrator switch summary                                                     | 104 |

| 6.3 | $1^{st}$ integrator amplifier                                                          | 108 |

| 6.4 | Integrator bias current.                                                               | 108 |

| 6.5  | Gain-booster for NMOS cascode transistors |

|------|-------------------------------------------|

| 6.6  | Gain-booster for PMOS cascode transistors |

| 6.7  | $1^{st}$ integrator CMFB switch summary   |

| 6.8  | Comparator switch summary                 |

| 6.9  | Comparator preamplifier                   |

| 6.10 | Comparator latch                          |

| 6.11 | Reference buffer                          |

| 6.12 | Bias circuit                              |

|      |                                           |

| 7.1  | LVDS clock amplifier                      |

| 7.2  | LVDS clock amplifier jitter summary       |

| 7.3  | LVDS transmitter                          |

| 7.4  | ESD snapback transistors                  |

| 7.5  | Pin summary                               |

|      |                                           |

| 8.1  | Power supply range                        |

| 8.2  | Measured performance                      |

# List of Figures

| 1.1 | Performance comparison with IEEE-published DT and CT $\Delta\Sigma$ mod-         |    |

|-----|----------------------------------------------------------------------------------|----|

|     | ulators                                                                          | 5  |

| 1.2 | Silicon area comparison with IEEE-published DT and CT $\Delta\Sigma$ mod-        |    |

|     | ulators                                                                          | 6  |

| 1.3 | A 4-b ADC put in a feedback configuration together with a loop-filter            |    |

|     | and 4-b DAC can achieve >4-b resolution if oversampled                           | 8  |

| 1.4 | Noise-shaping can push quantization noise out-of-band. Shows how                 |    |

|     | a 4-b ADC can achieve 15-b performance (87.5-dB SQNR) through                    |    |

|     | feedback, filtering, and oversampling. As shown, the OSR is $8\times.$ $$ .      | 9  |

| 1.5 | Assuming the DAC does not introduce any errors, the modulator's                  |    |

|     | quantization error is solely due to the ADC and is modeled by $Q(z)$ .           | 9  |

| 1.6 | Pole-zero plots of the STF, NTF, and $L(z)$ of a feedforward $\Delta\Sigma$ mod- |    |

|     | ulator. STF and NTF share the same set of poles. Poles of $L(z)$                 |    |

|     | mirror and become the zeros of the NTF                                           | 11 |

| 1.7 | Frequency response of the STF, NTF, and $L(z)$ of a feedforward $\Delta\Sigma$   |    |

|     | modulator. Peaks in $L(z)$ mirror to become zeros in the NTF                     | 12 |

| 1.8 | A feedforward $\Delta\Sigma$ modulator                                           | 13 |

| 1.9 | A feedback $\Delta\Sigma$ modulator.                                             | 13 |

| 2.1 | $5^{th}$ -order cascade-of-integrators feedforward form (CIFF)                   | 19 |

| 2.2  | Possible NTF zero positions in the z-plane for a CIFF $\Delta\Sigma$ modulator.                 | 20 |

|------|-------------------------------------------------------------------------------------------------|----|

| 2.3  | Local feedback loop of CIFF.                                                                    | 20 |

| 2.4  | $5^{th}\text{-}\mathrm{order}$ cascade-of-resonators feed<br>forward form (CRFF)                | 22 |

| 2.5  | Possible NTF zero positions in the z-plane for a CRFF $\Delta\Sigma$ modulator.                 | 22 |

| 2.6  | Local feedback loop of CRFF                                                                     | 23 |

| 2.7  | Frequency response of CIFF and CRFF at $16 \times$ OSR                                          | 26 |

| 2.8  | Pole-zero plot of CIFF and CRFF at $16 \times$ OSR                                              | 26 |

| 2.9  | Frequency response of CIFF and CRFF at $8 \times$ OSR                                           | 28 |

| 2.10 | Pole-zero plot of CIFF and CRFF at $8 \times$ OSR                                               | 29 |

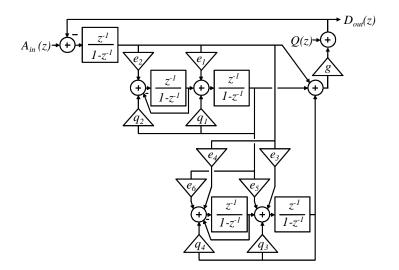

| 2.11 | Balmelli's modulator                                                                            | 31 |

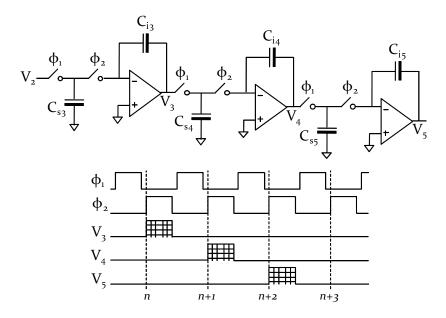

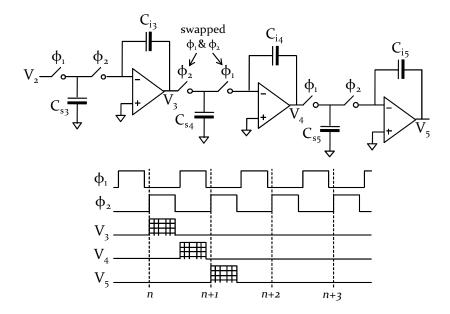

| 2.12 | Conventional clocking scheme                                                                    | 32 |

| 2.13 | Balmelli's modulator clocking scheme for the $4^{th}$ and $5^{th}$ integrators.                 | 32 |

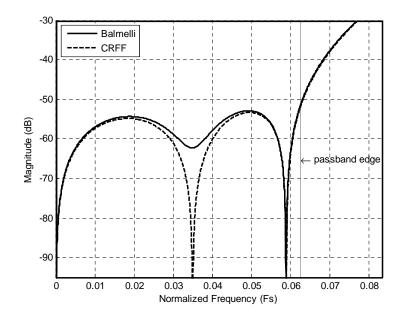

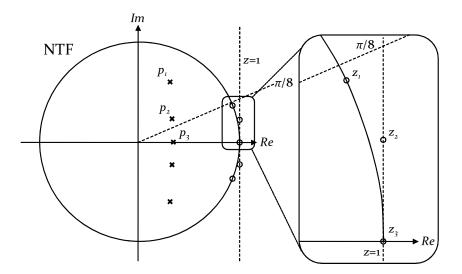

| 2.14 | Frequency response of Balmelli's modulator at $8\times$ OSR                                     | 33 |

| 2.15 | Pole-zero plot of Balmelli's modulator at $8 \times$ OSR                                        | 34 |

| 2.16 | Jiang's modulator.                                                                              | 35 |

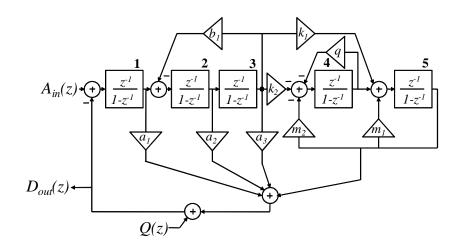

| 3.1  | The proposed modulator.                                                                         | 37 |

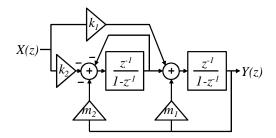

| 3.2  | Jiang's biquad cell.                                                                            | 37 |

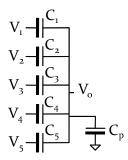

| 3.3  | Passive summation                                                                               | 39 |

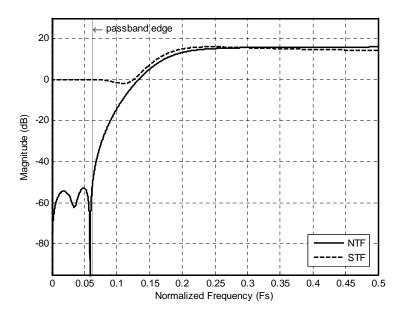

| 3.4  | NTF and STF                                                                                     | 44 |

| 3.5  | The proposed modulator. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 44 |

| 3.6  | Pole-zero plot of the proposed topology                                                         | 45 |

| 3.7  | First-order coefficient sensitivity analysis.                                                   | 48 |

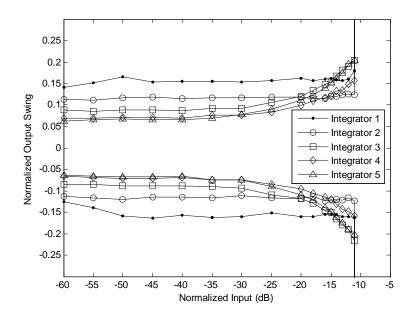

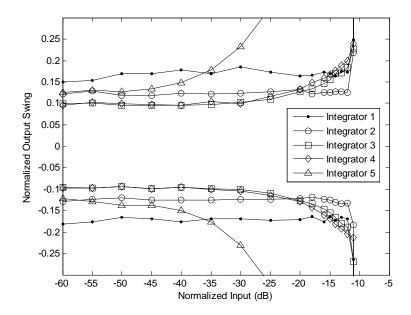

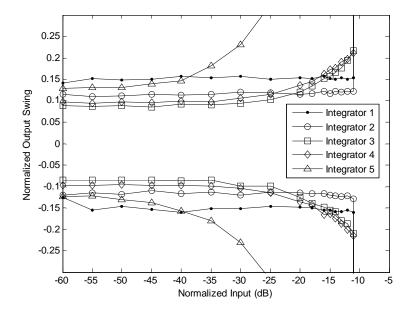

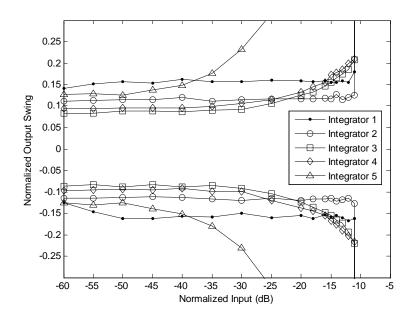

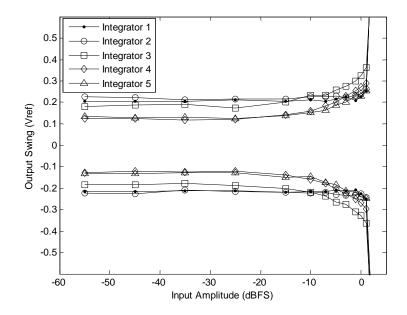

| 3.8  | The proposed modulator's output swing for different integrators                                 | 51 |

| 3.9  | CIFF output swing for different integrators                                                     | 52 |

| 3.10 | CRFF output swing for different integrators.                                                    | 52 |

| 3.11 | Balmelli's modulator output swing for different integrators                                     | 53 |

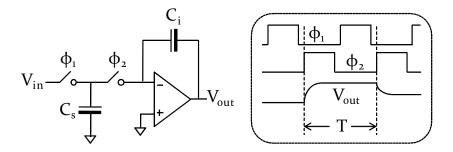

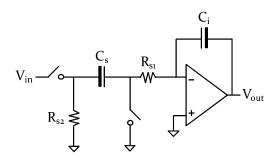

| 4.1  | Single-sampled integrator.                                                               | 55 |

|------|------------------------------------------------------------------------------------------|----|

| 4.2  | Double-sampled integrator.                                                               | 55 |

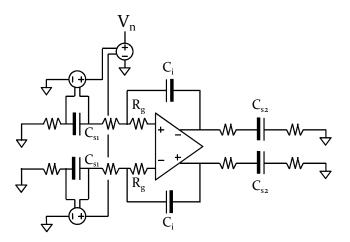

| 4.3  | Integrator with a fully-floating input network                                           | 60 |

| 4.4  | Bilinear feedback with conventional (nonbilinear) input. $\ldots$ .                      | 63 |

| 4.5  | Bilinear feedback with conventional (nonbilinear) input $z\operatorname{-domain}$ model. | 63 |

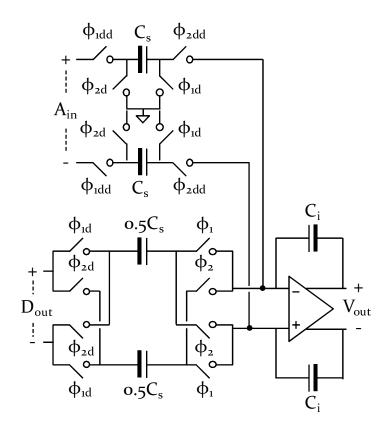

| 5.1  | A double-sampled modulator with Senderowicz's fully-floating feed-                       |    |

|      | back network                                                                             | 65 |

| 5.2  | Adding a degree-of-freedom to a modulator with fully-floating feedback.                  | 65 |

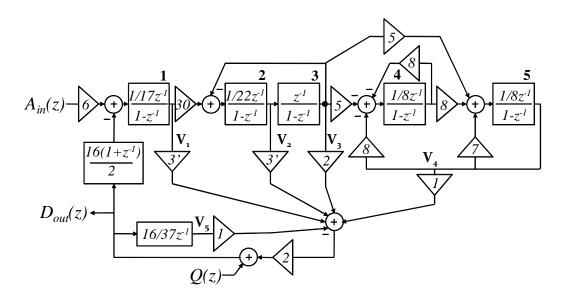

| 5.3  | The proposed 5 <sup>th</sup> -order double-sampled $\Delta\Sigma$ modulator              | 67 |

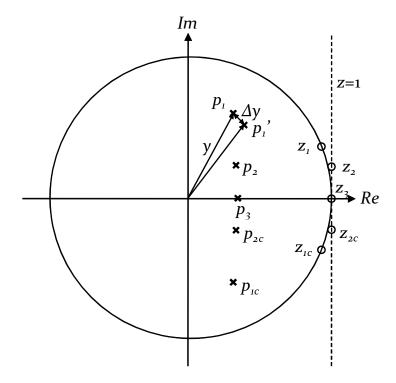

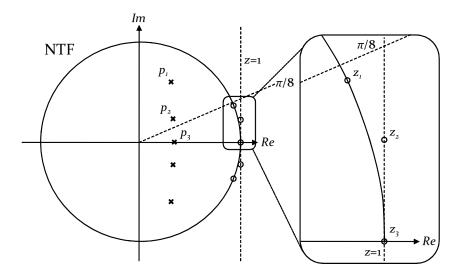

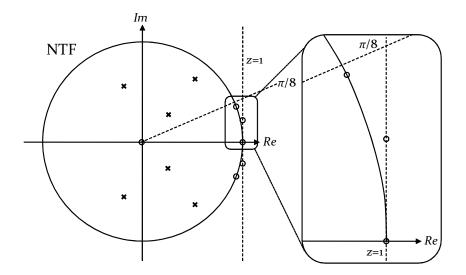

| 5.4  | Unquantized pole-zero locations of for the proposed modulator                            | 70 |

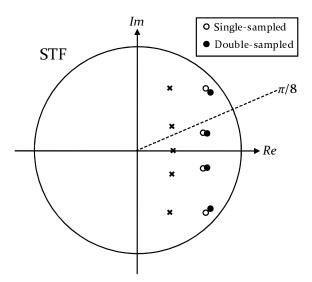

| 5.5  | Movement of STF zeros when double-sampled                                                | 71 |

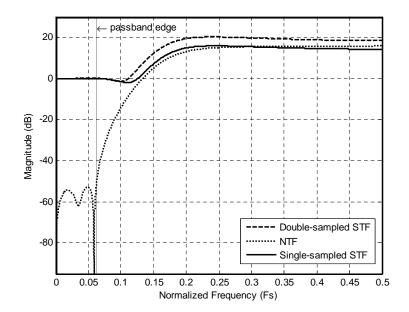

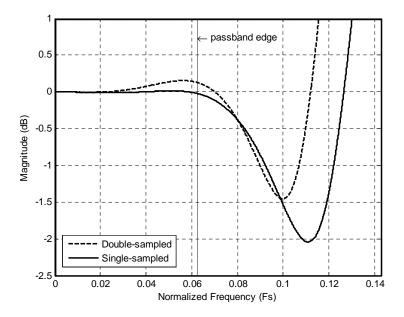

| 5.6  | STF and NTF of double-sampled modulator. $\ldots$ $\ldots$ $\ldots$ $\ldots$             | 71 |

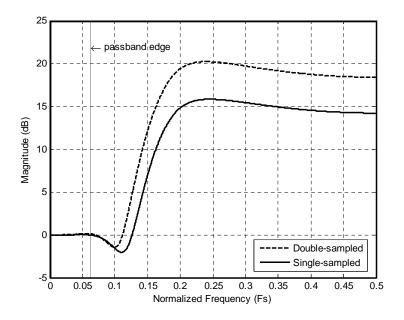

| 5.7  | STF change after double-sampling                                                         | 72 |

| 5.8  | STF change after double-sampling (close-in view). $\ldots$                               | 72 |

| 5.9  | The proposed 5 <sup>th</sup> -order double-sampled $\Delta\Sigma$ modulator              | 75 |

| 5.10 | Internal signal swing for various stages after quantization                              | 76 |

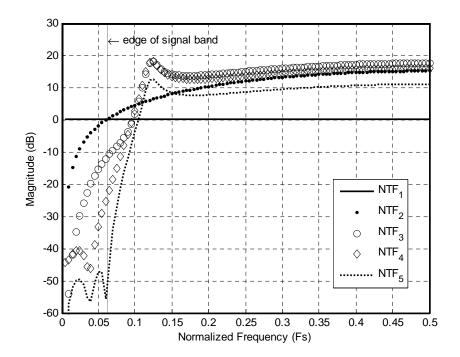

| 5.11 | NTF pole-zero locations after quantization.                                              | 76 |

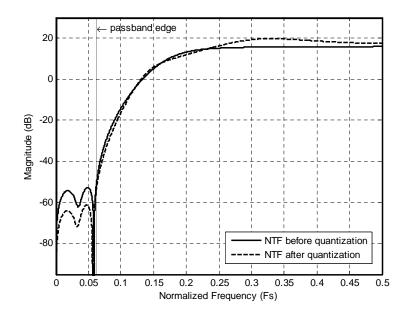

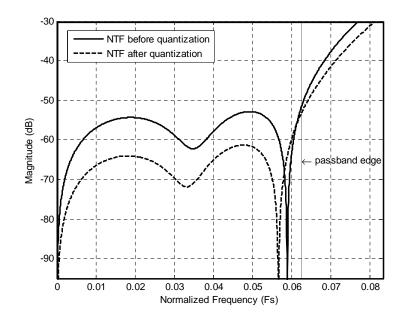

| 5.12 | NTF before and after quantization                                                        | 77 |

| 5.13 | NTF before and after quantization (close-in view). $\ldots$                              | 78 |

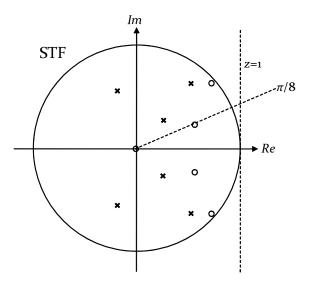

| 5.14 | STF pole-zero locations after quantization.                                              | 79 |

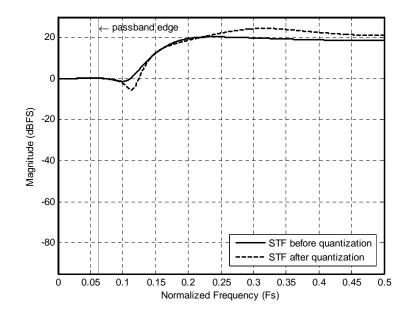

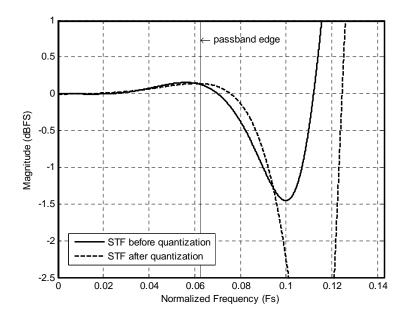

| 5.15 | STF before and after quantization                                                        | 79 |

| 5.16 | STF before and after quantization (close-in view). $\ldots$                              | 80 |

| 5.17 | Noise transfer functions from internal nodes to the input node                           | 81 |

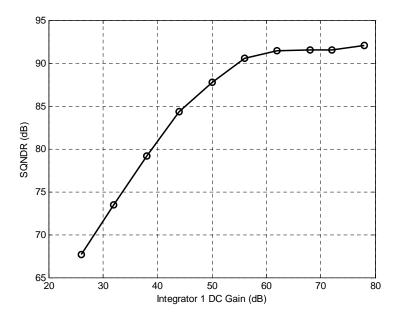

| 5.18 | $1^{st}$ integrator amplifier dc gain requirement                                        | 83 |

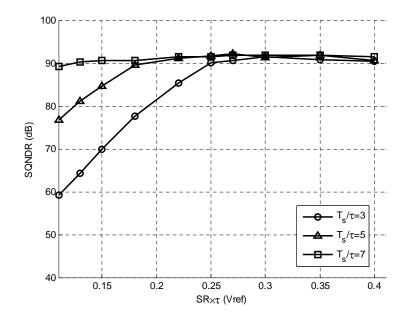

| 5.19 | $1^{st}$ integrator amplifier slew-rate and settling requirements                        | 85 |

| 5.20 | DWA capacitor matching requirement $(3\sigma)$                                           | 87 |

| 5.21 | $2^{nd}$ integrator $\pm 0.3\%$ input capacitor mismatch.                                | 88 |

| 5.22 | $2^{nd}$ integrator $\pm 1\%$ input capacitor mismatch                         | 88  |

|------|--------------------------------------------------------------------------------|-----|

| 5.23 | $2^{nd}$ integrator input capacitor mismatching requirement                    | 89  |

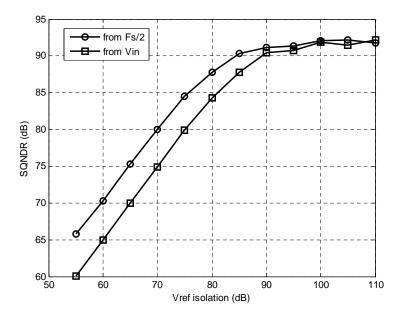

| 5.24 | $V_{ref}$ isolation from $\frac{F_s}{2}$ and $V_{in}$                          | 90  |

| 5.25 | Gaussian distributed clock jitter $(3\sigma)$ with respect to clock period vs. |     |

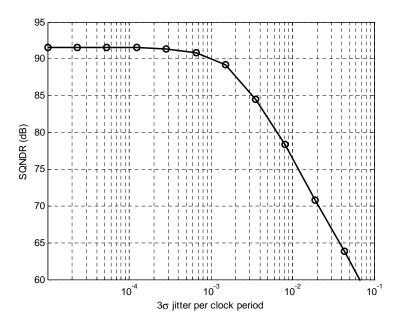

|      | SQNDR                                                                          | 92  |

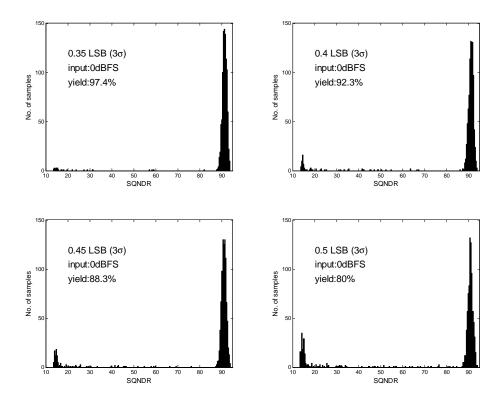

| 5.26 | Effect of quantizer offset on overall yield at 0-dBFS input $\ . \ . \ .$      | 94  |

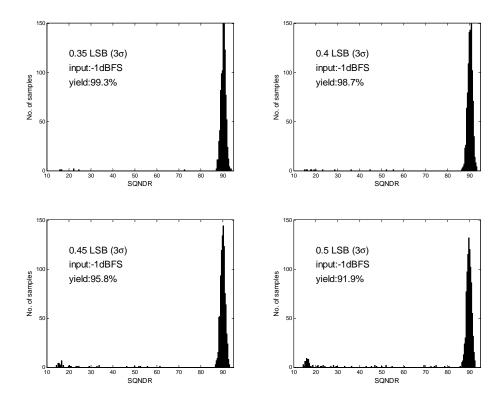

| 5.27 | Effect of quantizer offset on overall yield at -1-dBFS input                   | 95  |

| 6.1  | Single-ended switched-capacitor integrator during charge-transfer 1            | 100 |

| 6.2  |                                                                                | 103 |

| 6.3  |                                                                                | 103 |

| 6.4  | Folded-cascode amplifier with folded-cascode gain-boosting amplifiers.         |     |

|      |                                                                                |     |

| 6.5  |                                                                                | 109 |

| 6.6  | Gain-booster for PMOS cascode transistors                                      | 10  |

| 6.7  | Double-sampled common-mode feedback circuit.                                   | 11  |

| 6.8  | Single-ended version of time-interleaved comparator                            | 115 |

| 6.9  | Two-stage preamplifier for comparator unit-cell                                | 18  |

| 6.10 | Comparator regenerative latch                                                  | 121 |

| 6.11 | Quantizer reference ladder.                                                    | 122 |

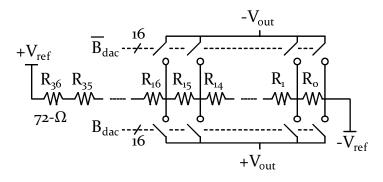

| 6.12 | DWA feedback path                                                              | 123 |

| 6.13 | 4-b DAC                                                                        | 124 |

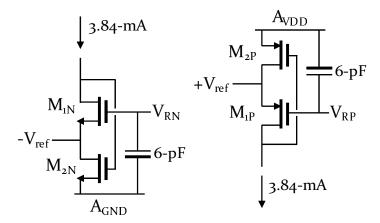

| 6.14 | Differential reference buffers.                                                | 125 |

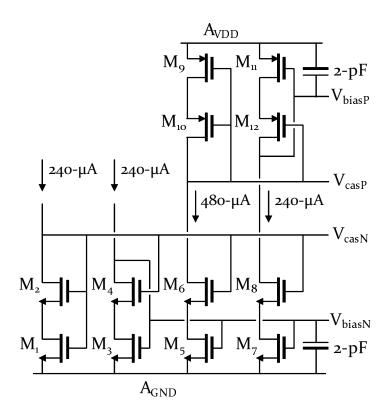

| 6.15 | Biasing circuit for amplifiers                                                 | 126 |

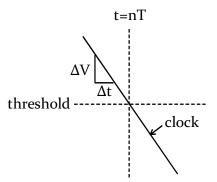

| 7.1  | Electronic noise to jitter translation.                                        | 190 |

|      | U U                                                                            | 129 |

| 7.2  |                                                                                | 131 |

| 7.3  | LVDS clock two-stage amplifier                                                 | 133 |

| 7.4  | LVDS output driver                                                             | 135 |

| 7.5  | ESD topology                                                                         |

|------|--------------------------------------------------------------------------------------|

| 7.6  | Die orientation skewed to corner of package                                          |

| 7.7  | Pin-assignment                                                                       |

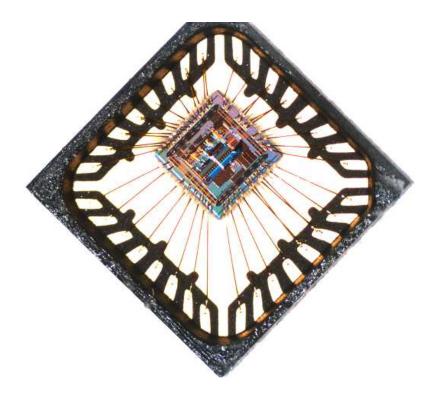

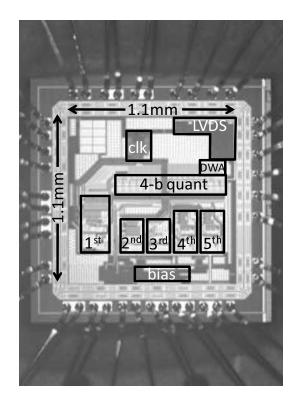

| 8.1  | Die micrograph                                                                       |

| 8.2  | Turning off the reference buffer to set $\pm V_{ref}$ equal to the supply rails. 144 |

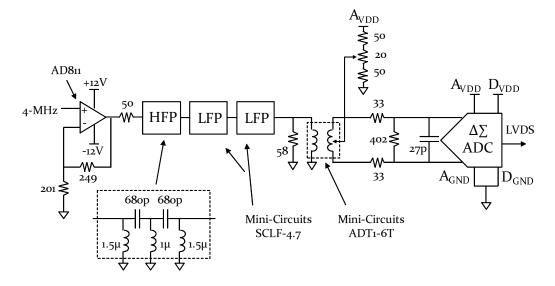

| 8.3  | DUT board analog front-end                                                           |

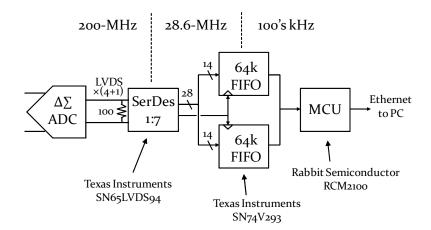

| 8.4  | DUT board digital back-end                                                           |

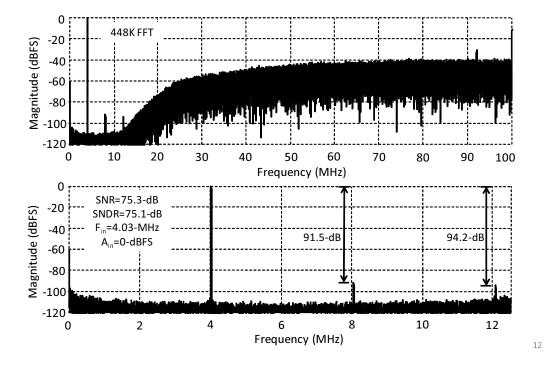

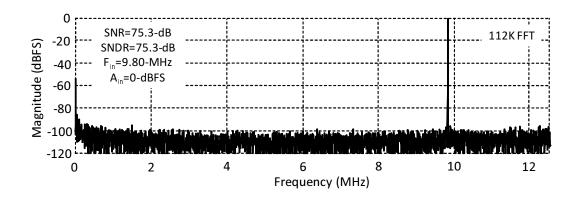

| 8.5  | Measured spectrum (full and close-in views)                                          |

| 8.6  | Measured spectrum to test for jitter sensitivity                                     |

| 8.7  | Measured SNR and SNDR vs input amplitude                                             |

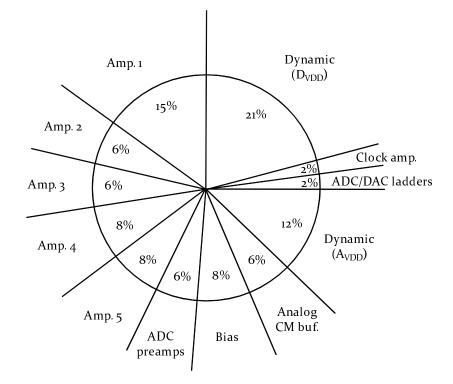

| 8.8  | Power consumption breakdown of prototype modulator 151                               |

| 8.9  | Performance comparison with IEEE-published DT and CT $\Delta\Sigma$ mod-             |

|      | ulators                                                                              |

| 8.10 | DUT board                                                                            |

| 8.11 | DUT board                                                                            |

| 9.1  | Measuring aliased amplifier noise                                                    |

## Chapter 1

# Introduction

#### 1.1 Overview

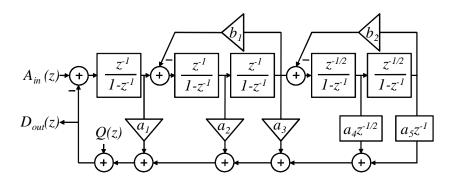

Discrete-time (DT) switched-capacitor (SC)  $\Delta\Sigma$  analog-to-digital converters (ADCs) have long been a workhorse in high-performance analog-to-digital conversion. These converters are popular because they can achieve high-resolution under a limited power-supply voltage and are tolerant against process and temperature variations. Unfortunately, due to its oversampling nature, achieving a wide bandwidth while maintaining high-resolution and linearity is difficult. To the best knowledge of the author, no DT  $\Delta\Sigma$  modulator with an effective number of bits (ENOB) > 12-b and a signal bandwidth > 10-MHz has been reported to date. This work demonstrates with a novel feedforward DT loop-filter and a time-interleaved offset-canceled comparator, that such performance (12.2-b ENOB, 12.5-MHz) can be achieved in a 0.18- $\mu$ m CMOS process with relatively low power (89-mW), relatively small silicon area (0.8-mm<sup>2</sup>), and no calibration.

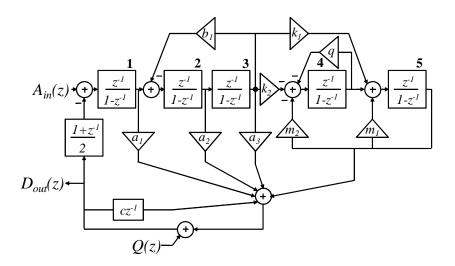

To maximize signal bandwidth for a given process technology, a low oversampling ratio (OSR) is desired. However, quantization noise, which normally can be reduced down to negligible levels in mid to high OSR modulators, can become a significant source of error in low OSR modulators. For example, at  $8 \times$  OSR, the popular cascade-of-integrators-feedforward form (CIFF)  $\Delta\Sigma$  modulator [20] has a peak signal-to-quantization-noise ratio (SQNR) of only 81.5-dB with 4-b quantization and an out-of-band noise gain of 6. In practice, a 10-dB margin between the target SNR and the SQNR is often added on to ensure a robust design. This suggests a modulator with an SQNR of 81.5-dB has a final SNR of 71.5-dB, which is less than 12-b ENOB performance. This leads to the main contribution of this work, which is the introduction of a new loop-filter topology that uses strictly delaying  $(z^{-1})$  integrators similar to CIFF, but provides 86.5-dB of SQNR (5-dB advantage over CIFF). Unlike Balmelli's loop-filter [4] which also provides better SQNR than CIFF, this loop-filter can be *double-sampled* in a straightforward manner so that the bandwidth of the operational transconductance amplifier (OTA) is fully exploited. In addition to the loop-filter, a time-interleaved comparator suitable for accurate high-speed signal quantization in a double-sampled converter is introduced. This comparator plays a key role in the successful implementation of the prototype  $\Delta\Sigma$ modulator in this research work.

The rest of this dissertation is organized as follows. In the remaining parts of this chapter, state-of-the-art DT and continuous-time (CT)  $\Delta\Sigma$  modulators reported in IEEE literature will be compared to the prototype herein in terms of performance and silicon area. The basic operation of feedforward DT  $\Delta\Sigma$  modulators will be discussed, followed by an outline of the differences between feedforward and feedback modulators, and DT and CT modulators. Chapter 2 discusses the bottlenecks that limit performance in conventional and recently-published feedforward  $\Delta\Sigma$  loop-filters. Chapter 3 introduces the new loop-filter topology suitable for high-speed double-sampled low OSR  $\Delta\Sigma$  modulation and explains why this topology advances the state-of-the-art. Chapter 4 goes over the basic concept of double-sampling and the bilinear feedback network [5] vital to combating capacitor mismatch in the global feedback path of a double-sampled  $\Delta\Sigma$  modulator. Chapter 5 introduces the new double-sampled  $\Delta\Sigma$  modulator that exploits the proposed loopfilter for efficient high-speed low OSR analog-to-digital conversion. Chapter 6 details the prototype implementation and introduces the new time-interleaved comparator for accurate high-speed signal quantization in a double-sampled converter. Chapter 7 elaborates on the peripheral circuits used to complete the prototype, including a Low-Voltage Differential Signalling (LVDS) clock amplifier, LVDS transmitters, electro static discharge (ESD) circuitry, and biasing circuits. Chapter 8 describes the test setup, measurement results, and PCB construction. Chapter 9 discusses some of the difficulties faced by the author during design, prototyping, and testing. Finally, a summary of this research and suggestions for future work follows in Chapter 10.

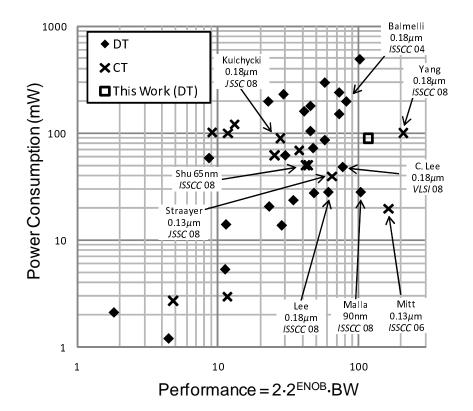

#### **1.2** A quick comparison with the state-of-the-art

A common figure-of-merit (FOM) used to compare  $\Delta\Sigma$  modulators is defined as total power consumption divided by performance, where performance is defined as the product of the effective number of bits (2<sup>ENOB</sup>) and the decimated samplingrate (2·Bandwidth):

$$FOM = \frac{Power}{2 \cdot 2^{ENOB} \cdot Bandwidth} .$$

(1.1)

Here, ENOB =  $\frac{SNDR-1.76}{6.02}$  and SNDR, in units of decibels (dB), represents the signal-to-noise-and-distortion ratio of the modulator [27]. The rationale behind the FOM is that it provides a measure of how much power is needed to achieve a certain performance. In ADCs, performance is generally accepted as the resolution and linearity it provides i.e., ENOB, and the speed at which it operates (Nyquist frequency). Naturally, the lower the FOM, the more efficient the modulator. This FOM has units of *Joules per conversion* and is often scaled by a factor of  $10^{-12}$  and

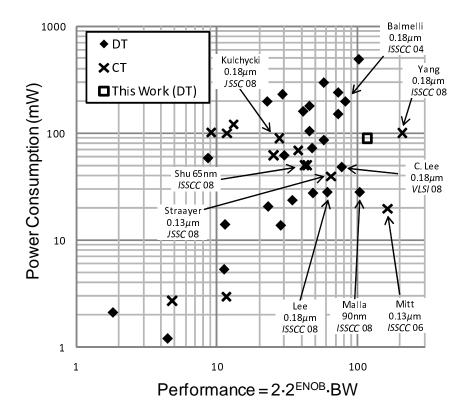

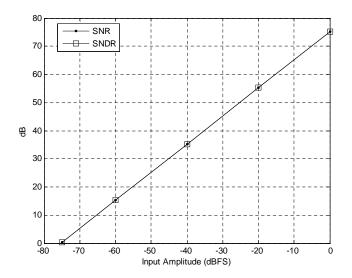

annotated as pJ/conversion. To compare the measured prototype performance of this work with the state-of-the-art, a list of IEEE-reported  $\Delta\Sigma$  modulators<sup>1</sup>, both DT and CT, is complied and plotted on a log-log scale in Figure 1.1. A trend is visible in the graph between performance and power consumption, which indicates that higher performance generally requires more power. Here, performance is defined as the denominator term of the FOM. Comparing all DT modulators, this work not only bucks the trend, but is also the highest-performing DT  $\Delta\Sigma$  modulator. As will be discussed in Chapter 9, the prototype's SNDR is still 3-dB short of the original target. However, the discrepancy is likely due to a now-known error made during OTA noise simulation and can be corrected in a future revision of the circuit.

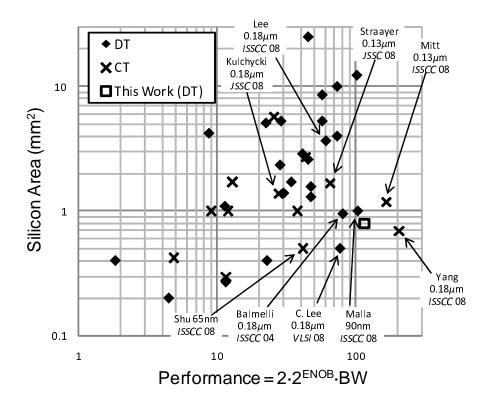

Besides efficiency, ADCs can be compared in terms of its physical size with respect to performance. Plotted on a log-log scale in Figure 1.2 are the silicon areas of the same modulators in the previous figure. A weaker but still visible trend suggests higher performance usually demands larger silicon areas. Comparing this work to others, this modulator is physically small for the performance it delivers. Smaller silicon area can translate to lower cost and eases integration into larger chips. For a list of the data-points used here, please refer to Table 1.1.

### **1.3** Basic operation of feedforward $\Delta\Sigma$ modulators

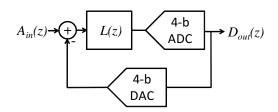

At a high-level, the feedforward  $\Delta\Sigma$  modulator consists of a loop-filter and a quantizer placed in feedback configuration. The modulator is operated at a rate much higher than the maximum input signal frequency of interest. A block-level diagram of a 4-b  $\Delta\Sigma$  modulator is shown in Figure 1.3. A 4-b digital-to-analog converter (DAC) in the feedback path converts the quantized output back to the analog domain so proper feedback can be applied. The loop-filter, L(z), provides the necessary

<sup>&</sup>lt;sup>1</sup>Not an exhaustive list, but to the best knowledge of the author, the highest-performing  $\Delta\Sigma$  modulators reported in IEEE literature up until Apr. 2008 have been included.

Figure 1.1: Performance comparison with IEEE-published DT and CT  $\Delta\Sigma$  modulators.

Figure 1.2: Silicon area comparison with IEEE-published DT and CT  $\Delta\Sigma$  modulators.

| Author          | Year | Type          | OSR  | Tech.            | MHz   | SNDR | mW    | $\mathrm{mm}^2$ |

|-----------------|------|---------------|------|------------------|-------|------|-------|-----------------|

| Paton [54]      | 2004 | CT            | 10   | 0.13-µm          | 15    | 63.7 | 70    | 1               |

| Breems [55]     | 2004 | CT            | 8    | 0.18-μm          | 10    | 58   | 122.4 | 1.7             |

| Yan [15]        | 2004 | CT            | 16   | $0.5-\mu m$      | 1.1   | 83   | 62    | 5.76            |

| Dörrer [56]     | 2005 | CT            | 26   | 0.13-µm          | 2     | 71   | 3     | 0.3             |

| Mitteregger [1] | 2006 | CT            | 16   | .13-μm           | 20    | 74   | 20    | 1.2             |

| Caldwell [16]   | 2006 | СТ            | 5    | 0.18-μm          | 10    | 57.2 | 101   | 1               |

| Caldwell [16]   | 2006 | CT            | 5    | 0.18-μm          | 20    | 48.8 | 103   | 1               |

| Li [14]         | 2007 | CT            | 12   | 0.25-µm          | 2.5   | 80.5 | 50    | 2.73            |

| Song [58]       | 2008 | CT            | 37.5 | 0.25-µm          | 2     | 63.4 | 2.7   | 0.42            |

| Shu [59]        | 2008 | CT            | 16   | 65-nm            | 8     | 70   | 50    | 0.5             |

| Yang [2]        | 2008 | CT            | 32   | 0.18-µm          | 10    | 82   | 100   | 0.7             |

| Marques [60]    | 1998 | SC            | 24   | $1-\mu m$        | 1     | 85   | 230   | 5.25            |

| Geerts [61]     | 1999 | $\mathbf{SC}$ | 24   | $0.5$ - $\mu m$  | 1.1   | 82   | 200   | 5.06            |

| Fujimori [62]   | 2000 | $\mathbf{SC}$ | 8    | $0.5$ - $\mu m$  | 1.25  | 87   | 105   | 24.8            |

| Geerts [63]     | 2000 | $\mathbf{SC}$ | 24   | $0.65$ - $\mu m$ | 1.25  | 89   | 295   | 5.3             |

| Vleugels [6]    | 2001 | $\mathbf{SC}$ | 16   | $0.5$ - $\mu m$  | 2     | 87   | 150   | 10              |

| Gupta [64]      | 2002 | $\mathbf{SC}$ | 29   | $0.18$ - $\mu m$ | 1.1   | 88   | 180   | 2.6             |

| Hamoui [65]     | 2003 | $\mathbf{SC}$ | 16   | $0.18$ - $\mu m$ | 1.5   | 71   | 59    | 4.2             |

| Park [66]       | 2003 | $\mathbf{SC}$ | 8    | $0.35$ - $\mu m$ | 2.5   | 88   | 495   | 12.25           |

| Jiang [10]      | 2004 | $\mathbf{SC}$ | 8    | $0.18$ - $\mu m$ | 2     | 82   | 159   | 2.9             |

| Balmelli [4]    | 2004 | $\mathbf{SC}$ | 8    | 0.18-µm          | 12.5  | 72   | 200   | 0.95            |

| Bosi [57]       | 2005 | $\mathbf{SC}$ | 4    | 0.18-µm          | 10    | 73   | 240   | 4               |

| Koh [67]        | 2005 | $\mathbf{SC}$ | 20   | 90-nm            | 1.94  | 63   | 1.2   | 0.2             |

| Jiang [68]      | 2005 | $\mathbf{SC}$ | 20   | 90-nm            | 1     | 61   | 2.1   | 0.4             |

| Nam [34]        | 2005 | $\mathbf{SC}$ | 16   | $0.25$ - $\mu m$ | 1.25  | 89   | 87    | 8.6             |

| Paramesh [69]   | 2006 | $\mathbf{SC}$ | 8    | 90-nm            | 20.48 | 63   | 73    | 1.3             |

| Lee [71]        | 2006 | $\mathbf{SC}$ | 60   | $0.18$ - $\mu m$ | 1.1   | 76   | 5.4   | 1.1             |

| Kwon [70]       | 2006 | $\mathbf{SC}$ | 33   | $0.18$ - $\mu m$ | 2.2   | 78   | 13.8  | 2.32            |

| Cao [72]        | 2007 | $\mathbf{SC}$ | 50   | $0.25$ - $\mu m$ | 1.25  | 75   | 14    | 0.27            |

| Kanazawa [73]   | 2006 | $\mathbf{SC}$ | 12.5 | $0.18$ - $\mu m$ | 4     | 77.3 | 27.54 | 1.57            |

| Fujimoto [74]   | 2006 | $\mathbf{SC}$ | 12   | 0.18-µm          | 3.2   | 76.3 | 23.76 | 1.7             |

| This work       | 2008 | $\mathbf{SC}$ | 8    | 0.18-µm          | 12.5  | 75.1 | 89    | 0.8             |

| Christen [75]   | 2007 | $\mathbf{SC}$ | 12   | $0.13$ - $\mu m$ | 10    | 63   | 20.5  | 0.4             |

| C. Lee [76]     | 2008 | $\mathbf{SC}$ | 23.8 | $0.18$ - $\mu m$ | 4.2   | 79   | 28    | 3.67            |

| Malla [3]       | 2008 | $\mathbf{SC}$ | 10.5 | 90-nm            | 20    | 70   | 28    | 1               |

| Chang [77]      | 2007 | $\mathbf{SC}$ | 16   | $0.25$ - $\mu m$ | 2.2   | 78.5 | 62.5  | 1.4             |

Table 1.1: IEEE-published  $\Delta\Sigma$  modulators

Figure 1.3: A 4-b ADC put in a feedback configuration together with a loop-filter and 4-b DAC can achieve >4-b resolution if oversampled.

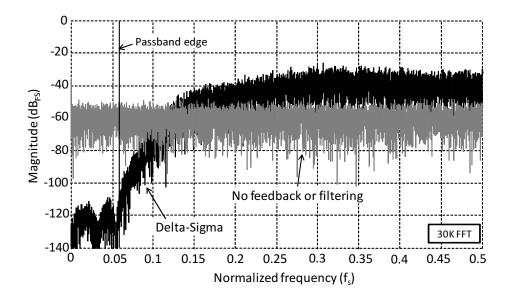

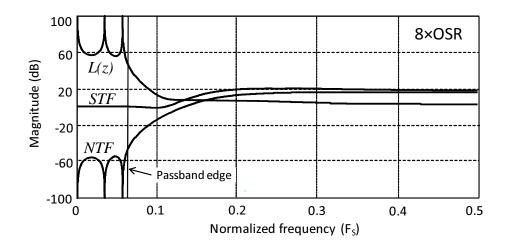

filtering to "shape" the quantization noise of the 4-b ADC to push it outside the band-of-interest. Figure 1.4 shows the concept of noise-shaping at work. The lighter color spectrum is the standalone 4-b ADC output with no feedback and zero input. The flat response across the entire Nyquist band suggests that no noise-shaping is present. Now assuming the user is only interested in a small range of input frequencies from dc to  $\frac{F_s}{2} \div 8 = \frac{F_s}{16}$ , then negative feedback and filtering can be applied to the 4-b ADC such that the quantization noise from dc to  $\frac{F_s}{16}$  is "pushed" to higher frequencies, as exemplified by the darker color spectrum in Figure 1.4. In this example, because the highest frequency of interest is  $\frac{F_s}{2} \div 8$ , the OSR equals 8. To complete the analog-to-digital conversion process, the noise beyond  $\frac{F_s}{16}$  is filtered out with a sharp digital filter and decimated to reduce the sampling-rate to twice the Nyquist frequency, i.e.  $\frac{F_s}{8}$ .

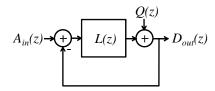

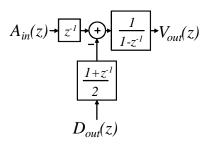

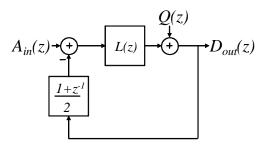

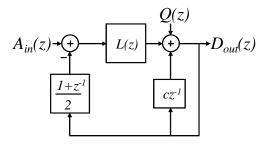

To model the noise-shaping phenomenon, a linearized model of the  $\Delta\Sigma$  modulator is needed. Figure 1.5 shows how the 4-b ADC can be modeled as a quantization noise source, Q(z), that sums with the output of the loop-filter. The 4-b DAC is assumed perfectly linear in the feedback path and can be done so because different DAC linearization algorithms exists to partially or completely remove the DAC's nonlinearity in a  $\Delta\Sigma$  modulator. Chapter 6 studies the Data Weighted Averaging (DWA) algorithm [22] used in this work.

Using superposition, it is possible to separate the output,  $D_{out}(z)$ , into its respective signal  $(A_{in}(z))$  and quantization noise (Q(z)) components. Setting Q(z)

Figure 1.4: Noise-shaping can push quantization noise out-of-band. Shows how a 4-b ADC can achieve 15-b performance (87.5-dB SQNR) through feedback, filtering, and oversampling. As shown, the OSR is  $8\times$ .

Figure 1.5: Assuming the DAC does not introduce any errors, the modulator's quantization error is solely due to the ADC and is modeled by Q(z).

to zero, the contribution of  $V_{in}(z)$  at  $D_{out}(z)$  can be found:

$$STF = \left. \frac{D_{out}(z)}{A_{in}(z)} \right|_{Q(z)=0} = \frac{L(z)}{1+L(z)}.$$

(1.2)

This result is termed the signal transfer function (STF) and tends to unity if  $|L(z)| \gg$ 1. Since the STF describes the conversion process from the analog domain to the digital domain, a unity gain response across the passband is desirable. Now setting  $A_{in}(z)$  to zero, the contribution of Q(z) at  $D_{out}(z)$  can be found, which equals

$$NTF = \left. \frac{D_{out}(z)}{Q(z)} \right|_{A_{in}(z)=0} = \frac{1}{1+L(z)}.$$

(1.3)

This result is termed the noise transfer function (NTF) and tends to zero if  $|L(z)| \gg$ 1. Again, this is a desirable result because the goal is to suppress quantization noise, Q(z), at the output. By giving L(z) a large magnitude response within the bandof-interest, quantization noise is suppressed while the input signal is faithfully converted to the digital domain. The aggregate output that combines the contributions of  $A_{in}(z)$  and Q(z) equals to

$$D_{out}(z) = A_{in}(z) \cdot STF + Q(z) \cdot NTF.$$

(1.4)

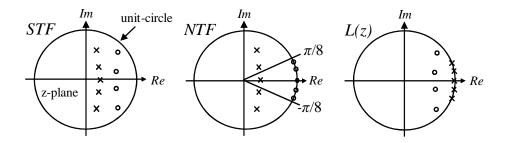

To gain a better understanding of the relationship between L(z), NTF and STF, a set of pole-zero plots that generated the noise-shaping response in Figure 1.4 is shown in Figure 1.6. Poles of L(z), due to feedback, become zeros of the NTF. STF and NTF share the same set of poles, and is a distinct characteristic of feedforward  $\Delta\Sigma$  modulators. Figure 1.7 plots the magnitude response of L(z), NTF and STF. It is easy to see that L(z) and NTF mirror each other in the modulator's passband because poles of L(z) are zeros of NTF as mentioned earlier. The zeros of NTF are spread across the passband to achieve better quantization noise suppression. Spreading these zeros is not always an option and depends on the loop-filter's

Figure 1.6: Pole-zero plots of the STF, NTF, and L(z) of a feedforward  $\Delta\Sigma$  modulator. STF and NTF share the same set of poles. Poles of L(z) mirror and become the zeros of the NTF.

topology. In some topologies, NTF zeros must be located at dc, and subsequently their SQNR will be worse for a given set of pole locations.

Also worth noting is the coupling between STF and NTF beyond the passband. In a feedforward  $\Delta\Sigma$  modulator, higher out-of-band NTF gain results in higher out-of-band STF gain. This phenomena is seen as a drawback because excessive out-of-band STF gain increases the modulator's sensitivity towards highfrequency inputs. In a communication system where adjacent or nearby channels cannot be attenuated sufficiently, the modulator can saturate and become unstable. There exists, however, a tradeoff that justifies higher out-of-band STF gain, and that is, by increasing the NTF's out-of-band gain, passband quantization noise can be reduced. A term often used to describe the aggressiveness of the noise-shape is quantization noise gain. It is a vaguely defined term that conveys how much out-ofband gain is in the NTF's frequency response. Usually, the more quantization noise gain a modulator can handle, the higher the SQNR. However, higher quantization noise gain threatens stability because accumulated quantization noise in the modulator can take up precious dynamic range, which in turn can saturate the quantizer and drive the modulator unstable [21, 10]. From here on, quantization noise gain is defined to be the magnitude of the NTF at  $\frac{F_s}{2}$ .

Figure 1.7: Frequency response of the STF, NTF, and L(z) of a feedforward  $\Delta\Sigma$  modulator. Peaks in L(z) mirror to become zeros in the NTF.

### 1.4 Feedforward vs. feedback $\Delta\Sigma$ modulators

DT  $\Delta\Sigma$  modulators can be separated into two main categories, feedforward and feedback, as shown in Figure 1.8 and Figure 1.9, respectively. In a feedforward modulator, outputs of all integrators are fed forward and summed at the input of the quantizer. Only one global negative feedback path exists, which goes from the output of the modulator back to the input of the 1<sup>st</sup> integrator. In a feedback modulator, there are no feedforward paths to the quantizer (except for the last integrator), but multiple feedback paths exist that go from the output of the modulator back to the input of each integrator. From a complexity standpoint, it can be argued that both are similarly complex because on one hand, the feedforward modulator requires an extra summing node, but on the other hand, the feedback modulator is multiple feedback DACs. From the perspective of relaxing the modulator's out-of-band signal sensitivity, the feedback modulator wins because its STF usually exhibit a low-pass characteristic, which act to prevent out-of-band input signals from saturating the modulator. This is possible because its STF and NTF do not

Figure 1.8: A feedforward  $\Delta \Sigma$  modulator.

Figure 1.9: A feedback  $\Delta\Sigma$  modulator.

share the same set of poles [20]. From the perspective of performance at low OSRs, however, the feedforward modulator has an advantage. Balmelli showed that the input-referred error and noise contributions beyond the  $1^{st}$  integrator depends on the gain coefficient,  $k_1$ , of the  $1^{st}$  integrator, and the OSR [4]. Errors and noise beyond the  $1^{st}$  integrator are suppressed when

$$k_1 > \frac{\pi}{OSR}.\tag{1.5}$$

As the OSR is reduced, it becomes more difficult to satisfy (1.5) for both feedforward and feedback modulators. However, because the values of the coefficients,  $k_1$  to  $k_n$ , usually appear in descending order for feedforward modulators and ascending order for feedback, the feedforward modulator has a better chance at reducing the effects of errors and noise beyond the 1<sup>st</sup> integrator. It is for this reason, that a feedforward topology is chosen for this research work.

### 1.5 Discrete-time vs. continuous-time $\Delta\Sigma$ modulators

In recent years, a significant number of publications have appeared in the literature regarding advances in CT  $\Delta\Sigma$  modulators [55, 54, 56, 14, 15, 16]. These modulators are attractive to the designer for two main reasons. First, they provide inherent anti-alias filtering with its continuous-time loop-filter at no additional cost in power or silicon area. Second, the internal sampling-rate of CT modulators can be several times higher than DT modulators implemented in the same process because its integrators are not required to settle at the end of every cycle. As long as a CT integrator does not slew and its phase-shift induced excess loop-delay is under a certain limit, its speed requirements are met. Two of the best CT  $\Delta\Sigma$  modulators reported to date operate at an impressive 640-MS/s [1, 2], which is very fast compared to the 200-MS/s prototype of this work. However, there are at least four reasons for choosing a DT implementation over CT, and the rest of this section explains what they are.

First, in terms of clock jitter sensitivity, the DT modulator has an edge because its sensitivity is proportional to the input signal frequency rather than the sampling-frequency. In an 8× OSR 1-b 90-dB SNR-targeted design, the jitter sensitivity of a DT modulator is roughly an order of magnitude less sensitive than a CT modulator [4]. However, it must be noted that a multi-bit non-return-to-zero (NRZ) feedback DAC in a CT modulator can significantly relax jitter sensitivity. Nonetheless, the CT modulator with 12-b ENOB and 20-MHz of bandwidth reported by Mitteregger [1], features a 4-b NRZ feedback DAC, but due to its still-critical jitter specification, a dedicated 300-fs RMS jitter phase-locked loop (PLL) was invested to accompany the modulator. As a comparison, the RMS jitter specification for the prototype herein is 3.2-ps (an order of magnitude less sensitive) for an ENOB of 12.2-b in a 12.5-MHz band (comparable performance).

Second, in terms of manufacturability and robustness, the DT modulator

has an edge because its filter coefficients can be defined precisely with excellent predictability. Coefficients of a DT modulator are defined by capacitor ratios, which can be matched to roughly 0.1% (3- $\sigma$ ) accuracy in modern CMOS processes. The absolute value of the capacitors are unimportant as it does not alter the ratio between them. With such initial coefficient accuracy, it is possible for a DT modulator to implement an NTF with a higher Q-factor than a CT modulator, yet suffer less performance variability due to manufacturing process variations. Loop-filter coefficients of CT modulators, at least for the case of active-RC  $\Delta\Sigma$  modulators, are dependent upon the absolute values of resistors and capacitors. In modern CMOS processes, the absolute value of resistors can vary by as much as  $\pm 75\%$  depending on the type of resistor element used. If salicide-blocked polysilicon resistors are available, the tolerance level can improve to roughly  $\pm 25\%$ . Nonetheless, calibration is still necessary to tune the CT modulator's coefficients to within a  $\pm 10\%$  range for stable operation [14]. Additional circuitry needed to calibrate the CT modulator also increases the complexity of the converter.

Third, in terms of flexibility, the DT modulator wins because it can be clocked at virtually any rate below the maximum sampling-frequency. In communication systems, this can be beneficial if the channel bandwidth varies over time and the converter is able to dynamically adjust its sampling-rate to reduce power consumption. This is possible with DT modulators because poles and zeros of the NTF automatically scale with the clock frequency. However, CT modulators do not enjoy this flexibility because their filter coefficients are determined by time-constants rather than capacitor ratios. Changing the clock frequency of a CT modulator without properly adjusting the time constants can destabilize the modulator.

Fourth, in a DT modulator, sampling of critical signals can be time-isolated such that the sampling instant occurs during a window where other circuits are quiet [17]. For large system-on-chip (SoC) designs fabricated on heavily-doped epitaxial wafers, noise can couple from distant locations regardless of physical separation or guard rings [47]. In these situations, time-isolation may be the answer. However, signals in a CT modulator are continuous by nature, so time-isolation is not an option.

In addition to the four reasons stated above, DT modulators can be *double-sampled* to gain, ideally, a factor-of-two increase in bandwidth without increasing power consumption, assuming a 50% duty cycle [5, 6]. Equally so, double-sampling a modulator can ideally halve its power consumption while maintaining the same signal bandwidth. However, double-sampling brings with it sensitivities that do not exist for single-sampled  $\Delta\Sigma$  modulators. Chapter 4 studies the non-idealities that must be overcome in order to fully take advantage of the speed benefits offered by double-sampling.

## 1.6 Basic design methodology for DT feedforward $\Delta\Sigma$ modulators

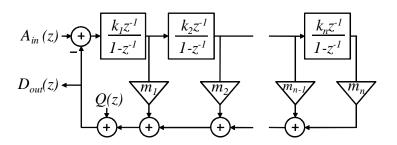

The design of a DT modulator usually begins by specifying a target NTF. A classical filter function such as inverse Chebyshev or an automated filter design algorithm such as CLANS [21, 9] can be used to design the NTF. Once it is obtained, the coefficients in the denominator of the NTF are used to solve for the coefficients in L(z). As shown in Figure 1.8, the feedforward modulator has 2n coefficients,  $k_1$  to  $k_n$  and  $m_1$  to  $m_n$ . The denominator of the NTF, on the other hand, has only n coefficients  $(a_{1-n})$  for an  $n^{th}$ -order modulator. To reduce the number of coefficients in L(z) to n,  $k_{1-n}$  or  $m_{1-n}$  can be set to unity. As an example,  $k_{1-n}$  is set to unity and the equation is used to solved for  $m_{1-n}$  with respect to the target NTF, which may be in the following form:

$$NTF_{target} = \frac{(1-z^{-1})^n}{1+a_1 z^{-1} + a_2 z^{-2} + \ldots + a_n z^{-n}} .$$

(1.6)

Here, the target NTF that has all n NTF zeros located at dc because the feedforward modulator in Figure 1.8 does not allow zeros to be located elsewhere. Chapter 2 looks at topologies that can move the zeros away from dc for better passband quantization noise suppression. The closed-loop NTF of the feedforward modulator in Figure 1.8 can be shown to be equal to

$$NTF = \left. \frac{D_{out}(z)}{Q(z)} \right|_{A_{in}(z)=0} = \frac{(1-z^{-1})^n}{(1-z^{-1})^n + \sum_{i=1}^n z^{-1} \cdot (1-z^{-1})^{(n-i)} \cdot m_i}.$$

(1.7)

Equating the coefficients in the denominator of (1.6) to the coefficients in the denominator of (1.7) for the same powers of  $z^{-1}$ , permits solving for  $m_{1-n}$  (*n* equations and *n* unknowns). Thereafter, the gains  $m_{1-n}$  can be redistributed throughout the modulator so that the signal-swing at each integrator's output stays within practical limits for circuit implementation [18]. Finally, to ease layout and to improve the predictability of capacitor ratios, all coefficients are quantized into rational numbers. Slight changes in the NTF pole locations are expected after quantization, but if done properly, the changes should affect the NTF minimally. A step-by-step example of matching an NTF to a modulator topology is available in Chapter 3.

# Chapter 2

# Existing $\Delta \Sigma$ Loop-Filter Topologies

## 2.1 Conventional feedforward topologies

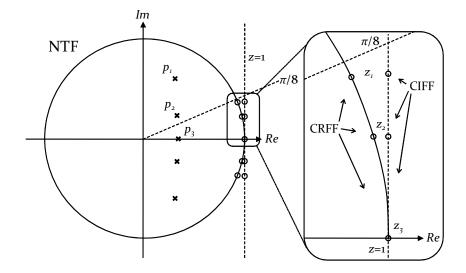

The previous chapter looked at the differences between feedforward and feedback modulators. In particular, it explained why the feedforward modulator has a better chance at achieving high-performance in a low OSR design than the feedback modulator. In this section, two conventional feedforward topologies are studied that enable the implementation of NTFs with zeros spread across the passband. Both modulators are similar to the feedforward modulator in Figure 1.8, but they utilize local feedback to move the NTF zeros away from dc. The first topology is the cascade-of-integrators-feedforward form (CIFF) which offers extra speed, but confines zeros to the vertical line that intersects z=1 in the z-plane. The second topology is the cascade-of-resonators-feedforward form (CRFF) which is slower than CIFF but allows zeros to be pinned to the unit-circle for maximum quantization noise suppression. Both topologies have their merits and will be studied here.

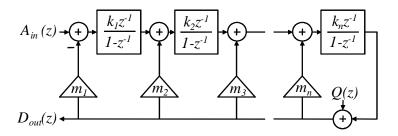

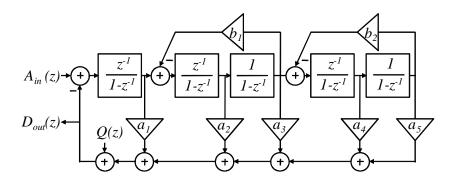

Figure 2.1:  $5^{th}$ -order cascade-of-integrators feedforward form (CIFF).

#### 2.1.1 CIFF

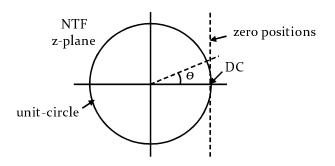

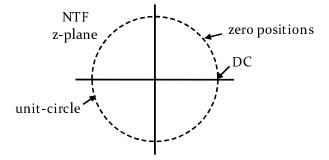

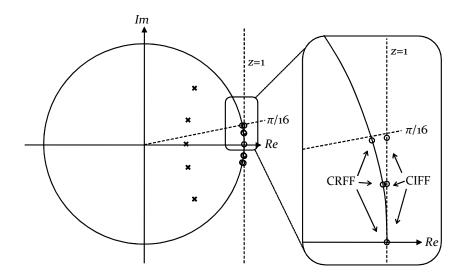

Shown in Figure 2.1 is a 5<sup>th</sup>-order CIFF  $\Delta\Sigma$  modulator. It consists of five delaying  $(z^{-1})$  integrators with two local feedback loops. Since all integrators are delaying, this topology offers the highest speed because the signal does not need to propagate through two or more amplifiers before it is sampled as is the case for CRFF (discussed shortly). Between the basic feedforward modulator shown earlier in Figure 1.8 and CIFF, the only difference is the addition of local feedback. This topology allows NTF zeros to be spread across the passband for enhanced quantization noise suppression similar to the example shown in Figure 1.6. By introducing local feedback around every two consecutive integrators, the zeros originally at dc will migrate to higher frequencies in the z-plane as complex conjugate pairs. The location of the loop-filter. For CIFF, the zeros are restricted to the vertical line that intersects z=1 as depicted in Figure 2.2. The feedback coefficient  $b_i$  controls the movement of its associated complex conjugate pair along this vertical line. Each feedback coefficient is responsible for exactly one complex conjugate pair.

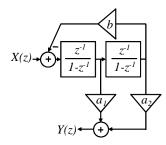

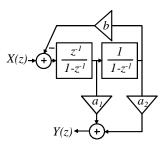

Now consider how the NTF zeros move with respect to  $b_i$ . One feedback loop of the modulator is isolated as shown in Figure 2.3. The transfer function  $\frac{Y(z)}{X(z)}$

Figure 2.2: Possible NTF zero positions in the z-plane for a CIFF  $\Delta\Sigma$  modulator.

Figure 2.3: Local feedback loop of CIFF.

can be found and is equal to

$$\frac{Y(z)}{X(z)} = \frac{a_1 z^{-1} + (a_2 - a_1) z^{-2}}{1 + 2z^{-1} + (1 + b) z^{-2}} .$$

(2.1)

Since poles of the loop-filter become zeros of the NTF for feedforward modulators (Chapter 1), the poles of  $\frac{Y(z)}{X(z)}$  will be the zeros of the NTF. Using the quadratic formula, the pole locations of  $\frac{Y(z)}{X(z)}$  (zeros of the NTF) can be determined as a function of b:

$$z = 1 + j\sqrt{b} \tag{2.2}$$

These NTF zeros are confined to the vertical line z=1, and because of this, the zeros are not as effective in pinning down the NTF as they would be if they were on the unit-circle. To see why, recall that the magnitude response for a system with a given set of pole-zero locations can be determined by the dividing the multiplication of

the distance to all zeros by the multiplication of the distance to all poles:

$$|H(z)| = \frac{\prod distance \ to \ zeros}{\prod distance \ to \ poles} \ .$$

(2.3)

If the zeros are not on the unit-circle, the numerator in (2.3) never becomes zero, therefore the zeros are not as effective. To make matters worse, as the frequency of the zeros on the vertical z=1 line increases, they move further away from the unitcircle, and the notch becomes shallower. This will be studied in detail later in this chapter. The angle  $\theta$  in Figure 2.2 determines the frequency of the zero-pair. To a good degree, and especially when  $\theta \ll 1$ , the frequency can be approximated with the following equation:

$$\theta \approx \sqrt{b}$$

. (2.4)

Later in this section, the effectiveness the zeros of CIFF for different OSRs are examined. When trying to match an NTF equation to a CIFF modulator, the feedback coefficients  $b_i$  should be assigned first, then the denominator of the NTF of  $n^{th}$  power can be used to solve for the remaining n coefficients  $(a_i)$  of the modulator.

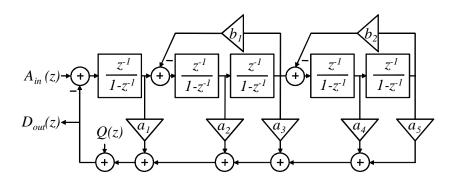

#### 2.1.2 CRFF

Shown in Figure 2.4 is a 5<sup>th</sup>-order CRFF  $\Delta\Sigma$  modulator. It is essentially the same as the CIFF modulator except two of the five delaying integrators are replaced by non-delaying integrators. These non-delaying integrators do not sample the input but rely on the previous stage to sample the signal. By cascading one non-delaying integrator with one delaying integrator, the signal is forced to propagate through two integrators in one clock period. This configuration limits speed and is the main drawback of CRFF. On the positive side, because of the non-delaying integrator, the delay around each local feedback loop is reduced to one cycle from two. This

Figure 2.4: 5<sup>th</sup>-order cascade-of-resonators feedforward form (CRFF).

Figure 2.5: Possible NTF zero positions in the z-plane for a CRFF  $\Delta\Sigma$  modulator.

speedup around the loop causes the NTF zeros to move around the unit-circle as opposed to moving along the vertical z=1 line as shown in Figure 2.5. Again, the zeros move in complex conjugate pairs, and each pair is controlled by exactly one feedback coefficient  $b_i$  similar to CIFF.

To study how the NTF zeros move with respect to  $b_i$ , one feedback loop is isolated as shown in Figure 2.6. Its transfer function  $\frac{Y(z)}{X(z)}$  can be found and is equal to

$$\frac{Y(z)}{X(z)} = \frac{(a_1 + a_2)z^{-1} - a_1 z^{-2}}{1 + z^{-1}(b - 2) + z^{-2}} .$$

(2.5)

Since the poles of the loop-filter become the zeros of the NTF for feedforward modulators, the poles of  $\frac{Y(z)}{X(z)}$  are expected to be the zeros of NTF. Using the quadratic

Figure 2.6: Local feedback loop of CRFF.

formula, the pole locations of  $\frac{Y(z)}{X(z)}$  (zeros of the NTF) can be determined as a function of b:

$$z = 1 - \frac{b}{2} \pm \frac{\sqrt{b^2 - 4b}}{2} \tag{2.6}$$

If  $0 \le b \le 4$ , the term under the square root is negative, and the pole locations can be rewritten as

$$z = 1 - \frac{b}{2} \pm j \frac{\sqrt{4b - b^2}}{2} \text{ for } 0 \le b \le 4.$$

(2.7)

These poles are on unit-circle and their angle (frequency) can be calculated using one of the following relationships:

$$\sin\theta = \frac{\sqrt{4b - b^2}}{2} \tag{2.8}$$

$$\cos\theta = 1 - \frac{b}{2} \tag{2.9}$$

The notch of this zero-pair is very deep because the zeros are on the unit-circle. Furthermore, as frequency increases, the effectiveness of the zero-pair remains the same as it will continue to move along the unit-circle. This is the main advantage CRFF has over CIFF. However, due to the speed limitation imposed by non-delaying integrators, most designers still opt for CIFF instead.

#### 2.1.3 CIFF vs. CRFF for different OSRs

The previous two subsections looked at the differences between CIFF and CRFF. In particular, the NTF zeros of CIFF are restricted to the vertical line that intersects z=1 while the zeros of CRFF are always positioned around the unit-circle. The zeros of CIFF are less effective than the zeros of CRFF because their ability to pin down quantization noise diminish as the zeros move towards higher frequencies (lower OSRs). However, CIFF offers speed as it uses only delaying integrators. Here, the NTFs of CIFF and CRFF are compared at  $8\times$  and  $16\times$  OSR to study the impact of the zeros on the NTF.

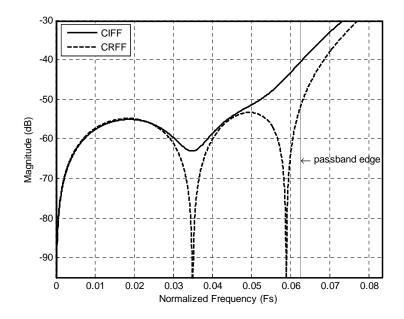

Shown in Figure 2.7 are two overlaid NTFs of a CIFF modulator and a CRFF modulator at  $16 \times$  OSR. Both NTFs are designed with 4-b quantization. Only the passband is shown because the zeros of the NTF is the primary interest here. Both NTFs share the same set of poles and both have a quantization noise gain of 4. The pole locations are designed using the Delta-Sigma Toolbox [9]. The NTFs are given here:

$$NTF_{CIFF(16\times)} = (2.10)$$

$$\frac{(1-z^{-1})(1-2z^{-1}+1.013z^{-2})(1-2z^{-1}+1.035z^{-2})}{(1-0.4299z^{-1})(1-0.8894z^{-1}+0.2523z^{-2})(1-1.0207z^{-1}+0.5637z^{-2})}$$

$$NTF_{CRFF(16\times)} = (2.11)$$

$$\frac{(1-z^{-1})(1-1.987z^{-1}+z^{-2})(1-1.965z^{-1}+z^{-2})}{(1-0.4299z^{-1})(1-0.8894z^{-1}+0.2523z^{-2})(1-1.0207z^{-1}+0.5637z^{-2})}$$

|       | CIFF   | CRFF   |

|-------|--------|--------|

| $b_1$ | 0.013  | 0.013  |

| $b_2$ | 0.035  | 0.035  |

| $a_1$ | 2.6600 | 2.6120 |

| $a_2$ | 3.1370 | 1.6731 |

| $a_3$ | 1.9673 | 1.3380 |

| $a_4$ | 0.6332 | 0.4590 |

| $a_5$ | 0.0423 | 0.0643 |

Table 2.1:  $16 \times \text{OSR}$  coefficients

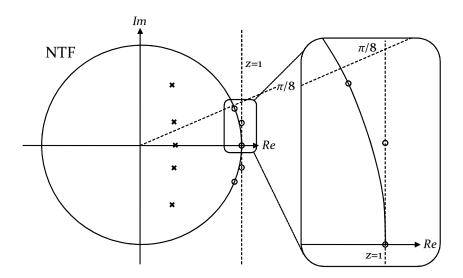

A pole-zero plot of these NTFs is shown in Figure 2.8, with the passband zeros magnified to highlight the differences between CIFF and CRFF. Comparing the frequency response plot with the pole-zero plot, it is easy to see the effect of the zeros on the NTF. For CRFF, the zeros are on the unit-circle which translate into deep notches in the frequency response. These notches hold down quantization noise so higher SQNR can be achieved. On the other hand, the zeros of CIFF are not on the unit-circle so the notches are shallower. This is clearly visible by comparing the notch of CIFF with the notch of CRFF in the middle of the passband. Moving up in frequency to the edge of the passband, the CIFF zero-pair has deviated so far from the unit-circle that the intended notch now appears as a momentary plateau that only serves to slow down the rise of the NTF. Nonetheless, discrete-time simulation suggests only a 1-dB difference in SQNR between CIFF (112-dB) and CRFF (113dB). Mostly likely than not, this mere 1-dB difference justifies choosing CIFF over CRFF for its speed advantage. Listed in Table 2.1 are the coefficients of the CIFF and CRFF modulators discussed here. As a side note, since the main purpose of this analysis is to study the effect of zero-placement on the NTF, no effort was made to gain-scale [18] or quantize the coefficients.

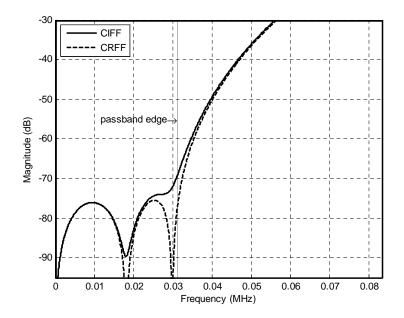

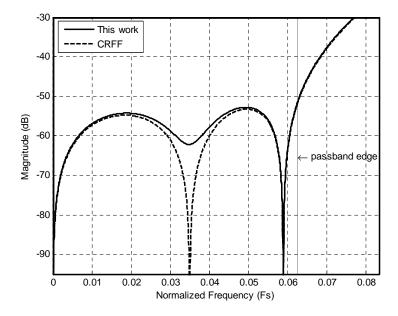

Now consider CIFF and CRFF at  $8 \times$  OSR. Shown in Figure 2.9 and Figure

Figure 2.7: Frequency response of CIFF and CRFF at  $16 \times$  OSR.

Figure 2.8: Pole-zero plot of CIFF and CRFF at  $16\times$  OSR.

2.10 are the frequency response plots and pole-zero plots of the NTFs of CIFF and CRFF, respectively. Again, both NTFs share the same set of poles and have a quantization noise gain 6. Since the OSR is now halved, the passband bandwidth doubles. The NTF of CRFF appears well defined with three deep notches spread across the passband. The NTF of CIFF, on the other hand, has two notches that struggle to pin down the NTF. Most concerning is the intended notch at the edge of the passband where it is almost invisible and seems to have no effect on the NTF in the immediate vicinity of the notch. In discrete-time simulation, a difference of 6-dB in SQNR is observed between CRFF (87.5-dB) and CIFF (81.5-dB), with 4-b quantization assumed. This 6-dB deficit is significantly worse than the 1-dB deficit at  $16 \times OSR$ , and especially because the peak SQNR here is only 87.5-dB as compared to 113-dB in the  $16 \times$  case. In other words, the percentage loss in SQNR is much greater here. The coefficients used to generate the plots are summarized in Table 2.2, and the NTFs are listed here:

$$NTF_{CIFF(8\times)} = (2.12)$$

$$\frac{(1-z^{-1})(1-2z^{-1}+1.05z^{-2})(1-2z^{-1}+1.125z^{-2})}{(1-0.3466z^{-1})(1-0.6659z^{-1}+0.1626z^{-2})(1-0.6238z^{-1}+0.451z^{-2})}$$

$$NTF_{CRFF(8\times)} = (2.13)$$

$$\frac{(1-z^{-1})(1-1.952z^{-1}+z^{-2})(1-1.865z^{-1}+z^{-2})}{(1-0.3466z^{-1})(1-0.6659z^{-1}+0.1626z^{-2})(1-0.6238z^{-1}+0.451z^{-2})}$$

In practice, designers usually set a margin between the target SNR of the modulator and the SQNR so that quantization noise is at least close to being negligi-

Figure 2.9: Frequency response of CIFF and CRFF at  $8 \times$  OSR.

ble if not completely negligible in the final noise budget. Here, with only 81.5-dB of SQNR, even a 10-dB margin will put the target SNR at 71.5-dB, which is below 12-b ENOB performance. Therefore, even though CIFF offers speed, it may not qualify as a viable topology in certain low OSR applications due to its low SQNR. The following section looks at Balmelli's modulator, which can alleviate this drawback of CIFF while using strictly delaying integrators.

Figure 2.10: Pole-zero plot of CIFF and CRFF at  $8\times$  OSR.

| Table 2.2. 8× OSK coefficients |         |         |          |  |  |  |

|--------------------------------|---------|---------|----------|--|--|--|

|                                | CIFF    | CRFF    | Balmelli |  |  |  |

| $b_1$                          | 0.05    | 0.048   | 0.05     |  |  |  |

| $b_2$                          | 0.125   | 0.135   | 0.13475  |  |  |  |

| $a_1$                          | 3.3637  | 3.1807  | 3.2290   |  |  |  |

| $a_2$                          | 4.7558  | 2.2061  | 4.3109   |  |  |  |

| $a_3$                          | 3.2632  | 1.9531  | 2.6676   |  |  |  |

| $a_4$                          | 0.9779  | 0.7373  | 0.6097   |  |  |  |

| $a_5$                          | -0.1605 | -0.0158 | -0.1128  |  |  |  |

|                                |         |         |          |  |  |  |

Table 2.2:  $8 \times$  OSR coefficients

## **2.2** Low OSR feedforward $\Delta \Sigma$ modulators

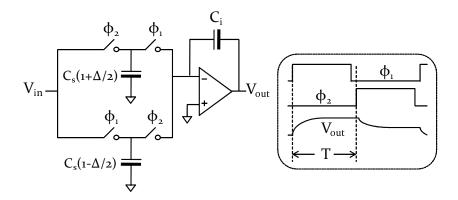

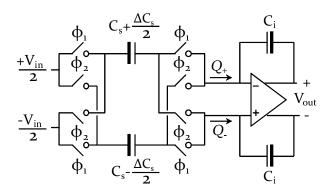

This section looks at two modulator topologies in the literature that are suitable for low OSR operation. Both can provide excellent attenuation of quantization noise within the passband at low OSRs, and neither resort to non-delaying integrators. The first is Balmelli's modulator [4], which is similar to CIFF in terms of speed, but has the ability to pin one pair of complex conjugate zeros to the unit-circle. The second is Jiang's modulator [10], which can pin two pairs of quantization noise zeros to the unit-circle, but has the drawback of heavier output loads and lower feedback factors.

#### **2.2.1** Balmelli's $\Delta \Sigma$ modulator