Copyright

by

Ku He

2012

# The Dissertation Committee for Ku He Certifies that this is the approved version of the following dissertation:

# Adaptive Low-Energy Techniques in Memory and Digital Signal Processing Design

| Committee:                        |

|-----------------------------------|

|                                   |

| Michael Orshansky, Co-Supervisor  |

| Andreas Gerstlauer, Co-Supervisor |

|                                   |

| Adnan Aziz                        |

| Constantine Caramanis             |

| Constantine Caramanis             |

| Rouwaida Kanj                     |

|                                   |

## Adaptive Low-Energy Techniques in Memory and Digital Signal Processing Design

by

Ku He, B.E., M.E.

### **Dissertation**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

**Doctor of Philosophy**

The University of Texas at Austin

May 2012

### **Dedication**

To my family

### Acknowledgements

First, I would like to thank my research advisors: Prof. Michael Orshansky and Prof. Andreas Gerstlauer, for their guidance and support during my time in graduate school at the University of Texas at Austin.

Secondly, I would like to thank the committee members of the Chinese Student and Scholar Association (CSSA) at the University of Texas, as well as the members of Austin Tsinghua Alumni Association (ATAA). We have worked together to hold many successful events.

Thirdly, I would like to thank my friends in Austin, and also my college classmates in the US. Your support helped me to overcome many difficulties during my research in the last five years.

Finally, I am grateful to my family for their love and steady support. I am proud of all of them: my parents Hualin He and Fuyu Liu, sister Xiangyu He, brother-in-law Shuanglin Liu, niece Muen Liu, uncle Huaxin He, aunt Di Yang, cousins Le He and Qian He.

Adaptive Low-Energy Techniques in Memory and Digital Signal

**Processing Design**

Ku He, Ph.D.

The University of Texas at Austin, 2012

Co-Supervisors: Andreas Gerstlauer and Michael Orshansky

As semiconductor technology continues to scale, energy-efficiency and power

consumption have become the dominant design limitations, especially, for embedded and

portable systems. Conventional worst-case design is highly inefficient from an energy

perspective. In this dissertation, we propose techniques for adaptivity at the architecture

and circuit levels in order to remove some of these inefficiencies. Specifically, this

dissertation focuses on research contributions in two areas: 1) the development of SRAM

models and circuitry to enable an intra-array voltage island approach for dealing with

large random process variation; and 2) the development of low-energy digital signal

processing (DSP) techniques based on controlled timing error acceptance.

In the presence of increased process variation, which characterizes nanometer

scale CMOS technology, traditional design strategies result in designs that are overly

conservative in terms of area, power consumption, and design effort. Memory arrays,

such as SRAM-based cache, are especially vulnerable to process variation, where the

penalty is a power and bit-cell increase needed to satisfy a variety of noise margins. To

improve yield and reduce power consumption in large SRAM arrays, we propose an

intra-array voltage island technique and develop circuits that allow for a cost-effective

deployment of this technique to reduce the impact of process variation. The voltage

vi

tuning architecture makes it possible to obtain, on average, power consumption reduction of 24% iso-area in the active mode, and the leakage power reduction up to 52%, and, on average, of 44% iso-area in the sleep mode. Alternatively, bitcell area can be reduced up to 50% iso-power compared to the existing design strategy.

In many portable and embedded systems, signal processing (SP) applications are dominant energy consumers. In this dissertation we investigate the potential of errorpermissive design strategies to reduce energy consumption in such SP applications. Conventional design strategies are aimed at guaranteeing timing correctness for the input data that triggers the worst-case delay, even if such data occurs infrequently. We notice that an intrinsic notion of quality floor characterizes SP applications. This provides the opportunity to significantly reduce energy consumption in exchange for a limited signal quality reduction by strategically accepting small and infrequent timing errors. We propose both design-time and run-time techniques to carefully control the quality-energy tradeoff under scaled V<sub>DD</sub>. The basic philosophy is to prevent signal quality from severe degradation, on average, by using data statistics. We introduce techniques for: 1) static and dynamic adjustment of datapath bitwidths, 2) design-time and run-time reordering of computations, 3) protection of important algorithm steps, and 4) exploiting the specific patterns of errors for low-cost post-processing to minimize signal quality degradation. We demonstrate the effectiveness of the proposed techniques on a 2D-IDCT/DCT design, as well as several digital filters for audio and image processing applications. The designs were synthesized using a 45nm standard cell library with energy and delay evaluated using NanoSim and VCS. Experiments show that the introduced techniques enable 40~70% energy savings while only adding less than 6% area overhead when applied to image processing and filtering applications.

### **Table of Contents**

| List of Tables                                                | ix  |

|---------------------------------------------------------------|-----|

| List of Figures                                               | X   |

| Chapter 1: Introduction                                       | 1   |

| 1.1 Adaptivity in SRAM                                        | 1   |

| 1.2 Adaptiviy in Image Processing System                      | 6   |

| 1.3 Adaptivity in Digital Filter                              | 12  |

| Chapter 2: Low-power techniques in SRAM                       | 15  |

| 2.1 Adaptive Framework in SRAM                                | 15  |

| 2. 2. Experiment                                              | 20  |

| 2.3 Summary                                                   | 31  |

| Chapter 3: Timing Error Acceptance in Image Processing        | 32  |

| 3.1 Error Control through Knowledge of Operand Statistics     | 32  |

| 3.2 Error Control by Dynamic Reordering of Accumulations      | 40  |

| 3.3 Preventing Error Spread and Amplification                 | 42  |

| 3.4 Reducing Residual Image Artifacts through Post-processing | 45  |

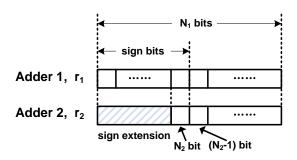

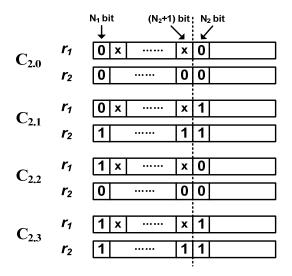

| 3.6 Timing Errors in Big Adder and Small Adders               | 73  |

| 3.7 Summary                                                   | 76  |

| Chapter 4: Digital filtering                                  | 77  |

| 4.1 Error Control through Operand Statistics                  | 77  |

| 4.2 Error Control through Reordering                          | 87  |

| 4.3 Experiment                                                | 90  |

| 4. 4 Summary                                                  | 99  |

| Chapter 5: Conclusion                                         | 100 |

| Bibliography/References                                       | 102 |

| Vita                                                          | 107 |

### **List of Tables**

| Table 2.1: On-chip voltage scheme area overhead estimation. | . 24 |

|-------------------------------------------------------------|------|

| Table 3.1: Energy Saving and Area of IDCT.                  | . 58 |

| Table 3.2: Energy under different combinations.             | . 58 |

| Table 3.3: Area/energy of IDCT with post processing.        | . 71 |

| Table 4.1: Energy and area overhead.                        | . 92 |

| Table 4.2: Energy savings and performance                   | . 92 |

# **List of Figures**

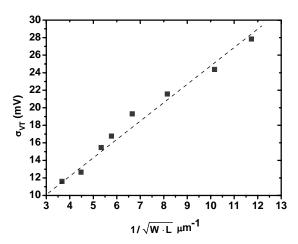

| Figure 1.1: Dependence of threshold voltage standard deviation on transistor area.2    |

|----------------------------------------------------------------------------------------|

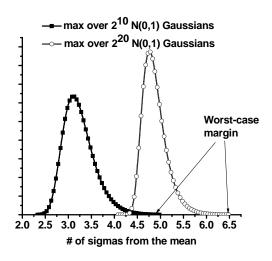

| Figure 1.2: The design specification increases due to long tail of Gumbel distribution |

| for high number of cells                                                               |

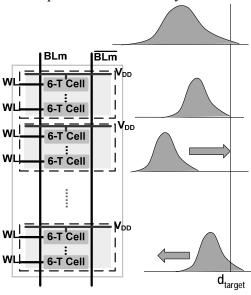

| Figure 2.1: Adjustment of a partition's $V_{DD}$ shifts access times of all cells in a |

| partition to fix violations or save power                                              |

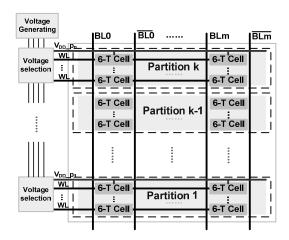

| Figure 2.2: SRAM architecture using row-based multiple voltage control 17              |

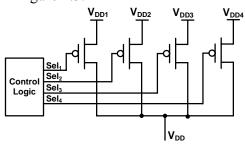

| Figure 2.3: PMOS switch network for a partition selects one of available voltages.18   |

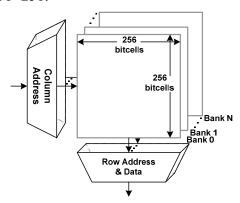

| Figure 2.4: SRAM bank architecture                                                     |

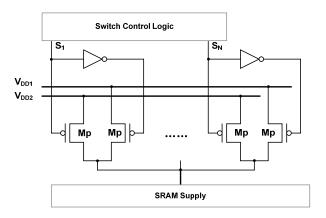

| Figure 2.5: SRAM voltage delivery architecture                                         |

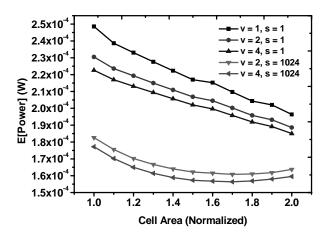

| Figure 2.6: Expected power vs. bitcell area Pareto curves for different voltage and    |

| switch complexities in active mode. 28                                                 |

| Figure 2.7: Expected leakage vs. bitcell area Pareto curves for different voltage and  |

| switch complexities in sleep mode. 29                                                  |

| Figure 2.8: Monte Carlo simulation for SNM in active mode                              |

| Figure 2.9: Monte Carlo simulation for SNM in sleep mode                               |

| Figure 2.10: Monte Carlo simulation for RCM                                            |

| Figure 2.11:. Monte Carlo simulation for WRM in active mode                            |

| Figure 3.1: Frequency distribution of IDCT coefficients for sample image 33            |

| Figure 3.2: Partitioning of input matrix. 33                                           |

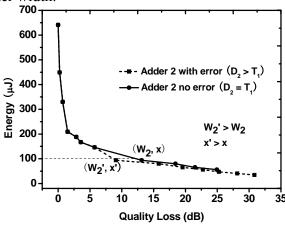

| Figure 3.3: Quality-energy tradeoffs in Adder 1 and Adder 2                            |

| Figure 3.4: Energy vs. quality loss Pareto front - comparison                          |

| Figure 3.5: DCT coefficient partitioning                                               |

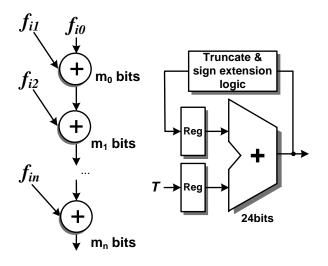

| Figure 3.6: Reduced width adder                                                        |

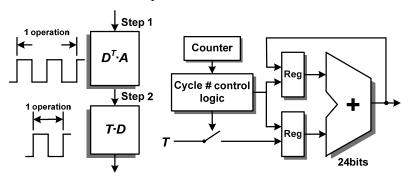

| Figure 3.7: A | Accumulation reordering architecture.                             | 42     |

|---------------|-------------------------------------------------------------------|--------|

| Figure 3.8: F | Rescheduling of algorithm steps.                                  | 44     |

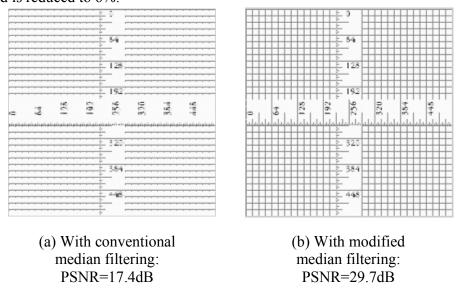

| Figure 3.9: I | mages with/without median filtering.                              | 47     |

| Figure 3.10:  | Modified median filtering algorithm, window length 3              | 48     |

| Figure 3.11:  | Bitmap for all components.                                        | 50     |

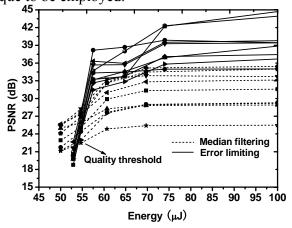

| Figure 3.12:  | Comparison between median filtering and error limiting            | 53     |

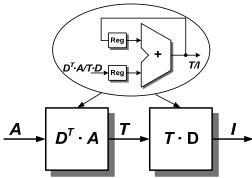

| Figure 3.13:  | 2D-IDCT design architecture.                                      | 54     |

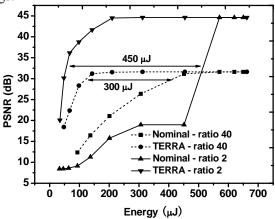

| Figure 3.14:  | Q-E tradeoff under different compression ratios                   | 56     |

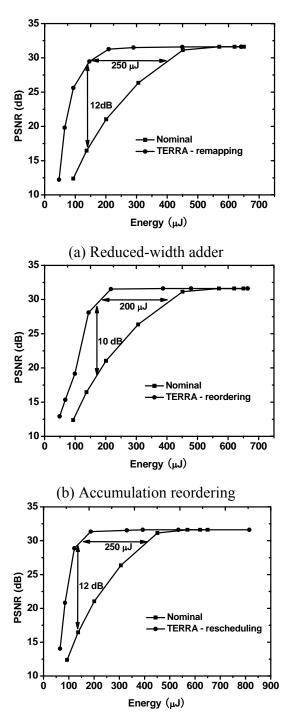

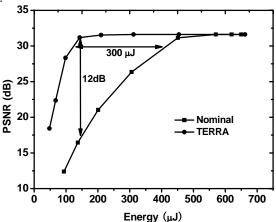

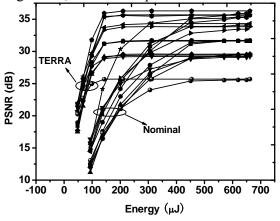

| Figure 3.15:  | Individual PSNR vs. energy profiles.                              | 57     |

| Figure 3.16:  | Combined PSNR vs. energy profile.                                 | 59     |

| Figure 3.17:  | Q-E curve for various images with/without our techniques          | 60     |

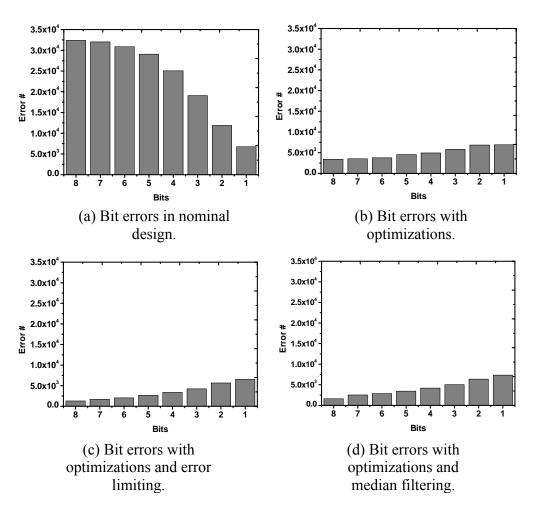

| Figure 3.18:  | Frequency of errors in individual bit positions.                  | 61     |

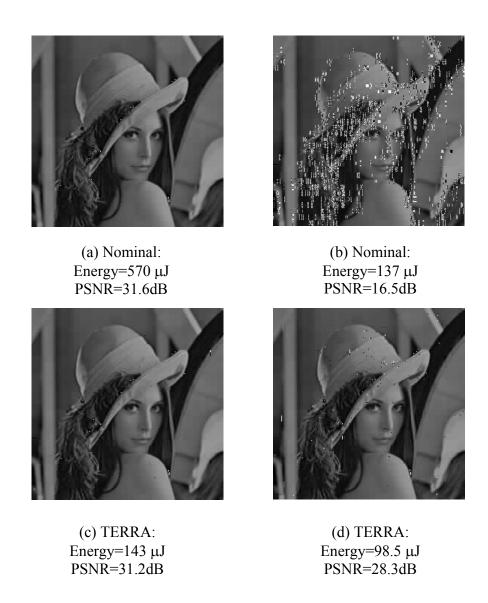

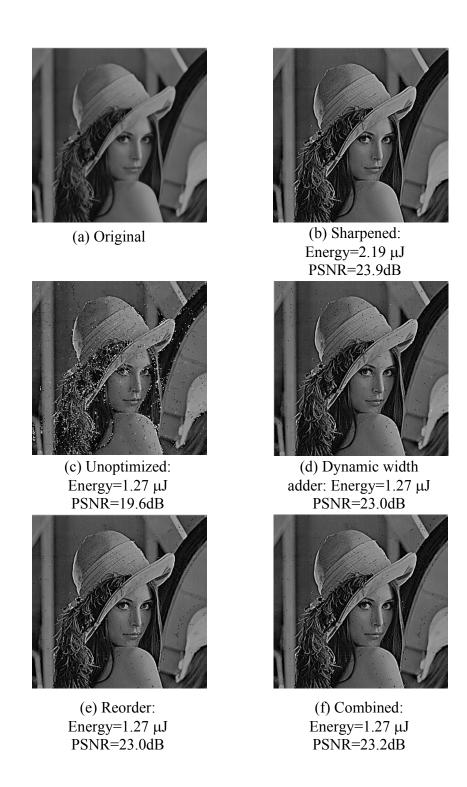

| Figure 3.19:  | Image quality under different energy budgets                      | 62     |

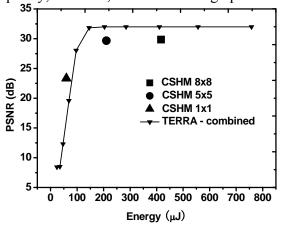

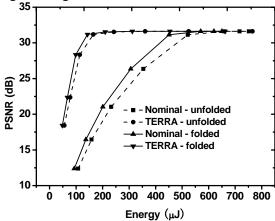

| Figure 3.20:  | Approximate 2D-DCT design: comparison of this work and CSHM       | [.63   |

| Figure 3.21:  | An unfolded IDCT design.                                          | 64     |

| Figure 3.22:  | An IDCT design using sign-magnitude representation.               | 65     |

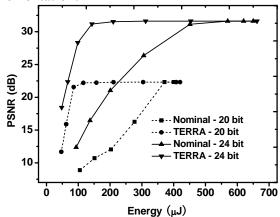

| Figure 3.23:  | An IDCT design using 20 bits vs. 24 bits.                         | 66     |

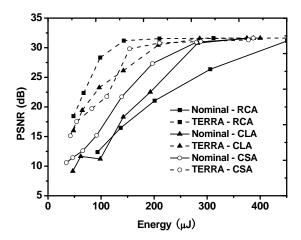

| Figure 3.24:  | Q-E tradeoff using various adder architectures.                   | 66     |

| Figure 3.25:  | Reduced-width CLA adder.                                          | 67     |

| Figure 3.26:  | QE tradeoff for balanced/unbalanced design.                       | 68     |

| Figure 3.27:  | PSNR curve for filtered and unfiltered image.                     | 71     |

| Figure 3.28:  | MS-SSIM curve for filtered and unfiltered image.                  | 71     |

| Figure 3.29:  | Image quality after post-processing.                              | 72     |

| Figure 3.30.  | Comparison between median filtering and error limiting using quan | ıtizec |

|               | data                                                              | 73     |

| Figure 3.31: The bitmap for adder 1 and adder 2.                                    | . 75 |

|-------------------------------------------------------------------------------------|------|

| Figure 3.32: The four subcases for $C_2$ .                                          | . 75 |

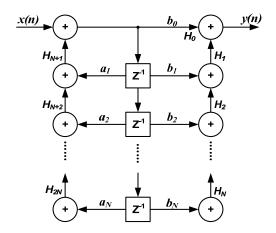

| Figure 4.1: Digtial filter in direct form II.                                       | . 78 |

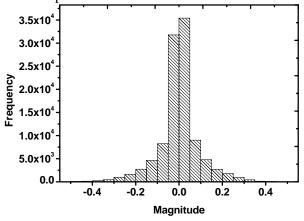

| Figure 4.2: Distribution of input data in an audio application.                     | . 79 |

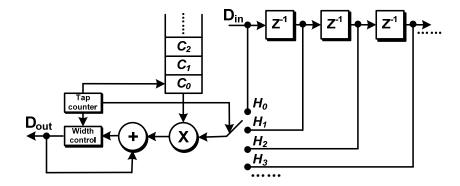

| Figure 4.3: Dynamic-width adder architecture.                                       | . 81 |

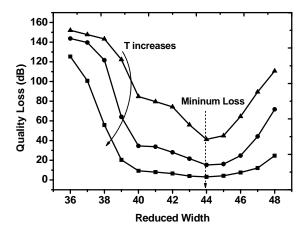

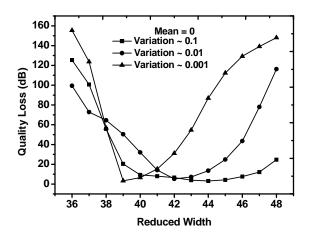

| Figure 4.4: Quality loss in two adders vs. Adder 2 bitwidth. Behavior for severa    | al   |

| values of timing budget is shown.                                                   | . 82 |

| Figure 4.5: Total quality loss as a function of Adder 2 bitwidth.                   | . 82 |

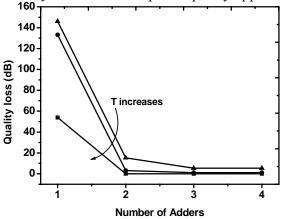

| Figure 4.6: Quality loss vs. adder number.                                          | . 83 |

| Figure 4.7: Dependence of optimal Adder 2 width on input data variance              | . 84 |

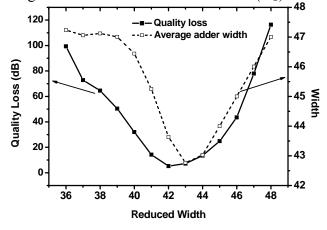

| Figure 4.8: Quality loss and average adder width                                    | . 84 |

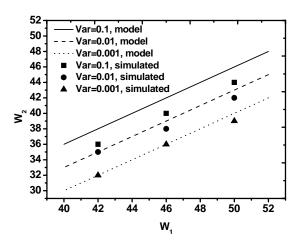

| Figure 4.9: Predicted $W_2$ and simulated $W_2$ under different $W_1$ .             | . 87 |

| Figure 4.10: Technique abstraction of arithmetic reordering.                        | . 90 |

| Figure 4.11: Single MAC filtering architecture.                                     | . 90 |

| Figure 4.12: Individual SSNR vs. energy profiles in FIR filters.                    | . 93 |

| Figure 4.13: FIR filters using reorder technique.                                   | . 94 |

| Figure 4.14: FIR filter for different input data with dynamic bitwidth optimization | ion. |

|                                                                                     | . 95 |

| Figure 4.15: Individual SSNR vs. energy profiles in IIR filters.                    | . 96 |

| Figure 4.16: Image quality under different energy budgets                           | . 98 |

### **Chapter 1: Introduction**

Energy efficiency is one of the paramount concerns in the design of embedded and portable system. Conventional worst-case design strategies are highly inefficient in terms of energy consumption. Hence, we propose adaptivity at both the architecture and circuit levels as a means to remove some of these inefficiencies. Specifically, this dissertation deals with two types of adaptivity: 1) adaptivity to process variations in SRAM design; 2) adaptivity to input data variations while giving up on timing correctness in DSP design.

In the following discussions, we will first review the background knowledge and the previous works of low energy techniques in SRAM and DSP. Details of our low-energy design techniques will be introduced in subsequent chapters.

#### 1.1 ADAPTIVITY IN SRAM

In nanometer technologies, the increase of process variation significantly impacts circuit yield. The impact of variability on the design of large SRAM arrays is especially severe. Some patterns of variability are highly systematic, such as those in photolithography and chemical-mechanical polishing. Among the random variability patterns, the threshold voltage variation due to random dopant placement is paramount. SRAM cells are typically sized to be of minimum area, because of the tight layout requirements for large arrays. Because the variance of threshold voltage variation is inversely proportional to the transistor area, the V<sub>th</sub> variance of small size transistors is large and is growing as reported in Figure 1.1 [1].

Figure 1.1: Dependence of threshold voltage standard deviation on transistor area.

SRAM cell design is driven by the need to satisfy static noise margin, write margin and read current margin over all cells in the array and these constraints determine both the minimum cell size and supply voltage. Increasing cell area and supply voltage can ensure that the noise margins are met. The requirement to meet noise margin constraints sets the limit on the smallest possible cell size and also on the minimum usable supply voltage  $V_{DD}$  for the array, commonly known as  $V_{min}$ . Because threshold voltage variation impacting the cells in the SRAM array is independent, the margin specification needs to be met at very high sigma corners, five or six sigma, in order to reach acceptable yield, requiring significant cell upsizing and increased  $V_{min}$ . SRAM cell area is an important metric of the success of technology scaling, and variability makes such traditional scaling hard to sustain. Thus, reducing the negative impact of random  $V_{th}$  variability on SRAM area is an important goal.

One effective strategy for dealing with variability is post-silicon adaptivity. Adaptive circuit-level solutions, such as adaptive supply voltage and adaptive body bias have been employed in order to increase frequency, reduce standby leakage, and reduce switching power in logic circuits. For example, the approach of [2] is based on applying

high  $V_{DD}$  and forward body bias for slow dies and low  $V_{DD}$  and reverse body bias for high power, thus shrinking the yield violation region. In techniques not directly addressing variability, multiple adaptive strategies for SRAM arrays have been explored to save leakage power or enhance cell stability. In [3], in order to achieve adequate SRAM cell stability, the authors use different  $V_{DD}$ s for read and write operation. In this case, assigning  $V_{DD}$  in a row-based manner is not suitable because there could be simultaneous read/write operations in the same row. In [4], the author uses dynamic voltage in a row-by-row manner and unaccessed rows are set to low  $V_{DD}$  to reduce leakage.

Earlier work has addressed the techniques for mitigating the impact of global dieto-die variation on the operation of SRAM arrays. In [5] adaptive body bias has been employed to increase SRAM yield. The high rate of read/hold failures at low V<sub>th</sub> corners has been reduced by employing reverse body bias and at high V<sub>th</sub> corners forward body bias has been used to reduce the write/access failures. In [6] the concept of column-based voltage assignment to reduce voltage overhead was described. However, the work has not developed the theoretical models that would be needed to guide adaptive design at specific levels of variability and for reduced bitcell area.

The key contribution of our work is that we propose a new architecture to reduce the overhead of high-sigma margin design on  $V_{DD}$  and cell area by employing an adaptive voltage scheme in a partitioned SRAM array. The key idea is to be able to shift empirical distributions (realizations) of the design margins in a partition to meet the target specification. Because the partition is smaller than the whole array, the tail of the Gumbel distribution is significantly reduced. For the partitions whose worst margin violates the specification, a higher voltage is selected to gain yield, otherwise voltage is reduced for power reduction.

Figure 1.2: The design specification increases due to long tail of Gumbel distribution for high number of cells

The central intuition we introduce is the possibility of smaller bit cell area design due to the use of adaptive techniques which enable reducing the pessimism in selection of design-time optimal solutions. Our basic argument is that accepting a larger single-cell spread, due to sizing-down the cell, and compensating it by post-silicon adjustment of the empirical realization of margins in the partition allows solutions that are area- and energy-superior to the traditional ones. In the sleep mode operation, the voltage of SRAM arrays is often reduced to a voltage level that guarantees that cell content will not be destroyed. Only SNM is relevant in the sleep mode. The key factor that determines the amount of power reduction in sleep mode is how low can the voltage, known as *data* retention voltage (DRV), be. The data retention voltage of an SRAM is determined by the worst-case tail of the DRV distribution of all the cells in the SRAM [7]. Under the normally distributed within-die threshold voltage variation, the  $6\sigma$  tail of the DRV distribution is almost 3X of the mean value. On the other hand, leakage power has exponential dependence on  $V_{DD}$ : a small amount of reduction of  $V_{DD}$  can lead to significant reduction of leakage power. Therefore, if we can reduce the mean value of

DRV of a SRAM in sleep mode using tuning, we can achieve significant leakage power saving.

Given the importance of minimum area design, the impact of post-silicon tuning must therefore be rigorously taken into account in order to size the cell optimally. This requires taking into account the underlying distribution of the process parameters in the device optimization to produce power-area Pareto analysis. We develop models to quantitatively predict the statistics of noise margins depending on the partitioning strategy. The ultimate objective of the model is to guide SRAM design for minimum area and minimum equivalent (mean) power superior to traditional design. The model predicts the benefits for the given cost. First, the models we derive include the realistic constraint that only a small finite number of voltage levels are available to be assigned to partitions. Second, the analysis is cognizant of the cost of the tuning architecture due to the need to assign different voltages to partitions depending on the realization. The cost includes the cost of generating additional voltage levels, creating extra routing, and control logic. Our solution for avoiding the prohibitive cost of continuous voltage adjustment is to provide a choice of several discrete but optimized voltage levels chosen at manufacture time. This drastically reduces the cost of adaptivity. While the cost of this adaptivity is quite low, even with only 2-4 voltage levels, as we demonstrate, our architecture allows a significant cell area reduction.

We use the framework of two-stage stochastic optimization for capturing the interaction between the design-time sizing and adaptivity. The analytical models for design margins are based on the extreme-value statistics. They allow to express yield as a function of supply voltage and size. We consider cases of continuously adaptable voltage and discrete adaptable voltage and express the yield as a function of tuning architecture parameters (partition size, range of continuous adaptable voltage or the values of discrete

adaptive voltages). In this dissertation, we provide a framework to handle multiple design margins taking into account the mutual correlation. Furthermore, we allow more general class of objective functions which allow minimization of power or a linear combination of mean and standard deviation of adaptive supply voltage. The method is based on application of stochastic dynamic programming [8] and exploits the recursive structure of the objective function.

### 1.2 ADAPTIVIY IN IMAGE PROCESSING SYSTEM

Nowadays, the gap between the limited battery life and the need to support more complex functionality of embedded systems is growing. Mitigating this gap requires continued advances in low energy design. To solve this problem, we propose to exploit error-tolerance of certain signal processing circuits to reduce their energy consumption. Our strategy focuses on circuit-level Timing ERRor Acceptance (TERRA) as a way to reduce energy. In a conventional design methodology, driven by static timing analysis, timing correctness of all operations is guaranteed by construction. The design methodology guarantees that every circuit path regardless of its likelihood of excitation must meet timing. Traditional design strategies do not consider the possibility of accepting timing errors. When V<sub>DD</sub> is scaled even slightly, large timing errors occur and rapidly degrade the output signal quality. This rapid quality loss under voltage scaling significantly reduces the potential for energy reduction. In this dissertation, we will show how the above quality-energy tradeoff can be dramatically improved. We achieve this by identifying the sources of early and, from the quality loss point-of-view, worst timing errors and modify the circuit such that the overall tradeoff between quality and energy is improved.

Several efforts in the past have explored the possibility of trading quality in DSP systems for lower energy. In [9, 10], energy is reduced by discarding algorithm steps or iterations that contribute less to the final quality. In [11], adaptive precision of the arithmetic unit output is used to save energy. In [12, 13], energy reduction is enabled by using lower voltage on a main computing block and employing a simpler error-correcting block that runs at a higher voltage and is thus, error-free, to improve the results impacted by timing errors of the main block. In [14], a low-power DCT core is implemented by identifying and skipping the unnecessary computations. In [15], power is reduced by applying aggressive voltage scaling to the memory of a multimedia system, and then filtering out the resulting memory faults. The most similar approach to ours is described in [16, 17, 18]. In this work, combinational logic blocks are restructured to enable utilization of intermediate results, which are arranged such that the more important ones, from the quality point of view, are obtained first.

An important distinction between prior work and our TERRA strategy is that in other work, the results produced by blocks subject to timing errors are not directly accepted. From the point of view of gate-level design, such techniques still guarantee timing correctness of all digital operations. In [12, 13], an estimated value of the result is used in downstream computation in case of timing errors. In [16, 17], computation is terminated early and intermediate results impacted by timing errors are ignored entirely. In contrast, our strategy allows using the erroneous results directly, providing, of course, that the magnitude of error is carefully controlled. As a result, we are able to achieve large energy savings in the low range of quality loss.

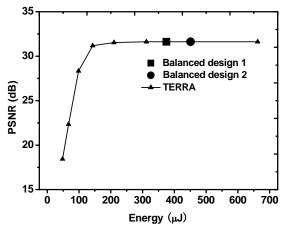

The available data from literature suggests that our design is effective. The energy savings achieved are higher than in earlier work: for example, the saving are 55% in [14], 40% in [16], and 62.8% in [18]. Because an exact comparison is difficult for designs in

different technologies, we implemented one of the prior designs (the CSHM-based DCT design described in [18]) and compared it with a DCT design based on our techniques. The results show that TERRA techniques can achieve substantially lower energy for an image quality of about 30dB.

We also anticipate that our strategy is extendable to a larger class of algorithms. Our approach does not require changing the algorithm itself, e.g. to allow for early termination. Instead, we directly re-design the implementation to tolerate timing errors. Another difference with [16, 17] is that their approach only allows a discrete set of quality-energy points. By contrast, our technique enables a range of trade-offs along a continuous quality-energy profile.

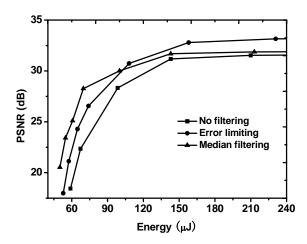

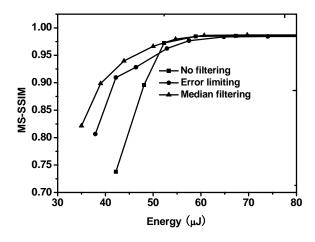

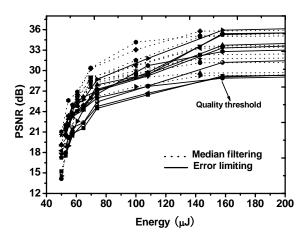

The proposed TERRA strategy is based on a statistical treatment of errors: while we give up on guaranteeing the worst-case timing, we have to satisfy timing requirements on average to keep global signal quality from severe degradation. Here we considerably extend earlier work by: (a) substantially extending formal analysis of the design choices that need to be made in implementing the timing-error accepting strategy, and (b) presenting novel post-processing techniques to improve the perceptive quality of the image produced by the error-accepting circuits. The new post-filtering techniques are motivated by our search for further ways to reduce the degradation of perceived image quality.

Experiments suggest that two images may have similar values of PSNR but be assessed as being of different quality by a human subject. It turns out that an image with fewer localized errors is more acceptable to human perception: the PSNR metric captures only the overall average signal quality, but does not capture well the local quality. MSB errors tend to cause significant local quality degradation. Thus, we have to ensure that if

timing errors occur, they are limited to the LSBs as much as possible. The introduced post-processing techniques aim to do that.

A widely used post-processing technique is filtering, such as a 2-D median filter. In [19], median filtering is used to remove noise. In this dissertation, we implement a simplified median filter that can quickly estimate the median of an array of pixels, such that the computational complexity is reduced and a low-energy design is achieved. Another existing approach for error reduction is to identify the erroneous results and then replace them with an approximated one [12]. We propose an image filter with error limiting that performs a partial substitution on the output pixel instead of replacing all of its bits. This significantly simplifies the error checking and correction logic. In contrast to previous work, our focus is on energy minimization under performance constraints instead of pure performance or throughput optimization [19].

We advance architecture-level techniques that significantly reduce algorithm quality loss under  $V_{DD}$  scaling, as compared to direct  $V_{DD}$  reduction. This leads to a superior quality-energy tradeoff profile. Fundamentally, this is enabled by (i) reducing the occurrence of early timing errors with large impact on quality, (ii) using control and data flow analysis to disallow errors that are spread and get amplified as they propagate through the algorithm, and (iii) applying post-processing techniques to reduce localized large magnitude errors that significantly degrade local image quality.

To address the first goal, we specifically focus on the behavior of timing errors in addition as a fundamental building block of most signal and image processing algorithms. Simple analysis shows that the magnitude of timing errors depends on the values of operands. A specific important class of operands leading to early and large-magnitude timing errors is the addition of small numbers with opposing signs. We develop two distinct techniques at two levels of granularity - one at the operation and one at the block

level - to reduce such errors. Note that depending on knowledge about data statistics, both techniques can be applied at design or at run time. For the design chosen in this dissertation, however, we limit discussions to static operation-level and dynamic block-level optimizations.

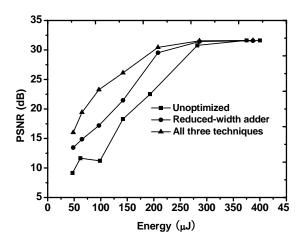

Targeting the first two goals, we present four quality-energy (Q-E) optimizations at the operation, block, algorithm and system levels. Techniques are introduced and demonstrated on the designs of an Inverse Discrete Cosine Transform (IDCT) and a Discrete Cosine Transform (DCT) as widely used image and video processing kernels. Specifically, the key contributions for architecture Q-E profile shaping are:

- 1) Controlling large-magnitude timing errors in operations by exploiting the knowledge of statistics of operands. In many cases, we have knowledge of data distributions that can be exploited at design or at run time. Specifically, in the IDCT/DCT algorithm, high-frequency coefficients tend to have small magnitude values, often of opposite sign. And such components tend to cause early and large quality loss (See Figure 3.3 (c) and Figure 3.19). Our technique is based on the realization that an adder with reduced bitwidth can be used to process such operands. Two objectives are achieved by using such adders: the magnitude of quality loss is reduced and its onset is delayed. In the IDCT/DCT algorithm, the classification can be done at design time, with higher-frequency components being processed in reduced-width adders while the rest of the matrix components are processed on the regular-width adder.

- 2) Controlling the frequency of error-generating additions by dynamically rearranging the sequence of operations, e.g. in accumulation. Similar to the previous technique, this strategy aims at reducing the quality loss in addition stemming from processing of small-valued opposite-sign numbers, but at a level higher than that for a single addition. Specifically, it is targeted at reducing the cumulative quality loss

resulting from multiple additions. Such multi-operand addition occurs, for example, in accumulation, which is a key component of many DSP algorithms, and, specifically, of IDCT/DCT.

- 3) Preventing occurrence of errors which can spread and get amplified throughout the algorithm. An important aspect of a design methodology that allows some timing errors is controlling the impact of these errors on output quality from the perspective of the entire algorithm. Specifically, a result impacted by timing errors early in the algorithm can have a dramatic impact on the overall quality by affecting downstream computations through repeated reuse of incorrect data. Therefore, we can not afford to allow errors in certain critical steps, and we propose a technique to avoid such errors based on rescheduling of the algorithm.

- 4) Post-processing to mitigate the effects of errors that do occur and to assist the aforementioned Q-E optimizations. In the pixel domain, timing errors appear as discontinuous outliers and MSB errors that significantly degrade *perceived* image quality. Such errors can be effectively detected and mitigated via median filtering or error limiting. A straightforward implementation of median filtering requires several full-bitwidth comparators, resulting in large energy and area overhead. Instead, we propose a low-cost scheme which computes an approximation of the median by using only two MSBs to perform the comparisons which reduces the overhead. Alternatively, in the 2D-IDCT algorithm, the average pixel value can be computed accurately even under scaled V<sub>DD</sub> just from the DC component. Furthermore, in order for a block of pixels to have MSBs that are different from the average, it has to either have large AC coefficients or an average which is closed to 2<sup>N</sup>, N here is any integer greater than 0. Hence, we can compute an error-free average and maximal range for each pixel. For each input block, we check the AC and DC components to determine the maximum possible difference

between pixel and average. If there are pixels for which the actual difference is smaller, we set their MSBs to their average value in order to limit possible errors in pixel MSBs.

### 1.3 ADAPTIVITY IN DIGITAL FILTER

Digital filter is another important DSP application which is heavily used in multimedia tasks such as speech, image, and video processing. Such tasks are often responsible for much of energy consumption on portable electronic devices. Extending battery time requires continued innovation in low-power methods for such multimedia applications. To enable a low-power digital filter design, we propose techniques based on timing error tolerance to significantly reduce energy consumption in digital filter circuits, which are an important building block of many such applications.

Because of their importance, much work has been done in the area of low-power implementation of digital filtering circuits over the previous decades. In general, finite-impulse response (FIR) filters tend to be more power-consuming than infinite-impulse response (IIR) ones [20]. A very incomplete list of approaches to reduce power consumption in FIR filters at the architectural level includes techniques such as multirate filtering, subfilter approaches and multiplierless architectures [20]. At the circuit level, optimal selections of filter bitwidth and realizations of adders and multipliers to reduce power consumption have been done either in a static [21] or dynamic [22] fashion. Furthermore, optimally choosing filter parameters for given target metrics such as gain, phase linearity, bandwidth, pass-band ripple or stop-band attenuation for low power has also been investigated [23].

It is widely recognized that voltage scaling is one of the most effective ways to reduce power consumption of any digital system. In [24, 11], this is exploited by implementing the filter using fastest possible filter structures and then using generated

timing slack to reduce power via voltage scaling. In the traditional paradigm of  $V_{DD}$  scaling, scaling is limited by the worst-case delay through any combinational logic. In other words, a conventional methodology guarantees timing correctness of all operations by construction. In this dissertation, we describe techniques that allow pushing  $V_{DD}$  scaling beyond this point and achieving further energy savings. In traditional approaches, scaling of  $V_{DD}$  beyond the point of worst-case delays immediately leads to large timing errors and rapidly degrades the output signal quality. This rapid quality drop eliminates the possibility of an efficient tradeoff between quality and energy. In this dissertation, we show how to achieve a graceful degradation of filter quality under scaled  $V_{DD}$ . We achieve this by identifying the sources of early and worst timing errors and designing filtering architecture to eliminate such errors.

In developing this approach we work in the wider framework of error-tolerant low-power design. In previous publications, techniques for trading quality for energy in digital filtering and digital signal processing (DSP) applications have been studied at varying levels of abstraction. In [10], the authors propose a technique that dynamically minimizes the order of a digital filter to reduce the switched capacitance and hence the total energy. In [25], the authors restructure the filter computations such that voltage scaling affects less important filter taps first.

Finally, in [26], energy is saved by using lower voltage on the main computing block and running a simplified estimating block at higher voltages to correct timing errors in the main block.

The common feature of prior work is that results produced by blocks subject to timing errors are not directly accepted. By contrast, our strategy allows using the erroneous results, provided, of course, that the frequency and magnitude of errors is carefully controlled. In this dissertation, we propose the concept of controlled timing

error acceptance for low energy DSP applications, and demonstrate a significantly improved quality-energy tradeoff for a 2D-IDCT block. And then we adapt and generalize this approach to develop an architecture and design strategy for low-power, timing error accepting digital filters with applications in a wide range of DSP systems.

We specifically propose two architecture-level techniques aimed at selectively accepting and controlling timing errors in the datapath of filters: 1) dynamic bitwidth adjustment to control the occurrence of large magnitude errors in small operand additions at run time, and (2) static filter tap reordering to control, at design time, the frequency of small valued operations leading to large errors. Fundamentally, both techniques are based on the observation that the largest and earliest timing errors stem from processing small inputs in the adder of the multiply-accumulate (MAC) units. By controlling the frequency and magnitude of such errors, we can allow for larger V<sub>DD</sub> scaling while maintaining a high output signal quality.

### **Chapter 2: Low-power techniques in SRAM**

#### 2.1 ADAPTIVE FRAMEWORK IN SRAM

The SRAM yield is set by the need to satisfy three noise margins: read current margin (RCM), write margin (WRM), and static noise margin (SNM). The SNM is defined as the minimum voltage noise required to flip the state of the cell. WRM is required to perform successful write in the period during which the word line is turned on. RCM is needed to ensure that there is enough time to build sufficient bit line voltage difference for the sense amplifier during the cell read. Thus, RCM can be captured as cell read delay time. For RCM, an upper limit will be imposed on the maximal cell read time over all cells. For the SNM and WRM, we have a lower bound on the minimal value of these margins over all cells. By negating SNM and WRM, we can assume without loss of generality that we have an upper bound on the maximal value of noise margins among all cells. The sizing of the SRAM cell transistors must be carefully adjusted in order to meet the conflicting requirements of the three margins. The total array yield is determined by the probability that the worst margin meets the target specification.

The satisfaction of noise margins is driven by the maximum of the cell margins in an array. Stochastically, the maximum over a large number of random variables follows extreme order statistics. For a typical SRAM consisting of a large number of cells, the worst case margins are asymptotically distributed according to a Gumbel distribution, which is characterized by long tails (Figure 1.2 in the introduction section). This requires that each cell's margins must be sufficiently high at high sigma corners in order to achieve the target yield.

Our adaptive framework for SRAM relies on partitioning the SRAM array into a set of *tunable blocks* which can be set to different supply voltages. Due to the smaller

number of cells in each block, the realization of the worst margin is significantly smaller (indeed, exponentially smaller [27]). As shown in Figure 2.1, because each partition contains only a sub-set of all cells in the array, there will be many partitions in which the worst realizations among the cells will still have margins which are less than the margin upper bound. Partition-based voltage assignment means that the entire set of realized bitcell margins in a partition is shifted. That ability allows us to accomplish one of two things: (1) for fixed cell area, we are able to reduce supply voltage in partitions whose worst realizations are below the relevant constraint, and thus reduce the average supply voltage; or (2) to reduce cell size which results in the larger spread in  $V_{th}$ , but which can now be tolerated because of the presence of tunability.

Figure 2.1: Adjustment of a partition's  $V_{DD}$  shifts access times of all cells in a partition to fix violations or save power

Figure 2.2: SRAM architecture using row-based multiple voltage control.

We now describe the SRAM architecture organization to implement our scheme. The array is partitioned in a row-by-row manner, as shown in Figure 2.2. The partitions are sets of rows that can be set at a distinct voltage. The supply voltage of all the bitcells in the partition and the corresponding wordlines can be set to one of the allowed voltage levels. The voltage levels between partitions can be different. The bitline voltages are fixed. There are two reasons why we choose the row-by-row partitioning strategy for the array: (1) If partitioning is done in a column-by-column way, the voltage for each partition is determined by the slowest cell in the column, but since SRAM is accessed in a row-by-row manner, for most of the read/write operations, it would waste power; (2) we fix the bitline voltages, while if the voltage island is partitioned in a column-by-column manner, the bitcell supply voltage would be different between the wordline voltage and bitline voltage. That would make it hard to achieve high SNM and WRM.

In Figure 2.1, each partition contains only a sub-set of all cells in the array. There will be many partitions in which the worst realizations among the cells will still have margins which are less than the margin upper bound. Partition-based voltage assignment means that the entire set of realized bitcell margins in a partition is shifted. That ability

allows us to accomplish one of two things: (1) for fixed cell area, we are able to reduce supply voltage in partitions whose worst realizations are below the relevant constraint, and thus reduce the average supply voltage; or (2) to reduce cell size which results in the larger spread in Vth, but which can now be tolerated because of the presence of tunability.

The voltages are generated by the on-chip voltage regulators. The area and power overhead associated with generation of additional voltage levels is estimated and is reported in Chapter 2.2. A PMOS switch network is used to carry the selected voltage to each partition, as shown in Figure 2.3.

Figure 2.3: PMOS switch network for a partition selects one of available voltages.

After the SRAM is manufactured, the RCM (or read time), SNM and WRM of each partition are measured. Based on the worst-case partition margins, a voltage is selected for that particular partition. The measurement of the RCM and WRM has been addressed in the work in [28], and the measurement of SNM has been addressed in [29].

We now develop an optimization framework for optimally designing, and understanding the impact of, a small number of distinct supply voltage levels that can be adjusted in independently tunable blocks of cells. As discussed in the previous chapter, the goal is to mitigate the impact of selecting parameters based on expected or realized worst-case randomness over a very large block of cells, as is required in order to satisfy

the margins described above. We show that allowing independent process parameters across a larger number but smaller blocks allows a more energy- and area-efficient design. Specifically, we want to study the reduction of area and power resulting from allowing different numbers of distinct, and optimized, voltage levels.

To choose the optimal cell size, voltage levels and partition numbers for the partitioned SRAM, we formalize the problem for SRAM operating in active mode as follows:

$$MIN_{W, VDD}$$

:  $P_{mean}(W, V_{DD})$  (1)

$s.t.: Yield \ge Yield_{target}$

We now describe the formulation, if we allow independent  $V_{DD}$  tuning for p tunable blocks of m cells each (so that  $p \cdot m = n$ ). At design time, a single value of supply  $V_{nominal}$  is set. Let the t size vector block\_margin^{nom}{}\_i denote the worst case margins of a tunable block i in the absence of adaptive voltage. The tunable voltage is used to adjust the untuned margins of block i. The voltage for block i is modified to  $V_{nominal} + \Delta V_{adapt,i}$  (block\_margin^{nom}{}\_i) in the post-silicon tuning phase. In this initial idealized treatment, the exact value of  $\Delta V_{adapt,i}$  is different for each block but its distribution can be quantitatively captured based upon our tuning policy which we describe later. The expected yield expression becomes:

$$Yield = Pr(min_{1 \le i \le p} block\_margin_i(W, V_{nominal} + \Delta V_{adapt, i}) \ge margin_{target})$$

The power minimization problem can be re-formulated as: ( $P_{mean}$  is the expected value of single cell mean power under  $V_{th}$  variability and below its expected value is taken over variability of  $\Delta V_{adapt}$ .)

$$MIN_{W,V_{adapt}}$$

:  $E[P_{mean}(W,V_{nominal} + \Delta V_{adapt})]$

$s.t.: Yield \ge Yield_{target}$

In the above,  $P_{mean}$  and Yield are monotonic increasing functions of tunable voltage. Thus in the adjustable post-silicon tuning, the tuning policy is determined by the worst-case margin vectors over each tuning block, and chosen to meet the margin target vector,  $margin_{target}$ . If the worst-case margins for a tunable block are above the margin target  $margin_{target}$  even for a single component among the t margins, then we increase  $V_{DD}$  until all the margin components are safely below  $margin_{target}$ . This allows us to meet yield constraints, although at the cost of a power penalty. If the worst-case margins are lower in all components with respect to  $margin_{target}$ , we can reduce  $V_{DD}$  as long as worst case margins continue to be lower than the margin targets in order to reduce power. After developing the above model, we need to set up experiments to extract necessary coefficients for the models and evaluate the effectiveness of our proposed framework.

#### 2. 2. EXPERIMENT

The following SRAM array organization, shown in Figure 2.4, is used for experimentation and for the extraction of power models. The array size is 1Mb and is divided into 16 banks. The word width of 32 bits is used, so that each access activates one row in a bank but only 32 out of 256 bitcells of the row are used. Each bitline has 256 bitcells. Sense amplifiers are used to recover the full-swing signals at the bitlines.

For the on-chip voltage distributing network, we note that in our earlier work [30] the models assumed an on-chip low-dropout voltage regulator to generate the voltage values because we focused on the array running only in the active mode, without the need to generate a lower voltage for the standby mode. Since we study both the active and sleep modes, the voltage may need to change by up to 70%, making low-dropout voltage regulator impossible. To resolve this problem and for the purpose of modeling and analysis, we assume that two off-chip voltage supply lines are available and the on-chip

voltage scheme generates all the intermediate voltages based on the two off-chip supplies. The on-chip voltage generating scheme utilizes the PMOS supply control network introduced in [31], as shown in Figure 2.5.

The advantages of using PMOS supply control scheme are: it does not require any on-chip passive components, resulting in a smaller area footprint; the output voltage values are digitally controlled, resulting in higher accuracy and can be easily interfaced with other digital logic; it directly uses the off-chip voltages, which is more stable because off-chip voltage regulator uses bigger capacitors and inductors to reduce power-line noise; it is passive and can support both active and sleep modes, while other types of on-chip voltage regulators would waste a lot of power in the sleep mode because it is almost impossible to bring down the voltage of the biasing circuits in these voltage regulator. The downside of the supply control is that it requires one extra external voltage, we assume this is acceptable in the SRAM design. Finally, we also note that we assumed a bank size of 256×256.

Figure 2.4: SRAM bank architecture

Figure 2.5: SRAM voltage delivery architecture.

Using the SRAM architecture and voltage generating circuits described above, we set up the models for evaluation of the design. We run experiments using the developed model to quantify the ability of the proposed scheme to reduce the impact of randomness on SRAM array. As mentioned before, the SRAM array needs to operate in active mode and sleep mode with V<sub>DD</sub> lowered to minimize leakage. In these two modes, the SRAM has different design margins to meet. In the active mode, the SRAM bitcells can be read, written or stay in hold. Hence, the SRAM design needs to satisfy the read margin, write margin, and static noise margin. In sleep mode, the supply voltage is lowered to a level above the voltage when the SRAM bitcells may flip, since the bitcells stay idle, only leakage power is consumed. The SRAM has only static noise margin to satisfy. We evaluate separately in these two modes the possible power and area reductions enabled by our tuning strategy.

The evaluation of the cost of tuning circuitry needs to be accounted for and here we provide the details of the additional circuitry to enable tunability. The sizes of the PMOS transistors in the switch network are determined by the maximum active current of the bitcell during the read and write operations plus the leakage current. The maximum current happens during the write operation because the bitcell may flip and draw current

from the power line. During a write operation, one word (32 bitcells) of a row is written, while the rest of the bitcells in the same row are being read. The maximum current from the on-chip voltage dividing network is drawn when the wordline driver is activated to drive one row and all the bitcells in that row flip. We characterize this current using HSPICE. In order to estimate the overhead of PMOS switch area, we relate it to the normalized width of the bitcell. The current across the PMOS linearly depends on the voltage and the width. Therefore, the size of the PMOS can be calculated as

$$W_P = I_{max} / (i_o \cdot V_{DD})$$

where  $i_o$  is the current conducted by the unit width PMOS transistor under a given  $V_{DD}$ . We also need to include the area and power cost of generating distinct voltages. The passsive voltage generating network needs only to supply the current for the bitcell and wordline, which is a relatively small current compared to the current consumed by precharge circuitry and row/column decoder: based on our simulation, when activity factor equals to 0.2, the precharge circuitry consumes about 79.2  $\mu$ W and the corresponding bitcells consume about 1.1  $\mu$ W power. Here the precharge circuitry power consists of the power used to charge/discharge the 256 bitlines in one bank. And the bitcells power consists of only the 32 bitcells' dyanmic power during read/write. Although the on-chip voltage distributing network does not provide power to the precharge circuitry, the tuning which happens on the on-chip voltage network can help reducing the precharge power. This is because the partition and tuning techniques reduce the average voltage on the SRAM cell (including the pass transistor) and the bitcell size, it leads to less discharge current and smaller load on the bitlines, and hence reduces the precharge power.

We model the overall area overhead as given by a function of the number of partitions (s), the number of distinct voltage levels (v), and the normalized bitcell width (w):

$$A_{O} = c_{0} \cdot s \cdot v \cdot w + c_{1} \cdot (v-1) \cdot w$$

where  $c_0$  is the area of the PMOS switch when w=1,  $c_1$  is the area of the voltage dividing network when w=1, and  $c_0=1.8$  and  $c_1=3.5$ . We assume that two of the voltages are generated externally. The estimated area overheads are shown in Table 2.1 for different partition complexities.

Table 2.1: On-chip voltage scheme area overhead estimation.

| Array size | S    | v | w | Area Overhead | Relative overhead(%) |

|------------|------|---|---|---------------|----------------------|

| 1Mb        | 1024 | 4 | 1 | 7393.8        | 0.7%                 |

| 1Mb        | 512  | 4 | 1 | 3707.4        | 0.4%                 |

| 1Mb        | 256  | 4 | 1 | 1864.2        | 0.2%                 |

In the active mode, we model the total power using the following formula:

$$P_{tot} = \alpha \cdot (0.5 \cdot P_{read} + 0.5 \cdot P_{write}) + (1 - \alpha) \cdot P_{leak}$$

where  $\alpha$  is the activity factor, 0.2 activity is used in the experiment.  $P_{read}$  is the read power, and as mentioned before, we assume that the SRAM array is divided into banks which have a size of 256×256, during read operation, only one row in a certain bank is being accessed, the rest of the banks consume only leakage power. Therefore, the read power consists of the bitline power which is consumed when charging and discharging the bitline, the power consumed when driving the wordline, the cell power of the bank being accessed, together with the leakage power of the rest of the banks:

$$P_{read} = P_{bitline} + P_{wordline} + P_{cell} + P_{l}$$

Similarly, for the write power  $P_{write}$ , it consists of the bitline power, wordline power, cell power, and active leakage power.

$$P_{write} = P_{bitline} + P_{wordline} + P_{cell} + P_{l}$$

The activity factor of 0.5 means that read and write operations take 50% of the time respectively.  $P_{leak}$  here is the leakage power in the active mode. In contrast to the leakage power in the sleep mode, active leakage power is consumed when  $V_{DD}$  is around 1V.

We now describe the experiments conducted using the aforementioned architecture and cost models. In this dissertation we use multiple constraints. The multiple constraints used are: the bitcell delay which defines the RCM, SNM, WRM in the active mode, and SNM in the sleep mode.

The closed-form expressions for above design margins, power and leakage models in the active mode and the sleep mode were fitted to SPICE simulations of a cell designed in the 32nm process using the PTM BSIM model. The mean fitting error of the models for all the design margins was below 3%. Besides the fitted model of each single margin, we also model the covariance between any two distinct margins to characterize the correlation between them.

The fitted models for each constraint, power and leakage are as follows:

$$\begin{split} E[P(W,V_{DD})] &= e_0 \cdot W + e_1 \cdot W \cdot V_{DD} + \sum_{i=2}^{5} e_i \cdot V_{DD}^{i} \\ &\frac{1}{E[D(W,V_{DD})]} = f_0 \cdot W + f_1 \cdot W^{-1} + f_2 \cdot V_{DD} + f_3 \cdot V_{DD} \cdot W \\ &\frac{1}{\sigma_D(W,V_{DD})} = g_0 \cdot W + g_1 \cdot W \cdot V_{DD} + g_2 \cdot W \cdot V_{DD}^{2} + g_3 \cdot V_{DD} + g_4 \cdot V_{DD}^{2} \\ E[SNM(W,VDD)] &= k_0 \cdot W^2 + k_1 \cdot V_{DD} \cdot W + k_2 \cdot V_{DD}^{2} \cdot W + \sum_{i=-2}^{3} k_i \cdot V_{DD}^{i} \\ &\sigma_{SNM}(W,V_{DD}) = l_0 \cdot W + l_1 \cdot V_{DD} + l_2 \cdot W \cdot V_{DD} \end{split}$$

$$\begin{split} E[WRM(W,VDD)] &= m_0 \cdot W^2 + m_1 \cdot V_{DD} \cdot W + m_2 \cdot V_{DD}^2 \cdot W + \sum_{i=-2}^{3} m_i \cdot V_{DD}^{i} \\ &\sigma_{WRM}(W,V_{DD}) = n_0 \cdot W + n_1 \cdot V_{DD} + n_2 \cdot W \cdot V_{DD} \\ E[leak(W,V_{DD})] &= EXP(y_0 \cdot W + y_1 \cdot V_{DD} + y_2 \cdot W \cdot V_{DD} + \sum_{i=3}^{4} y_i \cdot V_{DD}^{i}) \\ &\Sigma_{mutual}(W,V_{DD}) &= EXP(q_0 \cdot W + q_1 \cdot W^2 + q_2 \cdot W \cdot V_{DD} + \sum_{i=3}^{5} q_i \cdot V_{DD}^{i}) \end{split}$$

We use polynomial functions to model the power, delay and noise margins, and the coefficients of the functions are generated by least-square fitting. We first run HSPICE simulation to obtain power and margin data points at discrete sets of W,  $V_{DD}$ . Based on such, we run into a recursive procedure to determine the fitted model of power and noise margins in terms of W and  $V_{DD}$ . The strategy we use is to start from the model which consists of only 1st order terms: W and  $V_{DD}$ , and then we keep adding higher order terms to reduce the fitting error. Also, we remove terms whose coefficients are close to zero while adding new terms. Finally, the procedure terminates when the fitted error is less than 5%.

The delay and leakage power can not be modeled using polynomial function directly. Instead, we model the inverse of delay and the logarithmic of leakage to bound fitted errors under the 5% of the HSPICE simulation results.

The circuit setup for noise margins characterization is as follows: For the SNM, there are two cases: one is the read SNM, and the other is the hold SNM. To measure read SNM, the pass transistor is turned on and we use the method introduced in [29]. For other margins like WRM, and RCM, we measure the write delay and the read delay of the SRAM cells. All the measurements are performed in the form of Monte Carlo simulation. Finally we compute the mean, deviation, and the covariance of all noise margins.

Similarly, we build the fitted models in sleep mode, as follows:

$$\begin{split} E[leak(W,V_{DD})] &= EXP(a_0 \cdot W + a_1 \cdot V_{DD} + a_2 \cdot W \cdot V_{DD} + \sum_{i=3}^4 a_i \cdot V_{DD}{}^i) \\ E[SNM(W,VDD)] &= b_0 \cdot W + b_1 \cdot W^2 + b_2 \cdot V_{DD} \cdot W + b_3 \cdot V_{DD}{}^2 \cdot W + b_4 \cdot V_{DD} + b_5 \cdot V_{DD}^2 \\ \frac{1}{\sigma_{SNM}(W,V_{DD})} &= c_0 \cdot W + c_1 \cdot W^{-1} + c_2 \cdot V_{DD}^{-1} + c_3 \cdot V_{DD} + c_4 \cdot V_{DD} \cdot W \end{split}$$

The E[SNM] expression represents the mean value for SNM. Since all mutual covariance expressions  $\Sigma_{mutual}(W, V_{DD})$  can use the same fitting formula but different fitting parameters, we use a common mutual covariance expression above to represent the covariance between any two constraints. e.g. read delay and SNM, write margin and SNM, etc.

Because the model already includes the correlation between any two margins, the optimization process automatically handles the case when two margins are conflicting. For example, increasing SNM may reduce WRM, the dynamic programming we use will search a balance point between these two margins according to the covariance matrix and guarantee that both margins are satisfied. The size of the SRAM array is fixed to be 1Mb. The nominal  $V_{DD}$  is IV for the active mode and 0.4V for the sleep mode. Adaptive voltage is limited to 20% of the nominal value. The ratio of transistor widths in the 6T cell is kept constant. The area changes are produced by varying the normalized width (w), which uniformly sizes all transistors in the cell. The yield constraint of 90% was used.

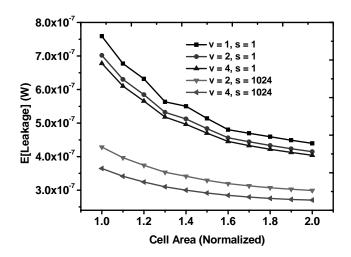

Using dynamic programming, we can solve the optimization problem (1). And based on the output of the optimization problem, we obtain the tradeoff curve between power and cell area, shown in Figure 2.6. In Figure 2.6, the experiment result shows that by applying the partition technique, we can achieve power saving and area saving. In the figure, v is voltage complexity, which is the number of voltages available for selection, and s is the switching complexity, which is number of partitions in the SRAM array.

Figure 2.6: Expected power vs. bitcell area Pareto curves for different voltage and switch complexities in active mode.

In Figure 2.6, one important question we sought to answer is the dependence of improvements in area and expected power on the number of voltage levels (v) available. We find that when no spatial partitioning is available (switch complexity s=1), there is little improvement with higher v. However, once spatial partitioning is available (s=1024), area savings are larger for a higher number of voltage levels. Yet, the difference between v=4 and v=2 is not dramatic, which indicates that even a small number of different voltage levels can be effective in tuning circuits.

Similarly, for SRAM operating sleep mode, based on the same principle we use for the active mode optimization, we derive the optimal voltage selection for different partition sizes and cell sizes, and we explore the area reduction under different switching complexity, the experiment result is shown in Figure 2.7.

Figure 2.7: Expected leakage vs. bitcell area Pareto curves for different voltage and switch complexities in sleep mode.

Figure 2.7 shows that by using larger partition size, for all values of switching complexity, the average leakage saving of 44% can be achieved.

Overall, we propose an SRAM tuning strategy for reducing intra-array randomness through shifting empirical distributions (realizations) of RCM, WRM, and SNM in a partition to meet the target. We develop quantitative models that for the first time allow rigorous design of adaptive SRAM arrays with large intra-array randomness.

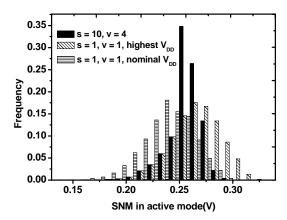

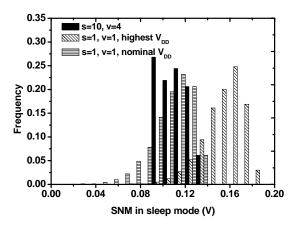

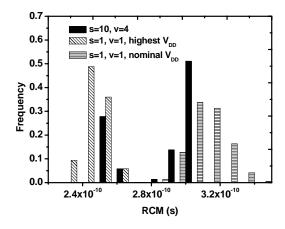

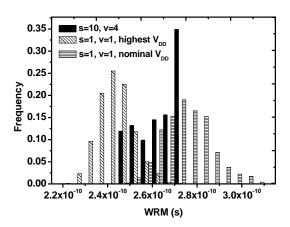

To verify the effectiveness of our partition technique SRAM on saving power while keeping all noise margins, we run Monte Carlo simulations on the SRAM block. In these simulations, without partitioning, the SRAM has to run at the highest voltage to satisfy a high yield target. With partitioning, only a few partitions have to run at the highest voltage to satisfy the margins. The results are shown from Figure 2.8 to Figure 2.11. Each of Figure 2.8~2.11 shows three cases: 1) No partition with nominal  $V_{DD}$ ; 2) No partition with the highest  $V_{DD}$ ; 3) 1024 partitions with four different  $V_{DDS}$ .

Figure 2.8: Monte Carlo simulation for SNM in active mode.

Figure 2.9: Monte Carlo simulation for SNM in sleep mode.

Figure 2.10: Monte Carlo simulation for RCM.

Figure 2.11:. Monte Carlo simulation for WRM in active mode.

## 2.3 SUMMARY

In this chapter, we propose an SRAM tuning strategy for reducing intra-array randomness through shifting empirical distributions (realizations) of RCM, WRM, and SNM in a partition to meet the target. We develop quantitative models that for the first time allow rigorous design of adaptive SRAM arrays with large intra-array randomness.

# **Chapter 3: Timing Error Acceptance in Image Processing**

The 2D-IDCT and 2D-DCT computations can be represented by  $I = C^T \cdot A \cdot C$  and  $I = C \cdot A \cdot C^T$ , respectively, where C is the orthogonal type-II DCT matrix and A is the spectrum coefficient matrix. It is customary to implement the 2D-IDCT/DCT as a sequence of two 1D-IDCT/DCTs. For each 1D-IDCT/DCT, the core algorithm is a matrix-vector dot product. For IDCT, the transformation is:

$$T(k) = \frac{c(k)}{2} \cdot \sum_{n=0}^{N-1} x(n) \cos\left[\frac{(2k+1)n}{2N}\pi\right]$$

$$N = 8, c(0) = \frac{1}{\sqrt{2}}, c(n) = 1, 0 \le k \le N-1$$

where x(n) is the data being processed. The DCT is very similar, except that the coefficient matrix is transposed. The following discussions will focus on a 2D-IDCT. Application to a corresponding 2D-DCT will be discussed later.

### 3.1 ERROR CONTROL THROUGH KNOWLEDGE OF OPERAND STATISTICS

When  $V_{DD}$  is scaled down, large magnitude timing errors are very likely to happen in additions of small numbers with opposing sign. Such additions lead to long carry chains and are the timing-critical paths in the adder. The worst case for carry propagation occurs in the addition of -1 and 1. In 2's complement representation, this operation triggers the longest possible carry chain and, thus, experiences timing errors first. Crucially, when a timing error occurs, the apparent result will also have a very large possible numerical error due to carry propagation into the MSBs leading to a large magnitude mismatch compared to the error-free result. For example, in an 8-bit computation, the error magnitude can be up to 64. This analysis and this problem is, of course, specific to the 2's complement representation of signed numbers. However, our techniques can also be used in sign-magnitude representation. As will be detailed later, in

sign-magnitude arithmetic, subtractions or opposing-sign additions are internally computed using 1's or 2's complement logic. This results in similar timing error behavior and our techniques remain effective.

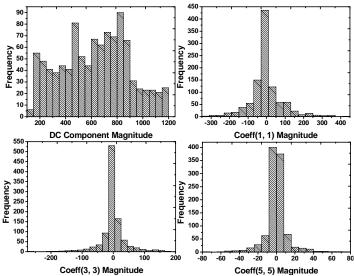

Figure 3.1: Frequency distribution of IDCT coefficients for sample image.

Figure 3.2: Partitioning of input matrix.

(c) Quality loss vs. component classification.

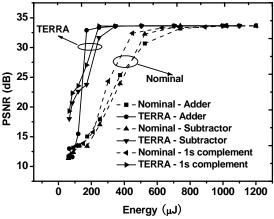

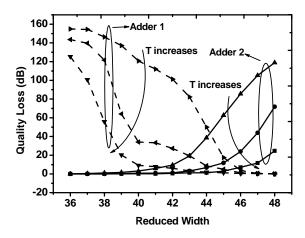

Figure 3.3: Quality-energy tradeoffs in Adder 1 and Adder 2.

In the 2D-IDCT algorithm, the additions that involve small-valued, opposite-sign operands occur in the processing of high-frequency components. This is because the first 20 low-frequency components contain about 85% or more of the image energy [18]. Hence, the magnitude of high-frequency components tends to be small, and coefficients follow a Laplace distribution with high probability densities concentrated in a narrow range [32], as shown in Figure 3.1. Furthermore, the Laplace distributions are zero-centered, which implies that high frequency components also tend to have opposing signs. As such, a significant amount of quality loss at scaled V<sub>DD</sub> can be attributed to additions involving such components. The first specific technique we employ is based on the realization that an adder with a bitwidth smaller than required by other considerations can be used to process such operands. Two objectives are achieved by using such adders: the magnitude of quality loss is reduced and its onset is delayed. Large-valued operands, of course, require a regular-width adder. Note that in an actual implementation it is possible to utilize a single adder with variable bitwidth.

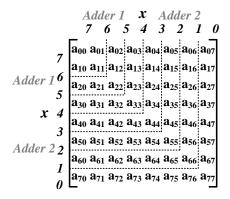

In the IDCT algorithm, the classification of matrix elements can be done at design time. This raises the question of (a) how to best perform this classification; and (b) how to identify the optimal bitwidth of the reduced-width adder. In the following, we develop a model to enable such a design optimization. We define Adder 1 as the regular-width adder and Adder 2 as the reduced-width adder. In classifying the components, we seek to find the boundary, within the data matrix, between the upper-left low-frequency components and the lower-right high-frequency components. We therefore define the following parameters of our model:

x: Boundary between high-/low-frequency coefficients (Figure 3.2).

$D_1$ : Worst-case delay of Adder 1.

$D_2$ : Worst-case delay of Adder 2.

$T_I$ : Timing budget of Adder 1.

$T_2$ : Timing budget of Adder 2.

We assume throughout this discussion that  $T_2=D_2$ , i.e. that no timing errors are allowed to occur in Adder 2. Furthermore, we assume that  $T_1=T_2$ , which implies that both adders are affected by  $V_{DD}$  scaling in an identical manner.

Based on this notation, we can study the Q-E characteristics of the two adders under scaled  $V_{DD}$ . By exploring adder characteristics, we are able to identify the optimal partitioning strategy from the point of view of achieving a globally optimal Q-E result. For simplicity, we substitute in this analysis the equivalent notion of timing budget for the value of  $V_{DD}$ .

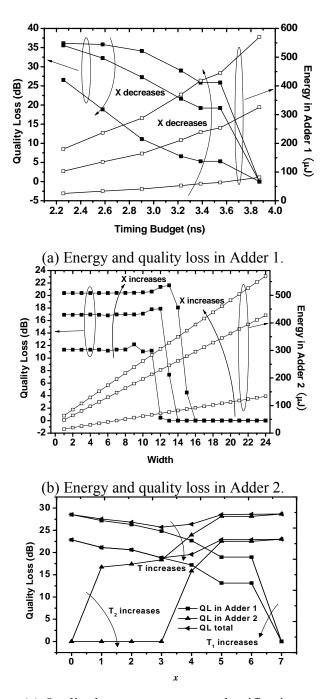

We first study the Q-E relation for the regular width adder, shown in Figure 3.3 (a). The right axis shows the energy value at different timing budgets  $T_I$ . As expected, allotting a smaller timing budget, which entails an equivalent lowering of  $V_{DD}$ , results in a reduction of energy. Increasing the number of matrix components processed in the reduced-width adder, i.e. increasing x, results in fewer additions performed by Adder 1, and thus a lower energy at the same timing budget. The quality loss (shown on the left axis) is initially low when the allotted timing budget is high and few computations experience error. As  $T_I$  is reduced, however, we begin to observe that the quality loss is smaller for larger x. This corresponds to the scenario in which fewer operations are performed by Adder 1, and thus there is less opportunity for timing errors to occur.

The Q-E behavior of the reduced-width adder is shown in Figure 3.3 (b). We are specifically interested in finding the Q-E behavior as a function of the bitwidth. Note that because no *timing* errors are allowed in Adder 2, an exploration with respect to timing budget, as shown for Adder 1 above, would have no purpose. We see that for large bitwidths of Adder 2, there is no quality loss. A significant reduction in quality occurs

with the onset of overflow errors when the magnitude of data being processed is larger than the available adder width.

Figure 3.4: Energy vs. quality loss Pareto front - comparison.

The analysis of the system Q-E behavior combines the behavior of Adder 1 and Adder 2. This enables exploration of the x,  $D_2$ ,  $W_2$ , and  $T_1$  design space in order to find an optimal Q-E solution. The primary trade-off involves the choice of x. From Figure 3.3 (c), we can see that the total quality loss reaches a minimum when x is around 4. For larger values, the quality loss due to Adder 2 becomes excessive. For smaller values, the quality loss is dominated by errors from Adder 1. However, the optimal choice of x also depends on both the total timing budget available as well as the bit-width of Adder 2. The set of optimal design decisions is best represented as a Pareto curve in the energy-quality space as shown in Figure 3.4. The figure shows the Pareto points, i.e.  $min(Q \mid E)$ , that are generated by different choices of x and  $W_2$  at different  $T_1$ .

To understand the behavior of Pareto points in Figure 3.4 and trace the dependence of the optimal x on  $T_1$  and  $W_2$ , we first study the simple case when  $D_2 \le T_1$ . Then, we relax the constraint to allow  $D_2 > T_1$ , and we adjust x and  $W_2$  under a fixed  $T_1$  to determine the new optimal set of x and  $W_2$  under the relaxed constraint.

Under the constraint that  $D_2 \le T_I$ , we can observe: 1) the optimal x is set by the overflow boundary  $(x_{of})$ ; and 2) the optimal Adder 2 width is the maximum Adder 2 width  $(W_{2max})$ , which is set by  $T_I$ . The  $x_{of}$  here is defined as the maximum possible x for a given  $W_2$  without having overflows in Adder 2, as shown in Figure 3.5 (a).

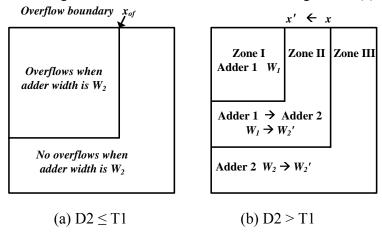

Figure 3.5: DCT coefficient partitioning.

For a given timing budget  $T_I$  and  $D_2 \le T_I$ , there must not be any timing errors and we can define a maximum Adder 2 width as  $W_{2max}$ . Since the onset of overflow immediately leads to large errors (Figure 3.3 (b)),  $W_{2max}$  also sets a maximum x of  $x_{of}$  at the boundary at which overflows appear. At the same time, we always aim to send as much data as possible to the error-free reduced-width adder (Adder 2), so as to reduce timing errors in the full-width adder (Adder 1). Hence, we choose x to be at its maximum limit ( $x_{of}$ ) to allow as much data as possible being processed in Adder 2.

To further explore the design space beyond the point for which no timing errors are allowed in Adder 2, we state a theorem, and present its complete proof in Section 2.5:

**Theorem1:** In the absence of overflows, the output timing error in a wide adder is greater than or equal to the error in a smaller-width adder when both adders process the same operands.

According to this theorem, sending more data to Adder 2, i.e. increasing x, will make it possible to further reduce the quality loss, even in the presence of timing errors in both adders. However, in order to avoid exceeding the overflow boundary with its large quality loss, we also have to increase  $W_2$  and hence  $x_{of}$ , relaxing the timing constraint for Adder 2 to  $D_2 > T_1$ . As shown in Figure 3.5 (b), data in Zone I and Zone II is originally processed by Adder 1 using width  $W_1$ . Data in Zone III is processed by Adder 2 using width  $W_2$ . After increasing x, data in Zone II is processed by Adder 2 using width  $W_2$ ', s.t.  $W_2 < W_2$ '  $< W_1$ . The quality loss in Zone II is reduced while the quality loss in Zone III increases according to Theorem 1. Since increasing x, i.e. sending more data to Adder 2, can reduce timing errors in Adder 1, but increasing  $W_2$  leads to more timing errors in Adder 2, there exists an x (and  $W_2$ ) with maximum quality loss reduction. These points correspond to the Pareto front of the dashed line in Figure 3.4.

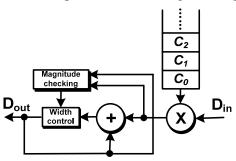

In the implementation, the reduced-width addition is actually realized using the truncated result of a regular-width adder sharing the same core logic. The combined adder architecture is shown in Figure 3.6. The indexes of the frequency coefficients are used by the control logic to determine whether to feed them into a full-width or reduced-width addition. The control logic compares the index of the matrix component currently being processed with the predetermined classification constant x. The output of this comparison is used to activate a truncation logic. The truncation logic takes a reduced number of LSBs from the full-width adder output according to the pre-designed Adder 2 width, and sign extends them back to the full width and feeds the result back into the destination accumulator.

(a) Technique abstraction

(b) Implementation

Figure 3.6: Reduced width adder.

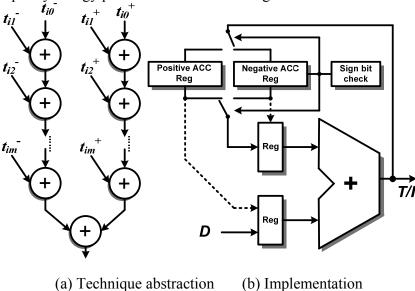

### 3.2 ERROR CONTROL BY DYNAMIC REORDERING OF ACCUMULATIONS

The technique introduced in Section 3.1 is able to delay the onset of large-magnitude errors in individual two-operand additions. The second technique presented in this section is based on reduction of the cumulative quality loss resulting from multiple additions, such as accumulations, which are a key component of many DSP algorithms, and, specifically, of IDCT. The key observation is that if positive and negative operands are accumulated separately, and added only in the last step, the number of error-producing operations is reduced to one last addition that involves operands with opposite sign. At the same time, the operands involved in this last addition are guaranteed to be larger in absolute value than any individual opposite-sign operands involved in the original sequence of additions. This guarantees that the reordered accumulation will result in a smaller quality loss under scaled timing.

Let us illustrate how the order of operations in accumulation affects the timing errors occurring at a given timing budget. The difference between optimized and unoptimized sequences is significant. As an example, consider four numbers (-1, 1, -1, 1) being accumulated. There are three possible sequences of accumulation:

Case 1: 111111111+00000001+111111111+00000001

Case 2: 111111111+11111111+00000001+00000001

Case 3: (11111111+111111111)+(00000001+00000001)

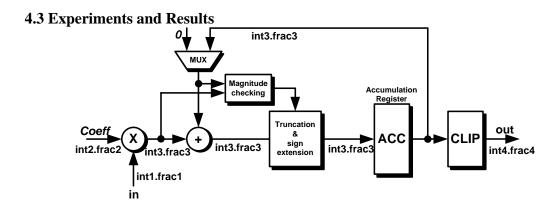

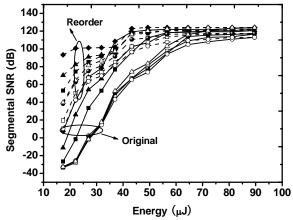

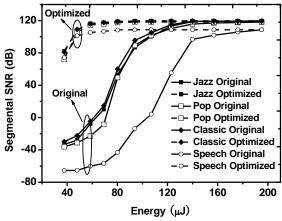

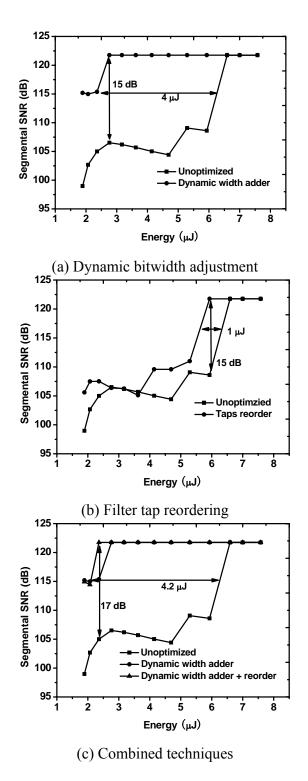

For Case 1, the 1st and the 3rd additions have large delay, each with a carry chain length of 8. For Case 2, the 3rd addition has large delay with a carry chain of 8. For Case 3, only the addition outside the brackets has large delay with a carry length of 7. The total timing budget in Case 3 is roughly half of that of Case 1. Thus, we observe that the order of accumulation can significantly affect the frequency of worst-case delay as well as the length of the longest carry chain.