Copyright

by

Yao-Feng Chang

2015

# The Dissertation Committee for Yao-Feng Chang Certifies that this is the approved version of the following dissertation:

## Intrinsic Unipolar SiO<sub>x</sub>-based Resistive Switching Memory: Characterization, Mechanism and Applications

| Committee:              |

|-------------------------|

|                         |

| Jack C. Lee, Supervisor |

| Deji Akinwande          |

| Burt W. Fowler          |

| Edward T. Yu            |

| Paul S. Ho              |

# Intrinsic Unipolar SiO<sub>x</sub>-based Resistive Switching Memory: Characterization, Mechanism and Applications

by

Yao-Feng Chang, B.S.; M.S.

### Dissertation

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

**Doctor of Philosophy**

The University of Texas at Austin August, 2015

#### Acknowledgements

First and foremost, I would like to express my gratitude to my Ph.D. advisor Professor Jack C. Lee for being such a great mentor guiding me throughout my research and study. He has always been responsible, supportive, attentive and encouraging. I would like to thank him for all the valuable discussions which consolidate my knowledge on device physics and lead me into the cutting-edge research. His effective management style helps to keep me on the right tract of research while also leave me enough space to advance myself and bring out new ideas. It is a great experience working under Professor Lee's supervision, not only because of his knowledge on semiconductor research and industry, but also his active personality that teaches me to be open-minded and always keep heads up.

I'm grateful for all the supports from my dissertation committee Prof. Deji Akinwande, Prof. Edward T. Yu, Prof. Paul S. Ho and Dr. Burt W. Fowler. I would like to thank them for their suggestions and advices to make this Ph.D. work better.

I would like to thank my group members and colleagues for their continuous support. This dissertation could not be accomplished without their assistance. I really appreciate the help and guide from senior group member Dr. Yen-ting Chen and Dr. Burt W. Fowler, who trained me on all the device fabrication and characterization techniques. Without their solid work and rich experiences on SiO<sub>x</sub>-based resistive switching devices, I would not be able to initiate my research on SiO<sub>x</sub>-based resistive switching devices so smoothly. I would like to thank them for being so generous to pass down their knowledge and experiences. Special thanks go to my colleague Fei Zhou, who gives me tremendous help throughout my research. Without his help, the fabrication process for scaled devices

could not be set up in such a short time. I would like to thank him for his sincere encouragement and caring. I'd also like to extend my gratitude to my fellow group members Dr. Yanzhen Wang, Dr. Fei Xue, Pai-Yu Chen, and Brad Bringhurst for their assistance and support.

I would like to express my deepest gratitude to my family. I appreciate my parents for their selfless love and endless support. Words won't be enough to thank them for being there for me whenever I need them. Many thanks to my beloved wife Chen for making my life colorful, easing my nerves, and encouraging me to pursue my dreams.

Finally, I'm grateful for this Ph.D. journey. What I learned here is far beyond research itself. I think the biggest difference between us human beings and the other animals is that we accumulate knowledge. No matter how far away the goal is, it can be reached step by step. No matter how huge the task is, it can be finished piece by piece. Even if at the end you couldn't get to the finish line yourself, someone else will carry on. Or, maybe there isn't any finish line. That's how we keep reaching. So don't worry if you don't see any improvement today, or your device failed, or your boss think your idea is worthless. Just keep your head up, and show the world the most undefeatable human stubbornness.

Intrinsic Unipolar SiO<sub>x</sub>-based Resistive Switching Memory:

**Characterization, Mechanism and Applications**

Yao-Feng Chang, Ph.D.

The University of Texas at Austin, 2015

Supervisor: Jack C. Lee

Floating gate (FG) nonvolatile memory has been the main structure of nonvolatile

memory devices, since its invention in 1967 by D. Kahng and S. M. Sze. They have been

widely employed in the portable electronic products such as mobile phones, digital

cameras, notebook computers, mp3 players and USB flash drives. However, as device

size continues to shrink, the typical flash memory device will continue to suffer from

issues of retention and endurance. In order to solve the problems, researchers have

considered new storage layers and novel structures in nonvolatile memory devices to

replace the conventional floating gate device. Therefore, a great deal of potential memory

structures have been proposed, with some transferring into a production line, such as

phase change memory (PCM), magnetic random access memory (MRAM) and

ferroelectric random access memory (FeRAM). In the innovation of memory devices,

resistance random access memories (ReRAMs) have gained significant research interest

as an alternative for next-generation nonvolatile memory due to its high density, low cost,

low power consumption, fast switching speed and simple cell structure.

In this dissertation, the intrinsic unipolar silicon oxide (SiO<sub>x</sub>-based) Resistive-

RAM (ReRAM) characterization, mechanism and applications have been presented. I

investigate device structures, material compositions and electrical characteristics to

vii

realize ReRAM cells with high ON/OFF ratio, low static power consumption, low switching power, and high readout-margin using complementary metal-oxide-semiconductor (CMOS) compatible SiO<sub>x</sub>-based materials. These ideas are combined with the use of horizontal and vertical device structure designs, composition optimization, electrical controlling and external factors for understanding resistive switching mechanism. Modeling of resistive switching mechanism, including temperature effect, pulse response and carrier transport behaviors are performed, to develop a compact model in energy diagram, trap-level information in SiO<sub>x</sub> resistive switching layer, even for computer-aided design (CAD) in very-large-scale integration (VLSI) design. Finally, synapse-based neuromorphic system is demonstrated in SiO<sub>x</sub>-based ReRAM, combining with bio-inspiration and biomimetics process illustrations. This work presents the comprehensively investigation of SiO<sub>x</sub>-based resistive switching characteristics, mechanisms, applications for future post-CMOS devices era.

## **Table of Contents**

| List of Ta  | blesxi                                                                                                                               |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------|

| List of Fig | gures xii                                                                                                                            |

| Chapter 1   | Introduction1                                                                                                                        |

| 1.1         | History of Memory1                                                                                                                   |

| 1.2         | Evolution of Nonvolatile Memory                                                                                                      |

| 1.3         | Novel Device Architecture – Resistive RAM (ReRAM)5                                                                                   |

| 1.4         | Emerging Active Material – Silicon Oxide (SiO <sub>x</sub> )7                                                                        |

| 1.5         | Outline8                                                                                                                             |

| Chapter 2   | Device Structure, Materials and Resistive Switching Behaviors11                                                                      |

| 2.1.        | Post-Deposition Anneal (PDA) and Polarity Effects                                                                                    |

| 2.2.        | Device Structure Designs, Composition, and Multilevel Operation19                                                                    |

| 2.3.        | Oxygen-Induced Bi-Modal Failure Phenomenon (Ambient Effect)34                                                                        |

| Chapter 3   | Resistive Switching Mechanism and Modeling40                                                                                         |

| 3.1.        | Edge and Bulk device Structures, and Backward-Scan Effect42                                                                          |

| 3.2.        | Oxide Stoichiometry Effects and Program Window Optimization50                                                                        |

| 3.3.        | Multilevel, Temperature Effect and Band diagram Modeling72                                                                           |

| -           | Integrated One Diode - One Resistor Architecture in Nano-Pillar SiO <sub>x</sub> stive Switching Memory by Nano-Sphere Lithography99 |

| 4.1         | SiO <sub>x</sub> -based memory element (1R) Fabricated by NSL and Basic<br>Characteristics                                           |

| 4.2         | 1D-1R Architecture in Nano-Pillar SiO <sub>x</sub> Resistive Switching Memory by Nano-Sphere Lithography                             |

|             | A Synaptic Device Built in 1D-1R Architecture with Intrinsic SiO <sub>x</sub> -based AM                                              |

| 5.1         | 1D-1R Architecture Fabricated by Standard CMOS Process110                                                                            |

| 5.2         | Basic Resistive Switching Behaviors in 1D-1R Architecture112                                                                         |

| 5.3         | Pulse Mapping and Long-Term Potentiation (LTP) and Long-Term Depression (LTD) Synaptic Behaviors                                     |

| 5.      | .4   | Spike-Tin      | ning-Dependent Plasticity (STDP) in the SiO <sub>x</sub> -based 1D-                | -1R |

|---------|------|----------------|------------------------------------------------------------------------------------|-----|

|         |      | architectu     | re                                                                                 | 119 |

| Chapte  | r 6: | Conclusio      | on and Future Work                                                                 | 126 |

| 6.      | .1.  | Conclusio      | on                                                                                 | 126 |

| 6.      | .2.  | Future W       | ork                                                                                | 128 |

|         |      | 6.2.1.         | Frequency Response and Internal Filament Modeling                                  | 128 |

|         |      | 6.2.2.         | Stacking Engineering of SiO <sub>x</sub> /HfO <sub>x</sub>                         | 129 |

|         |      | 6.2.3.<br>Bior | Bio-Inspiration from Mitochondrion: Reactive Oxygen mimetics in Electronics Device |     |

| Bibliog | grap | hy             |                                                                                    | 133 |

| Vita    |      |                |                                                                                    | 142 |

### **List of Tables**

| Table 1.1. | Potential of the current prototypical and emerging memory                      | 6  |

|------------|--------------------------------------------------------------------------------|----|

| Tabel 3.1. | Voltage dependence of current (I) and normalized conductance (G <sub>N</sub> ) | ), |

|            | and the axes used for linear fitting are listed for common insulator           |    |

|            | charge transport expressions                                                   | 5  |

| Tabel 3.2. | Defect switching charge-states, unoccupied switching charge-state              |    |

|            | energy level ( $E_C$ ), thermodynamic energy level ( $E_{TH}$ ), occupied      |    |

|            | switching charge-state energy level $(E_{V})$ and effective bandgap            |    |

|            | energy (E <sub>G</sub> )8                                                      | 3  |

## **List of Figures**

| Figure1.1   | Device structure of conventional nonvolatile flash memory and its        |

|-------------|--------------------------------------------------------------------------|

|             | application on electronics products                                      |

| Figure1.2   | Nonvolatile memory with (a) nanocrystal structure and (b) trapping       |

|             | dielectric structure                                                     |

| Figure1.3   | Potential memory structures: MRAM, FeRAM, and PCM4                       |

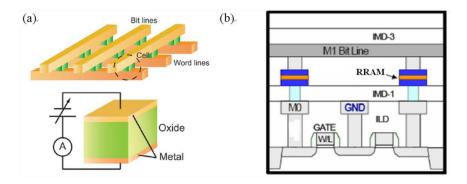

| Figure1.4   | Schematic structures of (a) 1R (ReRAM) device and (b) 1T (transistor) -  |

|             | 1R (ReRAM)6                                                              |

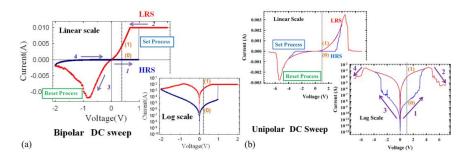

| Figure1.5   | Switching characteristics of ReRAM device (a) bipolar-type and (b)       |

|             | unipolar-type of SiO <sub>x</sub> -based ReRAM6                          |

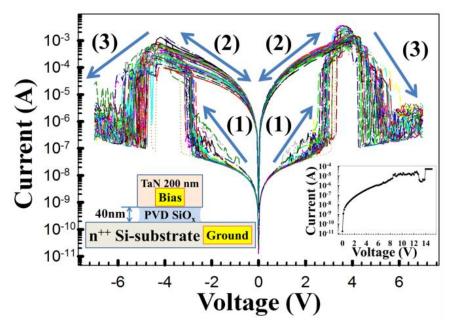

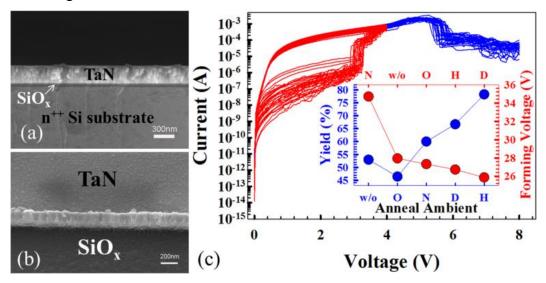

| Figure 2.1. | 30 cycles of resistive switching behavior in samples with PDA. Insets    |

|             | show a schematic representation of the $TaN/SiO_2/n^{++}$ Si-substrate   |

|             | structure, and an I-V plot of electroforming data                        |

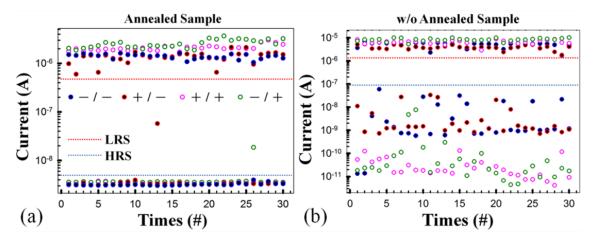

| Figure 2.2. | Polarity dependence (-/- means negative SET/negative RESET) of LRS       |

|             | and HRS distributions across 30 cycles for samples (a) w/ and (b) w/o    |

|             | 5min 500°C PDA in O <sub>2</sub>                                         |

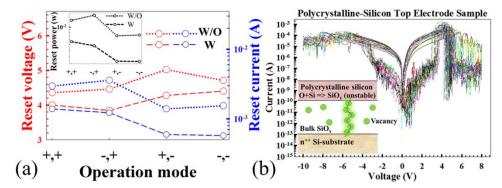

| Figure 2.3. | (a) Polarity dependence of RESET voltage, RESET current, and RESET       |

|             | power for samples w/ and w/o PDA. (b) Polycrystalline-silicon top        |

|             | electrode device switching characteristics                               |

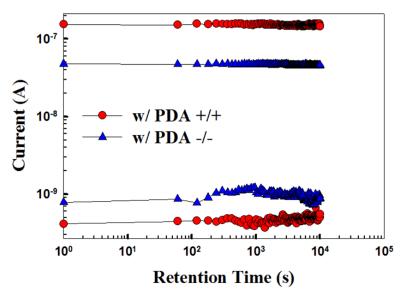

| Figure 2.4. | Retention test at room temperature for samples w/ PDA in positive and    |

|             | negative polarity conditions                                             |

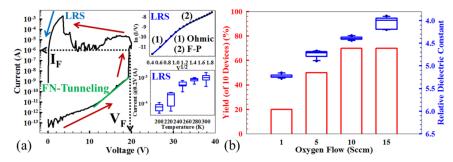

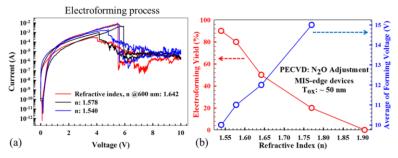

| Figure 2.5. | (a) The electroforming process. Insets show plots of temperature-related |

|             | in LRS. (b) The device yield and permittivity as function of oxygen flow |

|             | rate31                                                                   |

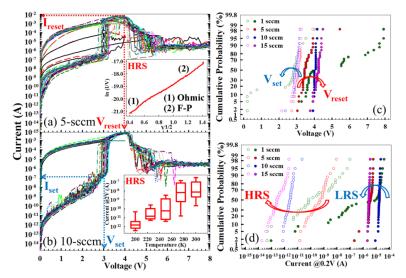

| Figure 2.6.  | Switching behaviors of (a) 5-Sccm and (b) 10-Sccm samples. Insets plot    |

|--------------|---------------------------------------------------------------------------|

|              | temperature-related in HRS. The distribution of oxygen-flow               |

|              | dependence (c) V <sub>set</sub> /V <sub>reset</sub> and (d) HRS/LRS31     |

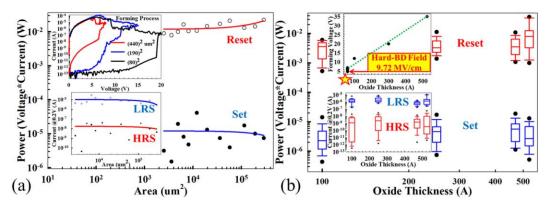

| Figure 2.7.  | (a) The electroforming process, average of switching powers, and HRS      |

|              | and LRS as a function of device size. (b) The forming voltage, statistics |

|              | of switching powers, and HRS and LRS as a function of $SiO_x$ thickness.  |

|              | 32                                                                        |

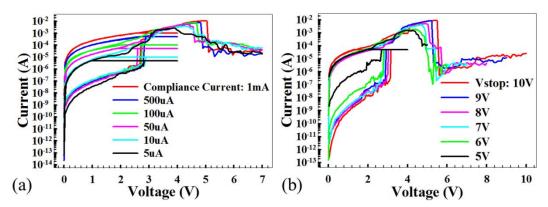

| Figure 2.8.  | Continuous unipolar switching behaviors (a) under a series of             |

|              | compliance current and (b) under a series of stopped voltage32            |

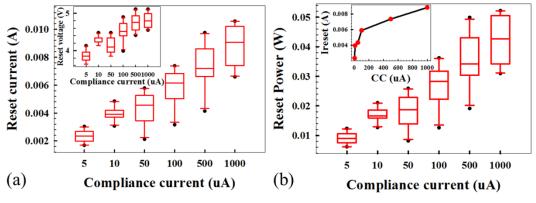

| Figure 2.9.  | (a) Statistics plots of RESET current, voltage, and (b) RESET power as    |

|              | a function of compliance current. The inset shows the average RESET       |

|              | current under a series of compliance current                              |

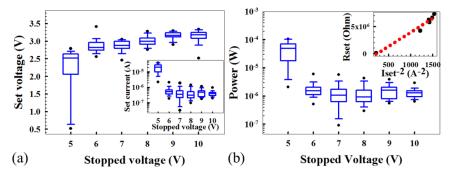

| Figure 2.10. | (a) Statistics plots of SET current and voltage as a function of stopped  |

|              | voltage. (b) Statistics plots of SET power as a function of stopped       |

|              | voltage                                                                   |

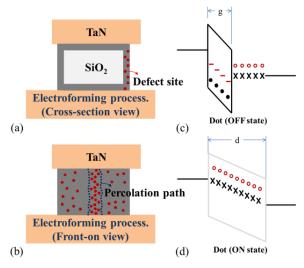

| Figure 2.11. | Schematic pictures of (a) showing the filament near the sidewall and (b)  |

|              | a front-view of the filaments. The band diagrams of sidewall-devices (c)  |

|              | HRS and (d) LRS states. 33                                                |

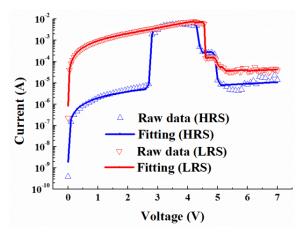

| Figure 2.12. | The simulated fitting curve from HRS and LRS in resistive switching       |

|              | behaviors. 33                                                             |

| Figure 2.13. | The simulated curve in (a) compliance current effect and (b) stopped      |

|              | voltage effect. 34                                                        |

| Figure 2.14. | The resistive switching behaviors and forming process (insets) in (a)     |

|              | vacuum and (b) N <sub>2</sub> ambient                                     |

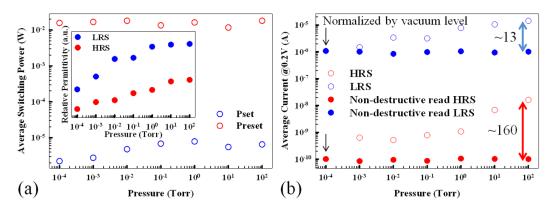

| Figure 2.15. | (a) Average of switching powers, relative permittivity values for LRS                            |

|--------------|--------------------------------------------------------------------------------------------------|

|              | and HRS by Frenkel-Poole fitting (inset), and (b) LRS and HRS as a                               |

|              | function of N <sub>2</sub> pressure                                                              |

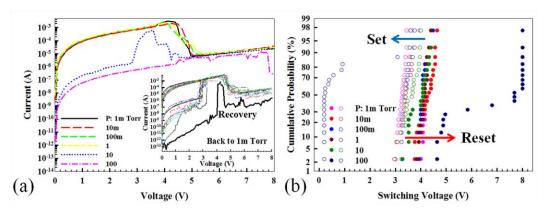

| Figure 2.16. | (a) Average current for 20 SET/RESET cycles for different 20% $\mathrm{O_2}\text{-}\mathrm{N_2}$ |

|              | pressures and recovery process in vacuum (inset). (b) Cumulative                                 |

|              | probability of switching voltage as function of 20% O <sub>2</sub> -N <sub>2</sub> pressure.39   |

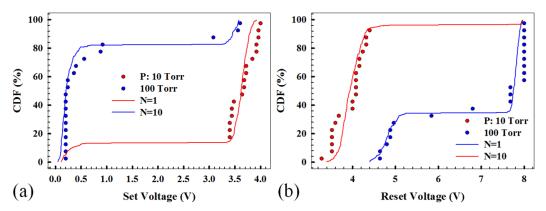

| Figure 2.17. | Initiation of resistive switching failures above 10 Torr of 20% $O_2$ - $N_2$                    |

|              | mixture showing the cumulative distribution function (CDF) using bi-                             |

|              | modal Monte Carlo simulation fitting for (a) SET and (b) RESET                                   |

|              | voltage39                                                                                        |

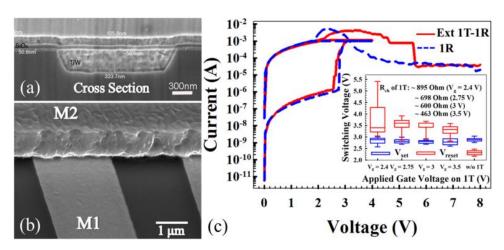

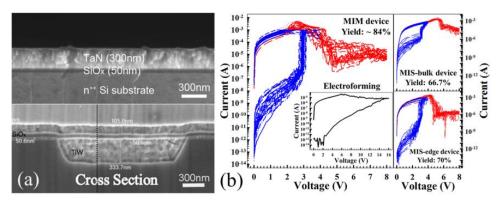

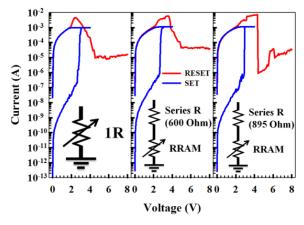

| Figure 3.1.  | (a) Cross-sectional and (b) tilted-view SEM images of MIM edge-                                  |

|              | device, and (c) resistive switching behaviors with and without an                                |

|              | external 1T-1R configuration                                                                     |

| Figure 3.2.  | (a) Cross-sectional and (b) tilted-view SEM images of MIS bulk-device                            |

|              | and (c) resistive switching behaviors                                                            |

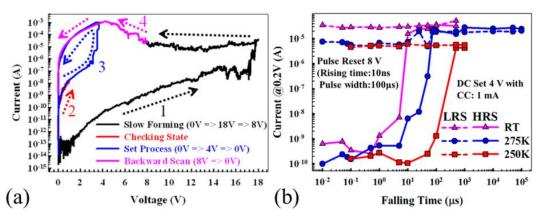

| Figure 3.3.  | (a) The backward-scan effect in DC sweep. (b) The backward-scan                                  |

|              | effect using AC pulses with controlled falling times versus temperature.                         |

|              | 50                                                                                               |

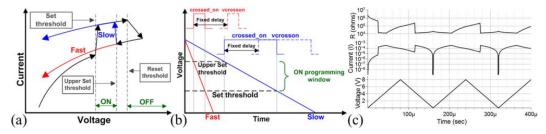

| Figure 3.4.  | The fast (red) and slow (blue) backward voltage sweeps plotted in (a) I-                         |

|              | V and (b) V-t form. (c) Resistance (R), current (I) and voltage (V)                              |

|              | simulation results from OFF to ON state50                                                        |

| Figure 3.5.  | (a) SEM images of MIS and MIM structures. (b) 30 cycles of I-V plots                             |

|              | for MIM, MIS-bulk and MIS-edge devices with corresponding yield                                  |

|              | labeled. 69                                                                                      |

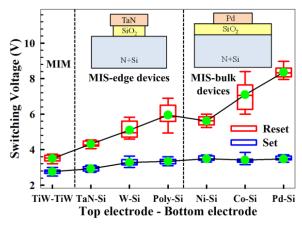

| Figure 3.6.  | Effects of electrode material on SET and RESET switching voltage             | s in  |

|--------------|------------------------------------------------------------------------------|-------|

|              | MIM, MIS-edge and MIS-bulk devices.                                          | 70    |

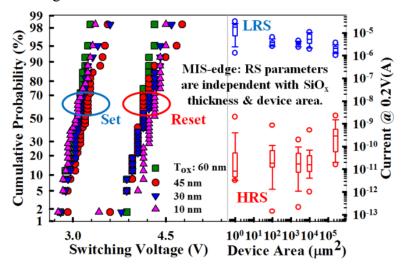

| Figure 3.7.  | RS parameter dependence on SiO <sub>x</sub> thickness and device area in MIS | S-    |

|              | edge devices.                                                                | 70    |

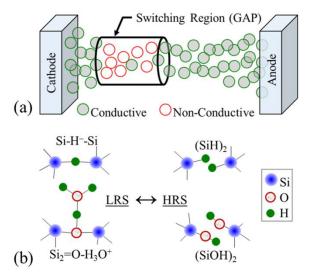

| Figure 3.8.  | (a) Physical representation of conductive filament with switching re-        | gion. |

|              | (b) Hypothesized defect complex in LRS and HRS.                              | 70    |

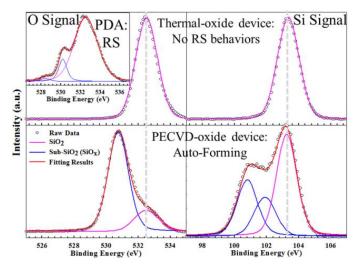

| Figure 3.9.  | XPS spectra and fitting results for LPCVD thermal oxide, sputtered           | l     |

|              | oxide with PDA treatment, and PECVD oxide.                                   | 71    |

| Figure 3.10. | (a) I-V plots for $SiO_xN_y$ -based devices, demonstrating autoforming       |       |

|              | capability. (b) Device yield and forming voltage versus refraction in        | ndex. |

|              |                                                                              | 71    |

| Figure 3.11. | RS characteristics of MIM device with and without an external series         | es    |

|              | transistor                                                                   | 71    |

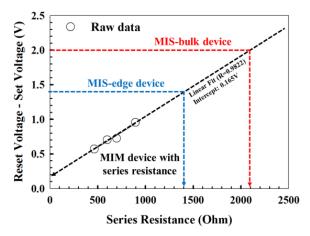

| Figure 3.12. | Program voltage window $(V_{reset} - V_{set})$ dependence of MIM structure   | re    |

|              | versus external series resistance.                                           | 72    |

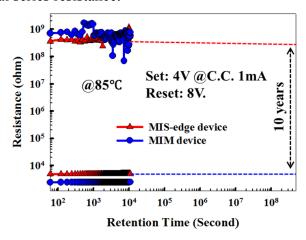

| Figure 3.13. | Static data retention test at 85 °C for MIM and MIS-edge devices             |       |

|              | programed to the HRS and LRS.                                                | 72    |

| Figure 3.14. | Current transport modeling in various voltage ranges with multi-lev          | /el   |

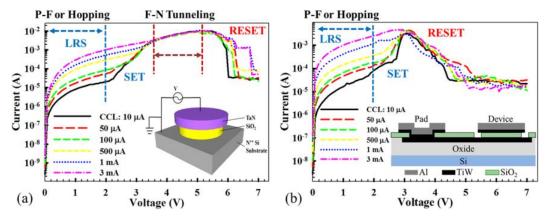

|              | control by CCL in (a) MIS and (b) MIM structures.                            | 94    |

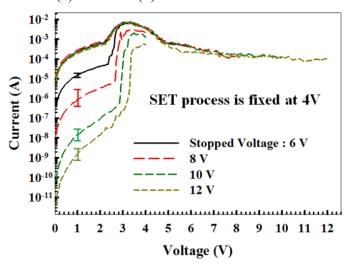

| Figure 3.15. | Switching behaviors and HRS curves for MIM device programed w                | ith a |

|              | series of RESET stopped voltages.                                            | 94    |

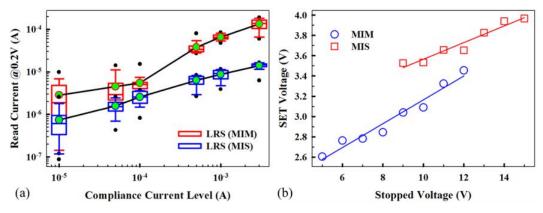

| Figure 3.16. | (a) LRS for MIM and MIS structures programed by controlling the              | CCL.  |

|              | (b) SET voltage versus RESET stopped voltage for MIM and MIS                 |       |

|              | devices                                                                      | 94    |

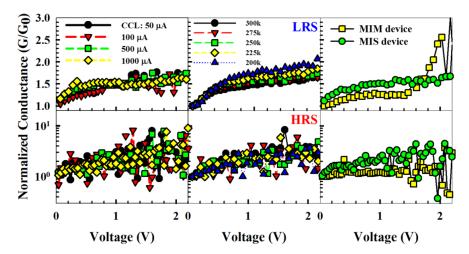

| Figure 3.17. | Normalized conductance of LRS/HRS as a function of CCL, ambient           |              |

|--------------|---------------------------------------------------------------------------|--------------|

|              | temperature, and MIM and MIS structure95                                  |              |

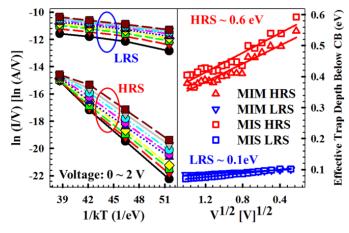

| Figure 3.18. | Poole-Frenkel emission analysis results in low voltage region and         |              |

|              | calculated energy barrier versus $V^{1/2}$ of LRS and HRS for MIM and MIS | S            |

|              | structures                                                                |              |

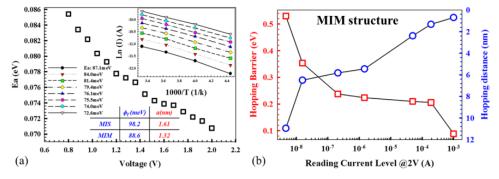

| Figure 3.19. | (a) Fixed-range hopping conduction of LRS in low voltage region for       |              |

|              | MIM and MIS structures. (b) Hopping barrier and hopping distance as a     | l            |

|              | function of reading current level by CCL control95                        |              |

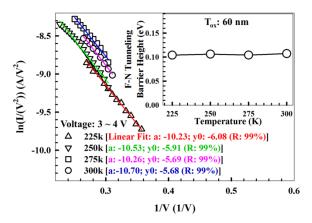

| Figure 3.20. | Fowler-Nordheim tunneling in MIS structure for the LRS in the             |              |

|              | moderate voltage region at 225 - 300 K96                                  |              |

| Figure 3.21. | Linear I-V response for MIM device showing RESET voltage sweep.           |              |

|              | Data fits to hopping conduction and TAT are plotted, and the              |              |

|              | extrapolated TAT threshold voltage is labeled                             |              |

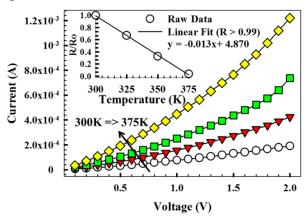

| Figure 3.22. | Measured I-V curves from 0 V to 2 V as a function of ambient              |              |

|              | temperature. Temperature coefficient was evaluated from the R - T plot    |              |

|              | in inset. 96                                                              |              |

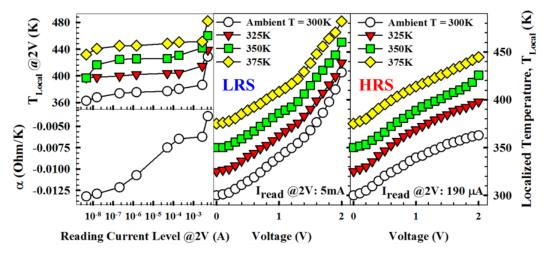

| Figure 3.23. | Extracted localized temperature and temperature coefficient for a series  |              |

|              | of ambient temperature ranges and intermediated states. Localized         |              |

|              | temperature versus voltage for LRS and HRS                                |              |

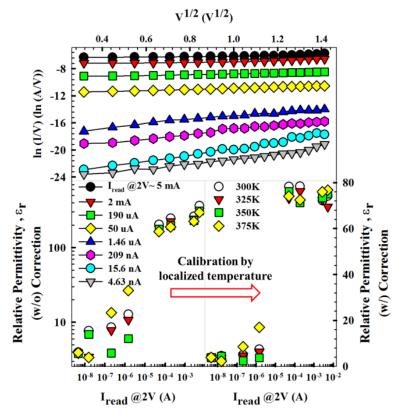

| Figure 3.24. | Relative permittivity extraction method and values as a function of       |              |

|              | ambient temperature range and intermediate states without and with        |              |

|              | localized temperature calibration. 97                                     |              |

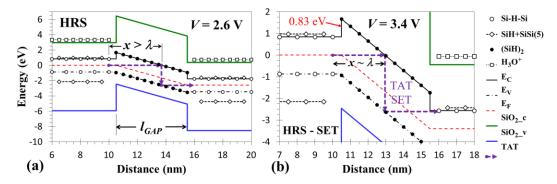

| Figure 3.25. | Energy band diagrams plotting electron potential energy versus distance   | <del>)</del> |

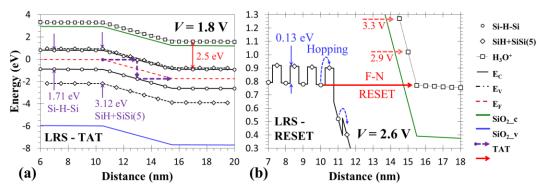

|              | along the conductive filament in the HRS                                  |              |

| Figure 3.26. | Energy band diagrams plotting electron potential energy versus distance                 | :e |

|--------------|-----------------------------------------------------------------------------------------|----|

|              | along the conductive filament in the LRS                                                |    |

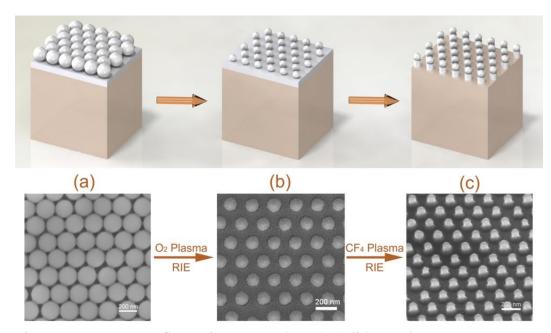

| Figure 4.1   | 1R process flow using nano-sphere (NS) lithography106                                   |    |

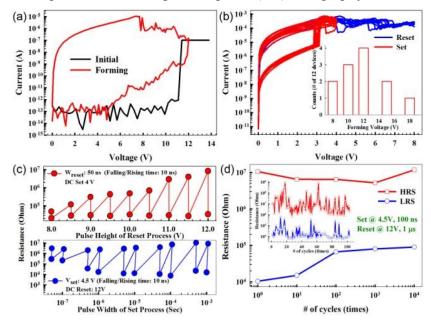

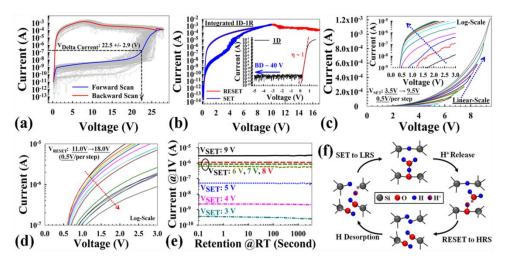

| Figure 4.2   | DC sweep resistive switching behaviors and AC pulsed response of 1R                     |    |

|              | element. 106                                                                            |    |

| Figure 4.3   | 1D-1R fabrication procedure using DSE                                                   |    |

| Figure 4.4   | 1D-1R electrical characteristics when using NSL and DSE107                              |    |

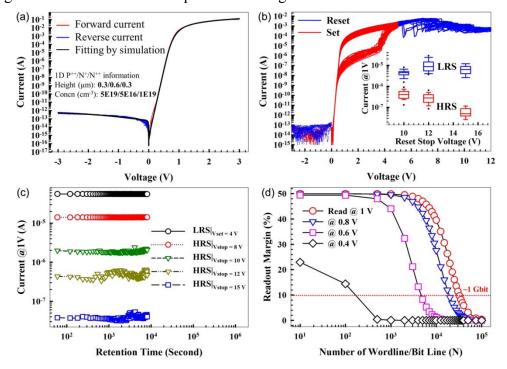

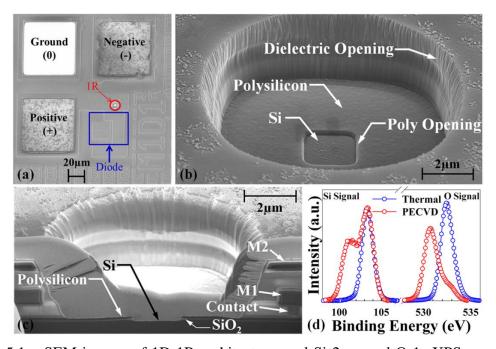

| Figure 5.1.  | SEM images of 1D-1R architecture, and Si- $2p_{2/3}$ and O-1s XPS spectra               | l  |

|              | for PECVD oxide and thermal oxide                                                       |    |

| Figure 5.2.  | DC sweep resistive switching behaviors of 1D-1R architecture124                         |    |

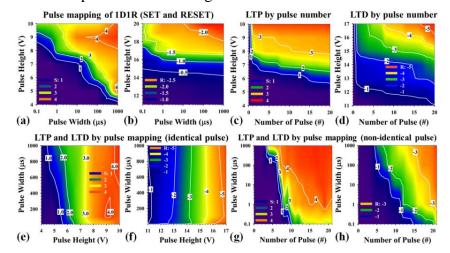

| Figure 5.3.  | AC pulse mapping plots of current-change ratio by modulating pulse                      |    |

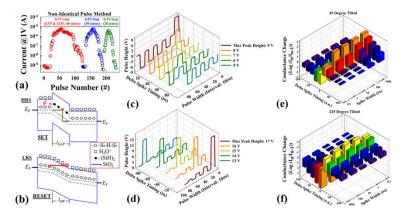

|              | height and pulse width to demonstrate synaptic behaviors124                             |    |

| Figure 5.4.  | Demonstration of a SiO <sub>x</sub> -based synaptic device                              |    |

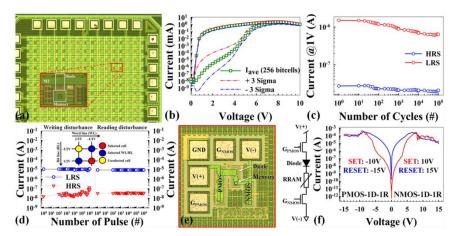

| Figure 5.5.  | Electrical variation and reliability results for array structure for potential          | al |

|              | use in future neuromorphic computing applications125                                    |    |

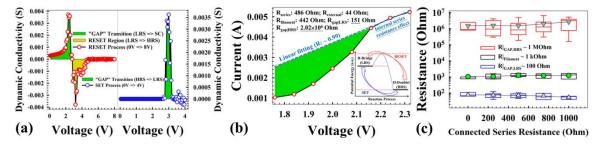

| Figure 6.1.  | (a) $\partial I/\partial V$ characteristics for RESET and SET processes. (b) Calculated | ļ  |

|              | resistance values of filament, HRS, and LRS, and (c) for 10 cycles                      |    |

|              | versus external series resistance                                                       |    |

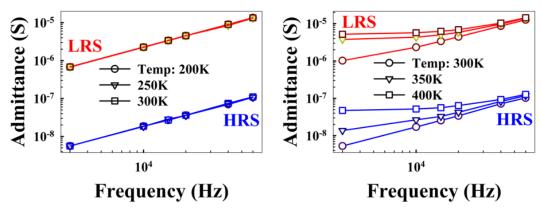

| Figure 6.2.  | Admittance versus AC frequency between LRS and HRS (a) at low                           |    |

|              | temperature range and (b) at high temperature range                                     |    |

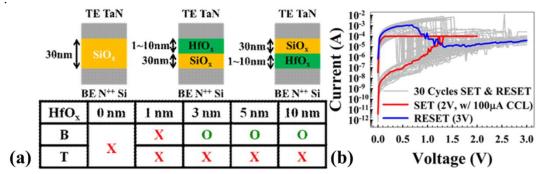

| Figure 6.3.  | (a) Schematic description of vertical stacks of $SiO_x/HfO_x$ layers (scales            | 3  |

|              | and layer position). (b) Thirty I-V SET and RESET curves in air with                    |    |

|              | low voltage (< 2V) switching. 130                                                       |    |

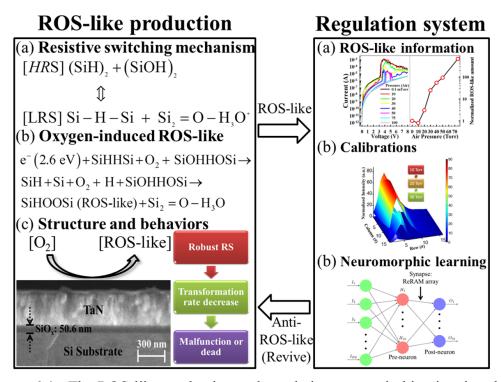

| Figure 6.4.  | The ROS-like production and regulation system in biomimetics electric                   | cs |

|              | devices                                                                                 |    |

#### **Chapter 1: Introduction**

#### 1.1 HISTORY OF MEMORY

If there was no record of culture relics and words for civilization, the era never existed in the past. People portrayed everything of life at different times in natural materials, such as stone, metal, and wood, to inherit the experience of life and prove the existence of once to be passed along. However, because the carriers of civilizations are bulky and difficult to be depicted and wrote by people, the life experience and scientific civilization can only be spread in the same place. When a major disaster or a big famine comes to here, people are forced to migrate to other environments, leading to the accumulated experience and knowledge of civilization making a fresh start. With the evolution of the times, the inventions of paper and printing bring people a convenient and light carrier of words, which causes the appearance of book. Not only the knowledge and ideas can be duplicated in books, but also they can be easily spread around the world. These inventions will make many people share the achievements of civilization. Owing to the continuous accumulation and growth of knowledge, the amount of papers and books used to store all civilizations also increase dramatically. In order to conserve these books and record the civilizations, people continue to set up the library around the world. But the space is limited; people are bound to find new ways to store knowledge. As the advent of the digital age, the problem of expansion of knowledge and information will be solved for human being.

Since the advent of the digital era, the way of digital memory is continuously in progress. Since the holes cards, magnetic matrix, tapes, magnetic cards, and hard disk used successively to nowadays flash memory invented by Simon M. Sze, the capacity and density of digital memory continues to upgrade and the speed also continuously increases. With the rise of portable electronic and Internet operations, knowledge of

people around the world communicates and delivers fast anytime and anywhere. The uploaded content is no longer just text but using the manner of photos, video, and sound to record moments of life in detail, even using the websites, blogs, Facebook, etc. to communicate with each other. These progress and development are attributed to digital electronic technology and digital memory evolution.

#### 1.2 EVOLUTION OF NONVOLATILE MEMORY

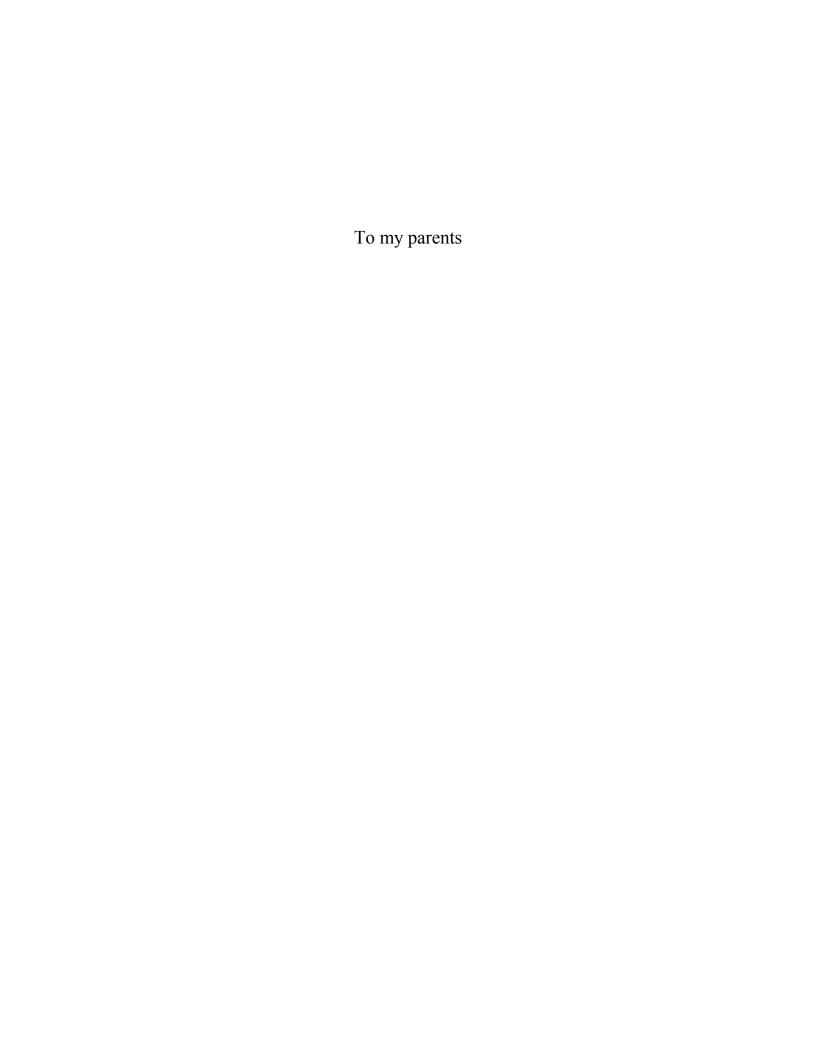

In Floating gate (FG) nonvolatile memory has been the main structure of nonvolatile memory devices, since its invention in 1967 by D. Kahng and S. M. Sze. They have been widely employed in the portable electronic products such as mobile phones, digital cameras, notebook computers, mp3 players and USB flash drives. The typical structure of a nonvolatile flash memory device is shown in Figure 1.1. The operating principle of conventional nonvolatile memory is based on the use of polycrystalline silicon as a floating gate to store charges injected from a channel [1]. Once charges are present in the floating gate, the threshold voltage of the memory device is changed. The logical signal "0" and "1" is thereby defined by the level of threshold voltage. However, as device size continues to shrink, the typical flash memory device will continue to suffer from issues of retention and endurance. As the typical flash memory device scales down to the nanoscale, stored charges in the floating gate can easily tunnel through the tunnel oxide to the Si substrate [2]. The reason for this is that the thickness of the scaled tunnel oxide cannot provide enough blocking effect to keep the stored charges. Additionally, the presence of leakage paths in the tunneling oxide, created after thousands of operations, will cause a rapid and complete loss of stored charges in a floating gate with a continuous polycrystalline semiconductor layer.

Figure 1.1 Device structure of conventional nonvolatile flash memory and its application on electronics products

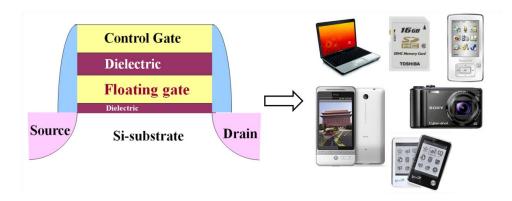

In order to solve the above-mentioned problems, researchers have presented two main methods to improve memory devices with different storage technologies: (1) methods which change the storage layer without changing the device structure and (2) methods proposing novel structures. In order to change the storage layer, either silicon nitride (served as a trapping layer in SONOS (silicon/oxide/nitride/oxide/silicon)) [3-6] or discrete nanocrystals [7-11] have been employed as storage cells (Figure 1.2). The stored charges can exist in the trap states of the charge trapping layer or can be retained in the distributed nanocrystals to maintain the memory function, even if localized leakage paths are present in the tunneling oxide.

Figure 1.2 Nonvolatile memory with (a) nanocrystal structure and (b) trapping dielectric structure.

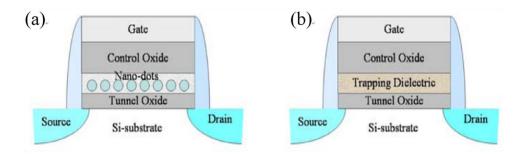

However, making changes to the storage layer still cannot solve issues of scaledown and program/erase speed. Therefore, researchers have considered new storage layers and novel structures in nonvolatile memory devices to replace the conventional floating gate device. The new nonvolatile memory devices must exhibit better program/erase speed and endurance. As for the scale-down requirements, the new device should be compatible with cross-point structure. Therefore, a great deal of potential memory structures have been proposed (Figure 1.3), with some transferring into a production line, such as phase change memory (PCM) [12], magnetic random access memory (MRAM) [13] and ferroelectric random access memory (FeRAM) [14]. In the innovation of memory devices, resistance random access memories (ReRAMs) have gained significant research interest as an alternative for next-generation nonvolatile memory [15-20] due to its high density, low cost, low power consumption, fast switching speed and simple cell structure. In addition, ReRAMs can possess program/erase speeds as high as SRAM, density as high as DRAM and nonvolatility for flash memory; therefore, ReRAMs demonstrate an extremely high potential for replacing NAND flash and DRAM to become the next-generation nonvolatile memory.

Figure 1.3 Potential memory structures: MRAM, FeRAM, and PCM.

#### 1.3 NOVEL DEVICE ARCHITECTURE – RESISTIVE RAM (RERAM)

The structure of ReRAM devices consists of sandwiched metal/insulator/metal (MIM) layers. By applying voltage or current, the resistance of the device can be changed, thereby giving the device data storage characteristics (Figure 1.4). ReRAM first originated from Hickmott in the 1960s; he discovered that the resistance of AlO<sub>x</sub> could be modified after voltage or current operation. In recent years, the resistive switching behaviors of a large variety of materials have been reported, including binary metal oxides such as NiO, CuO and HfO<sub>x</sub>. The logic state "0" or "1" is defined by different resistance values, and can be read by applying a low voltage to measure the resistance state (Figure 1.5). ReRAM devices exhibit good nonvolatile characteristics, and the stored data can be retained until the next data is written. It does not suffer from the issues of conventional flash memory does, which uses a continuous polycrystalline semiconductor layer as storage layer, in which the presence of leaky paths in the tunneling oxide will cause a rapid and complete loss of stored charges after thousands of operations. Unlike conventional flash memory, ReRAM uses resistance value to define the data state, and because its resistance state can be retained for a long time, ReRAM has better data storage capability (including switching speed, switching energy, and operation voltage) (Table 1.1) [21-23]. Characteristics such as low operation voltage, a fast program/erase speed and good scale-down capability make ReRAM a suitable candidate for the next-generation of nonvolatile memory. Hence, ReRAM is gaining significant interest in academia and industries for its high practicality and potential for commercial uses.

Figure 1.4 Schematic structures of (a) 1R (ReRAM) device and (b) 1T (transistor) - 1R (ReRAM).

Figure 1.5 Switching characteristics of ReRAM device (a) bipolar-type and (b) unipolar-type of  $SiO_x$ -based ReRAM.

|                         | Pr                      | ototypical (Table E | RD3)       | Emerging (Table ERD5)               |                   |                                  |                                      |                                              |                                                                                  |

|-------------------------|-------------------------|---------------------|------------|-------------------------------------|-------------------|----------------------------------|--------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------|

|                         |                         | I                   |            | Redox RRAM Others                   |                   |                                  |                                      | Others                                       |                                                                                  |

| Parameter               | FeRAM                   | STT-MRAM            | PCRAM      | Emerging<br>ferroelectric<br>memory | Conducting bridge | Metal Oxide:<br>Bipolar Filament | Metal Oxide:<br>Unipolar<br>Filament | Metal Oxide:<br>Bipolar Interface<br>Effects | Carbon-based Memory, Mott<br>Memory, Macro-molecular<br>Memory, Molecular Memory |

| Scalability             |                         | •••                 | $\odot$    | •••                                 | •                 | $\odot$                          | $\odot$                              | · ·                                          | ?                                                                                |

| MLC                     |                         | _                   | <u>•</u>   | <b>9</b>                            | <u> </u>          | •••                              | •••                                  | •••                                          | ?                                                                                |

| 3D integratio           | n 😃                     | •••                 | <u> </u>   | _                                   | •••               | •                                | •                                    | •                                            | ?                                                                                |

| Fabrication cost        | <u></u>                 | <u></u>             | •••        | <u></u>                             | •••               | •                                | ••                                   | ••                                           | ?                                                                                |

| Retention               | <u></u>                 | •••                 | ••         | <u></u>                             | •••               | •                                | •••                                  | _                                            | ?                                                                                |

| Latency                 |                         | •                   | ••         | •                                   | •••               | <u></u>                          | •••                                  | •••                                          | ?                                                                                |

| Power                   | <u> </u>                | <u></u>             |            | <u> </u>                            | <u> </u>          | <u></u>                          | <u> </u>                             | •••                                          | ?                                                                                |

| Endurance               | •                       | •                   | •••        | <u></u>                             | •••               | <u></u>                          |                                      | •••                                          | ?                                                                                |

| Variability             | •                       | _                   | •••        | <u></u>                             | •••               | •                                | (2)                                  | <u>•</u>                                     | ?                                                                                |

|                         |                         |                     | •••        |                                     |                   |                                  |                                      |                                              |                                                                                  |

| Scalability             | F <sub>min</sub> >45 nm | F =                 | 10-45 nm   | F <sub>rin</sub> <10 r              |                   |                                  |                                      |                                              |                                                                                  |

| MLC                     | difficult               | possi               |            | feasible                            |                   |                                  |                                      |                                              |                                                                                  |

| 3D integration          | difficult               | possi               |            | feasible                            |                   |                                  |                                      |                                              |                                                                                  |

|                         |                         |                     |            |                                     |                   |                                  |                                      |                                              |                                                                                  |

| Fabrication cost        |                         | medi                |            | low                                 |                   |                                  |                                      |                                              |                                                                                  |

| Retention               | poor (<<1yr)            |                     | est (>1yr) | long (>10y                          | rs)               |                                  |                                      |                                              |                                                                                  |

| Latency                 | long<br>(>10us)         | medii<br>10usi      |            | short<br>(<300ns)                   |                   |                                  |                                      |                                              |                                                                                  |

| Power                   | high                    | medi                |            | high                                |                   |                                  |                                      |                                              |                                                                                  |

| (Demonstrated<br>Write) |                         | IIIou               |            | , riigii                            |                   |                                  |                                      |                                              |                                                                                  |

| Endurance               | ≤1E5 cycles             | ≤1E1                | 0 cycles   | >1E10 cyc                           | les               |                                  |                                      |                                              |                                                                                  |

| Variability             | problematic             | reaso               | onable     | low                                 |                   |                                  |                                      |                                              |                                                                                  |

Table 1.1. Potential of the current prototypical and emerging memory.

#### 1.4 EMERGING ACTIVE MATERIAL – SILICON OXIDE (SIO<sub>x</sub>)

There have been many studies of binary metal oxide-based and perovskite oxidebased resistance switching characteristics for electronic device development [24, 25], which can have operating instability issues due to difficulty in controlling stoichiometric compositions [26, 27]. Therefore, a simple process that is compatible with conventional complementary metal-oxide semiconductor (CMOS) fabrication allows multi-layer compositional engineering and provides good electrical stability and high yield, which are critical requirements for neuro-electronics realization [28]. Silicon oxide (SiO<sub>x</sub>) has long been used as gate dielectrics for metal-oxide-semiconductor field-effect transistors. In addition to excellent insulating properties, resistive switching properties have been observed in SiO<sub>x</sub> materials as early as 1962 by Hickmott and 1967 by J. G. Simmons and R. R. Verderber, with additional modeling being done by G. Dearnaley in the 1970s [29-31]. They observed that a simple metal-insulator-metal structure (e.g. Au/SiO<sub>x</sub>/Al, MIM) can form an active memory device based on its repeatable negative resistance phenomenon. Recently, Yao et al. have reported SiO<sub>x</sub>-based resistive switching behaviors in vacuum, indicating that this traditionally passive material can be converted to an active memory element and controlled by external electrical activation [32-37]. Amount of recent reports also describe and indicate that using SiO<sub>x</sub> as the active switching medium in resistive switching memory devices [38-41]. We have further demonstrated a Si diode (1D) with low reverse-bias current integrated with a SiO<sub>x</sub>-based memory element (1R) using nano-sphere lithography and deep Si etching to pattern a P++/N+/N++ epitaxial Si wafer [42]. The above achievements for intrinsic SiO<sub>x</sub>-based ReRAM indicate: 1) High device yield, forming-free operation, reduced operating voltage, excellent scalability (to dimensions < 40 nm in 1D-1R architectures without scarifying the device performance, such as the retention of multilevel states and endurance reliability) and good device

stability; 2) Pulsed programming in the 50 ns-regime and low reverse current with large rectification ratio to meet low-energy consumption criteria (> $10^6$  for high-conductance states and negative-bias current) for integrated 1D-1R nano-pillar architectures; and 3) wide programming resistance dynamic range (potentially up to  $10^8$ ), multi-level states, and excellent reliability. However, the resistive switching mechanisms in  $SiO_x$  are not well understood and use as an electronic synaptic device has not previously been demonstrated.

#### 1.5 OUTLINE

This research work aims at exploring the possibility of SiO<sub>x</sub> layer as potential resistive switching material and developing emerging memory device and architectures for next generation nonvolatile memory applications. SiO<sub>x</sub>-based materials are selected here for low-power portable electronics, highly-integrated of compact memory design, and other applications. This research work started from investigating device structures, material compositions and electrical characteristics to realize ReRAM cells with high ON/OFF ratio, low static power consumption, low switching power, and high readout-margin using CMOS compatible SiO<sub>x</sub>-based materials in both metal-insulator-semiconductor (MIS) and metal-insulator-metal (MIM), and one diode - one resistive switching element (1D-1R) architectures. Then the study of modeling of resistive switching mechanism, including temperature effect, pulse response and carrier transport behaviors will be performed, to develop a compact model in energy diagram, trap-level information, dipole polarization in SiO<sub>x</sub> resistive switching layer, even for computer-aided design (CAD) in very-large-scale integration (VLSI) design. An intriguing non-Von Neumann computing architecture, named synapse-based neuromorphic system, will

be demonstrated in SiO<sub>x</sub>-based ReRAM, combining with bio-inspiration and biomimetics process illustrations. The novel applications in the physiology and pathology discussions in reactive oxygen species (ROS) production and regulation processes will be clarified. This work will present the comprehensively investigation of SiO<sub>x</sub>-based resistive switching characteristics, mechanisms, applications for future post-CMOS devices era.

In chapter 2, device structure, materials and electrical controlling for  $SiO_x$ -based ReRAM were investigated. MIS architecture was fabricated with various post-deposition anneal using rapid thermal annealing. Polarity effects of resistive switching characteristics and RESET process were studied. Horizontal and vertical device structure designs, and composition optimization ( $SiO_x$ , x < 2) by sputtering process have been fabricated in MIS architecture. Device characteristics including SET/RESET voltage, high/low resistive state (HRS/LRS), forming process and electrical controlling characterizations with various compliance current limitations and stopped voltage values have been compared. Effect of ambient dependence in  $SiO_x$ -based ReRAM has also been examined.

In chapter 3, to further understanding the resistive switching mechanism for SiO<sub>x</sub>-based ReRAM, edge and bulk device structures has been applied. An unusual backward-scan effect with DC and AC electrical response were studied. The switching behavior of the backward-scan effect is incorporated into Verilog-A simulations to characterize integration strategies for future circuit-level applications. Oxide stoichiometry effects by PECVD process on reversible switching and program window optimization has been fabricated and examined to achieve autoforming process. Different electrode materials have also been applied into SiO<sub>x</sub>-based ReRAM to achieve flexible manufacturing process. Modeling of resistive switching mechanism, including temperature effect, pulse response and carrier transport behaviors will be performed, to develop a compact model

in energy diagram, trap-level information, dipole polarization in  $SiO_x$  resistive switching layer, even for computer-aided design (CAD) in very-large-scale integration (VLSI) design.

In chapter 4, a Si diode (1D) with low reverse-bias current is integrated with a SiO<sub>x</sub>-based memory element (1R) using nano-sphere lithography (NS lithography, or NSL) and deep-Si-etching (DES) to pattern a P<sup>++</sup>/N<sup>+</sup>/N<sup>++</sup> epitaxial Si wafer. Nano pillar type 1R and 1D-1R architectures with NSL forming a self-aligned process have been fabricated with various pillar size down to 40nm, high density, large-scale nano-pillar (NP) array architecture. The nanostructures fabricated using NSL can be well controlled in shape, size, and inter-pillar spacing through direct assembly of polymer nanospheres on the wafer-scale. Performance of 1R and 1D-1R structures are characterized and show that the integrated nano-pillar 1D-1R configuration offers low static-power for suppression of sneak-path issues. The work demonstrated here provides an efficient fabrication process and low reverse-bias current in a SiO<sub>x</sub>-based 1D-1R configuration for potential use in future ultra-large-scale nonvolatile memory applications.

In chapter 5, we realize a device with biological synaptic behaviors by integrating silicon oxide ( $SiO_x$ ) resistive switching memory with Si diodes. Minimal synaptic power consumption due to sneak-path current is achieved and the capability for spike-induced synaptic behaviors is demonstrated, representing critical milestones for the use of  $SiO_2$ —based materials in future neuromorphic computing applications. Biological synaptic behaviors such as long-term potentiation (LTP), long-term depression (LTD) and spike-timing dependent plasticity (STDP) are demonstrated systematically, and represent interesting potential applications for  $SiO_x$ -based resistive switching materials.

In chapter 6, the contribution of this dissertation is summarized and suggestions on future work have been proposed.

# **Chapter 2: Device Structure, Materials and Resistive Switching Behaviors**

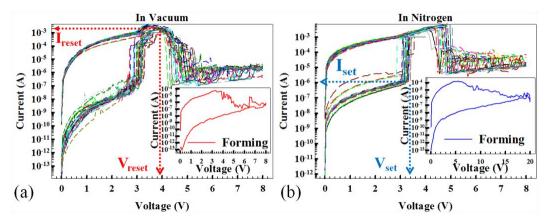

Recent reports by Yao et. al. on SiO<sub>x</sub>-based resistive switching in vacuum indicate that this traditionally passive material can be converted to an active memory material by external electrical activation [43, 44]. Although many resistive switching mechanisms have been reported for various materials, the exact switching mechanisms in SiO<sub>x</sub>-based materials have yet to be identified and may be different than traditional materials [45, 46]. Therefore, characterizing the polarity dependence of device switching is a top priority for the non-polar, SiO<sub>x</sub>-based resistive switching memory. Specifically, analyzing and understanding device RESET switching parameters will help develop a resistive switching model. Here, SiO<sub>x</sub>-based resistive switching memory is realized by fabricating a tantalum nitride (TaN)/SiO<sub>2</sub>/heavily doped n-type (n<sup>++</sup>) Si-substrate structure. Device switching characteristics and stability were investigated with and without a post-deposition anneal (PDA). The polarity dependence of switching characteristics suggests that the switching region is located at the cathode side, potentially due to the asymmetrical thermal-dissipation structure of the TaN/SiO<sub>2</sub>/n<sup>++</sup> Si device. In addition, the oxygen content effect in SiO<sub>x</sub>-based ReRAM has been investigated by controlling the oxygen flow during reactive sputter deposition. It has been found that device yield, switching characteristics and stability are improved for oxygenrich devices. The effects of SiO<sub>x</sub> thickness, device area, and multilevel operation by controlling compliance current and stopped voltage values suggest that the switching region is located at the interface and is localized rather than uniformly throughout the bulk SiO<sub>x</sub> layer. One of the key phenomena: the sensitivity to oxygen in SiO<sub>x</sub>-based ReRAM has also been investigated by controlling the ambient gas pressure and monitoring resistive switching characteristics. Operating stability measurements in

vacuum, nitrogen and oxygen-nitrogen ambients show that SiO<sub>x</sub>-based ReRAM is sensitive to oxygen partial pressure, where resistive switching is temporarily disabled. A subsequent vacuum recovery process restores normal functionality. The statistical distribution of electrical parameters in the oxygen-induced device failures can be described using bi-modal Monte Carlo simulations and additional failure analysis. For reliability issue, data retention tests in the high-resistance state (HRS) and low-resistance state (LRS) for over 10<sup>4</sup> sec confirm the nonvolatile nature of the device. Testing several different device structures and ambient effect enable development of a possible resistive switching model to aid characterizing SiO<sub>x</sub>-based devices for use in future ReRAM applications.

The SiO<sub>x</sub>-based devices were fabricated on n<sup>++</sup> (100) Si (1-7×10<sup>19</sup> cm<sup>-3</sup>) substrate as bottom electrode with resistivity of 0.001-0.005 ohm-cm. Surface native oxide was removed by 1% dilute HF. A various thickness of SiO<sub>x</sub> layer (10 nm, 30 nm, 45 nm, and 60 nm) was deposited by magnetron sputtering of silicon target in Ar and O<sub>2</sub> ambient at 200 °C with different O<sub>2</sub> flow rate during deposition (denoted as "1, 5, 10, 15-sccm samples"), followed by 5 min PDA at 500°C in O<sub>2</sub> (denoted as "w/ annealed sample"). The top electrode, 200 nm-thick TaN, was sputtered onto the SiO<sub>x</sub> film and patterned in a square (various device sizes). Control samples without PDA (denoted as "w/o annealed sample") were also prepared using the same process. CF<sub>4</sub>-based plasma chemistry was used to etch TaN and CHF<sub>3</sub>/O<sub>2</sub> was used to etch the SiO<sub>2</sub> layer. I-V characteristics were measured using an Agilent B1500A semiconductor device analyzer in vacuum ambient (<1×10<sup>-4</sup> mbar) or N<sub>2</sub> purge (1 atm). "SET Current/RESET Current (I<sub>set</sub>)/(I<sub>reset</sub>)" and "SET Voltage/RESET Voltage (V<sub>set</sub>)/(V<sub>reset</sub>)" are defined as the values of absolute current and voltage measured at the beginning of resistance switching from HRS/LRS to

LRS/HRS, respectively. The definition of the "LRS Current" HRS Current" is the measured current in the LRS/HRS at 0.2 V bias magnitude.

#### 2.1. POST-DEPOSITION ANNEAL (PDA) AND POLARITY EFFECTS [47]

Figure 2.1 shows I-V characteristics of 30 switching cycles for a sample (structure: 40 nm thickness SiO<sub>x</sub> and a square of 540 µm edge length, as shown in inset of Figure 2.1) with PDA. Voltage was applied to the top electrode and the bottom electrode was grounded. Before switching cycle measurements, an electroforming process is required, where leakage current fluctuations are observed with increasing bias, as shown in the right inset of Figure 2.1. Forming voltage and the corresponding forming current are typically about 14 V and 1 µA, respectively, which implies that the electroforming process is related to soft breakdown rather than permanent, hard-breakdown. The memory cell can then be operated as a reversible switch by an external bias. After electroforming, resistive switching phenomena are observed by sweeping the voltage from 0 V to positive or negative values (7 V or -7 V). At a voltage defined as  $V_{\text{reset}}$ , the current begins to decrease from a LRS and, in some memory cells, gradually reaches a HRS. However, in some cells, the decrease in current from LRS to HRS occurs rapidly over a small voltage range. In all devices, absolute current increases suddenly at V<sub>set</sub> when using either positive or negative voltage sweeps (4 V or -4 V), and the device transitions to a LRS. In addition, the absolute RESET voltage is always larger than the absolute SET voltage, which is a dramatic and unique difference as compared to unipolar or non-polar resistive switching devices based on other materials.

The electrical characteristics of the SiO<sub>x</sub>-based device, specifically the electrical stability of the memory window, could be improved by introducing a PDA into the

fabrication process, as shown in Figure 2.2 (a) and (b). By comparing the LRS and HRS current for samples with and without PDA, enhanced stability of the HRS current is observed in the samples with PDA. Furthermore, a memory window (LRS/HRS current) of at least one order of magnitude could be maintained without degradation after 30 switching cycles for both sweep polarities. Larger HRS current was measured in the sample without PDA for a negative reset sweep as compared to a positive reset sweep (-/-represents a negative SET process and a negative RESET process), but, no HRS current dependence was observed as a function of SET polarity, as shown in Figure 2.2 (b). This implies that, for devices electroformed with positive polarity, the negative RESET process may be less effective than the positive RESET process; in other words, when using positive RESET polarity, the device is programmed to a HRS with higher resistance as compared to using negative RESET polarity.

In order to further investigate the observed polarity effect and its impact on RESET capability, the statistical mean values of the RESET switching parameters were extracted from the 30-cycle test for samples w/ and w/o PDA, as shown in Figure 2.3 (a). For the mean, absolute value of RESET voltage, a negative RESET voltage sweep results in larger RESET voltage values as compared to a positive RESET process. On the other hand, the RESET current and RESET power (inset in Figure 2.3 (a)) demonstrate the opposite trend where a negative RESET results in smaller values as compared to the positive RESET process. The polarity of the SET process had no observable effect on RESET switching characteristics. According to previous studies, as a result of the electroforming process, Si nano-filaments are expected to be formed near the device edge. Also, the resistive switching characteristics were independent of electrode material and oxide thickness. Based on recent simulation results, RESET current and power would be expected to provide sufficient Joule-heating to rupture the conductive path. For our

device architecture, the asymmetric reset power characteristics and the sweep polarity effect may result from two possible effects: (1) oxygen-vacancy clustering and (2) asymmetric thermal-mass structures. Oxygen vacancy clustering would be expected to increase the oxygen vacancy concentration near both electrodes, with less concentration near the middle due to oxygen-ion absorption (oxygen-sink) by the electrodes and dielectric-breakdown-induced nonstoichiometric oxygen deficiency in SiO<sub>x</sub>. When electrons are injected into the filament from the cathode, they would flow through a filament cross section determined by the vacancy concentration. Since the vacancy concentration is high near the cathode, we expect a thin cross section (vacancy clustering) with high current density. As the current enters the middle region, it must spread-out since there is lower vacancy concentration, and the current density will decrease. Finally, when the electron current reaches the anode, even though there is now increasing vacancy concentration, it remains spread-out and flows with low current density. This scenario would predict that the filament cross section will always be thinner at the cathode due to current spreading near the middle of the filament, and can explain why the device might always switch at the cathode.

The top TaN electrode has lower thermal conductivity ( $< 8.8 \text{ W} \times \text{m}^{-1} \times \text{K}^{-1}$ ) than the bottom  $n^{++}$  Si-substrate (151 W  $\times$  m<sup>-1</sup>  $\times$  K<sup>-1</sup>), leading to an asymmetric thermal-mass structure. Due to the distinct thermal-dissipation difference between TaN and  $n^{++}$  Si, and even for similar electrode materials (for example a polycrystalline silicon/SiO<sub>2</sub>/ $n^{++}$  Si-substrate structure), as shown in Figure 2.3 (b), a positive RESET process requires higher power than a negative RESET, but only if the resistive switching region is located at the cathode-side rather than at the anode-side. As a result, the RESET switching characteristics of SiO<sub>x</sub>-based resistive memory devices may depend on the thermal-dissipation efficiency of the electrodes, and this will affect both the HRS and LRS

current, where the LRS current has larger values for a positive RESET than for a negative RESET, as shown in Figure 2.2. It may be noted that, for both samples, the RESET voltage trend is opposite to that of the RESET current trend, which may result from a constant power consumption during the RESET switching process. This may indicate that the energy required for state transformation from HRS-to-LRS is similar to the energy required for the LRS-to-HRS transition. In this case, the trend in V<sub>reset</sub> with polarity would be opposite to that of the I<sub>reset</sub>, and constant RESET power would be required regardless of sweeping polarity when an asymmetric power dissipation structure is excluded.

Based on the above analyses, a preliminary resistive switching mechanism for SiO<sub>x</sub>-based resistive switching behavior can be proposed. For the LRS, under a higher positive or negative bias (7 V or -7 V), the connected filament would be ruptured or broken, in concept due to current-induced Joule heating, which provides sufficient energy to recover defect trap levels or to oxidize the resistive switching layer near the cathode. As a result, for positive bias sweeping, the resistive switching location would be near the bottom n<sup>++</sup> Si electrode; whereas for negative bias sweeping, the switching location would be near the top TaN electrode due to the oxygen-vacancy clustering effect. For devices in the HRS, the filament would be re-connected regardless of SET voltage polarity. Compared to using a TaN electrode, resistive switching in polycrystalline-silicon electrode devices exhibits less stable operation, potentially due to an inefficient O recovery process, as shown in the inset of Figure 2.3 (b). Although these findings support a thermally-driven RESET process, determination of the detailed resistive switching mechanisms in SiO<sub>x</sub>-based devices will require further investigations including an analysis of device current transport behavior as a function of temperature.

Figure 2.4 shows data retention performance of  $SiO_x$ -based resistive switching memory devices w/ PDA in positive (+/+) and negative (-/-) operating conditions. The readout of LRS and HRS is performed after applying 4 V / 7 V or -4 V / -7 V cycles, and then, after every decade of cycles, LRS and HRS current are measured at + 0.2 V. In Figure 2.4, the retention reliability test for both measurement conditions are stable with a resistance ratio of at least one order of magnitude and no degradation is observed for more than  $10^4$  sec, indicating that a 10-year lifetime might be expected and further confirming the nonvolatile nature of the  $SiO_x$ -based resistive switching device.

Figure 2.1.30 cycles of resistive switching behavior in samples with PDA. Insets show a schematic representation of the TaN/SiO<sub>2</sub>/n<sup>++</sup> Si-substrate structure, and an I-V plot of electroforming data.

Figure 2.2. Polarity dependence (-/- means negative SET/negative RESET) of LRS and HRS distributions across 30 cycles for samples (a) w/ and (b) w/o 5min 500°C PDA in O<sub>2</sub>.

Figure 2.3. (a) Polarity dependence of RESET voltage, RESET current, and RESET power for samples w/ and w/o PDA. (b) Polycrystalline-silicon top electrode device switching characteristics.

Figure 2.4. Retention test at room temperature for samples w/ PDA in positive and negative polarity conditions.

#### 2.2.DEVICE STRUCTURE DESIGNS, COMPOSITION, AND MULTILEVEL OPERATION [48]

Figure 2.5 (a) shows I-V characteristics of the electroforming process for 15-sccm samples. Voltage was applied to the top electrode (60 nm-thick  $SiO_x$  layer and 80  $\mu$ m edge length) and the bottom electrode was grounded without any compliance current limitation. As bias is increased beyond the Fowler-Nordheim tunneling regime, current fluctuations are observed at the forming voltage ( $V_F$ ). Typical values for  $V_F$  and forming current are 20 V and 1  $\mu$ A, respectively. The electroforming process is completed during the backward voltage sweep from 20 V to 0 V, leading to a LRS (Figure 2.5 (a)). Figure 2.5 (b) shows the "number of working devices" and the corresponding relative dielectric constant ( $\varepsilon_T$ ) of the  $SiO_x$  layer, extracted by AC capacitance values, as a function of oxygen flow rate during  $SiO_x$  deposition. The difference in relative dielectric constant values implies that the  $SiO_x$  layer composition is changed by controlling the oxygen flow

rate, with "oxygen-rich" devices being deposited at the higher  $O_2$  flow rates ( $\varepsilon_r$  close to 3.9 indicates stoichiometric  $SiO_2$ ) or "silicon-rich" devices at lower  $O_2$  flow rates ( $\varepsilon_r >$  3.9 indicates non-stoichiometric  $SiO_x$ ). Note that oxygen-rich devices, such as the 10-sccm or 15-sccm samples, show higher device yield than the silicon-rich devices. This may imply that the concentration of defective traps is affected by the stoichiometry of the  $SiO_x$  layer.

Figure 2.6 (a) and (b) show *I-V* characteristics of the 5-sccm and 10-sccm samples for 30 switching cycles, respectively. Voltage was applied to the top electrode while the bottom electrode was ground. The compliance current was limited to 1 mA during each 4 V forward/reverse sweep used to program the device to the LRS. Unipolar switching is observed for both devices. By sweeping the voltage to 8 V, the current begins to decrease at  $V_{reset}$  and the device is programmed into a HRS. On the other hand, the current increases suddenly at V<sub>set</sub> to return a LRS when sweeping the voltage to 4 V. The HRS/LRS resistance ratios for both structures are ~103, which easily satisfies the requirement for sensing. However, the variances of  $V_{set}$ ,  $V_{reset}$ , HRS current and LRS current in the low oxygen-flow samples are larger than the high oxygen-flow variances, as shown in Figure 2.6 (c) and (d). For example, the coefficient of variation (the ratio of the standard deviation to the mean), of  $V_{set}$ ,  $V_{reset}$ , and HRS and LRS current in the 5sccm samples are 6.75 %, 11.7 %, 167 % and 38.7 %, which are much larger than those for the 10-sccm samples (5.62 %, 1.42 %, 113 % and 14.5 %). The relation between switching parameter variance and SiO<sub>x</sub> layer stoichiometry may imply a difference in defect concentration between the two sample types. The variation in defect concentration may be related to a change in the average hopping distance between adjacent traps or the available electron energy levels within the filament, both of which would be expected to affect the filament rupture and formation in a localized region. In addition, the RESET voltage is always larger than the SET voltage, which is unique as compared to other material systems. Metal filament formation, for example a Ta filament resulting from metal atoms diffusing into the  $SiO_x$  layer, can be ruled out in this case since the I-V response maintains the characteristic response for  $SiO_x$  materials.

To further investigate the conduction mechanism of the  $SiO_x$ -based ReRAM, a set of I-V curves for LRS and HRS is plotted as In(I/V) versus square root of voltage (see insets of Figure 2.5 (a) and Figure 2.6 (a), respectively). Ohmic behavior is observed for both LRS and HRS at low bias voltage (Region 1). This suggests that, at low bias, current transport behavior is dominated by thermal generation. On the other hand, at higher bias  $(1 \text{ V} \sim 2 \text{ V})$ , a modified Frenkel-Pool characteristic is observed. Therefore, the observed I-V curves in LRS and HRS are in good agreement with Frenkel-Pool charge transport. The conduction mechanism of Frenkel-Pool is related to trap sites in the insulating material. It is believed that these defective traps come from the non-stoichiometric  $SiO_x$  composition.

The effects of  $SiO_x$  thickness and area on the characteristics of 10-sccm  $SiO_x$ -based ReRAM are shown in Figure 2.7. It is found that smaller-area devices require larger voltage to be electroformed, presumably due to fewer electrically weak points per unit area (top inset of Figure 2.7 (a)). The SET and RESET power (voltage × current) and LRS and HRS current at 0.2 V are independent of device area, illustrating that resistive

switching is an inhomogeneous, filament-type phenomenon (bottom inset in Figure 2.7) (a)). Figure 2.7 (b) shows the electroforming voltage (top inset), SET and RESET powers, and HRS and LRS current (bottom inset) as a function of SiO<sub>x</sub> thickness. The electroforming voltage decreases with SiO<sub>x</sub> thickness until hard breakdown and the irreversible switching occurs at 60 Å thickness. The thinner samples exhibit lower "yield" and less stable switching behavior than thicker samples, suggesting that the effective thickness of the "switchable filament" is approaching the physical thickness of the SiO<sub>x</sub> layer in the thinner samples (100 Å). Kim et. al. have reported that the "switchable filament" in the localized region is about 3-10 nm thick near the interface between insulating layer and anode electrode. It should be noted that other parameters such as SET voltage and RESET voltage are fairly independent of SiO<sub>x</sub> thickness, indicating that device switching occurs in a small segment of the filament rather than throughout the entire bulk SiO<sub>x</sub> layer. The device I-V response remains essentially unchanged for a large range of SiO<sub>2</sub> thicknesses and electrode areas, indicating that SiO<sub>x</sub>based devices most likely follow a filament-type resistive switching characteristic rather than interface-type resistive switching.

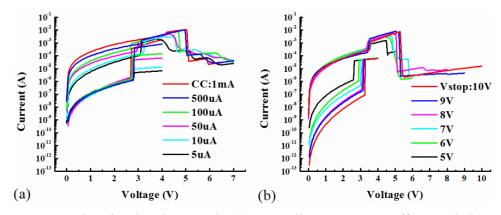

The multilevel effect as a function of compliance current limitation and stopped voltage value has been studied. Figure 2.8 shows the unipolar switching response for the 10-sccm samples under a series of compliance current limitations (i.e. 5  $\mu$ A - 1 mA during the set process with stopped voltage fixed at 7 V) and under a series of stopped voltages (i.e. 5 V - 10 V during the reset process with compliance current fixed at 1 mA). The stopped voltage is defined as the maximum value of sweeping voltage. One

can see that the resistive state of the SiO<sub>x</sub>-based ReRAM can be "tuned" by controlling external electric conditions. A higher compliance current limit results in a higher total switching power to achieve a larger LRS current (Figure 2.8 (a)). This suggests that when a "stronger" filament is formed in the resistive switching material, it can withstand much larger current. In order to achieve a stable and repeatable HRS current level, a series of stopped voltages were investigated for each compliance current condition, and then a specific stopped voltage was selected to achieve a nearly constant current level in the HRS. A larger stopped voltage results in more complete recovery from LRS to HRS. The recovery process is likely related to localized Joule heating, possibly assisted by an increasing electrical field, that alters filament morphology to a degree depending on the level of RESET achieved (as determined by analyzing the stopped voltage effect, Figure 2.8 (b)). Conceptually, filament morphology can be altered to achieve higher resistance by reducing the filament cross sectional area, forming a gap in the filament with larger width, or by reducing the concentration of conductive defects relative to non-conducting defects in a certain "weak point" along the filament. Thus, higher resistive states with smaller HRS current can be programmed by either increasing stopped voltage during RESET or by decreasing compliance current during the SET process.

Figure 2.9 shows summary statistics for RESET voltage (inset), current, and power as a function of compliance current. Most of the RESET process parameters, such as RESET voltage, RESET current and RESET power, increase with compliance current. The increasing trend in these RESET parameters suggest that a higher compliance current limitation results in the formation of more "robust" filaments that

subsequently need larger RESET current or RESET power to rupture the filament. The relation between average RESET current for a series of compliance current limitations is shown in the inset of Figure 2.9 (b). Since the RESET current is consistently higher than the compliance current limit used to program the device, it can be concluded that initiation of the RESET process is based on a thermal-assisted switching mechanism. This is also consistent with the increasing trend of RESET voltage values with compliance current limitation. Therefore, it can be understood that the resistive switching mechanism in the SiO<sub>x</sub>-based device is dependent mainly on applied power (i.e. a comprehensive effect of RESET voltage and RESET current).