Copyright

by

Juan Carlos Rubio

2004

The Dissertation Committee for Juan Carlos Rubio certifies that this is the approved version of the following dissertation:

# Exploring the Potential of a Hierarchical Computing Model for a Commercial Server

| Committee:                   |

|------------------------------|

| Lizy Kurian John, Supervisor |

| Douglas C. Burger            |

| Joydeep Ghosh                |

| Kimberly Keeton              |

| Ann Marie Maynard            |

| Vale N. Patt                 |

# Exploring the Potential of a Hierarchical Computing Model for a Commercial Server

by

Juan Carlos Rubio, B.S.E., M.S.E.

## Dissertation

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

**Doctor of Philosophy**

The University of Texas at Austin

August 2004

To my parents and brothers, for their great support

# Acknowledgments

I am grateful to my advisor, Prof. Lizy John for her guidance and patience during this research. I also appreciate the interest she showed for the wellbeing of her students, and how she shared her perspective about research with all her students.

I thank Doug Burger, Joydeep Ghosh, Kimberly Keeton, Ann Marie Maynard and Yale Patt for being part of my dissertation committee. I feel honored for having a stellar committee and value all the comments they offered. These comments and some of their questions helped me present this dissertation in a clear and objective way.

I want to thank the current and past members of the Laboratory for Computer Architecture for their insight and support during my tenure as a graduate student. Conversations with them were a core component of my learning experience and contributed to more than one idea published during those years. Also, the comments they offered during several talks shaped the content and presentation of this dissertation. Thanks to Melanie, Shirley, Debi and Gem for helping with numerous administrative issues during my time in graduate school.

Thanks also to Tom Keller and Mootaz Elnozahy for their advice. I con-

sider myself very lucky to have met such talented people during my internships at the IBM Austin Research Lab. Presenting my work to them sharpened my presentation skills and helped me focus on the main issues of my research. Their industry perspective helped me understand the tradeoffs present in my research. I also need to thank other researchers from IBM ARL for their comments and help. Particularly Charles Lefurgy, for his collaboration with the data placement techniques, and the team that ported SimOS to the PowerPC platform.

A special mention goes to my parents, who taught me that exploring and thinking are two key components of the learning process. These qualities were extremely helpful while working on this research. During these years of graduate school, their love and support provided a safe harbor which made the experience more manageable.

This work was also possible thanks to Matt Smith, with whom I had many conversations about my research and life. Though Matt is not a computer scientist, his impeccable reasoning sparked more than one idea. Matt also served as my *full time counselor* during the stressful months before the dissertation, for what I am really grateful.

Juan Carlos Rubio

The University of Texas at Austin August 2004

vi

# Exploring the Potential of a Hierarchical Computing Model for a Commercial Server

| Publication No. |  |

|-----------------|--|

|                 |  |

|                 |  |

Juan Carlos Rubio, Ph.D.

The University of Texas at Austin, 2004

Supervisor: Lizy Kurian John

Computer servers are an important driving force in the computer industry. Virtually any major enterprise, such as airlines, banks, or product vendors, depends on servers for such core procedures as selling and distributing products or managing a workforce. Several hardware and software innovations have made their appearance in the context of computer server systems before they were adopted by desktop platforms. The server market has also driven the design of new system architectures. A large fraction of the computer server systems used today are running commercial workloads such as decision support systems (DSS), on-line transaction processing (OLTP) and web servers. Commercial workloads access large amounts of data, imposing heavy demands on the memory and storage sub-systems. As a result, there is a large amount of traffic in I/O and memory buses, which hurts the performance and scalability

of the system.

This dissertation investigates the data movement problem in a computer server system running a commercial workload. To reduce the amount of data transferred between the storage subsystem and the processors, processing units are distributed across the memory/storage hierarchy. A programming model is proposed to facilitate the decomposition of large tasks into simple operations. These operations are distributed through the layers of the hierarchy depending on the affinity of the operation to a particular layer. A task mapping heuristic is proposed for efficient mapping of operations into the various processors. They are executed by the assigned processors, and results are made available to the higher layers, where subsequent operations can be performed.

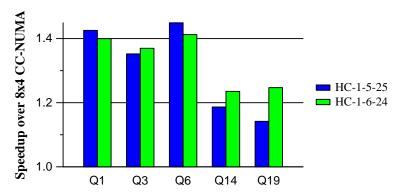

We evaluate the effectiveness of the proposed Hierarchical Computing model using the SimOS full system simulator. On a group of TPC-H like queries, Hierarchical Computing systems achieve speedups of up to 1.22x over comparable 8-processor CC-NUMA systems. We show that the improved execution is due to a reduction of data traffic over the global interconnects. The Hierarchical Computing model also shows good scalability for larger configurations. Comparing an HC system with 31 processors to a 32-processor CC-NUMA system shows speedups between 1.14x and 1.45x.

This dissertation also presents a data placement optimization to be used together with the Hierarchical Computing model or in a conventional CC-NUMA multiprocessor system. This technique uses information about the tasks that run in the system and tries to obtain a good layout to reduce the amount of global data transfers.

The effectiveness of the data placement optimizations is evaluated using a CC-NUMA system with 16 processors, where we obtain speedups of 4 to 13%

over a stripped data layout. Likewise, a Hierarchical Computing system with similar processor, memory and storage resources shows speedups of 15 to 30% over the HC system with a non-optimized layout, and 23 to 56% over the CC-NUMA system with a non-optimized layout.

# Contents

| Ackno   | wledgments                              | V   |

|---------|-----------------------------------------|-----|

| Abstra  | ıct                                     | vii |

| List of | Tables                                  | xi  |

| List of | Figures                                 | xii |

| Chapt   | er 1 Introduction                       | 1   |

| 1.1     | Transaction Processing Systems          | 2   |

| 1.2     | Challenges for Commercial Server Design | 4   |

|         | 1.2.1 Amount of Data Transferred        | 4   |

|         | 1.2.2 Interconnect Contentions          | 6   |

| 1.3     | Hierarchical Computing                  | 6   |

| 1.4     | Thesis Statement                        | 7   |

| 1.5     | Contributions                           | 7   |

| 1.6     | Organization                            | 9   |

| Chapt   | er 2 Related Work                       | 10  |

| 2.1     | System Architectures                    | 10  |

|        | 2.1.1 Database Machines                      |

|--------|----------------------------------------------|

|        | 2.1.2 Tree Organizations                     |

|        | 2.1.3 Intelligent Devices                    |

|        | 2.1.4 Clusters                               |

|        | 2.1.5 Heterogeneous Multiprocessor Systems   |

| 2.2    | Mapping of Operations                        |

| 2.3    | Data Layout                                  |

| 2.4    | Analysis of Commercial Workloads             |

| Chapt  | er 3 Hierarchical Computing                  |

| 3.1    | System Architecture                          |

| 3.2    | Execution Model                              |

| 3.3    | Addressing and Coherence                     |

| 3.4    | Security                                     |

| Chapt  | er 4 Task Mapping                            |

| 4.1    | Introduction                                 |

| 4.2    | Heuristic                                    |

| 4.3    | Cost functions                               |

|        | 4.3.1 Tasks and Operations                   |

|        | 4.3.2 Characteristic Function                |

| Chapte | er 5 Evaluation Methodology                  |

| 5.1    | Baseline System Configurations               |

| ¥      | 5.1.1 Organization                           |

|        | 5.1.2 Software                               |

|        | Hierarchical Computing System Configurations |

|        | 5.2.1 Organization                                        | 50 |

|--------|-----------------------------------------------------------|----|

|        | 5.2.2 Software                                            | 53 |

| 5.3    | Workload                                                  | 57 |

| Chapte | er 6 Results                                              | 64 |

| 6.1    | Hierarchical Computing                                    | 64 |

| 6.2    | Performance of HC systems                                 | 65 |

|        | 6.2.1 Data Transferred                                    | 65 |

|        | 6.2.2 Interconnect Contentions                            | 66 |

|        | 6.2.3 Average Memory Access Latency (AMAT)                | 67 |

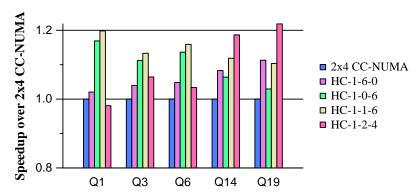

|        | 6.2.4 Speedup of Hierarchical Computing Systems           | 68 |

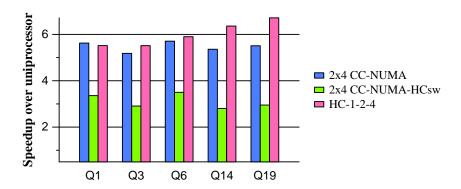

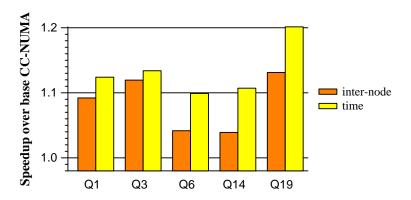

| 6.3    | Performance of an HC software-only system                 | 70 |

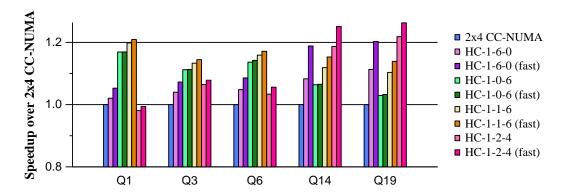

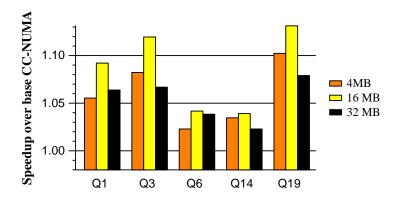

| 6.4    | Processor Sensitivity Analysis                            | 71 |

| 6.5    | Scalability of HC Systems                                 | 72 |

| 6.6    | Task Mapping Heuristic Trade-offs                         | 75 |

| Chapte | er 7 Data Placement Optimization                          | 78 |

| 7.1    | Introduction                                              | 78 |

| 7.2    | Simulated Annealing                                       | 79 |

| 7.3    | Data Placement                                            | 82 |

|        | 7.3.1 Solution State                                      | 82 |

|        | 7.3.2 Objective Function                                  | 83 |

|        | 7.3.3 Temperature Schedule for Data Placement             | 84 |

| 7.4    | Evaluation Methodology                                    | 85 |

| 7.5    | Results                                                   | 85 |

|        | 7.5.1 Data Placement on a Hierarchical Computing System . | 86 |

|        | 7.5.2 Data Placement on a Conventional CC NUMA System     | 87 |

| 7.5.3 Sensitivity Analysis                             | 87  |

|--------------------------------------------------------|-----|

| Chapter 8 Conclusions and Future Work                  | 91  |

| 8.1 Conclusions                                        | 91  |

| 8.2 Future Work                                        | 94  |

| Appendix A Parameters of Characteristic Time Functions | 97  |

| Bibliography                                           | 100 |

| Index                                                  | 116 |

| Vita                                                   | 118 |

# List of Tables

| 4.1 | Operations studied for the task mapping heuristic                 | 41 |

|-----|-------------------------------------------------------------------|----|

| 4.2 | Characteristics of the database tables for the cost function mea- |    |

|     | surements                                                         | 43 |

| 4.3 | Configuration of the system used to estimate the cost functions   | 43 |

| 5.1 | Configuration of the base systems                                 | 48 |

| 5.2 | Communication latencies for the CC-NUMA configurations            | 49 |

| 5.3 | Configuration of the processors in the HC configurations          | 54 |

| 5.4 | Dimensions of the benchmark tables                                | 58 |

| 5.5 | Description of benchmark queries                                  | 59 |

| 6.1 | Performance of the task mapping heuristic                         | 75 |

| A.1 | Parameters for table scan #1                                      | 98 |

| A.2 | Parameters for table scan #2                                      | 98 |

| A.3 | Parameters for table scan #3                                      | 98 |

| A.4 | Parameters for table scan #4                                      | 99 |

| A.5 | Parameters for index scan #1                                      | 99 |

| A.6 | Parameters for index scan #2                                      | 99 |

# List of Figures

| 1.1 | A conventional multi-tier system architecture                               | 3  |

|-----|-----------------------------------------------------------------------------|----|

| 1.2 | Data transferred for a group of DSS queries                                 | 5  |

| 1.3 | Classification of the data transferred in the $2\mathrm{x}4$ CC-NUMA system | 5  |

| 1.4 | Bus contentions for a group of DSS queries                                  | 6  |

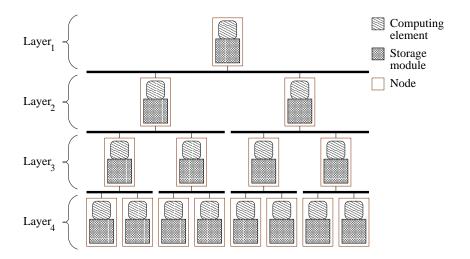

| 3.1 | A generalized view of a Hierarchical Computing System                       | 25 |

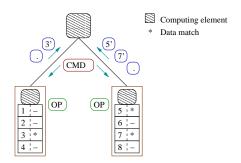

| 3.2 | Execution of an operation in the Hierarchical Computing model               | 27 |

| 3.3 | Individual Primitive                                                        | 30 |

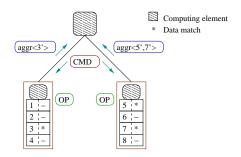

| 3.4 | Aggregate Primitive                                                         | 31 |

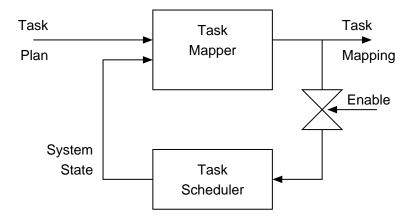

| 4.1 | Representation of the task mapping module as a feedback system              | 36 |

| 4.2 | Representation of a sample task for the task mapping heuristic              | 37 |

| 4.3 | Representation of a sample system for the task mapping heuristic            | 38 |

| 4.4 | Task mapping algorithm                                                      | 39 |

| 4.5 | Representation of a task map                                                | 40 |

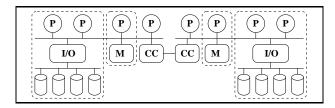

| 5.1 | Diagram of 2x4 CC-NUMA configuration                                        | 49 |

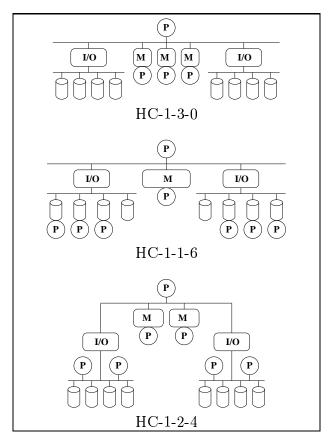

| 5.2 | Hierarchical computing configurations                                       | 53 |

| 5.3 | Distribution of tasks for the HC software on a CC-NUMA system               | 54 |

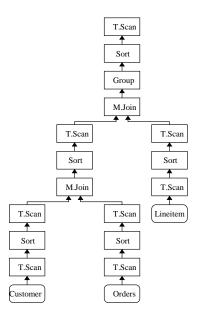

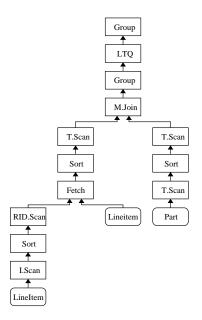

| 5.4 | Execution plan for Query 1                                                  | 60 |

|     |                                                                             |    |

| 5.5 | Execution plan for Query 3                                      | 60 |

|-----|-----------------------------------------------------------------|----|

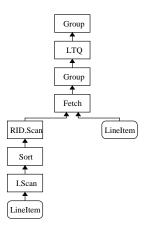

| 5.6 | Execution plan for Query 6                                      | 61 |

| 5.7 | Execution plan for Query 14                                     | 62 |

| 5.8 | Execution plan for Query 19                                     | 63 |

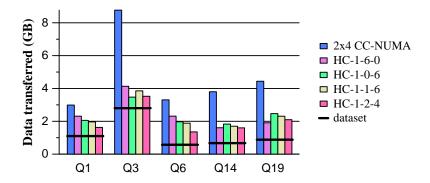

| 6.1 | Amount of data transferred over the global interconnect         | 66 |

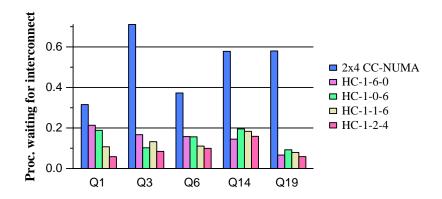

| 6.2 | Average number of processors that are waiting for a global in-  |    |

|     | terconnect every cycle                                          | 67 |

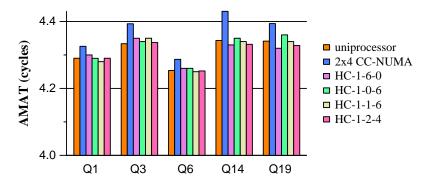

| 6.3 | Average memory access time                                      | 68 |

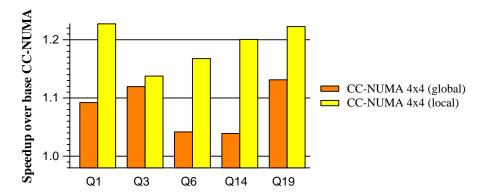

| 6.4 | Speedups of hierarchical computing systems over base shared     |    |

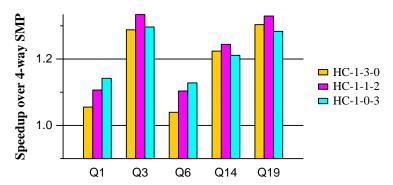

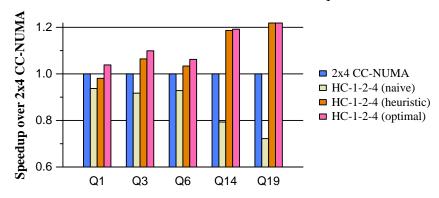

|     | memory multiprocessor system                                    | 69 |

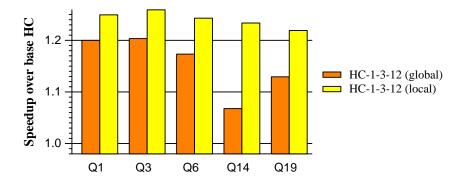

| 6.5 | Speedups of a software implementation of a hierarchical com-    |    |

|     | puting system                                                   | 71 |

| 6.6 | Speedups of hierarchical computing systems with fast processors | 73 |

| 6.7 | Speedups of large hierarchical computing systems over base mul- |    |

|     | tiprocessor system                                              | 73 |

| 6.8 | Speedups of small hierarchical computing systems over base      |    |

|     | shared memory multiprocessor system                             | 74 |

| 6.9 | Advantage of using the Task Mapping Heuristic                   | 76 |

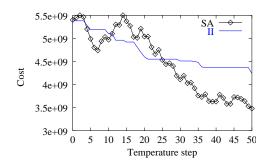

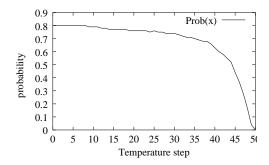

| 7.1 | Simulated annealing algorithm                                   | 80 |

| 7.2 | Cost function for the simulated annealing and the iterative im- |    |

|     | provement algorithms                                            | 81 |

| 7.3 | Uphill acceptance probability                                   | 81 |

| 7.4 | Sample data partition graph                                     | 84 |

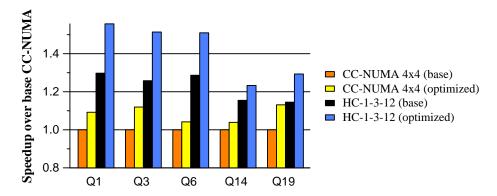

| 7.5 | Data placement optimization on a Hierarchical Computing system  | 86 |

| 7.6  | Performance of the data placement optimization on a CC-NUMA   |    |

|------|---------------------------------------------------------------|----|

|      | system                                                        | 87 |

| 7.7  | Performance comparison of the data placement optimization for |    |

|      | HC and CC-NUMA systems                                        | 88 |

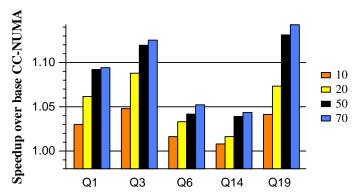

| 7.8  | Impact of the number of steps over the simulated annealing    |    |

|      | process in the data placement optimization                    | 88 |

| 7.9  | Impact of the chunk size over the simulated annealing process |    |

|      | in the data placement optimization                            | 89 |

| 7.10 | Performance of different objective functions in the simulated |    |

|      | annealing process in the static data placement                | 90 |

# Chapter 1

## Introduction

The server market is the driving factor for many technological advancements in the computer industry. This is true for the memory and disk sectors, and particularly true for the microprocessor sector. The server market also fosters the design of new system architectures, as in the case of symmetric multiprocessor systems, which were initially used for servers and have recently been adopted in high-end desktop systems.

A few years back, the server market was dominated mainly by systems running technical workloads. But during the last two decades, it has changed to power a large portion of commercial operations [83]. According to this study, commercial applications accounted for approximately 80% of the computer server market back in 1995. The same study expected an additional 15% annual growth in the high-end server market until the year 2000. Overall computer sales decreased after the "dot-com burst". But recently, the popularity of commercial applications has contributed to a new increase in servers sales worldwide [65, 50].

Commercial applications such as on-line transaction processing (OLTP)

and business decision support systems (DSS) are driving the development of powerful server systems. OLTP systems are used to handle tasks required during the routine functioning of a business (e.g., a client buys products; the managers check the inventory or adjust the price of an item). On the other hand, DSS systems are used to generate composite information based on the data gathered by a business, which usually comes from an OLTP system (e.g., find most popular product within a given demographic bracket, estimate net profit of all sales in the last three months).

Although both workloads fit within the category of transaction processing, they have many differences. While OLTP operations usually have datasets on the order of kilobytes or megabytes, DSS operations usually access megabytes or hundreds of megabytes of data. Recent literature suggests that DSS systems will be accessing terabytes in the near future [97]. OLTP operations are of short duration, taking milliseconds to complete, whereas DSS operations take minutes. The number of concurrent operations in an OLTP system is on the order of thousands, while DSS systems normally have less than a hundred concurrent operations. OLTP systems constantly modify the data stored in the databases (e.g., enter a sale, note the delivery of a package). DSS systems, on the other hand, use mostly read operations during their execution.

## 1.1 Transaction Processing Systems

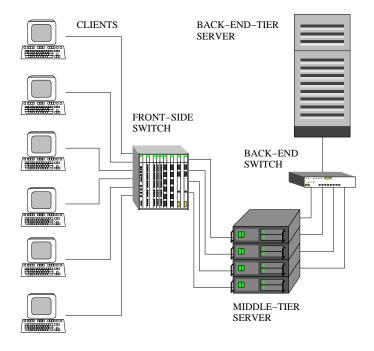

Transaction processing systems are typically implemented using a multitier architecture, as shown in Figure 1.1. This figure also shows how clients on the left are connected to an intermediate or *middle-tier* server through a switched network. The function of the middle-tier server is to act as a filter and

Figure 1.1: A conventional multi-tier system architecture used in a transaction processing system.

reject those requests presented by the clients that are incorrectly generated. It also enforces the security in the system and serves as a parser, transforming requests formulated in one language domain (e.g., HTML) to another (e.g., SQL).

The final component of the system is the back-end-tier, which is the focus of this research. This server is the one that manipulates the primary data of the commercial operation (e.g., it keeps the list of clients, the orders they place, prices of items, and their quantities in the warehouses). As such, the back-end-tier has complete control over a large portion of the data, which is normally local to it and accessed using a Relational Database Manager System (RDBMS or commonly DBMS). Implementations of this server include symmetric multiprocessor systems (SMP) as well as cluster servers.

## 1.2 Challenges for Commercial Server Design

In terms of their execution, commercial workloads are different from technical workloads and present more vigorous demands on the memory and storage sub-systems [57, 7]. In fact, research analyzing commercial workloads indicates that systems spend a significant fraction of the execution time waiting for I/O devices to access the data [32, 33]. Once the data is brought to main memory, the processor uses a substantial amount of the remaining execution time to handle memory accesses [4].

#### 1.2.1 Amount of Data Transferred

One reason for this imbalance between computation and data access is entrenched in the principles of traditional memory hierarchies, where data moves from the storage sub-system to main memory, and from there to the CPU, before it can be processed. Although we have become accustomed to this execution model, which works well for technical and some other applications, it is far from optimal for a commercial workload.

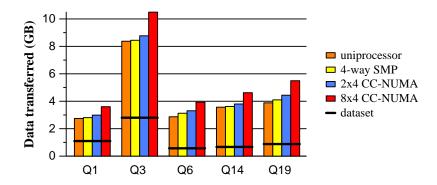

Many modern servers are shared memory multiprocessors (SMP) [19, 35], or clusters of SMP nodes [72, 27, 16]. Commercial applications running on these platforms transfer a large amount of data from storage to the CPU over the global interconnect. We observe that caches cannot hold the entire dataset, and queries that require multiple passes often end up retrieving the same data multiple times. Figure 1.2 illustrates this for a group of TPC-H like queries [92]. These queries will be discussed in detail in Chapter 5, but one can observe the enormous amount of data transferred, which can be more than 4 times the dataset size.

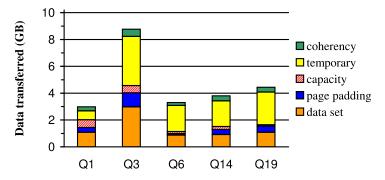

Figure 1.3 shows more details about the data transferred in the 2x4

Figure 1.2: Amount of data transferred between the processors and memory while executing a group of DSS queries. The dataset line marks the size of the dataset. The workload and configuration of the systems are described in Chapter 5.

CC-NUMA configuration. The dataset component represents the first time data is accessed. Since accesses are done at the granularity of a page, page padding indicates the additional bytes appended to the desired data. Capacity represents the accesses done by the processor to data that has already been in the caches. Software writes temporary data back to memory (and frequently to disk), in anticipation that it will be used again, but not immediately. Finally, coherence is the data used by the multiprocessor system to maintain a consistent view of memory. As this figure shows, a large amount of the data

Figure 1.3: Classification of the data transferred between the processors and memory in the 2x4 CC-NUMA system

is transferred because the memory/storage hierarchy cannot hold all the data used by the workload (capacity and temporary results).

#### 1.2.2 Interconnect Contentions

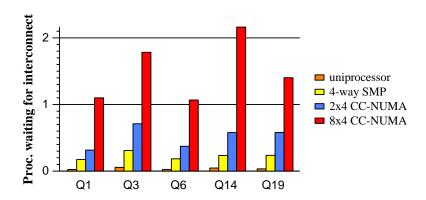

Also, depending on the configuration of the interconnect, a significant number of cycles is spent by the processors in bus contention. This is particularly important for most enterprise servers. Figure 1.4 shows that the average number of processors waiting for the bus increases dramatically with system size. Moving data between storage and computing elements creates a bottleneck. Clusters improve scalability, but do not solve the basic problems of data transport.

Figure 1.4: Average number of processors waiting for the bus. The workload and configuration of the systems are described in Chapter 5.

## 1.3 Hierarchical Computing

This dissertation presents the Hierarchical Computing model (HC) as a solution to the problems presented above. The HC model promotes the use of local data whenever possible. To accomplish this, computing is distributed across a computer system's memory/storage hierarchy. Processors are integrated together with the disk and memory controllers. Then, as a server handles a task, operations are distributed across these processors, which can operate on the data close to them. Their results can then be used by other processors to complete the assigned task.

#### 1.4 Thesis Statement

Placing processors across the memory/storage hierarchy can reduce the amount of data transferred over the global interconnect. This reduces contentions and significantly improves system performance.

#### 1.5 Contributions

The Hierarchical Computing model presented in this dissertation makes several contributions in the form of a hardware and software framework that can be used to run a commercial workload. The following list summarizes the contributions:

#### • Hierarchical Computing model

- We conducted an analysis of the different phases of a DSS workload. The key observation is that a well-tuned computer system running a DSS workload transfers between 2 to 4 times the required data. Furthermore, most of this data has been already accessed during the life of the query.

- This dissertation presents the design of a computer system that places processors across the memory/storage hierarchy. It describes the communication mechanisms between the processors in the system, including the handling of signals and management of buffers.

- We also propose an execution model for this new system architecture. This model is based on a decomposition of a task into a group of simpler operations. The operations are then assigned to different processors across the system. The dissertation also includes guidelines to provide a programming model suited for the workload.

- The potential of the HC system for a decision support system workload is then evaluated using full system simulation. The DSS workload is based on a group of queries from the TPC-H benchmark, which runs on top of IBM DB2.

#### Task mapping

- To quickly map the operations of a complex task (e.g.,database query) over the HC system, we develop a task mapping heuristic.

This heuristic shows good results for the studied decision support system workload.

- A methodology is proposed to easily obtain a group of empirical time equations based on the properties of the data being accessed and the operations performed over it. These time equations allow the task mapping heuristic to estimate the total time of performing a task in an HC system.

#### • Data Placement Optimization

- We demonstrate that a simulated annealing technique [46, 1] may be used to arrive at a good data layout based on information about the workload that will run in the system. This heuristic can be applied to HC and conventional CC-NUMA systems.

## 1.6 Organization

This dissertation is organized as follows. Chapter 2 presents a summary of prior research that is related to this work. Chapter 3 presents the Hierarchical Computing model, explaining the operation of the hardware, communication of the devices and programming model. Chapter 4 presents a technique that allows us to map code to the processing elements in a Hierarchical Computing system. Chapters 5 describes the experiments used to evaluate this idea and then results are presented in Chapter 6. Chapter 7 presents an automatic data placement optimization based on the simulated annealing method. This optimization is applied on both conventional and Hierarchical Computing systems. Chapter 8 concludes the dissertation by highlighting significant results and areas for possible future research.

# Chapter 2

## Related Work

The following sections present prior literature that is closely related to this research. This chapter has been split into four sections: System Architectures, Mapping of Operations, Data Placement and Analysis of Commercial Workloads.

## 2.1 System Architectures

The Hierarchical Computing system we investigate in this dissertation uses a hardware-software approach that allows it to reduce the amount of data transferred globally by the system. This section presents architectures that address the same problem or that result in similar hardware implementations.

#### 2.1.1 Database Machines

During the 1970s, computer scientists studying database applications proposed specially designed machines to handle the increasing gap in the performance between primary and secondary storage [31, 63]. Known as *Database Machines*, these systems incorporated specialized components (e.g., processors per-disk, per-track, and per-head, and associative memories) in order to

facilitate the access of data. These components allowed the system to efficiently access data from secondary storage or perform common operations over this data (e.g., join, sort). Unfortunately, their high degree of specialization sharply limited interest among the larger architecture and software communities. In addition, the use of non-commodity hardware made database machines prohibitively expensive, and the systems never came into widespread use.

DIRECT [21, 22] is a multiprocessor database machine designed around a MIMD architecture. The use of multiple instruction streams allows it to exploit inter-query concurrency, while the use of multiple data streams permits it to exploit intra-query concurrency. The machine is designed around a matrix interconnect, which permits any of the processors (PDP/11) to access a group of CCD modules <sup>1</sup>. In a way, the architecture of DIRECT is similar to that of a large scale SMP system, except that permanent storage and coherence were handled by the host processor.

Recursive machines were popular as a way to simplify the design of a computer system. In this approach, a simple flexible module is designed and used extensively throughout the system. One example, the DDM1 machine [18], is especially relevant to this work. It used data driven nets as its machine language, which is similar to the HC programming model described in Section 3.2. These nets could represent large amounts of concurrency and pipelining, as the modules in the multiprocessor system were completely asynchronous.

<sup>&</sup>lt;sup>1</sup>Charge-Coupled Device (CCD): MOS device made arranged in such a way that the electric charge output of one cell charges an adjacent one. They were used as pseudo-associative memory during 1970-1980. Today they are used as light sensors in digital photography.

#### 2.1.2 Tree Organizations

The X-tree machine [20, 71] developed at UC Berkeley is one of the key examples of Tree machines of the late 70s. This machine is another recursive architecture, formed by a group of modular components called *X-nodes*. Each X-node has a processor, some memory and a routing interconnect. The X-nodes are structured as a balanced binary tree, where communication between the nodes is done using messages.

Harris, et al. [30] also explore the design of a computer system that follows a tree organization. Each node has a processor and some amount of memory (DRAM). This organization is selected as it allows an extra order of magnitude in the number of processors before communication problems affect the system. Implementing interrupts (except for resetting the nodes) was seen as detrimental to the performance of the system. So in contrast with the X-tree machine, the communication between the nodes is controlled directly by the processors. They explore the use of this system to find solutions to the traveling salesperson problem and checker move selection. One of the criticisms of tree architectures during this period was that the interconnect at the top was not capable of providing enough bandwidth to the processors. However, the authors found that the processors at the root are not used as often as the leaf processors, reducing the impact of the bandwidth problem.

The aforementioned tree machines never got into mainstream computer design, and current server designers usually do not think of a tree architecture as a suitable topology for a commercial server.

#### 2.1.3 Intelligent Devices

Intelligent memories have targeted regular numeric applications [53, 23, 68], and recent projects are starting to look at their use in non-regular applications [66, 40, 28, 55]. Also several research groups have focused on the use of intelligent disks [43, 2, 74, 59].

Dynamic Associative Access Memory (DAAM) [51, 53] puts small processing elements (not a processor) near the sense amplifiers of a DRAM chip. The main use of these chips is to massively search data stored in them. The initial design of a 1 Mbit DRAM (organized as  $256 \times 4096$ ) expands the 10 transistors of the sense amplifiers to 24. Their calculations indicate that a large array could access a 1 TB database and search it in 60  $\mu s$ . Later work [52] reveals that the search operations could be done simultaneously with the refresh cycle of the memory cells.

Computational RAM (C-RAM) [23] adds bit-serial SIMD processors to the sense amplifiers of an otherwise conventional DRAM chip. This is designed to exploit the internal bandwidth of the memory chip. As the study suggests, the memory bandwidth at the sense amplifiers is up to 3 orders of magnitude higher than that at the processor level. The authors also fabricated an 8 Kbit prototype and showed the performance for regular applications (DSP).

The EXECUBE architecture [47, 48, 85] is based on a processor-inmemory (PIM) chip built using a 0.8  $\mu m$  trench cell CMOS DRAM technology. The chip has 4 Mbit DRAM and 100 K logic gates, organized as 8 processing elements (PE) connected as a 3-D hypercube (connections to 4 of its neighbors). Each PE has one 25 MHz CPU, two 32 Kx9 DRAM macros and an additional external link, which permits the chips to be connected as a massively parallel system without any glue logic. The PEs can operate as a MIMD computer (fetching instructions from its own memory), or in SIMD mode (when using an external broadcast bus).

The Intelligent RAM (IRAM) project [68, 69, 70] is probably the best known effort to combine processors and memory. This approach integrates a single processor inside a memory chip built using DRAM fabrication technology. The objective is to increase the available bandwidth and reduce the latency to memory. IRAM's first implementation is a vector processor, which shows the benefit of this idea for regular applications.

The goal of Active Pages is to off-load data manipulation to logic in the memory subsystem [66]. The authors propose an execution model that augments a memory page with a set of functions to operate on that data. Their first conceptualization of the idea was RADram (Reconfigurable Architecture DRAM), which includes reconfigurable logic (as an FPGA<sup>2</sup>). They expect to use an MDL process (Merged DRAM logic), which would result in a 10x slow-down of the logic with respect to the main processor. The second instantiation of Active Pages [67] proposes to replace the FPGA with simple processors by a simplified scalar MIPS R3000 or a VLIW processor. The scalar processor has the lowest power consumption of the three, while the FPGA results in greater speedups. They conclude that the VLIW implementation offers the best of both worlds.

FlexRAM [40, 87] tries to give applications greater flexibility by providing one central processor per chip (P.mem) and several simple processors next to the sense amplifiers (P.array). A P.array can see its memory and the memory of its two neighbors. P.mem can move data within the chip to facilitate certain operations. The system also has an inter-chip network, which allows a

<sup>&</sup>lt;sup>2</sup>Field Programmable Gate Array

P.mem to access any memory location in the system. Their experiments indicate that a system with four FlexRAM chips can run between 4 to 25 times faster than a system with conventional DRAM.

Riedel, et al. [74] mention that current disk drives have very efficient processors in the disk units. They propose a system called Active Disks, which uses processors at the disk units to run application-level code. Their experiments use separate slower computers to emulate Active Disks. The server is a regular computer with directly attached SCSI drives. All computers are connected using an Ethernet switch. Their evaluation for data mining, multimedia and scan operations shows speedups that scale linearly with the number of Active Disks used in the system.

The IDISK project [43] from UC Berkeley proposes to use an additional processor at the disk unit to perform operations on behalf of the main application. The disk units are connected using point-to-point serial interconnects, resulting in a flat cluster of disks. This resembles a computer cluster, except the clustering is performed at the disk level rather than at the computer level. Keeton et al. [42] indicates that using an IDISK system could be beneficial for a DSS workload.

There is another Active Disk project [2] based at the University of Maryland. The goal of this project is to move certain computations to the disk in order to off-load the host processor. Under this model, the host processor is used to coordinate the disks, schedule operations to them and combine the results. The authors propose a stream-based programming model that uploads user-defined *disklets* to the processors on disk. A disklet operates on a stream initiated on its behalf by the host processor. To guarantee the reliability and security of the system, certain safeguards are imposed on the disklets (i.e., they

cannot allocate memory or initiate I/O). Disklets can skip portions of a stream by interacting with the layer of the operating system that runs in the disk. Experiments on a group of basic database operations show good scalability for systems with up to 32 Active Disk modules. They also show that the communication between the disks is crucial for operations that combine data (join, sort and cube) [95].

#### 2.1.4 Clusters

For scalable applications, *clusters* [72] are a popular architecture. Most clusters that exist now have flat interconnection networks. At best, the interconnection network is hierarchical (e.g., the hierarchical switch in the Compaq AlphaServer GS320 system [27, 16]). This organization increases the bandwidth of the system.

Memik, et al. [59] evaluated the performance of smart disk clusters against traditional clusters. Their results indicate that smart disk clusters outperform traditional cluster architectures in most queries.

#### 2.1.5 Heterogeneous Multiprocessor Systems

Researchers have explored heterogeneous multiprocessor systems [60] so an application can select the resources that best fit its needs. The Hierarchical Processors and Memory (HPAM) [8, 9] and the Heterogeneous Distributed Shared-Memory (HDSM) [25] projects from Purdue address the design of these systems. Both projects use traditional parallel applications such as SPLASH-2 [98]. The HPAM project explores the design of a computer system with a small number of fast processing resources and a large number of relatively inexpensive processors. The system is hierarchical in a conceptual sense, as processors may be viewed as comprising a hierarchy according to speed/cost.

This work was followed by the HDSM project, where the nodes of an otherwise conventional cc-NUMA system are populated with different numbers and types of processors and memories. It uses a conventional interconnect, so any processor can access any memory location regardless of the node.

## 2.2 Mapping of Operations

Lee et al. [49] proposes an automatic code partitioning heuristic that is applied to a a FlexRAM system. The authors analyze the loop structure of programs from the SPEC CPU benchmark and classify them according to the affinity of the loops to either the host processor or the FlexRAM modules. The affinity is estimated using simple cost functions based on the number of instructions and iterations of the loops, and the frequency of the processors.

Manegold et al. [56] presents models to estimate the cost of performing database operations in a system with a general hierarchical memory subsystem. They analyze the memory access patterns of the queries and develop generic cost functions for each pattern. Their model uses information about the latency and bandwidth of the memory components combined with the requirements of the access pattern to estimate the cost of the query.

Rădulescu et al. [75] presents the Critical Path Reduction heuristic (CPR). CPR is used to schedule an application over a distributed system to exploit its task and data parallelism. They identify *M-tasks* and *S-tasks*; the former being a task that can run in multiple processors, while the latter runs in a single processor. The iterative heuristic then identifies the critical path and allocates additional processors to the M-task that will most likely shorten it.

### 2.3 Data Layout

Combinatorial optimizations, including simulated annealing, have been used in the context of VLSI and Electronic Design Automation to solve placement and route problems [78, 79]. In the field of computer architecture, the uses of combinatorial optimizations have been limited mostly to genetic algorithms used to explore the design space of microprocessor components [82, 24, 5]. Swanson et al. recently conjectured that SA could be used to assist instruction scheduling and placement [86]. Simulated annealing has also been used to cluster data when performing pattern recognition [39], and to produce optimized query plans [38].

Work by Tsangaris et al. looked at stochastic techniques for clustering objects [93]. Additional work shows that randomizing algorithms produce the best clustering, but the cost involved is too high for their application [94].

A study by McErlean et al. shows that simulated annealing can also be used to cluster data in a database [58]. Their work used real runs in a database instead of a cost function. Therefore it required many hours to generate a single layout. Our work shows that picking an adequate cost function can produce a layout in less than a second.

Work by Rao et al. uses genetic algorithms to find a good partition for a group of queries in a shared-nothing database cluster [73]. A partition is a description of the logical group of nodes (nodegroup) over which tables and indices are evenly allocated. Our approach is similar to theirs if we think of a single node of our CC-NUMA system as a nodegroup. However, we opt for a finer grained approach that allows small chunks of data to be allocated unevenly across the different disks of the system instead of evenly splitting tables across each nodegroup. Additionally, their work considers partitioning

as a part of query optimization. We look at data reorganization as a way to optimize the layout further for an existing set of query plans.

## 2.4 Analysis of Commercial Workloads

A significant amount of research has been done to identify the characteristics of commercial workloads. Research by Maynard, et al. [57] was among the first to appear in the literature. They used an RS/6000 system with an in-order processor to evaluate the cache behavior of an OLTP workload (TPC-A [88], TPC-C [90], and Laddis [81], among others). These results were compared with those of a group of proprietary technical applications and two benchmarks from the SPEC92 suite [80]. They found that the thread switching activity associated with commercial applications tend to diminish the temporal locality of instructions streams. Also, different threads tend to require different data, which applies additional pressure over the cache hierarchy.

Barroso, et al. [7] analyzed the memory performance of SMP systems running OLTP (TPC-B [89]), DSS (TPC-D [91]), and web index (AltaVista) workloads. They found that the processors running the OLTP workload results in a very large CPI (7.0). This CPI is larger than that of commercial systems running the real TPC-C benchmark. They also observed that increasing the size of the Bcache (board cache – equivalent to an L3 cache shared by all processors) helps the OLTP workload as it reduces the latency of instruction fetches. The DSS workload, on the other hand, has a lower CPI (1.5 to 1.9), and behaves well with the existing Scache (second level cache). The web index behaves similarly to the DSS workload. They also claim that "operating system activity and I/O latencies do not dominate the behavior of well-tuned

database workloads". We believe this statement is inaccurate as their system was designed to be memory resident <sup>3</sup>. Another problem with this study is their claim that TPC-B has a similar behavior to TPC-C. Later, the same group of researchers compares the behavior of the TPC-B and TPC-C benchmarks in their experimental infrastructure [84]. This work acknowledges that the CPI of a TPC-B workload is higher. It also indicated that the time spent in kernel functions can be high as 20%.

Keeton, et al. [41, 44] analyzed the performance of a 4-way SMP system running the TPC-C benchmark. They showed that the operating system accounts for 20% of the execution time. The overall average CPI of the benchmark was 3.39, which was skewed by the 6.48 cycles of the OS-CPI. They also indicate that the branch predictor in the processor does not work as efficiently as with the SPEC CPU benchmark. This might be due to the high contextswitch rates and use of non-looping branches of the workload. Likewise, the workload does not appear to benefit from the the out-of-order components of the processor, showing a majority of cycles where no instructions are decoded or retired. The authors suggested that a narrower issue width might be sufficient for the workload. It would be interesting to investigate the use of processors capable of holding more in-flight instructions (e.g., Pentium 4). Finally, they observe that a modest bus utilization (over 60%) can hamper the memory subsystem by increasing the average memory access latency (from 97 cycles to 111 cycles in a 4-way SMP system). In that situation, increasing the size of the L2 caches reduces the bus utilization, thus increasing the scalability of the system.

Ailamaki, et al. [4] analyzes the behavior of fundamental database op-

<sup>&</sup>lt;sup>3</sup>The largest database was 900 MB and they used a system with 2 GB of memory.

erations using four commercial database management systems (DBMS). They use simpler select and join operations, which are customized to resemble OLTP and DSS workloads. The workload is strictly memory resident. Their work disagrees with previous work, as they mention that the L2 cache has a bigger impact on data accesses, and instruction fetches are affected by the L1 cache. This discrepancy is caused by the design of the experiments, as the L1 cache is only 16 KB, and the workload only considers a single OLTP operation at a time.

Cao, et al. [12] studies a 4-way SMP system running the TPC-D benchmark. They observe that the average CPI (1.27) is comparable to that of SPEC CPU applications. They found that branch prediction works very well for this workload, in contrast with an OLTP workload. And similar to Ailamaki et al., they found that the small L1 cache constitutes a bottleneck for the instruction fetching <sup>4</sup>. They also show that different queries of the benchmark can have very large L2 cache misses (35.2%), and that the percentage of L2 misses is related to the cycles the processor is stalled. However, they do not show a relationship between these stalls and the CPI of the queries.

Hankins, et al. [29] presents a methodology to scale an OLTP workload so the behavior of the processor resembles that of a deployed system. They observe that an OLTP workload can operate in 3 regions: CPU bound (with a few warehouses, which results in a small dataset), balanced, and I/O bound. They study the number of instructions per transaction (IPX) and the CPI of the system as they scale the number of warehouses (size of the database). By monitoring those 2 factors, it is possible to designate a *pivot point*, where CPI

<sup>&</sup>lt;sup>4</sup>Ailamaki, et al. [4] uses a Pentium II Xeon with a 16 KB L1 instruction cache, whereas Cao, et al. [12] uses a Pentium Pro with an 8 KB L1 instruction cache.

and IPX cease to increase linearly. Their main observation is that if the scaled system is larger than the pivoting point, the database is representative of a full OLTP system. Other results agree with previous work.

## Chapter 3

# **Hierarchical Computing**

We present the Hierarchical Computing (HC) model as a solution to the data transfer problem present in conventional systems. The HC model distributes processing elements across the memory/storage hierarchy. To take advantage of the parallelism present in the tasks that run in the server, the system decomposes tasks into simpler operations. These operations are then distributed and executed by the different layers of the hierarchy depending on the affinity of the task to a particular layer. By performing some operations closer to where data resides, an HC system reduces the amount of data transferred over the global interconnect. This can effectively reduce contention problems.

This chapter presents the system architecture, execution and programming model of an HC system. The next chapter describes the technique used to map the operations of a task across the processors.

## 3.1 System Architecture

A traditional system requires all processing to be performed at the top of the memory/storage hierarchy. As explained in Chapter 1, Figure 1.2

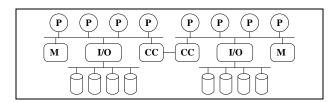

showed that commercial servers transfer large amounts of data over the system interconnect, while Figure 1.4 showed that a large number of processor cycles are lost because of contentions in the interconnect. It is the goal of the HC model to encourage the use of local accesses whenever possible by distributing computations across the memory/storage hierarchy. Processors are located in memory and disk, close to the location of the data. They are provided with a local bus to operate on the data, and communicate among themselves using a hierarchical interconnect (i.e., a tree). This interconnect matches the initial topology of the memory/storage hierarchy, which reduces the amount of additional communication links in the system.

Figure 3.1 shows the topology of a hierarchical computing system based on a binary tree interconnect. In this figure and across the rest of the dissertation, the term *storage* is used to indicate any device that can contain data; it applies both to permanent storage (e.g., disks, flash RAM, magnetic RAM) and to volatile storage (e.g., DRAM, SRAM). A node is formed by coupling the computing element (a single processor in this example) to the memory/storage module, or by using an integrated module like the ones mentioned in Section 2.1.3. We define a *layer* as the group of nodes that sit at the same logical distance from the top of the hierarchy. If all the nodes in a layer have the same hardware characteristics, we refer to the layer as homogeneous. A symmetric topology consists entirely of homogeneous layers. Through the rest of the dissertation we will be referring to a symmetric topology. The notation  $Layer_L$  is used to represent a given layer L, where  $Layer_1$  is the topmost layer. To identify individual nodes within a layer we use the notation  $Layer_L\{N\}$ , where N is the list of nodes.

Data accesses within the node are considered local data accesses and

Figure 3.1: A generalized view of a hierarchical computing system (HC-1-2-4-8). For simplicity, the diagram shows each node with only one computing element, one storage module, and either 2 children nodes or none, but other configurations are also possible. We also present the interconnection between a parent node and its children nodes as a bus, but it could also be a more complex network.

usually result in a significantly lower access latency, as they bypass the global interconnect circuitry. Local accesses also provide a higher bandwidth as it is usually easier to provide high speed or wider buses for local modules [68].

An HC system can use commodity processing and storage components, which could be placed in the same package. The intelligence required in the different levels of the hierarchy could also be realized using intelligent memory modules investigated in recent research [53, 23, 68, 66, 40, 28, 55] and intelligent or active disks [43, 2, 74, 59]. Computing capability can be realized in the network or switches using network processors [37, 64], micro-controllers, or similar chips embedded in the switch/bus interface.

#### 3.2 Execution Model

For presentation purposes, this section describes the execution model in terms of a decision support workload and the database software that runs in a server system. This execution model could be applied to other workloads and platforms as well.

The database server runs in one or more of the processors that sit at the top layer of the hierarchy. Once the database server receives a request to execute a query, it prepares an execution plan. This execution plan describes the operations that will be applied to the tables of the database to execute the query. The first step is the decomposition of the query into simpler operations [17, 10]. Then the order of execution of the operations is decided (query scheduling). This includes verifying that accesses to a table currently being modified are deferred until the completion of pending operations. Once the operations are scheduled, they are ready to be executed. It is at this point that an HC system differs from a conventional system. Whereas a conventional system will execute each one of the operations in the main processors, an HC system will run some of them in the processors across the storage hierarchy. At this point, the HC system takes the query schedule provided by the database software and maps each of the operations to a particular processor in the system. Chapter 4 presents the details of this operation.

Figure 3.2 shows three layers of a sample HC system. Data is partitioned to allow a high level of distributed computation. For illustration purposes, we will assume that all requested data resides in the intermediate layer ( $Layer_2\{1,2\}$  of Figure 3.2). A processor in the top layer ( $Layer_1\{1\}$ ) starts the distribution of the operation by allocating a response buffer. This buffer is used to hold any data generated by the lower level. After the buffer

is set, it issues a command (CMD) to one or more nodes in the intermediate layer  $(Layer_2)$ . Commands include enough information to allow nodes of the intermediate layers to perform the sub-queries. A command is really an index to one of the data handling routines that have been previously loaded into that layer by the database. After the command is sent, the node is free to operate on other tasks while it waits for data.

Figure 3.2: Execution of an operation in the Hierarchical Computing model.

Once a node receives a command from a higher layer, it checks the data in its storage module. If the data is not present within local storage, the process repeats downward. In effect, it performs a preorder traversal starting at the top of the hierarchy. The node prepares a command and sends it to the next layer, forwarding all responses to the higher layer. When a leaf node does not contain the requested data, a null response is sent.

To facilitate the communication of the data, the hardware provides basic

control flow signals. These help the top layer handle the amount of data that might result from a delegated operation.

All commands are tagged by the originating node with a unique identifier. The responding node also tags the response based on the tag of the initial command and the ID of the node. This technique is similar to the tokens used in traditional dataflow machines [6] and active messages [96]. The system can initiate operations in different nodes, allowing multiple independent operations to be performed in parallel. A node can receive multiple commands, and can execute them when the required data is available. Because there is no requirement that results return in order, they are distinguished by their tags. This mode of operation allows for a pipelined out-of-order execution similar to the one seen in modern microprocessors. To reduce the overhead of processing responses, we also tag a command with the *ID* of the layer initiating it.

Finally, the model implements a namespace locator in the form of a software-managed table allocation index. This index permits a processor to quickly locate data within its local storage. It is also used to determine if data is not present, thus avoiding a lengthy traversal of the data.

Minimizing the movement of data is accomplished by performing computations in the processing element closest to the data whenever possible. However, some operations may be performed at a different layer. This occurs when an operation benefits significantly from a more powerful computing element (e.g., a high frequency dynamically scheduled processor) or requires resources not available in the computing element (e.g., floating point units), or for combining partial answers supplied by other nodes. The idea that different operations benefit from different types of resources has been explored for traditional parallel processing workloads such as SPLASH [60, 8, 9, 25]. We

further discuss this and other related work in Section 2.1. Chapter 4 discusses in more details the issue of mapping the code in a Hierarchical Computing system.

As described earlier, the database manager loads ahead of time a set of data handling routines that will be used by the different nodes across the hierarchy. These routines are selected according to their use in modern transaction processing workloads. The current interface provides an implementation of the most common operations:

- Selection: locates records within a single table that match a particular criterion

- Join: merges the results of two or more selections or tables.

- Sort query results by some criterion

- Insert, remove, and update records from an existing table

To handle the different SQL operations and data manipulation algorithms, we use two types of operation primitives: *individual* and *aggregate*. These operations are based on the execution model presented in this section, and differ in the way the results are generated by the lower node and interpreted by the upper.

#### • Individual Primitive

During the execution of the operation, the lower layer informs the upper layer of every single result. It effectively acts as an unbuffered noncombining filter. An example is searching a range of data for a string. The semantics allow the operation to return on the first event triggered or to continue operating until it reaches the end of the region. Figure 3.3 shows the flow of commands and results for this primitive.

Figure 3.3: Individual Primitive.

#### • Aggregate Primitive

For this primitive, the lower layer accesses its associated data and finds those elements matching a particular criteria. However, it does not send all these results to the upper layer. Instead it sends an aggregate result once all the data has been analyzed. In the context of parallel processing, this operation is also known as data reduction. The most common aggregate functions in commercial workloads are: sum, count, average, max, and min. The average function is a special case, as it returns a pair of values, sum and count. The upper layer computes average from all returned sum and count values. Figure 3.4 shows the flow of commands and results for the aggregate primitive.

## 3.3 Addressing and Coherence

To manipulate the data in the system, we use a global virtual address space. That is, all processors share the same mapping of virtual to physical addresses. However, certain processors might be able to access only physical

Figure 3.4: Aggregate Primitive.

addresses that are local to their node. We say that the processors in the node own that range of addresses. As we will soon explain, this policy facilitates the maintenance of coherence in the system.

To support this model, the operating system (OS) uses a global set of address translation tables. For explanation purposes we continue presenting the case of processors in memory, but this can be applied to processors in disk as well. The OS must initialize the memory-processor modules before they can be used. The sequence of steps required to initialize a processor in memory is as follows:

- (i) The OS allocates a continuous region of memory on the range owned by that device.

- (ii) Next it prepares an address translation table for the portions of the virtual address space that physically reside in the memory local to the device.

- (iii) It then pins down those pages so they are not evicted from memory.

- (iv) The memory processor is instructed to use this address translation table.

(v) A semaphore is used to indicate that the global address space should not be modified for that range

If a change to the address translation tables is required, the OS must guarantee that the memory-processor modules affected are informed of the change. Currently, this process requires the OS to monitor the state of the address range semaphore. This is performed as follows:

- (i) The OS access the semaphore for that range

- (ii) If the semaphore is not set, the OS updates the corresponding tables.

- (iii) If the semaphore is set, it verifies the processors that own that range are not halted.

- (iv) If the processors are not halted, it waits for them to complete their work before updating the tables.

- (v) If the processors are halted, it resets the processors, update the corresponding tables and re-initialize the processors.

In this system, coherence is maintained using a hardware/software approach. The basic premise is that processors must not share data simultaneously if at least one is expected to modify it. Additionally, before allowing a processor to use the data, the system must guarantee that the data is current. If the routine running in one processor accesses data, and the system instructs another processor to regain write access of that data, the system flushes the caches to make the copy on memory current. While the second processor accesses the memory pages in write mode no other processors are allowed to read from it.

### 3.4 Security

Commercial applications require privilege control for the data they store. In the HC system, this is allowed by having meta data that is kept in the same storage module as the data. This meta data contains information that assists the database in determining the ownership of a group of rows. Commands are then sent with an identifier that indicates the originator of the query. The code that runs in the data location is then responsible for checking the privileges of the originator over the data. To guarantee that this ownership is respected, the data handling routines are provided by the database server.

## Chapter 4

# Task Mapping

#### 4.1 Introduction

The previous chapter presented the Hierarchical Computing (HC) architecture and its execution model. In an HC system, the operations that comprise a task (in this discussion, a database query) are executed in processors across the memory hierarchy. Some processors are closer to the data, which makes them prime candidates to execute an operation that uses that particular data. Additionally, processors might have different computation or storage capabilities, which can also affect the performance of the operation. The goal of the task mapping module in a HC system is to determine in which nodes operations should be executed.

This problem is closely related to a multiprocessor task scheduler [62, 15, 99, 77]. For almost all situations, the scheduling problem has been shown to be NP-complete [11]. But in most situations, it is possible to analyze the system and obtain an approximated solution (i.e., a schedule for which its cost approximates the cost of the lowest possible cost) [76]. For a Hierarchical

Computing system, the task is particularly challenging as the nodes may have different characteristics regarding CPU performance, data capacity, communication channels and data available. It is then necessary to determine an adequate mechanism to map the operations onto the system. A heuristic is used to obtain a good solution. The goal of this heuristic is to execute the operation in the processor that executes it most efficiently without hurting the performance of the whole task.

The workload used in this research consists of a group of queries executed by a database manager. Commonly, queries are represented using a high level language like SQL. It is the job of the database manager to parse the query and break it into simpler operations – process known as query decomposition. The next step is query scheduling, where the order of the operations is decided. The output of this stage is the query execution plan (QEP), which constitutes the input for the heuristic.

#### 4.2 Heuristic

A common scenario for an HC system involves the simultaneous processing of operations from multiple tasks (e.g., queries). At some point, an incoming task is presented to the system in the form of a task plan (e.g., query execution plan). The task mapper is then responsible for planning a good mapping for this task plan. To arrive at this mapping, it uses information about the incoming task, static information about the system, and dynamic information about active and pending operations. Figure 4.1 shows this task mapping mechanism as a feedback system. The task scheduler provides information about the current operations and the scheduled operations. The enable gate confirms that the task mapping is permissible and introduces it to the

task queue.

Figure 4.1: Representation of the task mapping module as a feedback system.

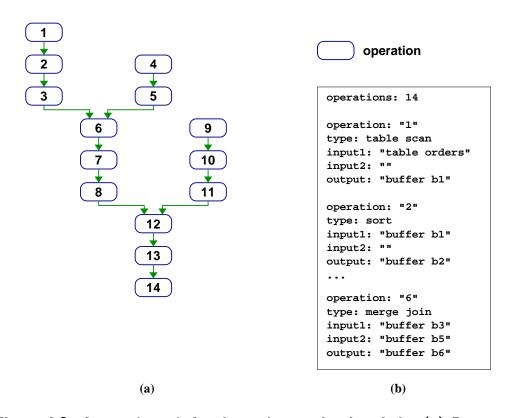

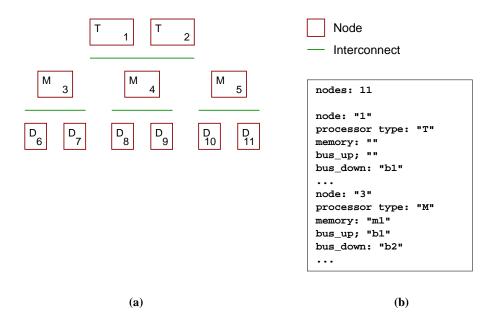

A divide and conquer heuristic is used to map operations across the nodes of the system. The input to the heuristic is a task. The task is represented as a directed graph of N operations and their requirements. Figure 4.2 shows the representation of a sample task. The system also uses an architectural description of a system to define the parameters of the mapping module. This description is specified as a list of M nodes and their properties. The requirements for an operation are specified as properties of the data that would be accessed and a characteristic function. Figure 4.3 shows the description of a sample system. For the workload we are studying, the properties of the data include number of rows the operation accesses and the width of the row. The characteristic function is an expression used to estimate the time required to perform the operation in a particular node of the system. The details of this function are presented in Section 4.3.2.

The goal of this heuristic is to reduce the total execution time of the task. To accomplish this, it tries to reduce the execution time for the critical

Figure 4.2: A sample task for the task mapping heuristic. (a) Representation of a task as directed graph of operations. (b) Formal description of the operations in a task.

Figure 4.3: A sample system for the task mapping heuristic: (a) graphical representation, and (b) formal description.

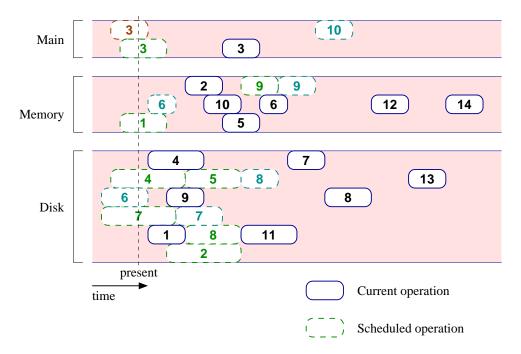

path without drastically affecting the latency of the other paths. Figure 4.4 shows the basic algorithm used to map the task across the nodes of the system.

Figure 4.5 shows a graphical representation of a map that reduces the time for the sample task (Figure 4.2) on the sample HC system (Figure 4.3). The task map is divided in 3 horizontal regions; one for each level of the hierarchy of the system. The width of the region depends on the number of processors on the layer. Operations are represented by bubbles and numbered according to the query execution plan. Operations shown using a dotted line belong to previously scheduled tasks, thus preventing the current operations from using the corresponding resources. Time is represented along the x-axis, with a dotted line to represent the present time. Operations to the left of the line have already completed.

- (i) For each operation, estimate cost of running in every node

- (ii) Divide the task graph into straight segments. Estimate minimum and median cost of each segment

- (iii) Starting at ready nodes, propagate median cost of segment

- When reaching intersections, select the segment with greatest cost to determine critical path

- (iv) Map operations in the critical path to the processor resulting in the earliest completion

- (v) Remove critical path from graph and repeat (from 3) for remaining operations

Figure 4.4: Task mapping algorithm.

#### 4.3 Cost functions

This section explains the process used to obtain the cost functions for the operations that constitute a task. Our approach uses an operational database system where sample operations are performed. The results from the experiment are then used to obtain empirical expressions for the time in terms of parameters of the workload.

#### 4.3.1 Tasks and Operations

The task mapping module in a Hierarchical Computing system receives the query plan as input. The individual operations that form the query plan are the operations considered by the task mapping module. Table 4.1 shows the operations considered by this task mapping heuristic. These operations are the most common components found in the queries of a DSS workload.

Figure 4.5: Representation of a sample task map. The dotted bubbles are the operations currently running in the system, the regular bubbles are the spots that would be assigned to the new task.

Table 4.1: Operations studied for the task mapping heuristic.

| Operations | Implementation       |  |

|------------|----------------------|--|

| table scan | predicate: 1 integer |  |

|            | predicate: 1 string  |  |

|            | predicate: 1 date    |  |

|            | predicate: 2 integer |  |

| index scan | predicate: 1 integer |  |

|            | predicate: 1 string  |  |

|            | predicate: 2 integer |  |

| sort       | quick                |  |

|            | bubble               |  |

| unique     | hash                 |  |

| join       | merge join           |  |

|            | nested loop join     |  |

|            | hash join            |  |

#### 4.3.2 Characteristic Function

To apply the task mapping heuristic, we need to estimate the cost of performing an operation in a given processor of the system. This estimation could be done using an analytical model, where a real operation is analyzed and a cost function is then generated. This process would require us to analyze each function and consider the impact that the configuration of the nodes might have on that operation. But this method is error prone and could potentially result in large error margins.

Instead, we use an empirical analysis of the functions. In this analysis we run a series of operations in a real system and measure their execution time. We then run a series of experiments with the intention of parameterizing the resulting time as a function of: properties of the operation, characteristics of the architecture, and location of the data. These experiments test the following

#### parameters:

- Processor configurations This parameter considers the different types of processors in the HC system. Those explored in this dissertation are main processor (1 GHz), memory processor (500 MHz) and disk processor (250 MHz). In this experiment, the processors have identical cache configurations and differ only in their operating frequencies.

- Datasets This parameter controls table sizes by adjusting the number of rows in the tables. These experiments produce a group of cost functions that are independent of the number of rows. This is explained in more detail below.

- Operations This parameter determines the algorithm used to access the data. The algorithms considered in this work are listed in Table 4.1.

The resulting time function is not a linear combination of the above stated parameters. The presence of caches, TLBs and finite amounts of memory results in a non-linear behavior of the time function as the dataset is changed. To reduce the impact of this variation, I set up five ranges of table sizes determined by the layers of the memory hierarchy. A linear dependence of time on the dataset size can be expected within each range. That is, a single linear expression can be found to represent the time needed to operate on tables that fit within a given range. The full range is not used to avoid hitting boundary conditions. The characteristics of the five ranges are described in Table 4.2. Measurements are performed using three table size within each range: upper limit, lower limit, and the geometric mean of the range.

The three processor configurations correspond to those listed in Table 5.3. Since performing this analysis requires a large number of experiments,

Table 4.2: Characteristics of the database tables for the cost function measurements. The average width of the rows is 100 bytes. The memory page size is set to 8 KB.

| Description            | Number of rows |

|------------------------|----------------|

| Fit in L1 cache        | 50 - 300       |

| Fit in L2 cache        | 700 - 2600     |

| Fit in TLB             | 3500 - 5200    |

| Fit in memory          | 5500 - 6000    |

| Does not fit in memory | 8000 - 12000   |

I chose to use a real computer system instead of software simulations. This approach causes a larger error for the estimated cost function, but is sufficient for the purposes of this study. The configuration of the testing system is listed in Table 4.3. The system has a single processor that runs at 1 GHz, and has an option in the BIOS that can slow it down to 500 MHz. To simulate the 250 MHz processor, a process is set to execute an infinite loop and execute at a 50% duty cycle, thus reducing the efficiency of the processor.

Table 4.3: Configuration of the system used to estimate the cost functions for the task mapping heuristic.

| Processor | 1 GHz                             |

|-----------|-----------------------------------|

|           | 3-way issue                       |

|           | 64 KB L1-D cache                  |

| Memory    | $256~\mathrm{MB},100~\mathrm{ms}$ |

|           | 2 banks                           |

|           | 64-bit, 200 MHz bus               |

| Storage   | 2 disks, 16 GB 10,000 RPM         |

|           | 64-bit, 66 MHz PCI bus            |

|           | 1 Ultra160 SCSI controller        |

The 13 operations used are listed in Table 4.1. The data resulting from

the experiments is then run through a linear regression analysis statistical package to obtain a group of parameterized expressions. For the *table scan*, *index scan*, *sort* and *unique* operations, the expression has the form:

$$t = t_{row \ independent} + t_{row \ dependent} R$$

(4.1)

where R is variable that represents the number of rows in the table.  $t_{row\ independent}$  is a parameter obtained from the linear regression, which does not depend on the number of rows.  $t_{row\ dependent}$  is the second parameter or coefficient obtained from the regression. For the join operations, the expression is:

$$t = t_{row \ independent} + t_{row \ dependent \ outer \ table} R_1 + t_{row \ dependent \ inner \ table} R_2$$

$$(4.2)$$

Here  $R_1$  is the number of rows in the *outer table* (normally the largest). Likewise,  $R_2$  represents the number of rows of the *inner table* (or elements in the hash structure for the hash join).

This analysis is performed for each processor configuration and memory range. Based on the memory ranges shown in Table 4.2, a boolean vector **S** is used to indicate the current memory range. Using this memory ranges allows us to decouple the analysis from a fixed table size. And using a boolean vector simplifies the notation of the expressions. The elements of the vector can be either 0 or 1 depending on the conditional statement shown in Equation 4.3.