Copyright

by

Yu-Wei Lee

2017

# The Dissertation Committee for Yu-Wei Lee Certifies that this is the approved version of the following dissertation:

# TEST AND SECURITY IN A SYSTEM-ON-CHIP ENVIORNMENT

|   | Committee:              |

|---|-------------------------|

| • | Nur Touba, Supervisor   |

| • | David Z. Pan            |

|   | Earl E. Swartzlander Jr |

| • | Lizy K. John            |

|   | Gang Huang              |

# TEST AND SECURITY IN A SYSTEM-ON-CHIP ENVIORNMENT

by

Yu-Wei Lee, B.S.; M.S.;

# **Dissertation**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

**Doctor of Philosophy**

The University of Texas at Austin

May 2017

# **Dedication**

To my parents, my family and my dearest wife.

### Acknowledgements

I would like to thank Prof. Nur Touba, for being my academic supervisor at Graduate school in University of Texas, Austin. There are simply too many things I have learned from him during this journey. Most importantly, I learned how not to settle and always do things the right way. These experiences will not only help me throughout my career, but will also be valuable to every decision I will be making in life.

I thank Prof. Lizy John, Prof. David Pan and Prof. Earl Swartzlander for agreeing to be on my Ph.D. committee and reviewing this dissertation.

I am also grateful to Dr. Gang Huang for being on my committee, providing his indepth advices from the industry perspective.

I would not be where I am now without the support of my family. I want to thank my parents for their support to everything I do. If I am going to have kids, I hope I can be as supportive as you two were to me. I want to thank my sister for her pep talks throughout the years. I hope to remain a good brother you love to hang out with, as well as a cool uncle to your adorable kids.

I am the luckiest man on earth to have my wife with me all the time. She is my ultimate cheerleader and I hope am doing the same for her. This have been an incredible journey, and I cannot wait hear the next movement of our symphony.

### Test and Security in a System-On-Chip Environment

Yu-Wei Lee, Ph.D.

The University of Texas at Austin, 2017

Supervisor: Nur A. Touba

This dissertation outlines new approaches for test and security in a System-on-Chip (SoC) environment. A methodology is proposed for designing a single test access mechanism (TAM) architecture on each die with a "bandwidth adapter" that allows it to be efficiently used for multiple different test data bandwidths in three-dimensional integrated circuits (3D-IC) using through-silicon vias (TSVs). In this way, a single test architecture can be re-used for pre-bond, partial stack, and post-bond testing while minimizing test time across all phases of test. Unlike previous approaches, this methodology does not need multiple TAM architectures or reconfigurable wrappers in order to be efficient when the test data bandwidth changes. In industry, sequential linear decompression is widely used to reduce data and bandwidth requirements. A new scheme using a multiple polynomial linear feedback shift register (LFSR) with rotating polynomial is proposed here to increase encoding flexibility resulting in higher compression ratios. An algorithm is described to assign test cubes to polynomials in a way that enhances encoding efficiency. For hardware security, a new attack strategy against logic obfuscation is described here. It is based on applying brute force iteratively to each logic cone one at a time and is shown to significantly reduce the number of brute force key combinations that need to be tried by an attacker. It is shown that inserting key gates based on MUXes is an effective approach to

increase security against this type of attack. In data security for hardware, existing techniques for computing with encrypted operands are either prohibitively expense (e.g., fully homomorphic encryption) or only work for special cases (e.g., linear circuits). A lightweight scheme implemented at the gate-level is proposed for computing with noise-obfuscated data. By carefully selecting internal locations for noise cancellation in arbitrary logic circuits, the overhead can be greatly minimized. One important application of the proposed scheme is for protecting data inside a computing unit obtained from a third party IP provider where a hidden backdoor access mechanism or hardware Trojan could be maliciously inserted.

# **Table of Contents**

| Table of Contentsviii                                                                                           |   |

|-----------------------------------------------------------------------------------------------------------------|---|

| List of Tablesx                                                                                                 |   |

| List of Figures xi                                                                                              |   |

| 1. Introduction1                                                                                                |   |

| Unified 3D Test Architecture for Variable Test Data Bandwidth Across Pre-Bond Partial Stack, and Post-Bond Test | • |

| 2.1. Proposed Scheme8                                                                                           |   |

| 2.2. Selecting Bandwidth for Each Stage of Test12                                                               |   |

| 2.3. Experimental Results                                                                                       |   |

| 2.4. Conclusions                                                                                                |   |

| 3. Improving Test Compression with Multiple-Polynomial LFSRs20                                                  |   |

| 3.1. Sequential Linear Decompression                                                                            |   |

| 3.2. Proposed Approach25                                                                                        |   |

| 3.3. Assigning Test Cubes to Polynomials through Bipartite Matching30                                           |   |

| 3.4. Experimental Results                                                                                       |   |

| 3.5. Conclusions                                                                                                |   |

| 4. Improving Logic Obfuscation via Logic Cone Analysis                                                          |   |

| 4.1. Brute Force Attack Strategy Based on Logic Cones39                                                         |   |

| 4.2. Effective Key Size for Cone-Based Attack                                                                   |   |

| 4.3. Insertion of Key Gates to Counter Attack                                                                   |   |

| 4.4. Experimental Results                                                                                       |   |

| 4.5. Conclusions                                                                                                |   |

| 5. Computing with Obfuscated Data via Noise Insertion and Cancellation54                                        |   |

| 5.1. Related Work                                                                                               |   |

| 5.2. Problem Definition57                                                                                       |   |

| 5.3. Cancelling Noise In Arbitrary Computations60                                                               |   |

| 5.4. Noise Propagation Path Selection in AIGs | 64 |

|-----------------------------------------------|----|

| 5.5. Experimental Results                     | 66 |

| 5.6. Analysis                                 | 70 |

| 5.7. Conclusions                              | 72 |

| 6. Summary and Future Works                   | 73 |

| References                                    | 75 |

| W7. 00                                        |    |

# **List of Tables**

| Table 1. Example of $time_i(B)$                                                | .14 |

|--------------------------------------------------------------------------------|-----|

| Table 2. 3D Benchmarks                                                         | .15 |

| Table 3. Experimental Result for Non-Flexible Designs                          | .17 |

| Table 4. Experimental Result for Flexible Designs                              | .18 |

| Table 5. Results for Using Proposed Scheme to Encode Test Data                 | .34 |

| Table 6. Comparison of Different MUX Input Selection Strategies in Effective I | Key |

| Size                                                                           | .46 |

| Table 7. Comparison of Different MUX Input Selection Strategies in Terms of    |     |

| Effective Key Size                                                             | .49 |

| Table 8. Comparison of Effective Key Size                                      | .50 |

| Table 9. Results for Inserting Noise Cancelling Gates                          | .68 |

# **List of Figures**

| Figure 1. JTAG Architecture                                                         |

|-------------------------------------------------------------------------------------|

| Figure 2. IEEE 1500 in a SoC of N Cores                                             |

| Figure 3. Input Bandwidth Adapter9                                                  |

| Figure 4. Block Diagram for Using Bandwidth Adapter10                               |

| Figure 5. Unified TAM, Bandwidth Adapter and the Corresponding Test Flow.11         |

| Figure 6. Symbolic Simulation of Sequential Linear Decompression23                  |

| Figure 7. Matrix Representation of Linear Equations24                               |

| Figure 8. Solving Linear Equations                                                  |

| Figure 9. Multiple-polynomial LFSR                                                  |

| Figure 10. Proposed decompression scheme with multiple-polynomial LFSR28            |

| Figure 11. Reducing hardware overhead for primitive polynomial generation by        |

| using MUXes to select between a polynomial and its reciprocal29                     |

| Figure 12. Example of assigning test cubes to polynomials thorough bipartite        |

| matching31                                                                          |

| Figure 13. Assigning test cubes to polynomials considering number of free variables |

| retained33                                                                          |

| Figure 14. Number of Polynomials versus Test Data35                                 |

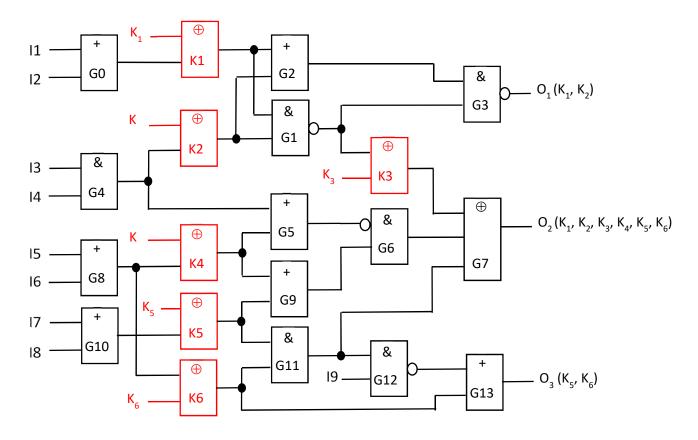

| Figure 15. Example of Circuit with 6 Key Gates Inserted                             |

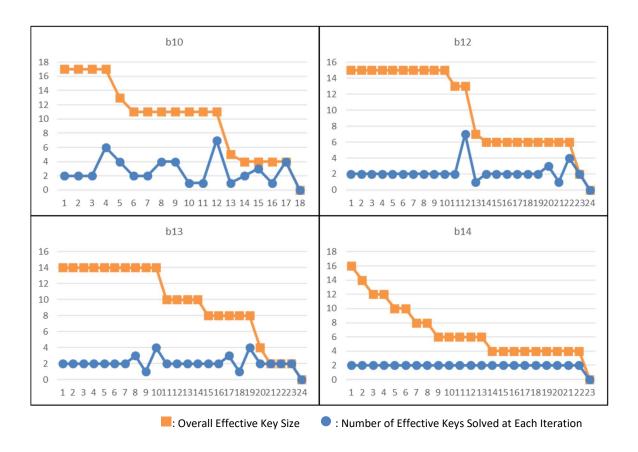

| Figure 16. Analysis of Effective Key Size for Cone Based Attack42                   |

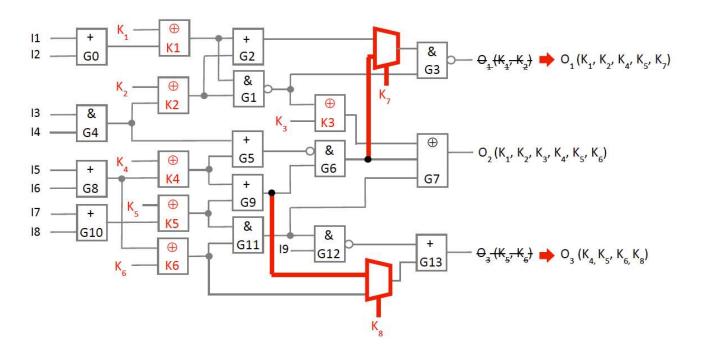

| Figure 17. Example of Circuit with 2 MUX Key Gates Inserted44                       |

| Figure 18. Pseudo Code for MUX Insertion                                            |

| Figure 19. Pseudo Code For Selecting Side Inputs                                    |

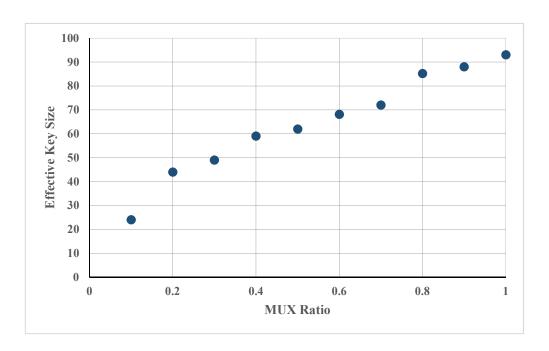

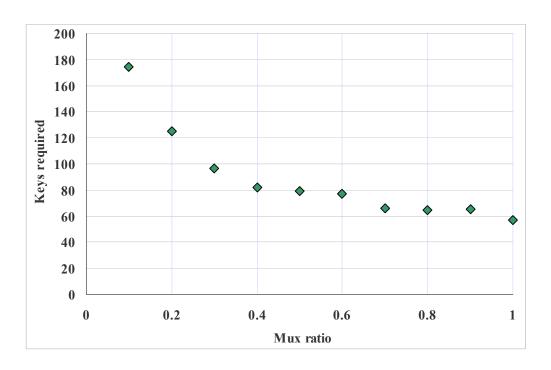

| Figure 20. | Effective Key Size for Cone-Based Attack for Insertion of 100 Keys | in |

|------------|--------------------------------------------------------------------|----|

|            | Circuit b13                                                        | 52 |

| Figure 21. | Number of Keys Inserted to Reach 50 Effective Keys for Cone-Based  | d  |

|            | Attack for Circuit b11                                             | 53 |

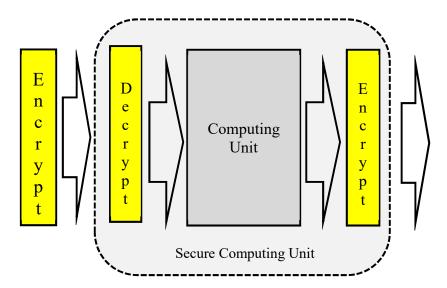

| Figure 22. | Conventional Secure Computing Scheme                               | 54 |

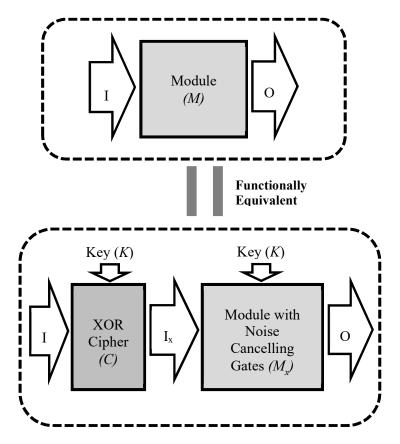

| Figure 23. | Overview of the Proposed Scheme                                    | 58 |

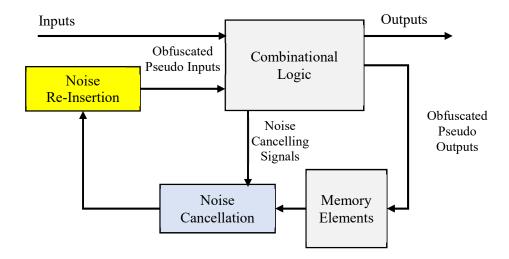

| Figure 24. | Noise Cancelling Scheme for Sequential Logics                      | 60 |

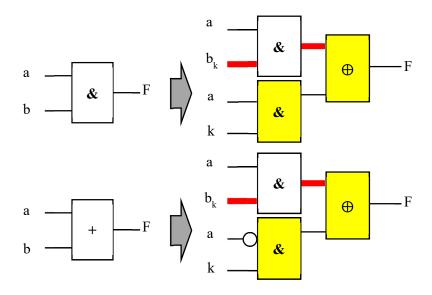

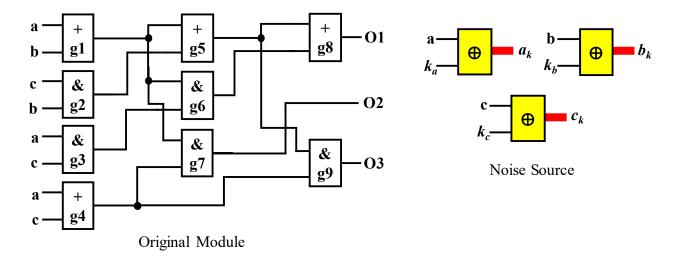

| Figure 25. | Noise Cancelling Gates for AND/OR                                  | 61 |

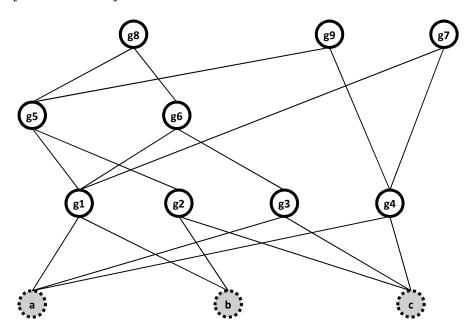

| Figure 27. | AIG of the same module shown in Figure 26.                         | 64 |

| Figure 28. | Example of Selecting Noise Paths in AIG for Module in Figure 26    | 66 |

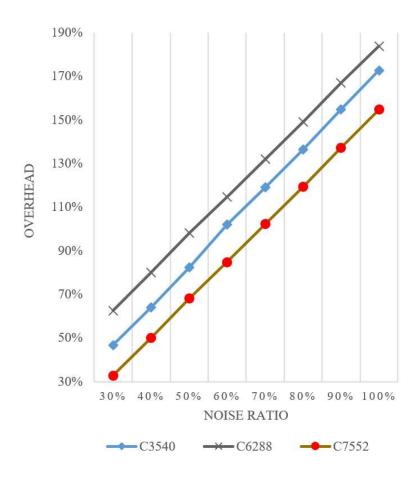

| Figure 29. | Overhead vs. Noise Ratio                                           | 70 |

### 1. Introduction

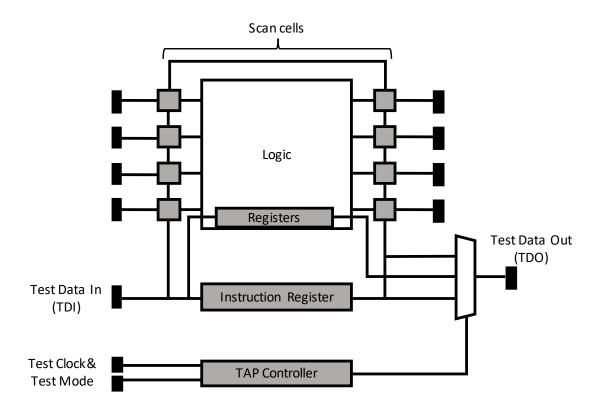

Improvements of IC technology increase the transistor density but also bring more challenges for design, verification, and test. As the scale and capabilities of ICs continue to grow, more effort is needed to ensure logic correctness and integrity. In design-for-test (DFT), scan based design greatly improves circuit testability. Scan chains are formed by connecting storage elements in a design into shift registers in test mode to provide better control and observability. The IEEE 1149.x family, also called Joint Test Action Group (JTAG) standard [IEEE 1149.1-2001], is one of the most widely adopted standards for DFT. Figure 1 presents an example of the JTAG architecture. Basic elements in JTAG include scan cells, test access ports (TAP), TAP controller, and instruction registers for the JTAG controller.

Figure 1. JTAG Architecture

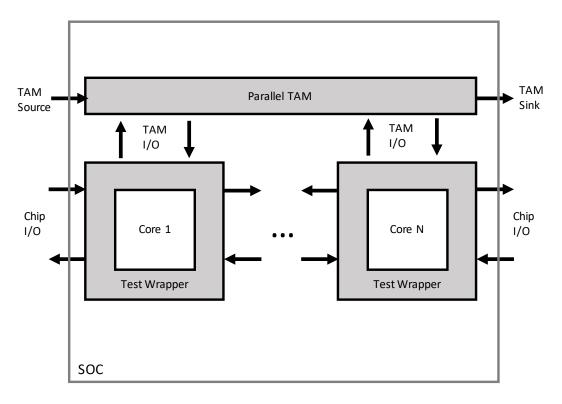

A System-on-Chip (SoC) can be viewed as a collection of multiple cores implementing different applications. Each core can be separately designed and integrated later onto a single piece of silicon. SoCs allows intellectual property (IP) cores to be easily reused and shortens design time for complex applications. DFT for SoCs may be complicated by the fact that each IP core may have different specifications for test. The IEEE 1500 standard was proposed to address the SoC core based test problem [Marinissen 99]. It inherits most of the properties of IEEE 1149.1 with some additional hardware components such as a test wrapper for each core, a single source and sink for test access, and an on chip test-access mechanism (TAM) to connect wrappers to the test controller. Figure 2 shows an example of an IEEE 1500 system in a SoC consisting of *N* cores. Optimizing TAMs is often a challenging problem in DFT since each core in a SoC may have a different specification for test, and the TAM is responsible for control and distribution of test data for each core under test.

Figure 2. IEEE 1500 in a SoC of N Cores

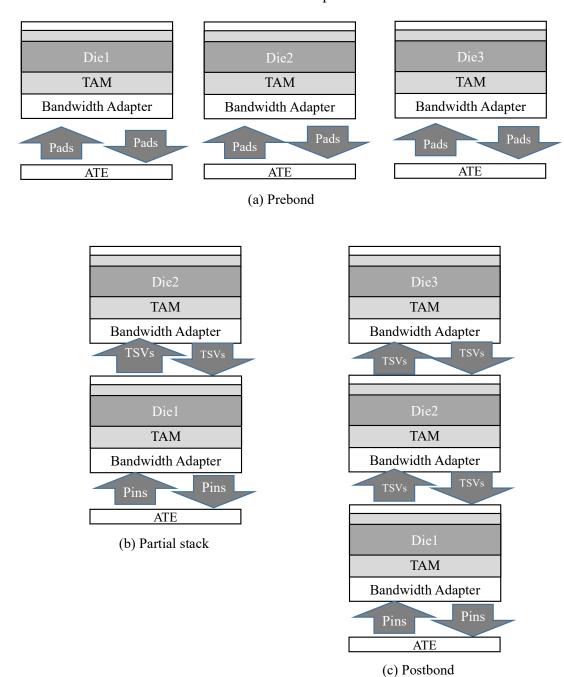

Manufacturing SoCs implemented with three-dimensional integrated circuits (3D-ICs) have become an increasingly used approach that provides technological advantages over traditional 2D design. In a 3D-IC, dies are manufactured individually before stacking. Before stacking, pre-bond testing can be used to screen out defective die and only knowngood die (KGD) are used when constructing the stack. Furthermore, during construction of the stack, additional known-good stack (KGS) testing can be done after each die is added. During each phase of test, the access mechanism and bandwidth requirement may be different. In chapter 2, a methodology is proposed for designing a single TAM architecture on each die with a "bandwidth adapter" that allows it to be efficiently used for multiple different test data bandwidths.

As SoC designs scale, more components are being integrated. Even with more components, test circuitry usually does not scale as quickly as the functional part. This creates challenges for test data compression because each component needs a separate testcubes, but still must sharing the same tester bandwidth. Test data compression is widely used to compress the amount of data stored on the tester. This helps to reduce tester storage requirements and improve test time as less data has to be transferred over the limited test data bandwidth between the tester and chip-under-test. Sequential linear decompression is a highly efficient technique used to reduce tester bandwidth requirement as well as data storage. This approach is based on a linear feedback shift register (LFSR) with multiple locations to inject variables from tester. Test cubes can be encoded by solving a system of linear equations where each equation corresponds to a care bit in the test vector being encoded [Könemann 01], [Krishna 01], [Rajski 04].

One common drawback for conventional LFSR decompression, however, is the encoding flexibility of the test cubes is restricted by the LFSR polynomial. Some test cubes simply are not encodable by some polynomials, but may be encodable by a different polynomial. Encoding flexibility can be greatly increased with a multiple-polynomial LFSR [Hellebrand 95] in which multiple polynomials can be selected to encode different test cubes. In chapter 3, a new data compression scheme based on a rotating multiple

polynomial LFSR is proposed to improve data compression in sequential linear decompression. The implementation eliminates the conventional control bits needed to switch the polynomials, and is made efficient in terms of hardware overhead through exploiting properties of primitive polynomials.

Advancement in DFT improves controllability and observability, but creates concerns that sensitive information about an IC might be exposed. The security concerns for an IC are applicable to both logic and data. IP piracy has become a problem for designers because an unauthorized party may learn and reproduce the design without consent by using reverse engineering. Another problem is that a malicious party may obtain enough knowledge about the design to insert additional circuitry to disrupt or change normal functionality. This kind of malicious circuitry is known as hardware Trojans. Logic obfuscation has been proposed to protect ICs against these attacks [Roy 08, 10], [Chakraborty 09a], [Baumgarten 10], [Rajendran 12, 14]. One approach is to use combinational obfuscation where "key gates" are inserted in a design which have primary inputs that are referred to as "key inputs". The design will only function correctly if the correct key values are used [Roy 08, 10]. In chapter 3, a new form of attack against logic obfuscation through analysis of logic cones is considered. In addition, a way to counter such an attack with MUXes as key gates is described.

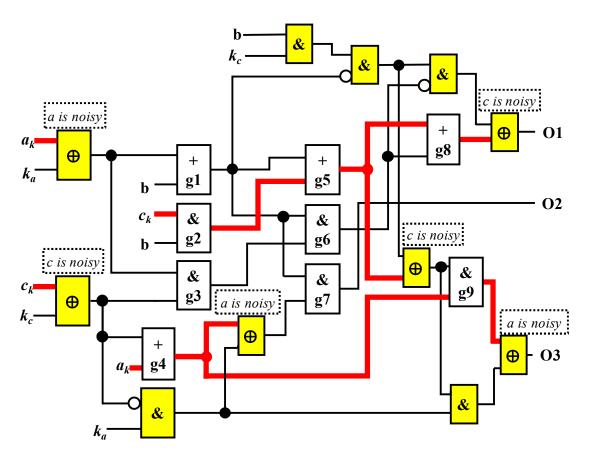

In addition to protecting the hardware, the data stored and processed in the hardware also needs to be protected. This concern is becoming increasingly prominent as more ICs are used for processing critical and personal information. For encryption in software, a groundbreaking scheme called fully homomorphic encryption (FHE) is proposed in [Gentry 09]. FHE allows computing with encrypted data so that an attacker could not obtain the plain text even with the ability to snoop information within the computation hardware. FHE can be implemented in software with very high performance overhead and implementation cost in hardware is unrealistically high. Chapter 4 proposes a lightweight hardware computing scheme where the computation is conducted on obfuscated data. The idea for protecting data in the computing unit is to insert noise in the

input data and cancel it out both partially internally in the computing unit as well as fully at the output of the computing unit. A key idea in the proposed approach is to reduce the complexity of the noise cancellation logic by carefully selecting internal locations to do local noise cancelling. This is done in a way that prevents more than one input per gate from propagating noise thereby avoiding the complexity that arises from reconvergent noise propagation paths. While the proposed methodology does not provide the level of strong encryption that fully homomorphic encryption would provide, it has the advantage of being lightweight, easy to implement, and can be deployed with relatively minimal performance impact. One important application of this approach is for protecting data inside a computing unit obtained from a third party IP provider where a hidden backdoor access mechanism or hardware Trojan could be maliciously inserted. Chapter 5 concludes the dissertation with a summary of the contributions and suggestions for future work.

# 2. Unified 3D Test Architecture for Variable Test Data Bandwidth Across Pre-Bond, Partial Stack, and Post-Bond Test<sup>1</sup>

Three-dimensional integrated circuits (3D-IC) using through-silicon vias (TSVs) are an important new technology that provides a number of significant advantages including increased functional density, shorter interconnect, higher performance, and lower power. Stacking in a 3D-IC can be done wafer-to-wafer (W2W), die-to-wafer (D2W), or die-to-die (D2D). W2W allows higher manufacturing throughput, but achieving a good compound yield is difficult. In D2W and D2D, pre-bond testing can be used to screen out defective die and use only known-good die (KGD) when constructing the stack. Furthermore, during construction of the stack, additional known-good stack (KGS) testing can be done after each die is added to the stack which adds additional test cost, but has been shown to payoff in reducing overall costs by avoid additional processing in some cases [Taouil 10].

In order to do pre-bond testing on the non-bottom layers, it is necessary to add probe pads for test purposes. This is because the TSV tips as well as the microbumps are too small to be probed and are sensitive to scrub marks [Marinissen 09]. These probe pads are a test overhead that takes up a lot of space and limits the locations where TSVs can be placed which puts constraints on the design and floorplan of a die. Minimizing the probe pads is very important. In post-bond test, the bottom layer is accessed through the normal functional pins, and test data is transported to the upper layers via test elevator TSVs.

In 2D testing, test access mechanisms (TAMs) are used to deliver test data to core wrappers which interface with the scan chains in the cores. Procedures for optimizing the test architecture (i.e., selecting the width of TAMs, which cores are connected to each TAM, and optimizing the test wrappers) to minimize test time and satisfy power constraints have been well studied [Iyengar 02], [Goel 02], [Xu 05], [Larsson 05]. These algorithms

<sup>&</sup>lt;sup>1</sup> The work in this chapter is published in [Lee 13]: Y.-W. Lee and N.A. Touba, "Unified 3D Test Architecture for Variable Test Data Bandwidth Across Pre-Bond, Partial Stack, and Post-Bond Test," *Proceedings of IEEE Symposium on Defect and Fault Tolerance*, Paper 7.5, 2013. Yu-Wei Lee is the author and Nur. A. Touba is the supervisor.

are based on having a fixed test data bandwidth available from the tester. Based on this bandwidth they optimize the test architecture to minimize test time.

For 3D testing, procedures for optimizing the test architecture for post-bond test under a constraint on the number of TSVs used as test elevators to bring test data from the bottom layer to the non-bottom layers has been proposed in [Wu 08] and [Noia 10a]. In [Noia 10b], an optimization procedure is described for generating a test schedule for each stage of KGS testing (as each die is added to the stack) followed by the final test.

In pre-bond test, the test data bandwidth available from the tester for non-bottom dies is severely constrained because of the need to minimize the number of probe pads and thus will likely be different from the test data bandwidth used in post-bond test. This creates a challenge for optimizing the test architecture to minimize the overall test time corresponding to the sum of the test time for pre-bond test of each die plus the time for post-bond test of the final stack. In [Jiang 09], a test optimization procedure is proposed for this problem, but it assumed that the test elevators to the non-bottom layers could be probed in pre-bond test, however this would require a large number of probe pads to accomplish. In [Jiang 12], the problem is addressed by designing two TAM architectures, one optimized for the test data bandwidth available for pre-bond test and the other optimized for the test data bandwidth available for post-bond test. The key idea is to try to share the test wires in pre-bond and post-bond test as much as possible to minimize overhead.

In this chapter, a methodology is proposed for designing a single TAM architecture on each die with a "bandwidth adapter" that allows it to be efficiently used for multiple different test data bandwidths. In this way, a single test architecture can be re-used for pre-bond, partial stack, and post-bond testing while minimizing test time across all phases of test. Unlike previous approaches, this methodology does not need multiple TAM architectures or reconfigurable wrappers in order to be efficient when the test data

bandwidth changes. This helps to simplify the test architecture and minimize routing and overhead costs. The work in this chapter is published in [Lee 13].

#### 2.1. PROPOSED SCHEME

The idea in the proposed scheme is to optimize the test architecture on a particular layer for the maximum test data bandwidth, n, that the layer will receive during any phase of test (pre-bond, partial stack, or post-bond). Then for any phase of test where the bandwidth to the layer is less than n, a bandwidth adapter is used to handle the bandwidth mismatch.

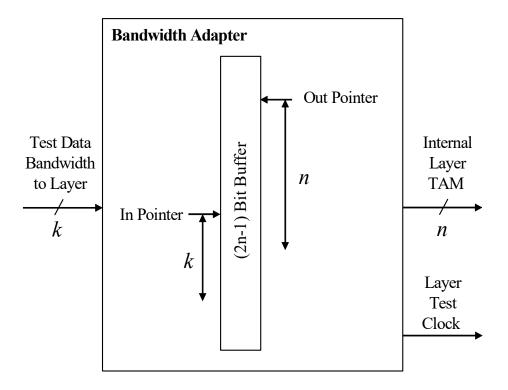

An input bandwidth adapter is shown in Figure 3. It takes as an input k bits of test data each clock cycle where k is less than or equal to n. It stores the k-bits received each clock cycle in a 2n-1 bit buffer at the location pointed to by the  $in\_pointer$  and then increments the pointer by  $k \mod 2n$ -1. When the difference between the  $in\_pointer$  and  $out\_pointer$  indicates that n or more bits are ready in the buffer, then the bandwidth adapter outputs the n bits pointed to by the  $out\_pointer$  and increments the  $out\_pointer$  by  $n \mod 2n$ -1. When the n bits are outputted, a pulse is generated on the  $layer\_test\_clock$  so that the internal layer TAM will transport the data. The bandwidth adapter can be designed in a general fashion to handle arbitrarily different test data bandwidths. Note that it is not necessary for n to be a multiple of k. Any value of k can be handled.

Figure 3. Input Bandwidth Adapter

By the same token, an output bandwidth adapter can be designed to handle the output response. It is the inverse of the input bandwidth adapater. It takes as an input the *n* bits of the internal layer TAM and the *layer\_test\_clock*, and it outputs *k* bit test data every clock cycle.

The proposed bandwidth adapter is totally independent to the underlying test architecture and thus is not limited to scan-based design. Note that some previous research has implemented the idea of variable bandwidth using reconfigurable wrappers which connect multiple scan chains to allow a smaller bandwidth to fill the scan chains [Khoche 01], [Koranne 03]. Serial/parallel conversion has also been used in [Noia 11] in the context of optimizing firm dies in post-bond test.

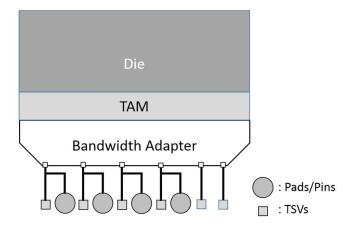

Figure 4 illustrates using a bandwidth adapter to unify the test architecture on a die for both pre-bond and post-bond test. The incoming bandwidth for pre-bond and post-bond tests are different because during pre-bond test, a smaller number of probe pads are used so the tester can directly probe the die, whereas during post-bond test, a larger number of test elevator TSVs are used to bring test data up from the pins in the bottom layer which are connected to the tester. The test architecture is optimized for the larger post-bond test data bandwidth, and then during pre-bond test, when the dies are tested separately, test vectors are brought in through the probe pads to the input bandwidth adapter which allows it to drive the larger number of TAM lines, and the output TAM lines go through an output bandwidth adapter to drive a smaller number of output probe pads.

Figure 4. Block Diagram for Using Bandwidth Adapter

Figure 5 illustrates all the different phases of test using the bandwidth adapter. As mentioned previously, partial stack test may be optional. With the help of a bandwidth adapter, the insertion of a partial stack utilizes the fact that only a subset of dies from the final stack test is tested in this stage. With the bandwidth adapter, the underlying test architecture does not need to be redesigned for this additional test. That is, the partial stack test can be viewed as an intermediate stage of a post-bond test. The dies in these

intermediate stages can use any bandwidth different from the final stack test within the limitation on the number of test elevators and test pins.

Figure 5. Unified TAM, Bandwidth Adapter and the Corresponding Test Flow

### 2.2. SELECTING BANDWIDTH FOR EACH STAGE OF TEST

This section describes how the test bandwidth is allocated at each stage of test to minimize the overall test time under the assumption of a unified test architecture with the proposed bandwidth adapter. There are two different scenarios considered in this section. The first scenario is only a pre-bond and post-bond test. The second scenario also includes partial stack tests, which can be viewed as a subset of the final stack test.

If only pre-bond and post-bond test are performed, the bandwidth used for pre-bond test of each die is equal to whatever maximum bandwidth is available from the tester to that particular die. That will depend on how many probe pads are available on the die. For post-bond test, the layers are tested in parallel under the constraint that the total amount of bandwidth for all layers is equal to the bandwidth between the tester and the pins of the bottom layer which is then distributed to the non-bottom layers via test elevator TSVs. The final post-bond test time is the largest test time among all layers in the design. The test data bandwidth that should be allocated to each layer to minimize the total test time needs to be selected.

The problem of determining the optimal post-bond bandwidth allocation to each layer can be formulated and solved with dynamic programming. The dynamic programming formulation can be written as follows:

$$\left\{ \begin{array}{l} \mathsf{T}(D_{i\ldots k},B) = \min\{\, \max[\, time_i(b_i), T(D_{i+1\ldots k},B-b_i)\,]\,\} \\ & if \,\, i < k \\ \\ \mathsf{T}(D_{i\ldots k},B) = time_i(B) \\ & if \,\, i = k \end{array} \right.$$

Where  $D_{i...k}$  represents set of dies from i through k.  $T(D_{i...k}, B)$  means the test time for dies from i through k with bandwidth B,  $b_i$  must be greater than 0 and represents the

bandwidth allocated to core i, and  $time_i(B)$  represents the test time for  $die\ i$  with bandwidth B.

The dynamic programming formulation above suggests that the search for an optimal bandwidth allocation can be divided into recursive subproblems. In addition, instead of examining all possible combinations exhaustively, the algorithm efficiently stores the results of overlapping subproblems into a table to avoid repeating unnecessary computation.

Function  $time_i(B)$  is a design-dependent function which queries what the test time for a layer would be using a given bandwidth B. To get this number, one of the many 2D algorithms for optimizing the test architecture for a given test data bandwidth can be used. For example, the TR-Architect algorithm [Goel 03] could be used as was done in the experiments reported in Section 4, but there are many others in the literature [Xu 05], [Larsson 05]. The proposed approach is applicable regardless of how the test architecture is optimized on each layer.

When determining  $time_i(B)$ , the existence of the bandwidth adapter needs to be taken into consideration. If B is smaller than the largest bandwidth used for die i in any phase of test, which will be referred to as  $B_{i,max}$  then for bandwidth B, the bandwidth adapter will be used to convert bandwidth B into the larger bandwidth  $B_{i,max}$ . The test time in this case will be equal to  $time_i(B_{i,max})$  scaled for the delay through the bandwidth adapter:

$$time_i(B) = [time_i(B_{i,max}) - P](\frac{B_{i,max}}{B_i}) + P$$

when  $B < B_{i,max}$

where *P* is the number of test patterns applied by the bottleneck TAM. The capture cycles for these patterns should not be scaled, so they are subtracted out before multiplying by the scaling factor so that only the shift time is scaled, and then the capture cycles are added back in unscaled.

The following is an illustrative example of deriving the optimal bandwidth allocation for a post-bond test. There are four dies in this example, D0, D1, D2 and D3 to

be placed at layer 0, layer 1, layer 2, and layer 3. The post-bond bandwidth is 6 in this example. Table 1 shows the relationship between bandwidth and test length for each die, namely the value of  $time_i(B)$ . Note that each die may come from very different designs, so the relationship between test time and bandwidth may not be consistent.

Table 1. Example of *time*<sub>i</sub>(*B*)

| Bi | D0 | D1 | D2 | D3 |

|----|----|----|----|----|

| 1  | 40 | 8  | 20 | 5  |

| 2  | 30 | 7  | 20 | 5  |

| 3  | 20 | 6  | 10 | 5  |

| 4  | 10 | 5  | 10 | 5  |

The algorithm begins with checking  $T(D_{0...3, 6})$ , which creates subproblems  $T(D_{1...3, 5})$ ,  $T(D_{1...3, 4})$ ,  $T(D_{1...3, 3})$ ,  $T(D_{1...3, 2})$  and  $T(D_{1...3, 2})$ . An example of an overlapping subproblem is that both  $T(D_{1...3, 3})$  and  $T(D_{1...3, 2})$  produce subproblem  $T(D_{2...3, 1})$ . Only necessary computation will be performed and will only be performed once. In this example, the optimal allocation is  $\{b0, b1, b2, b3\} = \{3, 1, 1, 1\}$ . The post-bond test time with the derived bandwidth allocation is 20.

Now consider partial stack tests. The bandwidth allocation problem can be solved in the same way as it is for final stack except that there are fewer layers. The same dynamic programming approach can be used. The key is to order the processing from smallest stack to largest stack because the bandwidth allocation for smaller stacks will be larger than for larger stacks. In this manner,  $B_{i,max}$  will be determined right away and then in all subsequent steps, the use of the bandwidth adapter will be known up front and can be factored in when determining  $time_i(B)$ .

So the overall procedure is to first determine the bandwidth for each die during prebond test. This is a given based on the number of probe pads available on the die. Next, if partial stack testing is to be done, then the bandwidth allocation for the smallest partial stack is computed first (using dynamic programming) since it will use the largest bandwidths, followed by the next smallest partial stack, and so forth until finally doing the full stack. The test architecture for each die is then designed and optimized based on the maximum bandwidth,  $B_{i,max}$ , that it receives in any phase of test. An input and output bandwidth adapter is then added to handle all other bandwidths that the die will see in any phase of test.

#### 2.3. EXPERIMENTAL RESULTS

Experiments were performed on the ITC'02 benchmarks. [Marinissen 02] provides detailed descriptions of the ITC'02 benchmarks. Each 3D benchmark has four layers and each layer contains a design from the ITC'02 benchmark set. Table 2 lists the components of each 3D benchmark.

Table 2. 3D Benchmarks

| Design | Layer 1 | Layer 2 | Layer 3 | Layer 4 |

|--------|---------|---------|---------|---------|

| 1      | h953    | d695    | u226    | d281    |

| 2      | f2126   | g1023   | d695    | u226    |

| 3      | p93791  | p34392  | p22810  | g1023   |

| 4      | q12710  | p34392  | p22810  | f2126   |

| 5      | p93791  | q12710  | p34392  | p22810  |

| 6      | t512505 | p93791  | q12710  | u226    |

| 7      | a586710 | p93791  | q12710  | p22810  |

| 8      | a586710 | t512505 | p93791  | p34392  |

To derive the test time for each design for different test data bandwidths, TR-Architect [Goel 03] was used in two scenarios. One is where the scan architecture is assumed fixed in the design as would be the case for hard cores (results shown in Table 3), and the second is where the scan architecture is assumed to be flexible as may be the case for soft cores (results shown in Table 4). The pre-bond bandwidth was assumed to be 8 in these experiments for the non-bottom layers, and the bottom layer was assumed to have a test data bandwidth of 32, 48, or 64. All possible partial stack tests are tested. The first partial stack test, which test layer 0 and layer 1 is referred to as intermediate test 1, and the second partial test is referred to as intermediate test 2. The final stack test involves testing all dies together.

In Table 3 and 4, results are shown for 3D designs 1 through 8 which are constructed with one ITC'02 benchmark circuit on each layer corresponding to what is shown in Table 2. The test time (in clock cycles) for each phase of test is shown comparing two cases. One is where a separate test architecture is designed for each different bandwidth (i.e., no bandwith adapter is used), and the other is where a single unified test architecture is designed using a bandwidth adapter.

As can be seen from the results in Tables 3 and 4, the overall test time of the proposed approach with a unified test architecture is very close to that of having separately optimized test architectures. In fact, it is even better in a few cases, but that is likely due to variations in the efficiency of different bandwidths for a design. The result is very good because it demonstrates that a unified test architecture which is simpler to design and requires less hardware overhead is able to do almost as well as if one custom designed a test architecture for each bandwidth that a layer sees.

Table 3. Experimental Result for Non-Flexible Designs

|     |                       |                        | Pre-bond   |           | Intermediate Test 1 |           | Final Stack |           | Overall    |           |            |           |         |

|-----|-----------------------|------------------------|------------|-----------|---------------------|-----------|-------------|-----------|------------|-----------|------------|-----------|---------|

|     | Pre-bond<br>Bandwidth | Post-Bond<br>Bandwidth | Separately | Unified   | Separately          | Unified   | Separately  | Unified   | Separately | Unified   | Separately | Unified   | ~       |

|     | Bunawian              | Build Wildell          | Optimized  | w/Adapter | Optimized           | w/Adapter | Optimized   | w/Adapter | Optimized  | w/Adapter | Optimized  | w/Adapter | Diff.   |

|     | 8                     | 32                     | 267163     | 267163    | 132343              | 132343    | 132343      | 132343    | 132343     | 132343    | 664192     | 664192    | 100.00% |

| 1   | 8                     | 48                     | 267163     | 267163    | 132343              | 132343    | 132343      | 132343    | 132343     | 132343    | 664192     | 664192    | 100.00% |

|     | 8                     | 64                     | 267163     | 267163    | 132343              | 132343    | 132343      | 132343    | 132343     | 132343    | 664192     | 664192    | 100.00% |

|     | 8                     | 32                     | 537887     | 537887    | 357757              | 357757    | 357757      | 357757    | 357757     | 357757    | 1611158    | 1611158   | 100.00% |

| 2   | 8                     | 48                     | 537887     | 537887    | 357757              | 357757    | 357757      | 357757    | 357757     | 357757    | 1611158    | 1611158   | 100.00% |

|     | 8                     | 64                     | 537887     | 537887    | 357757              | 357757    | 357757      | 357757    | 357757     | 357757    | 1611158    | 1611158   | 100.00% |

|     | 8                     | 32                     | 3961050    | 3851545   | 1314769             | 1314769   | 1522806     | 1526525   | 1538204    | 1533345   | 8336829    | 8226184   | 98.67%  |

| 3   | 8                     | 48                     | 3567417    | 3670068   | 921136              | 921136    | 1042640     | 1024827   | 1068036    | 1062649   | 6599229    | 6678680   | 101.20% |

|     | 8                     | 64                     | 3340565    | 3477831   | 695066              | 695066    | 812318      | 795918    | 833549     | 812143    | 5681498    | 5780958   | 101.75% |

|     | 8                     | 32                     | 6763984    | 6763984   | 3466238             | 3466238   | 3466238     | 3466238   | 3466238    | 3466238   | 17162698   | 17162698  | 100.00% |

| 4   | 8                     | 48                     | 6763984    | 6763984   | 3466238             | 3466238   | 3466238     | 3466238   | 3466238    | 3466238   | 17162698   | 17162698  | 100.00% |

|     | 8                     | 64                     | 6763984    | 6763984   | 3466238             | 3466238   | 3466238     | 3466238   | 3466238    | 3466238   | 17162698   | 17162698  | 100.00% |

|     | 8                     | 32                     | 9233954    | 9578467   | 3466238             | 3466238   | 3466238     | 3466238   | 3466238    | 3466238   | 19632668   | 19977181  | 101.75% |

| 5   | 8                     | 48                     | 9233954    | 9578467   | 3466238             | 3466238   | 3466238     | 3466238   | 3466238    | 3466238   | 19632668   | 19977181  | 101.75% |

|     | 8                     | 64                     | 9233954    | 9578467   | 3466238             | 3466238   | 3466238     | 3466238   | 3466238    | 3466238   | 19632668   | 19977181  | 101.75% |

|     | 8                     | 32                     | 30388711   | 30388711  | 22973206            | 22973206  | 23162552    | 23699371  | 24703920   | 23699371  | 101228389  | 100760659 | 99.54%  |

| 6   | 8                     | 48                     | 22627954   | 22627954  | 15212449            | 15212449  | 17126882    | 15808671  | 17229905   | 15883686  | 72197190   | 69532760  | 96.31%  |

|     | 8                     | 64                     | 20351239   | 20351239  | 12935734            | 12935734  | 13024248    | 13486929  | 13024248   | 13486929  | 59335469   | 60260831  | 101.56% |

| Avg |                       |                        |            |           |                     |           |             |           |            |           |            |           | 100.95% |

Table 4. Experimental Result for Flexible Designs

|     |                       |                        | Pre-bond   |           | Intermediate Test 1 Inter |           | Intermediat | Intermediate Test 2 Final Stack |            |           | Overall    |           |         |

|-----|-----------------------|------------------------|------------|-----------|---------------------------|-----------|-------------|---------------------------------|------------|-----------|------------|-----------|---------|

|     | Pre-bond<br>Bandwidth | Post-Bond<br>Bandwidth | Separately | Unified   | Separately                | Unified   | Separately  | Unified                         | Separately | Unified   | Separately | Unified   | Diff.   |

|     |                       |                        | Optimized  | w/Adapter | Optimized                 | w/Adapter | Optimized   | w/Adapter                       | Optimized  | w/Adapter | Optimized  | w/Adapter | Diff.   |

|     | 8                     | 32                     | 185043     | 193729    | 58383                     | 58383     | 66955       | 66656                           | 68623      | 68512     | 379004     | 387280    | 102.18% |

| 1   | 8                     | 48                     | 165924     | 175251    | 39264                     | 39264     | 44455       | 45225                           | 47749      | 48264     | 297392     | 308004    | 103.57% |

|     | 8                     | 64                     | 155826     | 162168    | 29165                     | 29165     | 33957       | 33794                           | 35351      | 35554     | 254299     | 260681    | 102.51% |

|     | 8                     | 32                     | 348445     | 348445    | 179417                    | 179417    | 200231      | 197433                          | 216881     | 200047    | 944974     | 925342    | 97.92%  |

| 2   | 8                     | 48                     | 287954     | 287954    | 118926                    | 118926    | 134129      | 134104                          | 141317     | 137619    | 682326     | 678603    | 99.45%  |

|     | 8                     | 64                     | 259052     | 259052    | 90024                     | 90024     | 99066       | 99066                           | 104303     | 102295    | 552445     | 550437    | 99.64%  |

|     | 8                     | 32                     | 3818236    | 3875858   | 1290998                   | 1290998   | 1514161     | 1514161                         | 1531433    | 1570649   | 8154828    | 8251666   | 101.19% |

| 3   | 8                     | 48                     | 3416782    | 3535277   | 885071                    | 885071    | 1006965     | 1016655                         | 1037496    | 1042895   | 6346314    | 6479898   | 102.10% |

|     | 8                     | 64                     | 3223401    | 3428306   | 691690                    | 691690    | 777193      | 787404                          | 787323     | 809828    | 5479607    | 5717228   | 104.34% |

|     | 8                     | 32                     | 4348203    | 4416227   | 1227133                   | 1227133   | 1443224     | 1443023                         | 1633317    | 1578602   | 8651877    | 8664985   | 100.15% |

| 4   | 8                     | 48                     | 3940850    | 4129643   | 842227                    | 842227    | 971816      | 982984                          | 1068114    | 1082651   | 6823007    | 7037505   | 103.14% |

|     | 8                     | 64                     | 3753565    | 4028200   | 632495                    | 632495    | 747585      | 746656                          | 819780     | 831156    | 5953425    | 6238507   | 104.79% |

|     | 8                     | 32                     | 7106302    | 7105983   | 1633317                   | 1633317   | 2040990     | 2057327                         | 2227321    | 2228377   | 13007930   | 13025004  | 100.13% |

| 5   | 8                     | 48                     | 6616992    | 6665707   | 1085050                   | 1085050   | 1406248     | 1406248                         | 1529900    | 1533397   | 10638190   | 10690402  | 100.49% |

|     | 8                     | 64                     | 6365179    | 6463831   | 833237                    | 833237    | 1047365     | 1068134                         | 1169749    | 1179100   | 9415530    | 9544302   | 101.37% |

|     | 8                     | 32                     | 29922077   | 29922077  | 22973206                  | 22973206  | 24263686    | 24437740                        | 24333128   | 24477405  | 101492097  | 101810428 | 100.31% |

| 6   | 8                     | 48                     | 21973150   | 21973150  | 15024279                  | 15024279  | 16249811    | 15620048                        | 16320517   | 15938714  | 69567757   | 68556191  | 98.55%  |

|     | 8                     | 64                     | 18695162   | 18695162  | 11746291                  | 11746291  | 12532429    | 12138131                        | 12553054   | 12138131  | 55526936   | 54717715  | 98.54%  |

| Avg |                       |                        |            |           |                           |           |             |                                 |            |           |            |           | 101.13% |

Note that even though the tester bandwidth is the same for all cases in pre-bond test, some cases reports different pre-bond test times. This arises due to the bandwidth adapter having to convert from a smaller tester bandwidth to a larger internal TAM bandwidth during pre-bond tests. It can be harder to efficiently schedule cores for larger TAM bandwidth. However, the test time in post-bond test is limited by the layer that takes the most time since post-bond test is performed in parallel. Therefore, the dynamic programming algorithm will try to use a larger TAM bandwidth for the bottleneck layer which may slightly increase pre-bond test time due to the inefficiency mentioned above. For non-bottleneck layers, the algorithm always try to use a bandwidth bigger than pre-bond bandwidth to avoid conversion at pre-bond. However, the net effect is improved overall test time because the reduction in post-bond test time is significantly greater than the increase in pre-bond test time.

#### 2.4. CONCLUSIONS

The proposed approach for designing a unified test architecture across all test stages in testing 3D-ICs allows efficient hardware utilization without significant overhead in test time. It is simple to design and implement, and can be used together with any of the existing 2D test architecture optimization schemes.

# 3. Improving Test Compression with Multiple-Polynomial LFSRs

Increasing integration density coupled with the need for more types of tests to be applied to achieve quality requirements has resulted in rapidly increasing test data volume. Test data compression is widely used to compress the amount of data stored on the tester. This helps to reduce tester storage requirements and improve test time as less data has to be transferred over the limited test data bandwidth between the tester and chip-under-test [Touba 06].

One highly efficient approach for compressing test cubes (which are test vectors in which the inputs unassigned by ATPG are left as don't cares) is to use sequential linear decompressors to encode them. Data from the tester are injected into a linear feedback shift registers (LFSR) while it loads scan chains thereby "dynamically" reseeding it. The final value of each scan cell after decompressing a test cube can be written as a linear equation in terms of the bits coming from the tester which act as free variables that can be assigned any value. Test cubes can be encoded by solving a system of linear equations where each equation corresponds to a care bit in the test vector being encoded [Könemann 01], [Krishna 01], [Rajski 04].

The amount of test compression achieved can be increased by increasing the number of scan chains driven by the decompressor (i.e., increasing the "expansion ratio"). As the expansion ratio is increased, it becomes increasingly difficult to solve the system of linear equations because more care bits need to be encoded while the number of free-variables remains the same. At some point, the equations for two or more care bits will become linearly dependent and not be solvable. The bottleneck tends to be the scan cells loaded the earliest because they depend on fewer free-variables as the number of free-variables injected in the LFSR in the beginning is small. Consequently there is less encoding flexibility for solving the scan chains loaded the earliest and they will tend to limit the overall test compression that can be achieved.

One powerful way to increasing the encoding flexibility is to use a multiple-polynomial LFSR [Hellebrand 95] in which there are several choices for the characteristic polynomial of the LFSR. The polynomial used for encoding each test cube can be selected. So if the system of linear equations for one polynomial is linearly dependent and unsolvable, then a different polynomial can be selected to change the linear correlations and provide a different system of linear equations that may be solvable. If the multiple-polynomial LFSR can be configured with say 16 different feedback polynomials, then there are 16 different sets of linear equations which can be solved thereby providing a much higher probability of encoding a test cube. This makes a big difference particularly for the scan cells loaded the earliest which depend on fewer free variables. By adding additional flexibility in the selection of the polynomial, this weakness can be significantly relieved allowing higher expansion ratios to be used to achieve greater test compression.

The original idea of using a multiple-polynomial LFSR to help in encoding test cubes was originally proposed in [Hellebrand 95] in the context of static LFSR reseeding in a built-in self-test (BIST) environment. In static LFSR reseeding, only the initial seed of the LFSR contains free-variables. No additional free-variables are injected during decompression. Thorough analysis and results are presented in [Hellebrand 95] showing the effectiveness of multiple polynomials in reducing the number of bits that need to be stored on-chip compared with using a single polynomial LFSR for encoding test cubes with static reseeding in a BIST environment.

In this chapter, the use of multiple-polynomial LFSRs for dynamic reseeding in a test compression environment is investigated. The new contributions of this work include the following:

- A scheme for using multiple-polynomial LFSRs without requiring any control data by formulating it as a matching problem

- A way to implement a multiple-polynomial LFSRs with less overhead by exploiting properties of primitive polynomials

- A method to use multiple-polynomials to increase the effectiveness of retaining unused free-variables [Muthyala 12]

- Experimental results demonstrating the improvements that can be obtained by using multiple-polynomials in dynamic reseeding alone and with retained free-variables.

The chapter is organized as follows: Section 3.1 reviews the fundamentals of sequential linear decompression. Section 3.2 describes the hardware implementation of the multiple polynomial LFSR with rotating polynomials. Section 3.3 presents the algorithm to assign test cubes to polynomials. Section 3.4 shows the experimental results. Section 3.5 is a conclusion.

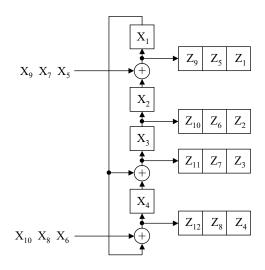

### 3.1. SEQUENTIAL LINEAR DECOMPRESSION

This section reviews the fundamental concepts behind sequential linear decomposition and techniques for reducing tester data through retaining free variables. In sequential linear decompression, variables are continuously injected into a LFSR [Mrugalski 04]. To determine the value of each injected variables, Linear equations can be obtained thorough symbolic simulation of the linear decompressor. This process is illustrated in figure Figure 6. At each cycle, new variables are injected into the decompressor. In Figure 6, these injected variables are represented by *X*. Also at each cycle, the content of the LFSR are being sent to the scan chains. These variables on the scan chains are represented by *Z*. At the bottom of Figure 6, a table is given for the linear equations of the variables after three cycles of symbolic simulations.

| $Z_9 = X_1 \oplus X_4 \oplus X_9$                          | $Z_5 = X_3 \oplus X_7$                       | $Z_1 = X_2 \oplus X_5$ |

|------------------------------------------------------------|----------------------------------------------|------------------------|

| $Z_{10} = X_1 \oplus X_2 \oplus X_5 \oplus X_6$            | $Z_6 = X_1 \oplus X_4$                       | $Z_2 = X_3$            |

| $Z_{11} = X_2 \oplus X_3 \oplus X_5 \oplus X_7 \oplus X_8$ | $Z_7 = X_1 \oplus X_2 \oplus X_5 \oplus X_6$ | $Z_3 = X_1 \oplus X_4$ |

| $Z_{12} = X_3 \oplus X_7 \oplus X_{10}$                    | $Z_8 = X_2 \oplus X_5 \oplus X_8$            | $z_4 = x_1 \oplus x_6$ |

Figure 6. Symbolic Simulation of Sequential Linear Decompression

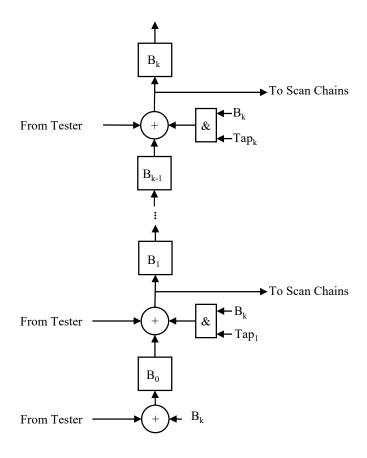

Figure 7 is a Boolean matrix representation of the linear equations obtained from the LFSR in Figure 6. Solving these linear equations determines what value should be assigned to each variable. Based on the equations, some of the variables may need to be a certain value, whereas some variables may be freely assigned with any value.

Figure 7. Matrix Representation of Linear Equations

The process of solving the linear equations is illustrated in Figure 8. A submatrix which corresponds to the rows that specify Z as care bits are extracted. The submatrix is then solved with Gauss-Jordan elimination. After the Gauss-Jordan elimination, variables can be put into two different categories: pivot and non-pivot variables. The pivot variables represent the variables that need to be assigned to a particular value to encode the test cube whereas the non-pivot variables can be freely assigned with any value. Therefore, non-pivot variables are also called free variables. It is desirable to increase the number of free variables to reduce amount of data required to be stored on tester.

Figure 8. Solving Linear Equations

Approaches to increase the number of free variables have been proposed. In [Muthyala 12], a FIFO is added before the sequential decompressor to retain the free variables. The retained free variables can then be used to encode the next test cube. It has been shown that using a FIFO can help to reduce amount of tester data with minimal performance impact.

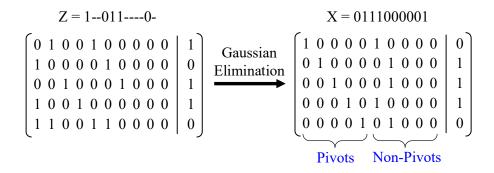

#### 3.2. PROPOSED APPROACH

The concept of the proposed scheme is instead of having a fixed LFSR structure with one polynomial, the LFSR can be reconfigured to implement multiple different polynomials. If a test cube is not encodable by a particular polynomial, a different polynomial can be used instead.

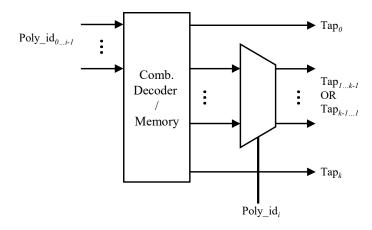

A Galois LFSR is a type of LFSR where the last bit is sent back and XORed with shifted values at certain tap locations. The tap locations depend on the polynomial of the LFSR. A multiple polynomial LFSR is implemented with reconfigurable tap locations. Figure 9 shows a Galois multiple-polynomial LFSR for sequential linear decompression with k bits. The  $TAP_i$  signals in Figure 9 select which locations to feedback the last bit  $B_k$  from the LFSR to implement the desired polynomial.

Figure 9. Multiple-polynomial LFSR

If the multiple polynomial LFSR is to be used with a set of p polynomials, then  $log_2/p$  /control bits are needed to select which polynomial to use. The p polynomials could either be stored in a ROM with p address locations each storing k-l bits for a k-bit LFSR (it is k-l because the first tap point is always used for any polynomial), or they could be implemented with combinational logic having  $log_2/p$  / inputs. The advantage of using a ROM implementation is that the set of polynomials can be chosen after the test cubes are generated.

In dynamic LFSR reseeding, where continuous flow decompression is used, it is undesirable to have to supply additional control bits to select the polynomial when decompressing a test cube. The proposed approach solves this problem by exploiting the fact that test cubes can be reordered. The proposed approach uses a counter to select the polynomial each time a test cube is decompressed such that the polynomials are constantly rotating (i.e., a different polynomial is used in each subsequent test cube decompression until all *p* polynomials have been used at which point it cycles back to the first one). In this way, the polynomial that is used to encode a particular test cube can be selected by the way the test cubes are ordered. Many test cubes can be encoded by all the polynomials, so it doesn't matter which one they are matched with. For some test cubes, only some of the polynomials can be used to encode them, so they must be placed in spots where they will be decompressed with a polynomial that can encode them. The next section will formulate the problem of ordering the test cubes as a bipartite matching problem. The advantage of this approach is that no control bits are needed for selecting the polynomial, so there is no additional data that needs to be stored and transferred from the tester to use a multiple polynomial LFSR compared to what is used for a conventional single polynomial LFSR.

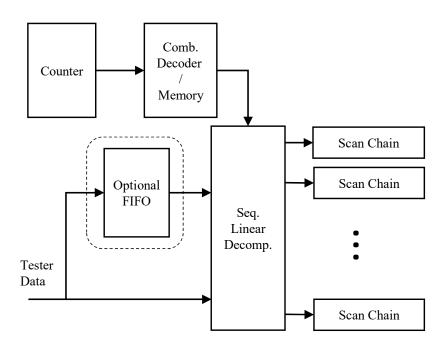

Figure 10 shows the proposed hardware implementation of decompression with a multiple polynomial LFSR with a rotating polynomial. In each new test cube decompression, the counter increments to switch to the next polynomial. The circuitry that generates the polynomial can be either a combinational decoder or a ROM. If it is desired to use the scheme described in [Muthyala 12] to retain the unused free variables for one test cube to help in encoding the next test cube, a FIFO can optionally be added. This helps to increase encoding efficiency. To maximize the number of free variables retained in the FIFO, the process that assigns the test cubes to polynomials can be modified as will be described in the next section.

Figure 10. Proposed decompression scheme with multiple-polynomial LFSR

Hardware overhead for the multiple polynomial LFSR can be further reduced by exploiting a property of primitive polynomials which is that the reciprocal of a primitive polynomial is also primitive [Pless 11]. The reciprocal is formed by simply reversing the order of the coefficients in a polynomial. For example, for the primitive polynomial ( $x^4 + x + 1$ , i.e., coefficients 10011), the reciprocal polynomial is ( $x^4 + x^3 + 1$ , i.e., 11001) is also primitive. Our experiments showed that the set of test cubes that can be encoded by a primitive polynomial and its reciprocal polynomial is as diverse as the polynomial with an arbitrary different primitive polynomial. There is no noticeable degradation in using a reciprocal polynomial versus using any other arbitrary primitive polynomial. The idea proposed here is to use this property to reduce the hardware costs. If a multiple polynomial with p primitive polynomials is to be used, instead of storing all p polynomials in the ROM, only p/2 polynomials could be stored in the ROM, and then MUXes can be used to generate the reciprocal of these p/2 polynomials to generate another set of p/2 polynomials as shown in Figure 11. This approach still generates p total primitive polynomials, but it uses a ROM that is half as large. However, it also requires k-1 2-to-1 MUXes to reverse the polynomials

for a k-bit LFSR. These reason why it is k-l instead of k is that there are k+l coefficients for each polynomial, but the first and last coefficients are always l, so they do not need to be reversed. Overall, the cost of the k-l MUXes is much less than (p/2)(k-l) ROM bits for sufficiently large p, and it does not scale as p is increased. For a combinational decoder implementation, using reciprocal polynomials also helps reduce the size of the combinational logic although the improvement is less than it is for a ROM implementation.

Figure 11. Reducing hardware overhead for primitive polynomial generation by using MUXes to select between a polynomial and its reciprocal

With the rotating polynomials, the test cube encoding process is the following. At design time, based on the length of the LFSR, p/2 primitive polynomials of the correct length are arbitrarily selected (assuming the reciprocal polynomials will also be used). The decompressor is designed with a mod-p counter along with the selected polynomials without any assumption of a specific set of test cubes. Once the set of test cubes are generated after ATPG, the test cubes are ordered using the procedure described in the next section. Note that multiple test cubes can be decompressed with the same polynomial since the counter will cycle back to the same polynomial repeatedly during decompression.

#### 3.3. Assigning Test Cubes to Polynomials through Bipartite Matching

Section 3.2 described the decompressor hardware with continuously rotating polynomials. In this section, an algorithm is described for ordering the test cubes in a way that each test cube is decompressed using a polynomial that can encode it.

Given the set of polynomials that are rotating in the decompressor, along with the test cubes that need to be encoded, the problem can be formulated as a bipartite graph:

- For each polynomial, a vertex on the left side is created for each time the polynomial is repeated during decompression due to the counter cycling through it. This total number of vertices on the right hand size will be equal to the total number of test cubes to be decoded. The set of vertices that represent the polynomials is denoted as  $V_L$ .

- For each test cube, a vertex is created on the right side. The set of vertices that represent the test cubes is denoted as  $V_R$ .

- For each vertex in  $V_L$  and  $V_R$ , create an edge if the corresponding polynomial in  $V_L$  can encode the corresponding test cube in  $V_R$ .

After the above procedure, the problem of assigning test cubes to polynomials is represented with a bipartite graph. A *matching* is a subset of edges such that each node appears exactly one time at the edges in the matching. The problem of finding the polynomials to encode all the test cubes is equivalent to a bipartite matching problem with a constraint that every node must appear in exactly one match.

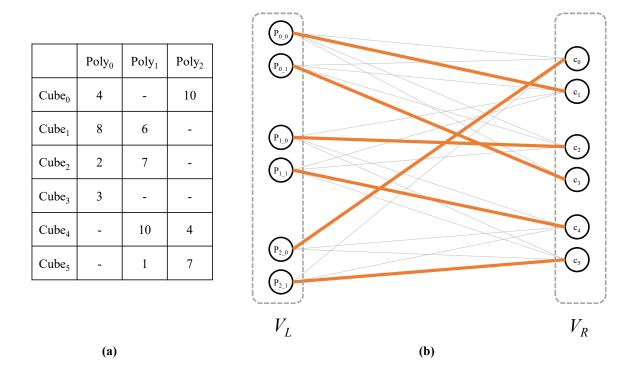

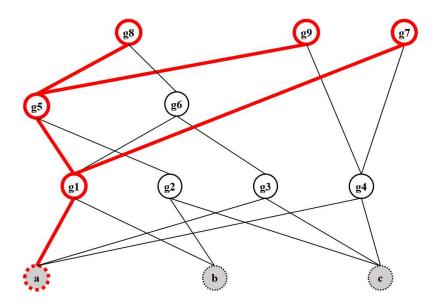

Figure 12 depicts an example of the bipartite matching problem. There are six test cubes, each can be encoded by a subset of the three given polynomials. To cover all test cubes, the polynomials are repeated twice. For example, vertex  $P_{\theta_-\theta}$  represents the first appearance of polynomial 0, and  $P_{\theta_-l}$  represents the second appearance of polynomial 0. Test cube 0, 1, and 2 are represented by vertices  $c_{\theta}$ ,  $c_{l}$  and  $c_{l}$  respectively. For each polynomial, the encodable test cubes are listed at the bottom. An example of a matching is shown in bold edges in Figure 12. Note that there is more than one matching possible. As

long as every vertex is matched, it is considered a legal solution to encode all test cubes with the given polynomials.

Figure 12. Example of assigning test cubes to polynomials thorough bipartite matching

Using the Ford-Fulkerson algorithm, the bipartite matching problem can be solved in O(VE). In this case, the number of vertices is O(T) where T is the total number of test cubes, and the number of edges is O(pT) since each test cube can have up to p edges where p is the number of polynomials. Thus, the overall complexity will be  $O(pT^2)$ .

In Section 3, using a FIFO to implement the scheme in [Muthyala 12] was mentioned as an optional unit. The purpose of the FIFO is to improve encoding efficiency by retaining as many unused free variables as possible. Under this objective, in addition to matching test cubes to polynomials that can encode it, the number of free variables that can

be retained should also be considered as this will vary depending on which polynomial is used to encode the test cube. This is because the FIFO only stores the latter free variables, and some polynomials will encode with more unused free variables towards the end than other polynomials will for a particular test cube. This can be considered by adding weights to the edges in bipartite graph corresponding to the number of free variables that get retained.

• For each edge between  $V_L$  and  $V_R$ , label the edge with weight equal to the number of free variable retained by encoding the test code represented by the vertex in  $V_R$  with polynomial represented by the vertex in  $V_L$ .

This revised scenario is equivalent to the maximum weighted bipartite matching problem. It has the same constraint that only one match is allowed for each vertex, but with additional objective that the optimal matching is the set of edges with the maximum sum of weights. Figure. 13 shows an example of building a maximum weighted bipartite matching problem and an optimal solution. The table on the left in Figure 13 describes the relationships between 6 test cubes and 3 polynomials. In the table, each entry shows how many unused free variables are retained when the polynomial is used to encode that test cube. If the entry is left blank, the polynomial cannot encode that test cube. On the right side of Figure 13, the edges between the vertices are created with the weight given in the table. For better readability, the weights on the edges are not shown. An optimal solution to the minimum-weighted matching problem is shown by bold edges in the graph.

Figure 13. Assigning test cubes to polynomials considering number of free variables retained

The maximum weighted bipartite matching problem with non-negative edges can be solved in  $O(V^2logV + VE)$ . So in this case, the overall complexity will be  $O(T^2logT)$  assuming the number of testcubes is much larger than the number of polynomials.

#### 3.4. EXPERIMENTAL RESULTS

A first set of experiments was performed using a 64-bit LFSR with 16 rotating primitive polynomials. The results are shown in Table 5. The first four columns show information about each circuit: number of test cubes, number of scan cells, and number of tester channels. Results are then shown for the conventional case where each test cube is encoded by the same polynomial. The number of scan chains was increased until it was no longer possible to encode all the test cubes with the given number of tester channels. The number of scan chains and the resulting amount of data that needs to be stored on the tester is shown for the conventional case.

Table 5. Results for Using Proposed Scheme to Encode Test Data

|         |       |        |        | Conve  | entional       | Proposed |         |           |                      |         |           |             |  |  |

|---------|-------|--------|--------|--------|----------------|----------|---------|-----------|----------------------|---------|-----------|-------------|--|--|

| Circuit | Num.  | Scan   | Tester |        | e Poly.<br>FSR |          | 16 Pol  | y. LFSR   | 16 Poly. LFSR + FIFO |         |           |             |  |  |

|         | Vect. | Cells  | Chans. | Scan   | Tester         | Scan     | Tester  | Percent   | Scan                 | Tester  | Percent   | Overhead    |  |  |

|         |       |        |        | Chains | Data           | Chains   | Data    | Reduction | Chains               | Data    | Reduction | (Cell Area) |  |  |

| Ckt-A   | 266   | 3,828  | 5      | 27     | 190,190        | 35       | 151,620 | 25        | 37                   | 139,225 | 37        | 35 FF       |  |  |

| Ckt-B   | 540   | 5,020  | 8      | 88     | 272,160        | 108      | 224,640 | 21        | 118                  | 207,360 | 31        | 46 FF       |  |  |

| Ckt-C   | 490   | 6,370  | 7      | 54     | 404,187        | 71       | 312,214 | 29        | 73                   | 298,872 | 35        | 44 FF       |  |  |

| Ckt-D   | 592   | 7,417  | 10     | 95     | 485,440        | 110      | 402,560 | 21        | 130                  | 361,120 | 34        | 47 FF       |  |  |

| Ckt-E   | 711   | 8,742  | 9      | 81     | 697,491        | 111      | 537,516 | 30        | 112                  | 506,331 | 38        | 32 FF       |  |  |

| Ckt-F   | 615   | 12,225 | 6      | 60     | 771,210        | 75       | 619,920 | 24        | 78                   | 597,708 | 29        | 31 FF       |  |  |

In the next section of Table 5, results were generated using the proposed multiple polynomial LFSR. The results under the major heading 16 poly. LFSR show the results without the optional FIFO. The number of scan chains was increased until it was no longer possible to encode all the test cubes with the given number of tester channels. As the number of scan chains goes up, the scan length goes down. Consequently, less data is shifted in from the tester to the decompressor, so the amount of data stored on the tester is reduced (i.e., the amount of test compression increases). The percentage reduction in test data is computed as:

The results show a 21-30% improvement in compression over conventional single polynomial LFSR when a rotating polynomial is used. This is because having multiple polynomials to choose from increases the chance of encoding a test cube, so more aggressive expansion to more scan chains is possible while still being able to solve the linear equations. That last columns in the table show the results for using an LFSR with 16 polynomials and including a FIFO to retain unused free variables using the method

described in [Muthyala 12]. As can be seen, this boosts the improvement in compression up to 29-39%. The overhead for the FIFO is shown in the last column in terms of the number of flip-flops used.

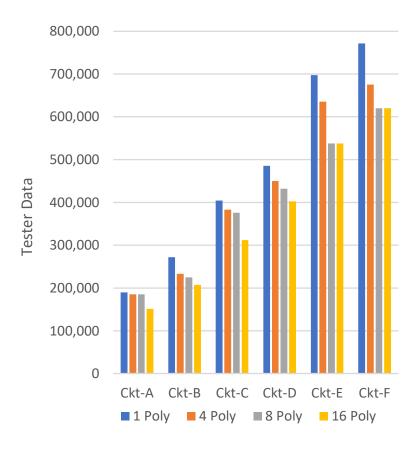

For the next set of experiments, the relationship between the number of polynomials used and the reduction in tester data was explored. The results are shown in Figure 14. Each of the circuits are shown on the *x*-axis with a bar for 1, 4, 8, and 16 polynomials. The amount of tester data used is shown on the *y*-axis. From the results, it can be seen that the more polynomials that are used, the more efficient the compression is. In some cases, the amount of compression stayed the same when the number of polynomials were increased (e.g., the results between 4 and 8 polynomials in Ckt-A), but then improved as the number of polynomials was increased further (i.e., the results between 8 and 16).

Figure 14. Number of Polynomials versus Test Data

#### 3.5. CONCLUSIONS

Multiple polynomial LFSRs can significantly improve test data compression for sequential linear decompressors. This chapter proposed an efficient implementation of a multiple polynomial LFSR with rotating polynomials which exploits the degree of freedom in ordering test cubes to avoid the need for control bits. Using multiple polynomial LFSRs is a low cost way to boost test compression without creating any additional complexity for continuous-flow decompression. The only cost is the additional area overhead for the multiple polynomial LFSR versus single polynomials LFSR, and running the bipartite matching algorithm for ordering the test cubes which runs in polynomial time.

## 4. Improving Logic Obfuscation via Logic Cone Analysis<sup>2</sup>

Logic obfuscation has been proposed as a means to hide the functionality of a design to protect it from reverse engineering, hardware Trojan, and IP piracy [Roy 08, 10], [Chakraborty 09a], [Baumgarten 10], [Rajendran 12, 14]. One approach is to use combinational obfuscation where "key gates" are inserted in a design which have primary inputs that are referred to as "key inputs". The design will only function correctly if the correct key values are used. This approach was proposed in [Roy 08, 10]. The IP vendor activates the obfuscated design by storing the correct key values in a tamper-evident memory or using a physically unclonable function (PUF) [Suh 07] to generate them in a way that an attacker cannot access the key values. Without the key values, the design is unusable even if the netlist is obtained by either stealing the design or reverse engineering it.

Logic obfuscation with XOR and MUXes is investigated in [Rajendran 14]. In order to evaluate the effectiveness of the key bits, hamming distance (HD) was used to evaluate the result after application of a wrong key. 50% of HD is desired to ensure the malicious users will not be able to obtain correct output easily without the correct key.

In addition to raising the effectiveness of key insertion, [Rajendran 12] also pointed out the importance of protecting the key bits against "attacks". If the attacker has the netlist and purchases a functional IC in the open market, then the attacker can try to determine the correct key input values to unlock the design. This is done by simulating input patterns on the netlist and comparing them with the correct output values obtained by running the same input patterns on the functional IC. It is shown in [Rajendran 12] that if an input pattern can be found which sensitizes a key input to a primary output without any interference from other key inputs, then the input pattern will propagate the correct key value to the primary output when running the pattern on the functional IC. The attacker can use ATPG

<sup>&</sup>lt;sup>2</sup> The work in this chapter is published in [Lee 15]: Y.-W. Lee and N.A. Touba, "Improving Logic Obfuscation via Logic Cone Analysis," *Proceedings of IEEE Latin-American Test Symposium*, 2015. Yu-Wei Lee is the author and Nur. A. Touba is the supervisor.

to try to find an input pattern that sensitizes a key input to a primary output treating all other key inputs as X's. Each time such a pattern is found, the attacker runs it on the functional IC and looks at the output to resolve the key value. Whenever a key value is resolved, it is no longer an X when sensitizing the remaining key inputs thereby making the problem iteratively easier. After as many keys are resolved as possible using this approach, the remaining keys can be determined through brute force. The brute force procedure is to try each possible combination of values for the keys until the correct one is found. Checking if the candidate combination of key values is correct is done by simulating a set of random patterns on the netlist using the candidate key values and then comparing that with the output response obtained by simulating the same patterns on the functional IC to see if they match.

In [Rajendran 12], a heuristic procedure is proposed for inserting key gates so as to increase the amount of interference between the key gates and reduce the chance of finding patterns that sensitize a key input to an output without interference from other key inputs. The goal is to maximize the number of key values for which brute force must be employed thereby increasing the difficulty for the attacker. The heuristic procedure is based on constructing a graph in which each node is a key, and weighted edges are placed between the nodes to indicate the amount of interference that is created. Each key gate is iteratively inserted in the design so as to maximize the resulting sum of the weights on all edges in the graph at each step.