Copyright by Khubaib 2014 The Dissertation Committee for Khubaib certifies that this is the approved version of the following dissertation:

## Performance and Energy Efficiency via an Adaptive MorphCore Architecture

Committee:

Yale N. Patt, Supervisor

Derek Chiou

Mattan Erez

Keshav Pingali

Chris Wilkerson

## Performance and Energy Efficiency via an Adaptive MorphCore Architecture

by

Khubaib, B.S.E.E.; M.S.E.

#### DISSERTATION

Presented to the Faculty of the Graduate School of The University of Texas at Austin in Partial Fulfillment of the Requirements for the Degree of

#### DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN

May 2014

Dedicated to my mother, Ammi Jaan

### Acknowledgments

First and foremost, I thank my advisor, Professor Yale N. Patt. I learned the fundamentals of computer architecture and microprocessor design in his 360N and 382N classes. His emphasis on fundamentals has always been inspirational to me. Professor Patt created a great environment for learning and doing impactful research. His feedback on my thesis and on all my other research projects has strengthened my work. He taught me a lot about communicating effectively via writing and presentations. I thank him for training me as a computer architect as well as teaching me many valuable real-life lessons. Lastly, I thank him for taking good care of his students.

I thank Aater Suleman for being a great friend and mentor, for helping me in writing papers, and for his many technical contributions to my research. He has shown me the value of creating and quickly evaluating first-order insights. Aater introduced me to the world of heterogeneous computing from which the idea of MorphCore came about. Additionally, I have benefited from simulation infrastructure that he developed. I am thankful to him for always being there to listen to my problems and to help me, in matters related to both research and life in general.

I thank the members of the HPS research group that worked with me while I was in the group: Peter Kim, José Joao, Chang Joo Lee, Eiman Ebrahimi, Rustam Miftakhutdinov, Veynu Narasiman, Carlos Villavieja, Marco A. Z. Alves, Milad Hashemi, Faruk Guvenilir, and Ben (Ching-Pei) Lin. They have been great friends and colleagues. The interactions with them have improved my research and have helped me develop as a computer architect. I thank José for always being there to answer any question I have, for maintaining our group's infrastructure, and for helping me with my papers. I thank Chang Joo for helping me with my questions on the memory system and I thank Rustam for providing insightful critique on my ideas, and for helping me with my simulation infrastructure. I thank Milad for his candid feedback on my ideas and for his many contributions to MorphCore research and paper. I thank Eiman, Veynu, Carlos, Marco, Faruk, and Ben for useful feedback on my research, for helping me in writing, and for teaching me computer architecture. I also thank them for proofreading my thesis. The best thing about being in the HPS research group with all of these people was the feeling that I can go talk to any one of them anytime about anything, and afterwards I would be happy that I did. Besides the HPS group members, I would like to express my gratitude to the following people and organizations.

I thank the members of my committee, Professor Derek Chiou, Professor Mattan Erez, Professor Keshav Pingali, and Chris Wilkerson for providing useful feedback.

I thank Nikhil Patil for always challenging my ideas, providing insightful feedback, reading my drafts, and for being a great friend. I have always learned something new after talking to him. I thank Moinuddin Qureshi for improving my understanding of caching and the memory system. I also thank him and Viji Srinivasan for mentoring me during my internship at IBM. I thank Rob Chappell, Chris Wilkerson, Doug Carmean, and Jared Stark for mentoring me during my internships at Intel and for useful discussions on research. Chris provided insightful feedback on many ideas that I explored during my work on MorphCore. I thank Onur Mutlu for useful discussions on research and for always pushing me to do more. I thank Francis Tseng, Bharath Balasubramanian, Chris Fallin, Dimitris Prountzos, George (Chia-Chih) Chen, and Hari Angepat for their friendship and useful discussions. I thank Dr. Shoab A. Khan for being a role model when I was going through my undergraduate education and for always being extremely helpful.

I thank Leticia Lira for her outstanding administrative support to HPS research group, Melanie Gulick for helping with matters related to ECE department and paperwork, and Intel for providing me with a PhD Fellowship.

My life in Austin and at UT would not have been good without the good company of my friends: Owais Khan, Zubair Malik, Umar Farooq, Amber Hassaan,

Faisal Iqbal, Tauseef Rab and Rashid Kaleem. I have enjoyed many nights and dinners with them discussing all sorts of random things. I especially thank my longtime roommate, Owais, for his great company. I thank my friends Bilal Amin, Shahzad Yasin, Bilal Saqib, and Imran Bhai for all the wonderful time we had together in Pakistan. These memories have kept me going during the tough times in graduate school.

Finally, I would like to thank my family. This thesis is dedicated to my mother. Without her infinite love, support, and confidence I would not have come to graduate school and finished my PhD. She has taught me the value of education, hard work and perseverance. I owe all my successes to her, and no words could express my gratitude to her. I am greatly thankful to my sisters, Ayesha and Fatima, for continuous love and support, and to my brother, Ubaid, who took care of matters at home while I was away. I would like to thank my wife, Sana, for her love and support during the last one and a half years of my PhD, and for pushing me to defend. I have been fortunate to have her in my life. Today I would also like to pay tribute to the memory of my late father. He would have been very happy to see me completing my formal education. The values he taught me at very young age have made me who I am today. My family has been a source of great comfort for me, and this thesis would be meaningless without them.

Khubaib May 2014, Austin, TX

## Performance and Energy Efficiency via an Adaptive MorphCore Architecture

Khubaib, Ph.D. The University of Texas at Austin, 2014

Supervisor: Yale N. Patt

The level of Thread-Level Parallelism (TLP), Instruction-Level Parallelism (ILP), and Memory-Level Parallelism (MLP) varies across programs and across program phases. Hence, every program requires different underlying core microarchitecture resources for high performance and/or energy efficiency. Current core microarchitectures are inefficient because they are fixed at design time and do not adapt to variable TLP, ILP, or MLP.

I show that if a core microarchitecture can adapt to the variation in TLP, ILP, and MLP, significantly higher performance and/or energy efficiency can be achieved. I propose MorphCore, a low-overhead adaptive microarchitecture built from a traditional OOO core with small changes. MorphCore adapts to TLP by operating in two modes: (a) as a wide-width large-OOO-window core when TLP is low and ILP is high, and (b) as a high-performance low-energy highly-threaded in-order SMT core when TLP is high. MorphCore adapts to ILP and MLP by varying the superscalar width and the out-of-order (OOO) window size by operating in four

modes: (1) as a wide-width large-OOO-window core, 2) as a wide-width medium-OOO-window core, 3) as a medium-width large-OOO-window core, and 4) as a medium-width medium-OOO-window core.

My evaluation with single-thread and multi-thread benchmarks shows that when highest single-thread performance is desired, MorphCore achieves performance similar to a traditional out-of-order core. When energy efficiency is desired on single-thread programs, MorphCore reduces energy by up to 15% (on average 8%) over an out-of-order core. When high multi-thread performance is desired, MorphCore increases performance by 21% and reduces energy consumption by 20% over an out-of-order core. Thus, for multi-thread programs, MorphCore's energy efficiency is similar to highly-threaded throughput-optimized small and medium core architectures, and its performance is two-thirds of their potential.

## **Table of Contents**

| Acknow        | vledgm        | nents                                                                                      | v   |

|---------------|---------------|--------------------------------------------------------------------------------------------|-----|

| Abstract viii |               |                                                                                            |     |

| List of       | Tables        |                                                                                            | xiv |

| List of       | Figure        | S                                                                                          | XV  |

| Chapte        | r1. I         | ntroduction                                                                                | 1   |

| 1.1           | The P         | roblem                                                                                     | 1   |

| 1.2           | The S         | olution                                                                                    | 3   |

| 1.3           | Thesis        | s Statement                                                                                | 4   |

| 1.4           | Contr         | ibutions                                                                                   | 4   |

| 1.5           | Disse         | rtation Organization                                                                       | 5   |

| Chapte        | r 2. (        | <b>Dverview of MorphCore Architecture</b>                                                  | 6   |

| 2.1           | Baseli        | ine Large OOO Core                                                                         | 6   |

|               | 2.1.1         | Energy Cost of OOO Execution                                                               | 7   |

| 2.2           | Adapt         | ting to TLP                                                                                | 8   |

|               | 2.2.1         | The Potential of In-Order SMT                                                              | 8   |

|               | 2.2.2         | Repurposing Core's Resources                                                               | 10  |

|               | 2.2.3         | Operating Modes                                                                            | 10  |

| 2.3           | Adapt         | ting to ILP and MLP                                                                        | 10  |

|               | 2.3.1         | Energy Cost of Wide Width                                                                  | 11  |

|               | 2.3.2         | Problem: Different Programs Benefit Differently from Wide<br>Width and/or Large OOO Window | 12  |

|               | 2.3.3         | Our Solution: Dynamically Vary Width and Window Size                                       | 14  |

| Chapte        | r <b>3.</b> A | Adapting to Thread-Level Parallelism (TLP)                                                 | 16  |

| 3.1           | Morp          | hCore Microarchitecture                                                                    | 16  |

|               | 3.1.1         | Overview                                                                                   | 16  |

|               | 3.1.2         | Fetch and Decode Stages.                                                                   | 17  |

|               | 3.1.3         | Rename Stage                                                                               | 17  |

|        | 3.1.4     | Select and Wakeup                                                                      | 20 |

|--------|-----------|----------------------------------------------------------------------------------------|----|

|        | 3.1.5     | Execution and Commit                                                                   | 22 |

|        | 3.1.6     | Load/Store Unit                                                                        | 22 |

|        | 3.1.7     | Recovering from Branch Mispredictions                                                  | 23 |

| 3.2    | Morpl     | hCore Discussion                                                                       | 24 |

|        | 3.2.1     | Area and Power Overhead of MorphCore                                                   | 24 |

|        | 3.2.2     | Timing/Frequency Impact of MorphCore                                                   | 24 |

|        | 3.2.3     | Turning Off Structures in InOrder Mode                                                 | 25 |

|        | 3.2.4     | Interaction with OS                                                                    | 25 |

| Chapte | er 4. N   | Mode Switching Policy for Adapting to TLP and Evaluation                               | 26 |

| 4.1    | When      | to Operate in OutofOrder Mode or in InOrder Mode?                                      | 26 |

|        | 4.1.1     | Changing Mode from OutofOrder to InOrder                                               | 27 |

|        | 4.1.2     | Changing Mode from InOrder to OutofOrder                                               | 27 |

|        | 4.1.3     | Overhead of Changing the Mode                                                          | 28 |

|        | 4.1.4     | Handling Medium TLP                                                                    | 29 |

| 4.2    | Exper     | imental Methodology                                                                    | 29 |

|        | 4.2.1     | Workloads                                                                              | 31 |

| 4.3    | 3 Results |                                                                                        | 33 |

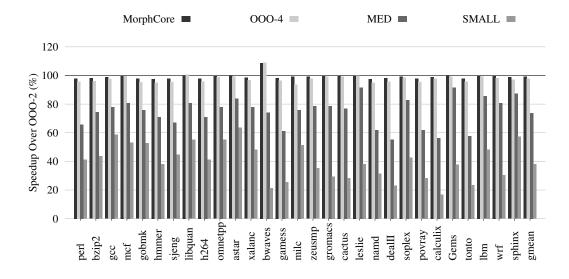

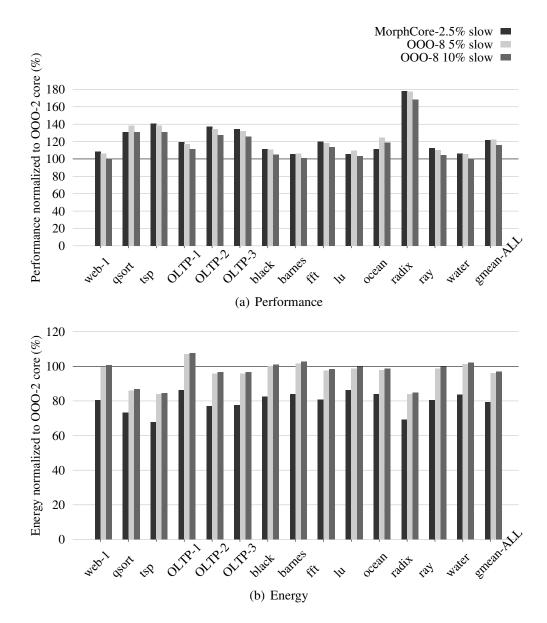

|        | 4.3.1     | Single-Thread Results                                                                  | 34 |

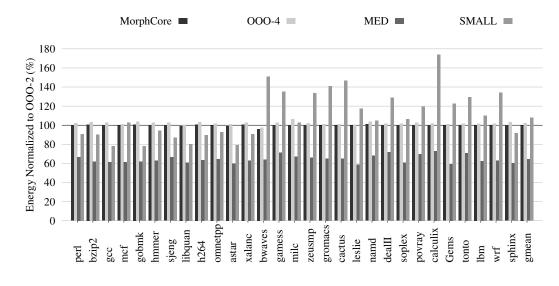

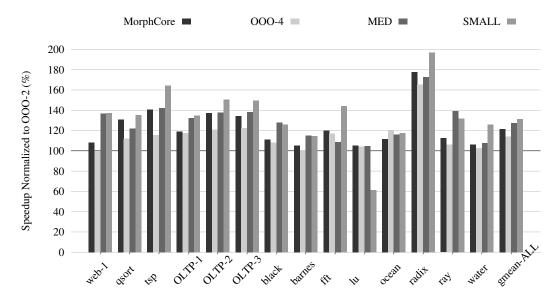

|        | 4.3.2     | Multi-Thread Results                                                                   | 37 |

|        | 4.3.3     | Single-thread and Multi-thread Results Summary                                         | 41 |

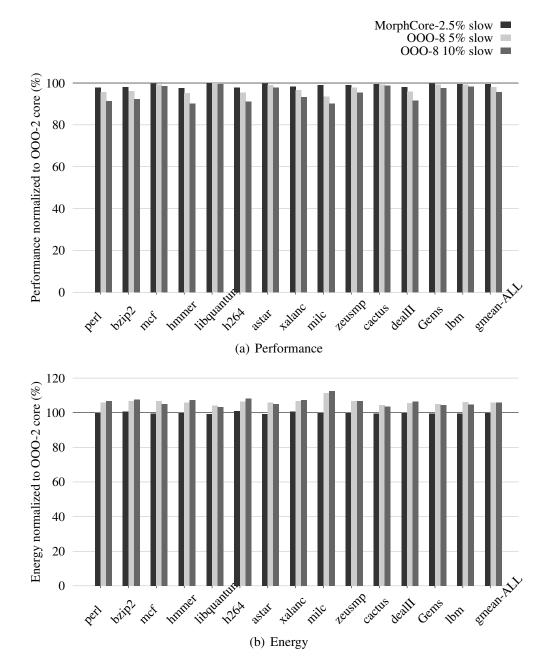

|        | 4.3.4     | Sensitivity of MorphCore's Results to Frequency Penalty                                | 41 |

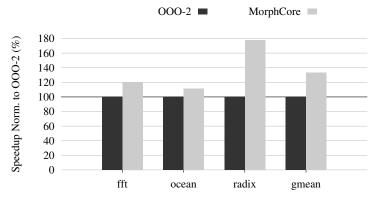

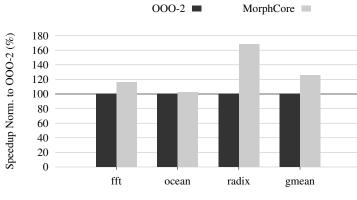

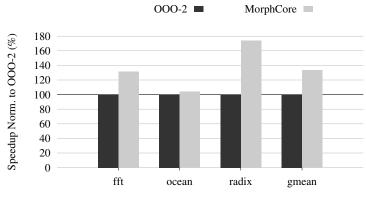

|        | 4.3.5     | Comparison with an 8-way SMT OOO Core                                                  | 42 |

|        | 4.3.6     | Effect of a Limited Capacity/Bandwidth Memory System                                   | 47 |

|        | 4.3.7     | Effect of Increasing the Superscalar Width                                             | 50 |

| Chapte | r 5. A    | Adapting to Instruction-Level Parallelism (ILP) and Memory-<br>Level Parallelism (MLP) | 52 |

| 5.1    | InOrd     | er Mode for Single-threaded Programs                                                   | 52 |

| 011    | 5.1.1     |                                                                                        | 53 |

| 5.2    |           | parchitectural Support                                                                 | 54 |

| 0.2    | 5.2.1     | Reducing the Superscalar Width                                                         | 55 |

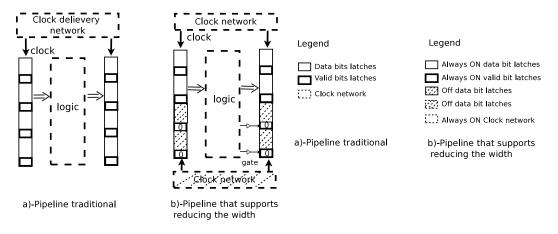

|        |           | 5.2.1.1 Pipeline Latches and the Clock Network                                         | 56 |

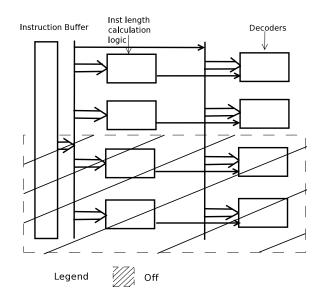

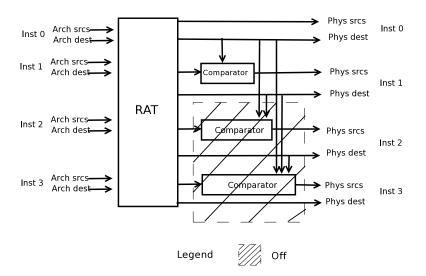

|        |           | 5.2.1.2 Decode, Rename and Execution Stages                                            | 57 |

|        | 5.2.2     | Reducing the OOO Window Size                                                           |    |

|        |           | $\mathbf{c}$                                                                           |    |

| Chapte | r6. N                                  | Mode Sw<br>ation                           | itching Policy for Adapting to ILP/MLP and Evalu-                    | 61       |  |

|--------|----------------------------------------|--------------------------------------------|----------------------------------------------------------------------|----------|--|

| 6.1    | MorphCore Procedure for Changing Modes |                                            |                                                                      | 61       |  |

| 6.2    |                                        | The Sampling-Based Mode Switching Policy   |                                                                      |          |  |

| 6.3    |                                        |                                            |                                                                      |          |  |

| 0.0    | 6.3.1                                  |                                            | ance-stats based policies                                            | 64<br>64 |  |

|        | 0.211                                  | 6.3.1.1                                    |                                                                      | 64       |  |

|        |                                        | 6.3.1.2                                    | Determining the width based on instructions issued                   |          |  |

|        |                                        | ( ) 1 )                                    | per cycle                                                            | 64       |  |

|        |                                        | 6.3.1.3                                    | Determining the width and window size based on branch mispredictions | 65       |  |

|        |                                        | 6.3.1.4                                    | Determining the window size based on ROB and RS occupation           | 65       |  |

|        | 6.3.2                                  | Reducir<br>Policies                        | ng the Overhead of Sampling with Signature-based                     | 65       |  |

|        |                                        |                                            | Code-based signature                                                 | 66       |  |

|        |                                        |                                            | Performance-stats based signature                                    | 66       |  |

| 6.4    | Evalu                                  |                                            | thodology                                                            | 66       |  |

| 6.5    |                                        |                                            |                                                                      | 68       |  |

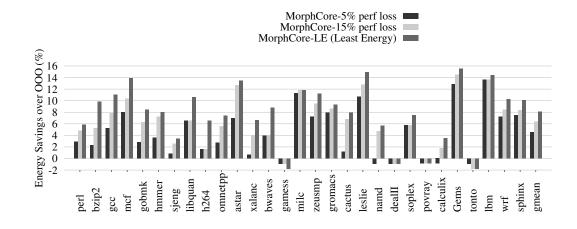

|        | 6.5.1                                  |                                            | Savings                                                              | 68       |  |

|        | 6.5.2                                  |                                            | s                                                                    | 69       |  |

|        | 6.5.3                                  |                                            | Switching Policy                                                     | 73       |  |

|        | 6.5.4                                  | Dynami                                     | c Voltage and Frequency Scaling                                      | 75       |  |

|        | 6.5.5                                  | Quantif                                    | ying the Frequency of Phase Changes                                  | 77       |  |

|        | 6.5.6                                  | Compar                                     | ison to Static Configurations                                        | 79       |  |

|        | 6.5.7                                  | Varying                                    | Only One Parameter (the Width or the Window Size)                    | 81       |  |

|        | 6.5.8                                  | Compar                                     | ison with the Cores Optimized for Low-Power                          | 84       |  |

| Chapte | r7. F                                  | Related V                                  | Vork                                                                 | 85       |  |

| 7.1    | Recor                                  | nfigurable                                 | e Cores                                                              | 85       |  |

| 7.2    | Heter                                  | Heterogeneous Chip-Multiprocessors         |                                                                      |          |  |

| 7.3    | Adapt                                  | Adapting a Core's Resources to ILP and MLP |                                                                      |          |  |

| 7.4    | Techn                                  | iques to S                                 | Scale a Core's Performance and Energy                                | 89       |  |

|        | 7.4.1                                  | Dynami                                     | c Voltage and Frequency Scaling                                      | 89       |  |

|        | 7.4.2                                  | Simulta                                    | neous Multi-Threading                                                | 89       |  |

| Chapte |                                        | Conclusio                                  |                                                                      | 90       |  |

| 8.1    | Summary                                |                                            |                                                                      | 90       |  |

| 8.2    | Limitations and Future Work            |                                            |                                                                      | 90       |  |

## Bibliography

## List of Tables

| 4.1 | Configuration of the simulated machine     | 30 |

|-----|--------------------------------------------|----|

| 4.2 | Characteristics of Evaluated Architectures | 32 |

| 4.3 | Throughput of Evaluated Architectures      | 32 |

| 4.4 | Details of the simulated workloads         | 33 |

| 4.5 | Micro-op throughput (uops/cycle) on OOO-2  | 38 |

| 6.1 | Configuration of the simulated machine     | 67 |

# **List of Figures**

| 2.1  | Out-of-Order core microarchitecture                                                                                                                   |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2  | Fraction of energy spent on different hardware resources 8                                                                                            |

| 2.3  | Performance of black with SMT 9                                                                                                                       |

| 2.4  | Fraction of energy per instruction spent on different hardware re-<br>sources                                                                         |

| 2.5  | Performance of cores with different widths and execution substrates. 12                                                                               |

| 2.6  | Overview of MorphCore modes when it adapts to ILP and MLP.<br>In (b)-(e), Solid boxes are ON, dotted and shaded boxes are turned<br>OFF.              |

|      | 011                                                                                                                                                   |

| 3.1  | The MorphCore microarchitecture                                                                                                                       |

| 3.2  | Microarchitecture of the Fetch stage                                                                                                                  |

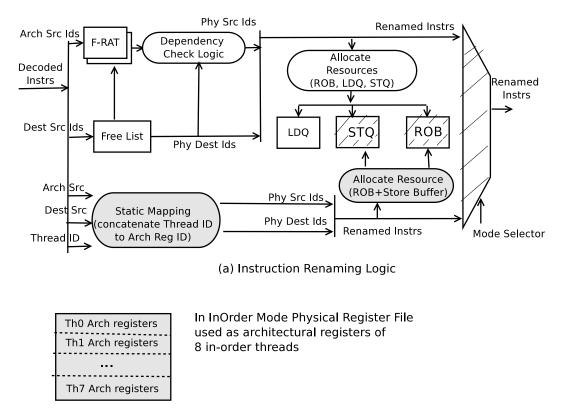

| 3.3  | Microarchitecture of the Rename stage                                                                                                                 |

| 3.4  | Microarchitecture of the Rename stage                                                                                                                 |

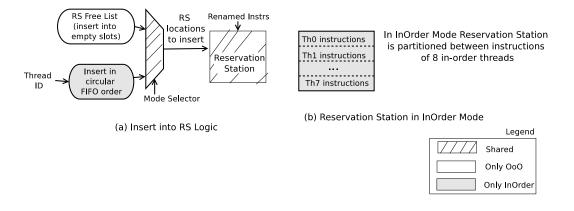

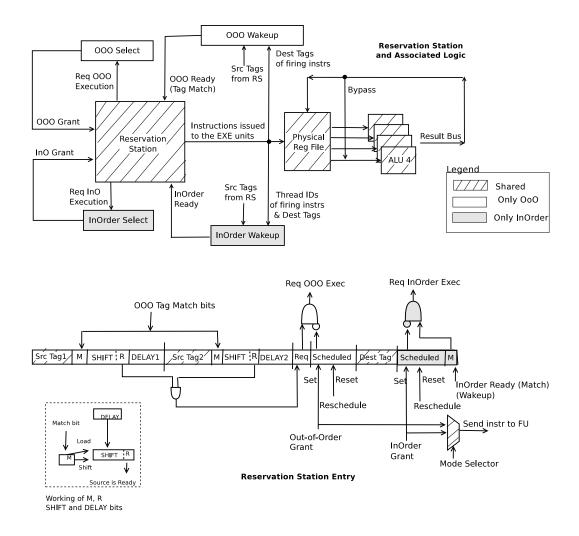

| 3.5  | MorphCore Wakeup and Selection Logic                                                                                                                  |

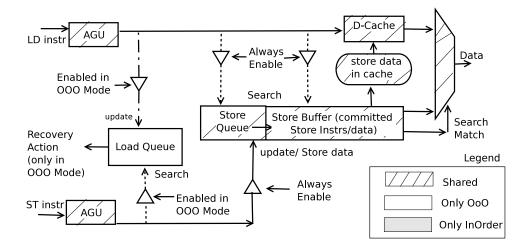

| 3.6  | Load / Store unit                                                                                                                                     |

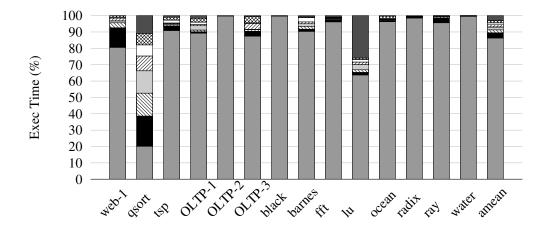

| 4.1  | Percentage of execution time depending on the number of active threads                                                                                |

| 4.2  | Single-thread performance results                                                                                                                     |

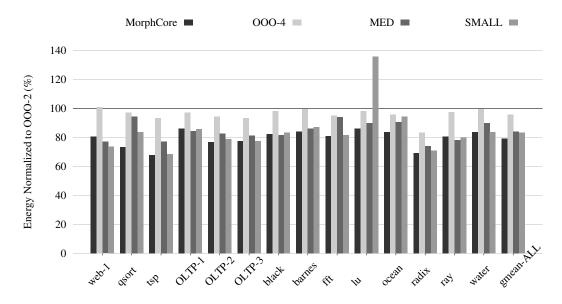

| 4.3  | Single-thread energy results                                                                                                                          |

| 4.4  | Multi-thread performance results                                                                                                                      |

| 4.5  | Multi-thread energy results                                                                                                                           |

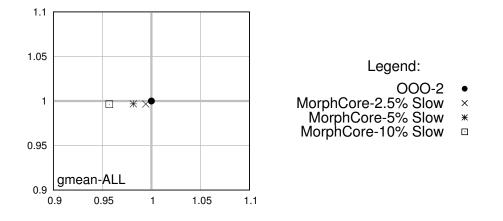

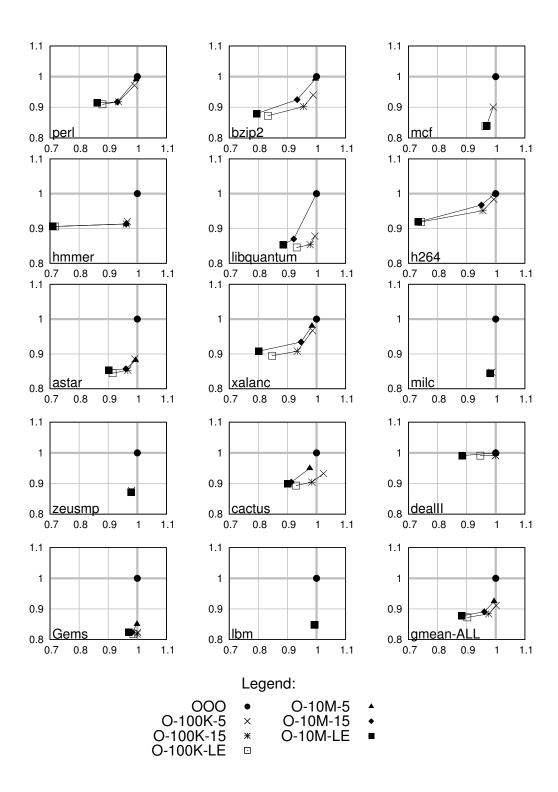

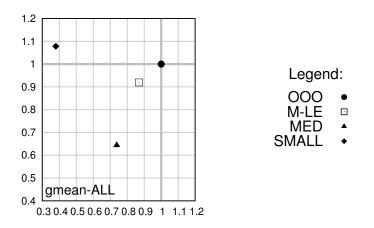

| 4.6  | Single-Thread performance-energy trade-off of MorphCore's fre-<br>quency penalty. x-axis is performance and y-axis is energy normal-<br>ized to OOO-2 |

| 4.7  | Multi-Thread performance-energy trade-off of MorphCore's frequency penalty. x-axis is performance and y-axis is energy normalized to OOO-2            |

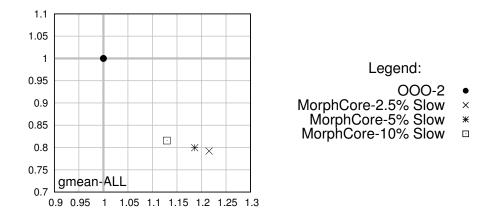

| 4.8  | Single-Thread performance and energy of MorphCore vs. 8-way<br>SMT OOO core                                                                           |

| 4.9  | Multi-Thread performance and energy of MorphCore vs. 8-way<br>SMT OOO core                                                                            |

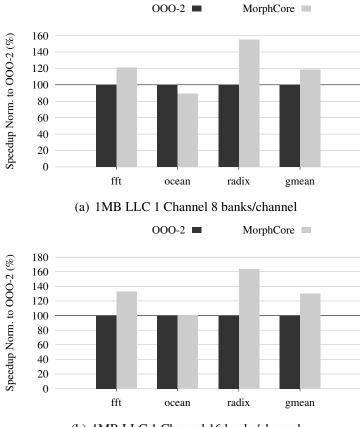

| 4.10 | Effect of Mem system parameters                                                                                                                       |

| 4.11 | Effect of Mem system parameters (contd.)                                                                                                                                                                              | 49 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

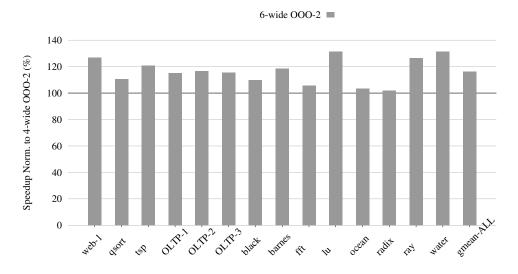

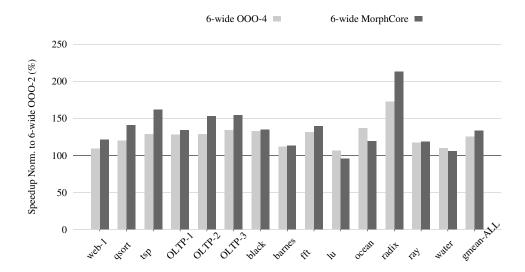

| 4.12 | Benefit of increasing the width for the baseline OOO-2 core                                                                                                                                                           | 51 |

| 4.13 | Sensitivity to the issue width showing benefit of the increased width for OOO-4 and MorphCore                                                                                                                         | 51 |

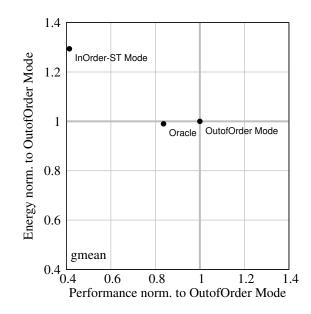

| 5.1  | Performance-energy trade-off of various operating points. Averaged over all SPEC 2006 benchmarks                                                                                                                      | 54 |

| 5.2  | The MorphCore microarchitecture with the ability to reduce width and window size                                                                                                                                      | 55 |

| 5.3  | Turning off pipeline latches and clock network                                                                                                                                                                        | 56 |

| 5.4  | Turning off half of instruction length detection logic and decoders                                                                                                                                                   | 57 |

| 5.5  | Turning off half of the dependency check logic in the Rename stage.                                                                                                                                                   | 58 |

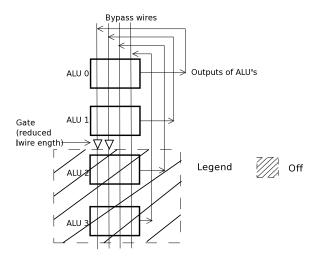

| 5.6  | Turning off execution units and bypass wires                                                                                                                                                                          | 58 |

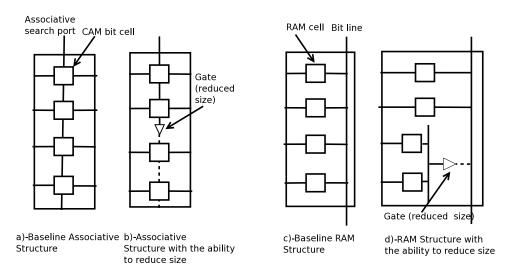

| 5.7  | Associative (CAM) and indexed (RAM) structures that support re-<br>ducing the size at runtime                                                                                                                         | 59 |

| 6.1  | Sampling-based mode switching policy                                                                                                                                                                                  | 62 |

| 6.2  | Energy-efficiency of MorphCore over OOO core.                                                                                                                                                                         | 69 |

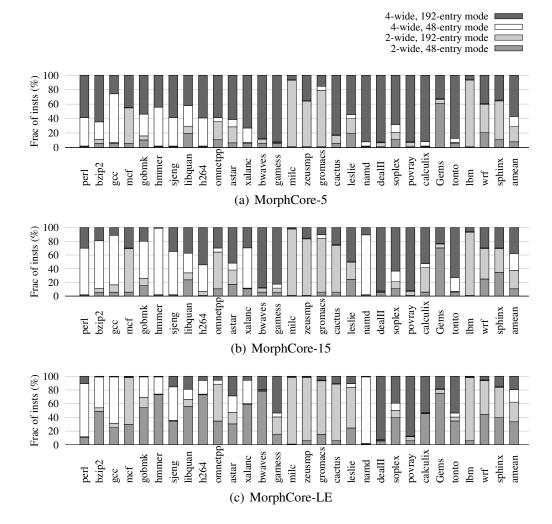

| 6.3  | MorphCore's modes coverage (fraction of instructions executed)                                                                                                                                                        | 71 |

| 6.4  | Performance-energy trade-off of various MorphCore's configura-<br>tions for several SPEC2006 benchmarks. X-axis is performance<br>and Y-axis is energy consumption normalized to OOO core                             | 72 |

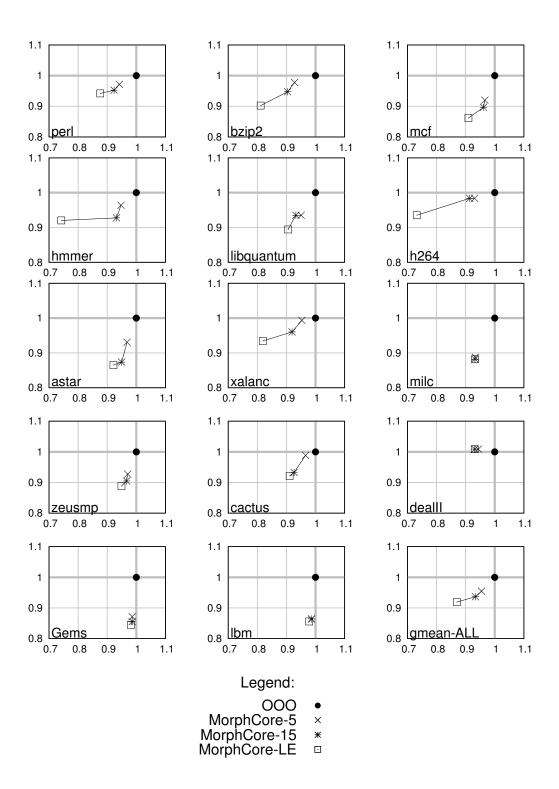

| 6.5  | Performance-energy trade-off of MorphCore with M=Sampling and O=Oracle mode switching policies. X-axis is performance and Y-axis is energy consumption normalized to OOO core.                                        | 74 |

| 6.6  | Performance-energy trade-off of OOO only-frequency scaling vs.<br>MorphCore. M=MorphCore, S=Slowed-down OOO, 5%, 10%, and<br>20%. X-axis is performance and Y-axis is energy consumption nor-<br>malized to OOO core. | 76 |

| 6.7  | Performance-energy trade-off of Oracle policies with different in-<br>terval sizes. X-axis is performance and Y-axis is energy consump-<br>tion normalized to OOO.                                                    | 78 |

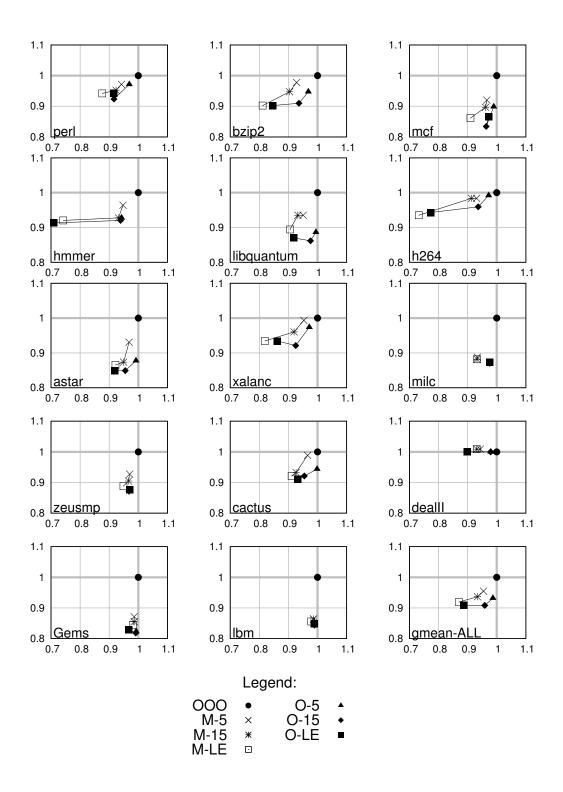

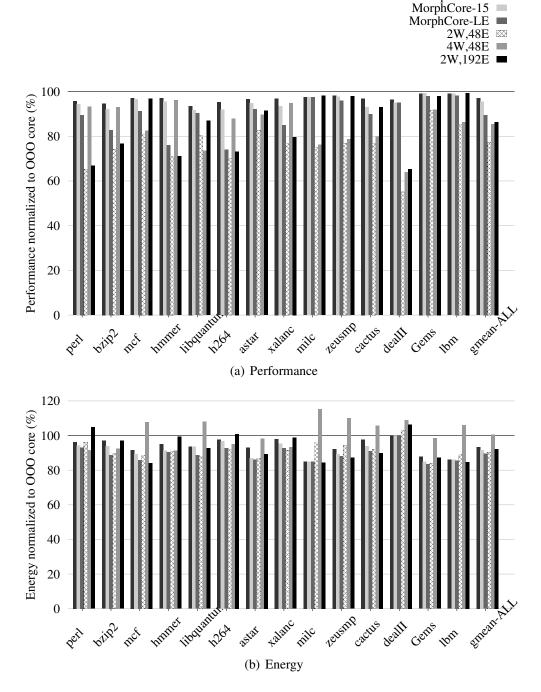

| 6.8  | Performance and energy of MorphCore compared to 3 static config-<br>urations. Three static configurations: MorphCore always executing<br>in 2W,48E mode, 4W,48E mode, and in 2W,192E mode.                            | 80 |

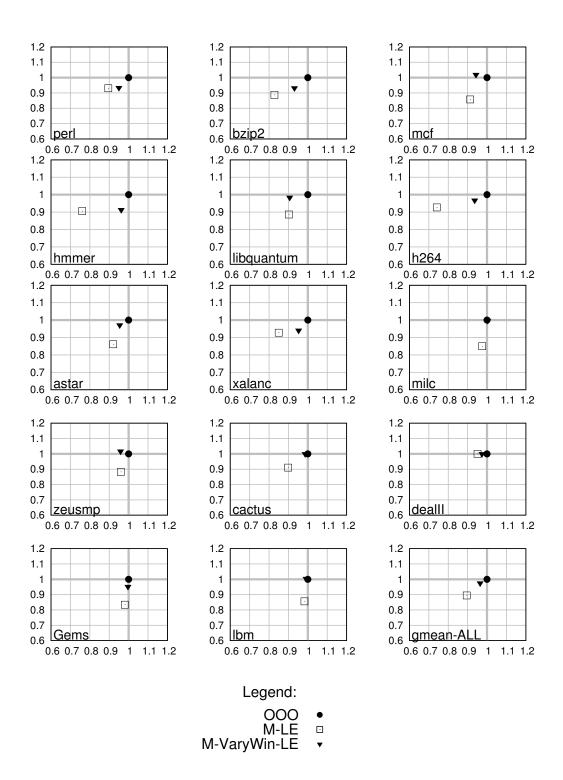

| 6.9  | Performance-Energy trade-off of varying only OOO window size.<br>X-axis is performance and Y-axis is energy normalized to OOO core.                                                                                   | 82 |

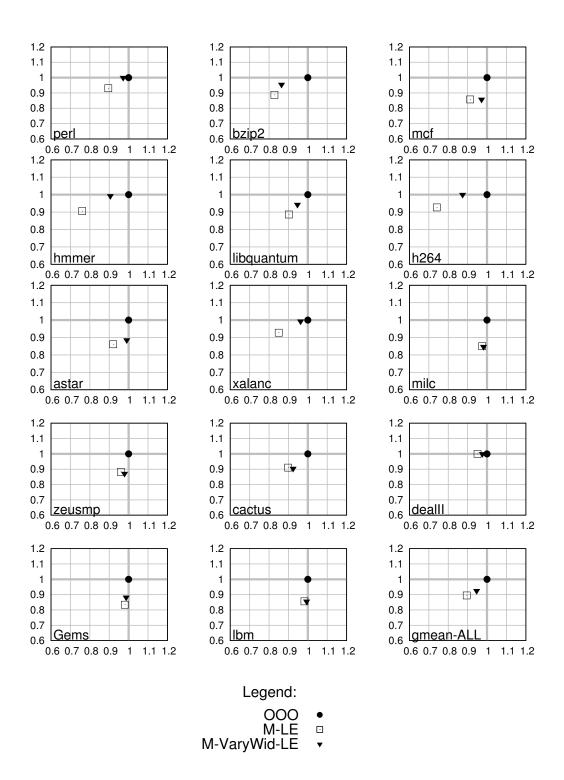

| 6.10 | Performance-Energy trade-off of varying only superscalar width. X-axis is performance and Y-axis is energy normalized to OOO core.                                                                                    | 83 |

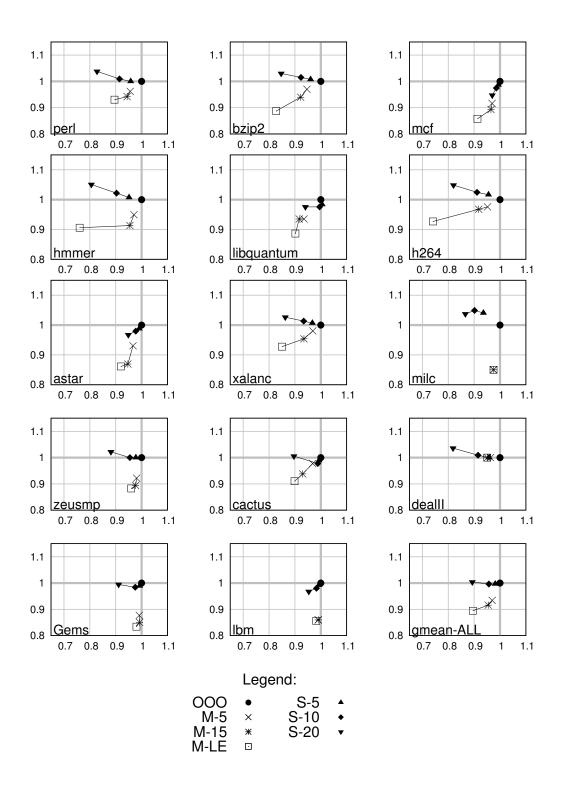

| 6.11 | Performance-Energy trade-off of MorphCore-LE vs. cores that are<br>optimized for low-power. X-axis is performance and Y-axis is en-<br>ergy normalized to OOO.                                                        | 84 |

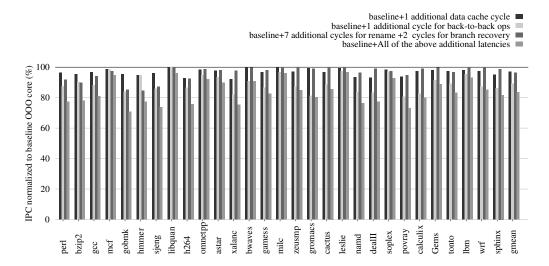

| 7.1  | Effect of increasing latencies on an OOO core performance                                                                                                                                                             | 86 |

## **Chapter 1**

### Introduction

#### 1.1 The Problem

The level of Thread-Level-Parallelism (TLP), Instruction-Level-Parallelism (ILP), and Memory-Level Parallelism (MLP) varies across programs and program phases. Within a single program TLP is defined as the number of concurrently active threads. A thread is active when it is not waiting for a synchronization event. TLP varies at run-time because of software requirements but also due to inter-thread synchronization. The two other factors, ILP and MLP are defined similarly. ILP is defined as the number of instructions executed in parallel, and MLP is defined as the number of memory requests issued in parallel. Within a single thread of execution, ILP and MLP often vary across programs and program phases because of the inherent structure of the programs and input set dependencies. Traditional core microarchitectures do not dynamically adapt to the changes in TLP, ILP, and MLP available in programs. This leads to wasted opportunity and inefficiency.

**Inefficiency by not adapting to TLP.** Today's cores do not dynamically adapt to changes in the TLP. In general, industry builds two types of cores: large out-of-order cores (e.g., Intel's Haswell, IBM's Power 8), and small (either inorder or small out-of-order) cores (e.g., Intel's MIC a.k.a Xeon Phi, Sun's Niagara, ARM's A15).

Large out-of-order (OOO) cores can provide high single-thread performance by exploiting available ILP and MLP, but they are energy-inefficient for multithreaded programs because they unnecessarily waste energy on exploiting ILP and MLP instead of leveraging the available TLP. In contrast, small cores do not waste energy on wide superscalar OOO execution, but rather provide high parallel throughput at the cost of poor single thread performance.

Heterogeneous (or Asymmetric) Chip Multiprocessors (ACMPs) [24, 25, 12, 29, 38] have been proposed to handle this software diversity. ACMPs provide one or few large cores for speedy execution of single-threaded programs and many small cores for high throughput in multi-threaded programs. Unfortunately, ACMPs require that the number of large and small cores be fixed at design time, which inhibits adaptability to varying degrees of software TLP.

To overcome the limitation of ACMPs, researchers have proposed CoreFusionlike architectures [19, 3, 21, 34, 33, 44, 10, 11]. They propose a chip with small cores to provide high throughput performance in multi-threaded programs. These small cores can dynamically "fuse" into a large core when executing single-threaded programs. Unfortunately, the fused large core has low performance and high energy consumption compared to a traditional out-of-order core for two reasons: 1) there are additional latencies between the pipeline stages of the fused core, thus increasing the latencies of the core's "critical loops", and 2) mode switching requires instruction cache flushes and incurs the cost of data migration between the data caches of small cores.

**Inefficiency by not adapting to ILP and MLP.** Large out-of-order (OOO) cores provide high single thread performance only when the program has high ILP/MLP; these cores waste energy on trying to exploit ILP/MLP when the program's inherent structure does not exhibit it. On the other hand, small cores' single thread performance is always low irrespective of the availability of ILP/MLP in the program.

Previously, researchers have proposed adapting a large core's resources to ILP and MLP in order to save energy. All of these proposals focus on adapting only one resource of the core to the requirements of the program. These proposals include varying only the number of functional units that are enabled [2, 28, 16], the size of the instruction queue [5, 6], the size of the OOO window [32], and the width of the core [31]. However, variation in ILP and MLP puts different requirements

on different structures of the core simultaneously. Thus, varying only one resource does not provide optimal energy efficiency.

#### **1.2** The Solution

To overcome the limitations of previous research, I propose MorphCore, an adaptive core microarchitecture that efficiently adapts at runtime to changes in TLP, ILP, and MLP in programs. The key insight behind MorphCore is that a traditional large OOO core can be minimally modified to design a microarchitecture that adapts to these changes and provides high performance and/or energy efficiency. We do so by designing and operating the MorphCore such that it efficiently increases the utilization of the large structures that are ON (increasing performance), and maximizes the number of structures that could be turned OFF (increasing energy efficiency). MorphCore provides five efficient and low-power operating modes: a highly-threaded in-order SMT mode, and four out-of-order modes with different superscalar widths and out-of-order window sizes. We describe how MorphCore adapts to TLP, ILP, and MLP below.

Adapting to TLP. MorphCore takes the opposite approach of previously proposed reconfigurable cores. Rather than fusing small cores into a single large core, MorphCore uses a large out-of-order core as the base substrate and adds the capability of in-order SMT to efficiently exploit highly parallel code when available. MorphCore switches between two of the five available modes to adapt to TLP. The two modes are OutOfOrder (one of the four out-of-order modes) and InOrder. In OutOfOrder mode, MorphCore provides the single-thread performance of a traditional out-of-order core with minimal performance degradation. However, when TLP is available, MorphCore switches into InOrder mode and operates as a highly-threaded in-order SMT core. This reduces execution time by exploiting TLP, and reduces energy consumption by turning off several high-energy structures (e.g., renaming logic, out-of-order scheduling, and the load queue) while in InOrder mode.

Adapting to ILP and MLP. MorphCore adapts (varies) the superscalar width and the OOO window size at runtime to match program behavior. It switches between the four out-of-order modes to adapt to ILP/MLP. Our design is influenced by two factors: 1) core's width and window size are the two major sources of energy consumption, and 2) we observe that width/window size need to be managed simultaneously as different programs require different width/window settings for optimal performance and energy.

#### **1.3** Thesis Statement

An out-of-order core microarchitecture can be modified to operate in five modes, as 1) a 4-wide 192-entry OOO core, 2) a 4-wide 48-entry OOO core, 3) a 2-wide 48-entry OOO core, 4) a 2-wide 192-entry OOO core, and 5) a 4-wide 8-way-threaded in-order SMT core, resulting in a core than can adapt dynamically to ILP, MLP, and TLP present in programs and provide higher performance and energy efficiency than traditional non-adaptive cores.

#### **1.4 Contributions**

My dissertation develops the MorphCore microarchitecture and makes the following contributions:

- It proposes the MorphCore microarchitecture that efficiently adapts to the TLP available in programs by operating as a big-width large-OOO-window core when TLP is low and ILP is high, and as a high-performance but lowerenergy highly-threaded in-order SMT core when TLP is high. This thesis describes in detail the microarchitecture of MorphCore that adapts to TLP, shows how only minimal changes to a traditional OOO core are required to provide the hardware support for the two modes, and shows how in-order SMT mode provides high performance and energy savings when TLP is high.

- 2. It quantitatively compares MorphCore to small, medium and large core ar-

chitectures in terms of performance and energy efficiency on single-threaded and multi-threaded programs.

- 3. It describes a MorphCore microarchitecture that efficiently adapts to ILP and MLP present in programs by varying the superscalar width and the OOO window size, and by operating in four out-of-order modes: (1) as a big-width large-OOO-window core, 2) as a big-width medium-OOO-window core, 3) as a medium-width large-OOO-window core, and 4) as a medium-width medium-OOO-window core.

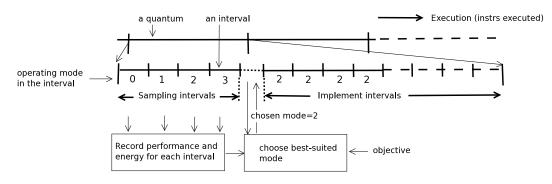

- 4. It proposes a simple and effective sampling-based mode switching policy for adapting to ILP and MLP. The policy periodically samples the performance and energy of each of the four out-of-order operating modes, and chooses the width/window size that will lead to the desired goal of performance or energy efficiency. We show that this policy is able to closely match the benefit of an oracle switching policy.

- 5. It presents the low-overhead microarchitectural support required to incorporate the five modes in a traditional large OOO core.

#### **1.5** Dissertation Organization

This dissertation is organized as follows. Chapter 2 provides the background and motivation for the work, and an overview of the MorphCore microarchitecture. Chapter 3 describes the design of MorphCore's operating modes to adapt to TLP. Chapter 4 presents our mode switching policy for adapting to TLP, and evaluates the design. Chapter 5 describes the design of MorphCore's operating modes to adapt to ILP and MLP. Chapter 6 describes our mode switching policy for adapting to ILP and MLP, and evaluates the design. Chapter 7 describes related work. Chapter 8 summarizes my results and suggests avenues for future work.

## Chapter 2

### **Overview of MorphCore Architecture**

#### 2.1 Baseline Large OOO Core

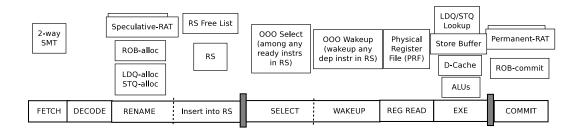

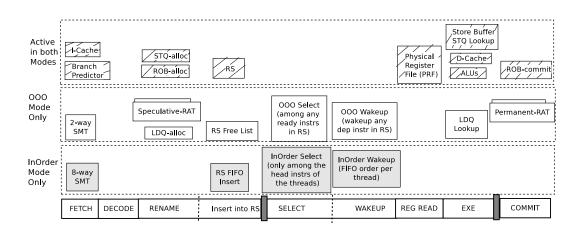

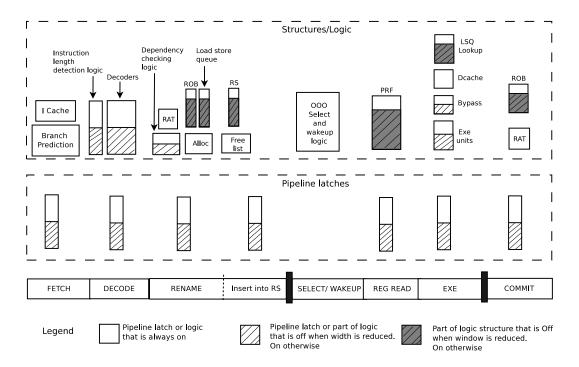

Out-of-order (OOO) cores provide better performance than in-order cores by executing instructions as soon as their operands become available, rather than executing them in program order. Figure 2.1 shows a high-level layout of a 2-way SMT OOO core pipeline, including the major structures accessed and functionality performed in different stages of the pipeline. We describe a Pentium-4 like architecture [35], where the data, both speculative and architectural, is stored in the Physical Register File (PRF), and the per-thread Register Alias Table (RAT) entries point to PRF entries. The front-end Speculative-RAT points to the speculative state, and a back-end Permanent-RAT points to the architectural state. The front-end of the pipeline (from the Fetch stage until the Insert into Reservation Station (RS)) works in-order. Instructions are fetched, decoded, and sent to the Rename Stage. The Rename stage renames (i.e. maps) the architectural source and destination register IDs into Physical Register File IDs by reading the Speculative-RAT of the thread for which instructions are being renamed, and inserts the instructions into the Reservation Station (also referred to as the Issue Queue).

Instructions wait in the Reservation Station until they are selected for execution by the Select stage. The Select stage selects an instruction for execution once all of the source operands of the instruction are ready, and the instruction is the oldest among the ready instructions. When an instruction is selected for execution, it readies its dependent instructions via the Wakeup Logic block, reads its source operands from the PRF, and executes in a Functional Unit. After execution, an instruction's result is broadcast on the Bypass Network, so that any dependent

Figure 2.1: Out-of-Order core microarchitecture

instruction can use it immediately. The result is also written into the PRF, and the instruction updates its ROB status. The instruction retires once it reaches the head of the ROB, and updates the corresponding Permanent-RAT.

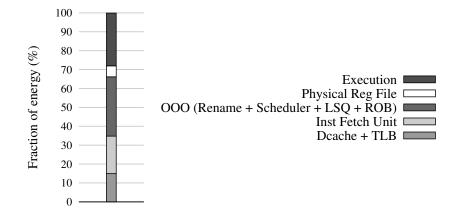

#### 2.1.1 Energy Cost of OOO Execution

Unfortunately, the single-thread performance benefit of the large OOO core comes with a large energy penalty. As shown in Figure 2.2, a significant fraction (28%) of total core energy is spent on structures that support OOO execution. The core is 4-wide 192-entry OOO. The energy is estimated using a modified version of McPAT [26], and is averaged over all SPEC 2006 programs. I have modified McPAT to better estimate the energy consumption because of SMT and clock's dynamic activity, and to report energy of different core structures at a finer grain level. This overhead exists to exploit ILP and MLP to increase core throughput, and is justified when the software has high ILP or MLP. However, when multiple threads of execution exist, the core can be efficiently utilized using in-order Simultaneous Multi-Threading (SMT).

Figure 2.2: Fraction of energy spent on different hardware resources

#### 2.2 Adapting to TLP

Simultaneous Multi-Threading (SMT) [14, 47, 42] is a technique to improve the utilization of execution resources using multiple threads provided by the software. In SMT, a core executes instructions from multiple threads concurrently. Every cycle, the core picks a thread from potentially many ready threads, and fetches instructions from that thread. The instructions are then decoded and renamed in a regular pipelined fashion and inserted into a common (shared among all the threads) Reservation Station (RS). Since instructions from multiple candidate threads are available in the RS, the possibility of finding ready instructions increases. Thus, SMT cores can achieve higher throughput provided that software exposes multiple threads to the hardware.

#### 2.2.1 The Potential of In-Order SMT

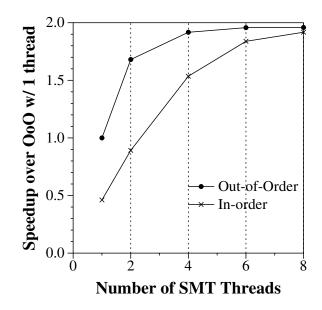

The observation that a highly multi-threaded in-order core can achieve the instruction issue throughput similar to an OOO core was noted by Hily and Seznec [13]. We build on this insight to design a core that can achieve high-performance and low-energy consumption when software parallelism is available.

Figure 2.3 shows the performance of the workload black (Black-Scholes pricing [30]) on an out-of-order and an in-order core. For this experiment, both

Figure 2.3: Performance of black with SMT

of the cores are similarly sized in terms of cache sizes, pipeline widths (4-wide superscalar) and depths (refer to Section 4.2 for experimental methodology). The performance of the in-order core is significantly less than the performance of the out-of-order core when both cores run only a single thread. As the number of SMT threads increases from 1 to 8, the performance of the out-of-order core increases significantly at 2 threads, but starts to saturate at 4 threads, because the performance of the in-order core continues to benefit from more threads (which allows it to better tolerate long latency operations and memory accesses). When the number of threads is equal to 8, the in-order core's performance begins to match the performance of the out-of-order core. This experiment shows that when high thread-level parallelism is available, high performance and low energy consumption can be achieved with in-order SMT execution; therefore the core does not require the complex and power hungry structures necessary for out-of-order SMT execution.

#### 2.2.2 Repurposing Core's Resources

A key insight behind MorphCore's design is that a highly-threaded in-order SMT core can be built using a subset of the hardware required to build an aggressive out-of-order core. For example, we use the Physical Register File (PRF) in the outof-order core as the architectural register files for the many SMT threads in InOrder mode. Similarly, we use the Reservation Station entries as an in-order instruction buffer and the execution pipeline of the out-of-order core as-is. This efficiently increases the utilization of the core's resources and increases both performance and energy efficiency.

#### 2.2.3 Operating Modes

In spite of its high energy cost, out-of-order execution is still desirable because it provides significant performance improvement over in-order execution. Thus, if we want high single-thread performance we must maintain support for out-of-order execution. However, when software parallelism is available, we can efficiently provide performance by using in-order SMT and not waste energy on out-of-order execution. To accomplish both, we propose the two operating modes of MorphCore: OutofOrder and InOrder. In OutofOrder mode, MorphCore works exactly like a traditional out-of-order core. In InOrder mode, MorphCore supports additional in-order SMT threads, and in-order scheduling, execution, and commit of simultaneously running threads.

#### 2.3 Adapting to ILP and MLP

Single thread performance and energy efficiency are both key to any modern general-purpose core design. Architects in industry are trying to maximize performance without increasing energy consumption. Industry is increasing single thread performance by increasing the superscalar width and the OOO window size. Increasing width increases the number of instructions that are fetched, decoded, renamed and allocated per cycle, so that more and more instructions are exposed to the execution engine (which also has the ability to execute and commit at an increased rate), potentially increasing the ILP and thus the performance. Increasing the OOO window size increases the number of "in-flight" instructions by increasing the number of ROB, Physical Register file (PRF), load/store queue (LSQ) and scheduler (RS) entries. This increases the microprocessor's ability to tolerate latencies, as well as its ability to expose parallel cache misses (known as Memory-Level Parallelism or MLP), both of which increase performance.

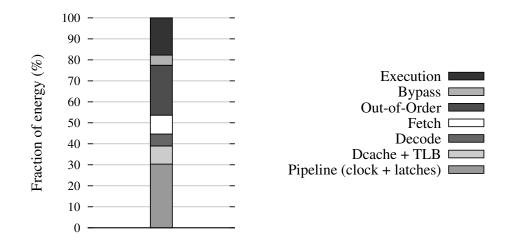

Figure 2.4: Fraction of energy per instruction spent on different hardware resources

#### 2.3.1 Energy Cost of Wide Width

These high performance features cost significant energy consumption. Figure 2.4 shows the fraction of Energy Per Instruction (EPI) spent on different hardware structures of a 4-wide 192-entry ROB OOO core (averaged over all SPEC 2006 programs). Energy is estimated using a modified version of McPAT 0.8 [26]. The two biggest sources of energy consumption are out-of-order execution structures (Rename, ROB, PRF, LSQ, and RS) and deep and wide pipeline (more specifically, pipeline latches and clock network). A deep pipeline enables high frequency operation, and a wider pipeline improves instruction throughput per cycle.

#### 2.3.2 Problem: Different Programs Benefit Differently from Wide Width and/or Large OOO Window

Increasing pipeline width and OOO window size benefits different workloads differently. For example, compute bound workloads can benefit from a wider pipeline as well as a larger window, however, memory bound workloads only benefit from a larger window size, if at all.

Figure 2.5: Performance of cores with different widths and execution substrates.

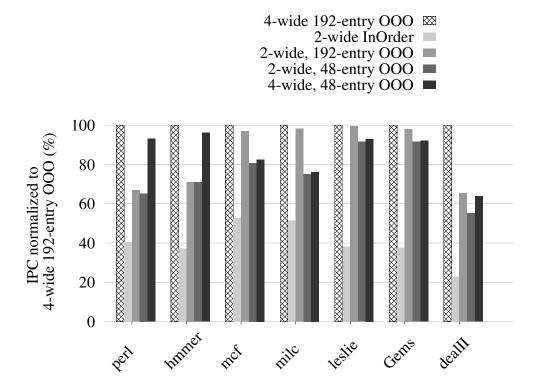

Figure 2.5 plots performance of four different less aggressive core configurations for seven SPEC2006 benchmarks normalized to a large more aggressive OOO core (4-wide and 192-entry OOO window). The four less aggressive core configurations are: a 2-wide in-order, a 2-wide 192-entry OOO, a 2-wide 48-entry OOO, and a 4-wide 48-entry OOO. The memory hierarchy is the same across all core configurations. Note that the 2-wide InOrder core loses performance significantly on all 7 benchmarks. The experiment also shows that wide width and large OOO window do not always help to increase performance significantly. For example, all workloads shown in Figure 2.5 except dealII can obtain performance close to a wide width, large OOO window core when they are run on a less aggressive core (either with a reduced width or with a reduced window or with both reduced width and reduced window). We discuss each of these applications in detail.

The benchmarks perl and hmmer can get high performance on a 4-wide 48-entry OOO core because they have short latency operations and high ILP. Such workloads need big width to exploit high ILP but do not need a big window to get high performance since instructions have short latencies and they drain quickly from the window. Thus, we conclude that for programs like perl and hmmer, a 4-wide 48-entry OOO core can provide a good balance between performance and energy consumption.

The benchmarks mcf and milc can get performance close to the big OOO core on a 2-wide, 192-entry OOO core because they are heavily memory-bound with high MLP, thus they need a large window to expose parallel memory misses and obtain performance. These programs do not need a wide width because the performance is memory-limited and the rate at which instructions are brought in into the window and executed does not matter. Thus, we conclude that for programs like mcf and milc, a 2-wide 192-entry OOO core can provide a good balance between performance and energy consumption.

The benchmarks leslie and Gems achieve performance close to that of a big OOO core even on a 2-wide, 48-entry OOO core. leslie is memory-bound with high MLP, but even a medium-sized window is able to expose the available MLP. Gems has very little ILP or MLP, thus it does not need wide width or large window. Thus, we conclude that for programs like leslie and Gems, a 2-wide 48-entry OOO core can provide a good balance between performance and energy consumption.

In summary, for the above mentioned programs, wide width and/or a large window do not create a performance gain; even a less aggressive core (either with reduced-width, or with reduced-window, or with reduced-window and reducedwidth) can provide performance close to a big OOO core. For such workloads, hardware supported wide width and large OOO window is inefficient.

Finally, dealII is an example of a program that needs a wide width and a large window to achieve high performance. dealII's instructions on average have longer latencies, and thus, a small window stalls frequently. With a large window, the instruction stream exposes high ILP, which makes it possible to get a significant performance boost with a wider core.

The data presented in Figures 2.4 and 2.5 motivates the need for an adaptive out-of-order core that dynamically varies its width and window to the needs of the program in order to achieve a balance between high performance and energy efficiency.

#### 2.3.3 Our Solution: Dynamically Vary Width and Window Size

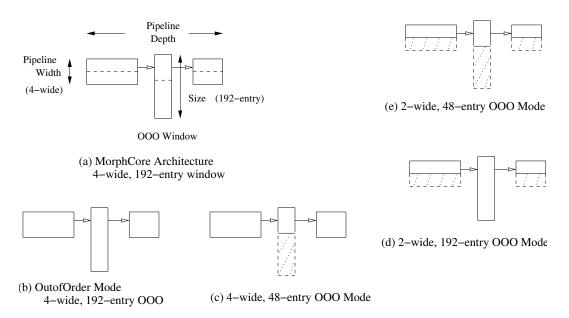

Figure 2.6: Overview of MorphCore modes when it adapts to ILP and MLP. In (b)-(e), Solid boxes are ON, dotted and shaded boxes are turned OFF.

The MorphCore microarchitecture can adapt to the resource needs of different programs or program phases by changing superscalar pipeline width and OOO window size. Figure 2.6 (a) shows the MorphCore microarchitecture. It supports wide superscalar width and large OOO execution window. In addition, it also has microarchitectural support for reducing the pipeline width and the window size (shown with dotted lines). Because MorphCore can vary two parameters, width and window, MorphCore provides four out-of-order operating modes as shown in Figure 2.6 (b)-(e). The modes are: 4-wide 192-entry OOO, 4-wide 48-entry OOO, 2-wide 192-entry OOO, and 2-wide 48-entry OOO. The 4-wide 192-entry OOO mode is the fully-provisioned high-power and high-performance mode, whereas the other three modes are "low-provisioned" low-power low-performance modes.

Our goal with the MorphCore microarchitecture is to provide high performance and, when needed, energy efficiency for single-threaded programs. MorphCore continuously monitors the executing workload and makes intelligent decisions to change the width and the window size. It employs a simple yet effective sampling-based mode switching policy that periodically samples the performance and energy of each of the four out-of-order operating modes, and chooses the width/window size that will lead to the desired goal of performance or energy efficiency.

### **Chapter 3**

### Adapting to Thread-Level Parallelism (TLP)

#### 3.1 MorphCore Microarchitecture

#### 3.1.1 Overview

The MorphCore microarchitecture is based on a traditional OOO core. Figure 3.1 shows the changes that are made to a baseline OOO core (shown in Figure 2.1) to build the MorphCore. MorphCore provides two operating modes to adapt to TLP: OutofOrder and InOrder. The figure shows the blocks that are active in both modes, and the blocks that are active only in one of the modes. In addition to out-of-order execution, MorphCore supports additional in-order SMT threads, and in-order scheduling, execution, and commit of simultaneously running threads in InOrder mode. In OutofOrder mode, MorphCore works exactly like a traditional out-of-order core.

Figure 3.1: The MorphCore microarchitecture

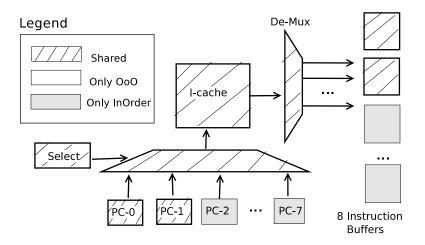

#### **3.1.2** Fetch and Decode Stages.

The Fetch and Decode Stages of MorphCore work exactly like an SMTenabled traditional OOO core. Figure 3.2 shows the Fetch Stage of the MorphCore. MorphCore adds 6 additional SMT contexts to the baseline core. Each context consists of a PC, a branch history register, and a Return Address Stack. In OutofOrder mode, only 2 of the SMT contexts are active. In InOrder mode, all 8 contexts are active. The branch predictor and the I-Cache are active in both modes.

Figure 3.2: Microarchitecture of the Fetch stage

#### 3.1.3 Rename Stage

Figure 3.3 shows the Rename Stage of the MorphCore. InOrder renaming is substantially simpler, and thus more power-efficient, than OOO renaming. In In-Order mode, we use the Physical Register File (PRF) to store the architectural registers of the multiple in-order SMT threads: we logically divide the PRF into multiple fixed-size partitions where each partition stores the architectural register state of a thread (Figure 3.3(b)). Hence, the architectural register IDs can be mapped to the Physical Register IDs by simply concatenating the Thread ID with the architectural register ID. This approach limits the number of in-order SMT threads that the MorphCore can support to *num\_physical\_registers/num\_architectural\_registers*.

(b) Physical Register File in InOrder Mode

Figure 3.3: Microarchitecture of the Rename stage

However, the number of physical registers in today's cores is already large enough (and increasing) to support 8 in-order SMT threads which is sufficient to match the out-of-order core's performance. For the x86 ISA [17] that we model in our simulator, a FP-PRF partition of 24 entries and an INT-PRF partition of 16 entries per thread is enough to hold the architectural registers of a thread. The registers that are not renamed and are replicated 2-ways in the baseline OOO core need to be replicated 8-ways in MorphCore.

Allocating/Updating the Resources. When the MorphCore is in OutofOrder mode, the instructions that are being renamed are allocated resources in the ROB

and in the Load and Store Queues. In InOrder mode, MorphCore leverages the ROB to store the instruction information. We partition the ROB into multiple fixed-size chunks, one for each active thread. We do not allocate resources in the Load Queue in InOrder mode since memory instructions are not executed speculatively. Thus, the Load Queue is inactive. The Store Queue that holds the data from committed store instructions and the data that is not yet committed to the D-cache, is active in InOrder Mode as well, and is equally partitioned among the threads.

Figure 3.4: Microarchitecture of the Rename stage

**Insert into the Reservation Station (RS).** Figure 3.4(a) shows the part of Rename stage that inserts renamed instructions into the RS. In OutofOrder mode, the RS is dynamically shared between multiple threads, and the RS entry that is allocated to an incoming renamed instruction is determined dynamically by consulting a Free List. In InOrder mode, the RS is divided among the multiple threads into fixed-size partitions (Figure 3.3(b)), and each partition operates as a circular FIFO. Instructions are inserted into consecutive RS entries pointed to by a per-thread RS-Insert-Ptr, and removed in-order after successful execution.

#### 3.1.4 Select and Wakeup

MorphCore employs both OutofOrder and InOrder Wakeup and Select Logic. The Wakeup Logic makes instructions ready for execution, and the Select Logic selects the instructions to execute from the pool of ready instructions. Figure 3.5 shows these logic blocks.

Figure 3.5: MorphCore Wakeup and Selection Logic

**OutofOrder Wakeup.** OutofOrder Wakeup logic works exactly the same as a traditional out-of-order core. Figure 3.5 (unshaded) shows the structure of an RS

entry [37]. An operand is marked ready (R-bit is set) when the corresponding MATCH bit has been set for the number of cycles specified in the DELAY field. When an instruction fires, it broadcasts its destination tag (power hungry), so that it can be compared against source tags of all instructions in the RS. If the destination tag matches the source tag of an operand, the MATCH bit is set and the DELAY field is set equal to the execution latency of the firing instruction (the latency of the instruction is stored in the RS entry allocated to the instruction). The DELAY field is also latched in the SHIFT field associated with the source tag. The SHIFT field is right shifted one-bit every cycle the MATCH bit is set. The R bit is set when the SHIFT field becomes zero. The RS-entry waits until both sources are ready, and then raises the Req OOO Exec line.

**OutofOrder Select.** The OutofOrder Select logic monitors all instructions in the RS (power hungry), and selects the oldest instruction(s) that have the Req OOO Exec lines set. The output of the Select Logic is a Grant bit vector, in which every bit corresponds to an RS entry indicating which instructions will fire next. When an instruction is fired, the SCHEDULED bit is set in the RS entry so that the RS entry stops requesting execution in subsequent cycles.

**InOrder Wakeup.** The InOrder mode executes/schedules instructions in-order, i.e., an instruction becomes ready after the previous instruction has either started execution or is ready and independent. We add 2 new bit-fields to each RS entry for inorder scheduling (Scheduled, and MATCH (M)). The new fields are shaded in Figure 3.5. The InOrder Wakeup Logic block also maintains the M/DELAY/SHIFT/R bit fields per architectural register, in order to track the availability of architectural registers. When an instruction fires, it sets the R, M, and DELAY bit fields corresponding to the destination register in the InOrder Wakeup Logic block as follows: resets the R bit, sets the MATCH (M) bit, and sets the DELAY field to the execution latency of the firing instruction (the DELAY/SHIFT mechanism works as explained above). Every cycle, for every thread, the InOrder Wakeup checks the availability of source registers of the two oldest instructions (R bit is set). If the sources are available, the Wakeup logic readies the instructions by setting the M bit in the RS entry to 1. The InOrder Wakeup is power-efficient since it avoids the broadcast and matching of the destination tag against the source operands of all instructions in the RS.

**InOrder Select.** The InOrder Select Logic block works hierarchically in a complexityeffective (power-efficient) manner by maintaining eight InOrder select blocks (one per thread) and another block to select between the outcomes of these blocks. Furthermore, each in-order select logic only monitors the two oldest instructions in the thread's RS partition, rather than monitoring the entire RS as in OOO select. Note that only two instructions need monitoring in InOrder mode because instructions from each thread are inserted and scheduled/removed in a FIFO manner.

### 3.1.5 Execution and Commit

When an instruction is selected for execution, it reads its source operands from the PRF, executes in an ALU, and broadcasts its result on the bypass network as done in a traditional OOO core. In MorphCore, an additional PRF-bypass and additional data storage are active in InOrder mode. This bypass and buffering is provided in order to delay the write of younger instruction(s) in the PRF if an older longer latency instruction is in the execution pipeline. In such a case, younger instruction(s) write into a temporary small data buffer (4-entry per thread). The buffer adds an extra bypass in the PRF-read stage. Instructions commit in traditional SMT fashion. For OutofOrder commit, the Permanent-RAT is updated as well. In InOrder mode, only the thread's ROB Head pointer needs to be updated.

#### 3.1.6 Load/Store Unit

Figure 3.6 shows the Load/Store Unit. In OutofOrder mode, load/store instructions are executed speculatively and out of order (similar to a traditional OOO core). When a load fires, it updates its entry in the Load Queue and searches the

Figure 3.6: Load / Store unit

Store Queue to get the latest data. When a store fires, it updates and stores data in the Store Queue, and searches the Load Queue to detect store-to-load program order violations. In InOrder mode, since load/store instructions are not executed speculatively, no Load Queue CAM searches are done. However, loads still search the Store Queue that holds committed data. Store instructions also update the Store Queue. Note that the introduction of InOrder mode in a traditional OOO core does not impact the memory consistency model or the cache coherence protocol implemented by the core.

### 3.1.7 Recovering from Branch Mispredictions

In OutofOrder mode, a branch misprediction triggers a recovery mechanism that recovers the F-RAT to the state prior to the renaming of the mispredicted branch instruction. In InOrder mode, a branch misprediction squashes the instructions in the RS partition, the ROB partition and the front-end pipeline from the thread, followed by redirection of the PC to the correct target.

### 3.2 MorphCore Discussion

#### 3.2.1 Area and Power Overhead of MorphCore

First, MorphCore increases the number of SMT ways from 2 to 8. This adds hardware to the Fetch stage and other parts of the core, which is less than 0.5% area overhead as reported by our modified McPAT [26] tool (the core area includes the area of the first-level instruction cache and data cache). Note that it does not incur the two biggest overheads of adding SMT contexts in an OOO core –additional Rename tables and physical registers– because the SMT contexts being added are in-order. Second, MorphCore adds InOrder Wakeup and Select logic, which we assume adds an area overhead of less than 0.5% of core area, half the area of the OOO Wakeup and Select logic blocks. Third, adding extra bypass/buffering adds an area overhead of 0.5% of core. Thus, MorphCore adds an area overhead of 1.5%, and a power overhead of 1.5% in InOrder mode.

#### 3.2.2 Timing/Frequency Impact of MorphCore

MorphCore requires only two key changes to the baseline OOO core:

1) InOrder renaming/scheduling/execution logic. MorphCore adds a multiplexer in the critical path of three stages: a) in the Rename stage to select between OutofOrder mode and InOrder mode renamed instructions, b) in the Instruction Scheduling stage to select between the OutofOrder mode and InOrder mode ready instructions, and c) in PRF-read stage because of additional bypassing in InOrder mode. In order to estimate the frequency impact of this overhead, we assume that a multiplexer introduces a delay of one transmission gate, which we assume to be half of an FO4 gate delay. Assuming 20 FO4 gate delays per pipeline stage [45, 7], we estimate that MorphCore runs 2.5% slower than the baseline OOO core.

2) More SMT contexts. Addition of in-order SMT contexts can lengthen the thread selection logic in MorphCore's front-end. This overhead is changing the multiplexer that selects one out of many ready threads from 2-to-1 to 8-to-1. We assume that running MorphCore 2.5% slower than the baseline OOO core hides this delay.

In addition to the above mentioned timing-critical changes to the baseline OOO core, MorphCore adds InOrder Wakeup and Select logic blocks. Because InOrder instruction scheduling is simpler than OutofOrder instruction scheduling, we assume that newly added blocks can be placed and routed such that they do not affect the critical path of other components of the baseline OOO core. Thus, we conclude that the frequency impact of MorphCore is only 2.5%.

### 3.2.3 Turning Off Structures in InOrder Mode

The structures that are inactive in InOrder Mode are either clock-gated (OOO scheduling and load queue) or power-gated (OOO renaming logic).

### 3.2.4 Interaction with OS

MorphCore does not require any changes to the operating system, and acts like a core with the number of hardware threads equal to the maximum number of threads supported in the InOrder Mode (8 in our implementation). Switching between the two modes is handled in hardware.

## **Chapter 4**

# Mode Switching Policy for Adapting to TLP and Evaluation

In Chapter 3, I introduced two of the five modes supported by the MorphCore microarchitecture: OutOfOrder and InOrder. The OutOfOrder mode is 4-wide superscalar and 192-entry out-of-order whereas InOrder mode is 4-wide superscalar 8-way threaded in-order SMT. This chapter describes the policy that we use to switch between these two modes when the MorphCore microarchitecture adapts to TLP, and evaluates its performance and energy efficiency.

### 4.1 When to Operate in OutofOrder Mode or in InOrder Mode?

The current implementation of MorphCore switches between OutofOrder and InOrder modes based on the number of active threads. A thread is active when it is not waiting for a synchronization event. We assume that the threading library uses MONITOR/MWAIT [17] instructions such that MorphCore hardware can detect a thread becoming inactive, e.g., inactive at a barrier waiting for other threads to reach the barrier, or inactive at a lock-acquire waiting for another thread to release the lock. The hardware makes the thread active when a write to the cacheline being monitored is detected.

MorphCore operates in OutofOrder mode when the number of active threads is fewer than or equal to 2. The rationale here is that when TLP is limited, executing OOO is the best and only way to obtain performance and energy efficiency. I show in Section 5.1 that 2-wide in-order execution not only loses performance significantly but increases energy consumption as well. MorphCore operates in In-Order when the number of active threads is greater than 2. The rationale here is that high core throughput can be obtained by executing the many available threads inorder while saving energy. MorphCore starts running in OutofOrder mode when the number of active threads is fewer than 2. If the OS schedules more threads on MorphCore, and the number of active threads becomes greater than 2, the core switches to InOrder mode. While running in InOrder mode, the number of active threads can drop for two reasons: the OS can de-schedule some threads or the threads can become inactive waiting for synchronization. If the number of active threads becomes smaller than or equal to 2, the core switches back to OutofOrder mode until more threads are scheduled or become active.

### 4.1.1 Changing Mode from OutofOrder to InOrder

Mode switching is handled by a micro-code routine that performs the following tasks:

1) Drains the core pipeline.

2) Spills the architectural registers of all threads. These registers are spilled to a reserved memory region. To avoid cache misses on these writes, we use Full Cache Line Write instructions that do not read the cache line before the write [17].

3) Disables the Renaming unit, OutofOrder Wakeup and Select Logic blocks, and Load Queue. Note that these units do not necessarily need to be power-gated (we assume that these units are clock-gated).

4) Fills the register values back into each thread's PRF partitions. This is done using special load micro-ops that directly address the PRF entries without going through renaming.

### 4.1.2 Changing Mode from InOrder to OutofOrder

MorphCore supports eight threads in InOrder mode and two threads in OutofOrder mode. When MorphCore changes mode from InOrder to OutofOrder, only two of the eight threads can be executed. Thus six of the eight threads are marked inactive or "not running" (unless they are already inactive, which is the case in our current implementation). The state of the inactive threads is stored in memory until they become active. To load the state of the active threads, the MorphCore stores pointers to the architectural state of the inactive threads in a structure called the Active Threads Table. The Active Threads Table is indexed using the Thread ID, and stores an 8-byte pointer for each thread. Mode switching is handled by a micro-code routine that performs the following tasks:

1) Drains the core pipeline.

2) Spills the architectural registers of all threads, and stores the pointers to the architectural state of the inactive threads in the Active Thread Table.

3) Enables the Renaming unit, OutofOrder Wakeup and Select Logic blocks, and Load Queue.

4) Fills the architectural registers of only the active threads into pre-determined locations in PRF, and updates the Speculative-RAT and Permanent-RAT.

### 4.1.3 Overhead of Changing the Mode

The overhead of changing the mode is pipeline drain, which varies with the workload, and the spill or fill of the architectural register state of the threads. The x86 ISA [17] specifies an architectural state of  $\sim$ 780 bytes per thread (including the latest AVX extensions). The micro-code routine takes  $\sim$ 30 cycles to spill or fill the architectural register state of each thread after the pipeline drain (a total of  $\sim$ 6KB and  $\sim$ 250 cycles for 8 threads) into reserved ways of the private L2 cache (assuming a 256 bit wide read/write port to the cache, and a cache bandwidth of 1 read/write per cycle). We have empirically observed a loss in performance of only less than 1% by reserving 6KB in the private 256KB cache. Note that the overhead of changing the mode can be reduced significantly by overlapping the spilling or filling of the architectural state with the pipeline drain.

#### 4.1.4 Handling Medium TLP

MorphCore operates in InOrder mode when the number of active threads is greater than 2. This policy works best when the number of active threads is maximum, i.e., 8, since many active threads sustain a high core throughput even when running in-order. However, the number of active threads can change at runtime. When only a few threads are active (e.g., 3-5), executing those threads in-order in InOrder mode may not achieve a high core throughput, and in fact may even reduce performance as compared to the baseline OOO-2 core (or OutofOrder mode).

A solution to this problem is to switch into OutofOrder mode when the medium number of active threads cannot sustain a high core throughput in InOrder mode but OOO execution can in OutofOrder mode. Detecting such situations and making the necessary mode switching decisions are future research areas. Note that the few active threads cannot all be run out-of-order simultaneously since the core supports only 2 OOO contexts. A technique called Balanced Multithreading [43] can be used to address this problem which proposes to time-multiplex the threads (2 at a time) onto a 2-SMT-context OOO processor when the number of active threads (their "virtual context") is greater than 2.

### 4.2 Experimental Methodology

Table 4.1 shows the configurations of the cores and the memory subsystem simulated using our in-house cycle-level x86 simulator. The simulator faithfully models microarchitectural details of the core, cache hierarchy and memory subsystem, e.g., contention for shared resources, DRAM bank conflicts, banked caches, etc. To estimate the area and energy of different core architectures, we use a modified version of McPAT [26]. We modified McPAT to: 1) report finer-grain area and power data, 2) increase SMT ways without increasing the Rename (RAT) tables, 3) use the area/energy impact of InOrder scheduling (1/2 of OOO), 4) model extra bypass/buffering, and 5) model the impact of SMT more accurately. Note that all core configurations have the same memory subsystem (L2, L3 and main memory).

|           | Core Configurations                                                      |

|-----------|--------------------------------------------------------------------------|

| 000-2     | <b>Core:</b> 3.4GHz, 4-wide issue OOO, 2-way SMT, 14-stage pipeline,     |

|           | 64-entry unified Reservation Station (Issue Queue), 192 ROB,             |

|           | 50 LDQ, 40 STQ, 192 INT/FP Physical Reg File, 1-cycle                    |

|           | wakeup/select Functional Units: 4 multi-purpose. ALU latencies           |

|           | (cycles): int arith 1, int mul 4-pipelined, fp arith 4-pipelined, fp di- |

|           | vide 8, loads/stores 1+2-cycle D-cache L1 Caches: 32KB I-cache,          |

|           | D-cache 32KB, 2 ports, 8-way, 2-cycle pipelined <b>SMT:</b> Stages se-   |

|           | lect round-robin among ready threads. ROB, RS, and instr buffers         |

|           | shared as in Pentium 4 [22]                                              |

| 000-4     | 3.23GHz (5% slower than OOO-2), 4-wide issue OOO, 4-way                  |

|           | SMT, Other parameters are same as OOO-2.                                 |

| MED       | Core: 3.4GHz, 2-wide issue OOO, 1 Thread, 10-stage, 48-entry             |

|           | ROB/PRF. Functional Units: Half of OOO-2. Latencies same as              |

|           | OOO-2. L1 Caches: 1 port Dcache, other same as OOO-2. SMT:               |

|           | N/A                                                                      |

| SMALL     | Core: 3.4GHz, 2-wide issue In-Order, 2-way SMT, 8-stage                  |

|           | pipeline. Functional Units: Same as MED. L1 Caches: Same                 |

|           | as MED. SMT: Round-Robin Fetch                                           |

| MorphCore | <b>Core:</b> 3.315GHz (2.5% slower than OOO-2), Other parameters         |

|           | are same as OOO-2. Functional Units and L1 Caches: Same as               |

|           | OOO-2. SMT and Mode switching: 2-way SMT similar to OOO-                 |

|           | 2, 8-way in-order SMT (Round-Robin Fetch) in InOrder mode. RS            |