Copyright

by

Byoung Ho Kim

2007

The Dissertation Committee for Byoung Ho Kim certifies that this is the approved version of the following dissertation:

# Predicting Performance Parameters of Analog and Mixed-Signal Circuits Using Built-In and Built-Off Self Test

| Committee:                   |

|------------------------------|

|                              |

| Jacob A. Abraham, Supervisor |

| Anthony Ambler               |

| D Cl                         |

| Ranjit Gharpurey             |

| Shouli Yan                   |

| Gyeong S. Hwang              |

| dycong b. Hwang              |

# Predicting Performance Parameters of Analog and Mixed-Signal Circuits Using Built-In and Built-Off Self Test

by

Byoung Ho Kim, B.S.;M.S.

#### DISSERTATION

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

#### DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN December 2007

## Acknowledgments

I would like to show my deepest gratitude to many people who have encouraged and assisted me throughout my Ph.D study. Of the people who have helped me during the lengthy journey of my dissertation, I would like to thank, first and foremost, Professor Jacob A. Abraham. As a supervisor, I owe him a great deal. His keen insights and breadth of knowledge allowed me to examine problems at a fundamental level and become a better researcher. I would like to thank Professor Anthony Ambler, Professor Ranjit Gharpurey, Professor Shouli Yan and Professor Gyeong S. Hwang for serving as my dissertation committee, and for many helpful and stimulating discussions. Also I thank my manager Chung-Yu Chen, team lead Nash Khouzam and Zhenhai Fu at National Semiconductor for their support and encouragement.

Many thanks to the present and former members of the CERC group, Haksoo Yu, Hongjoong Shin, Jihwan (Paul) Chun and Joonsung Park for their valuable discussion. Thanks are also due to Rajeshwary Tayade, Tung-Yeh Wu, Chaoming Zhang, Shobha Vasudevan, Whitney J. Townsend, Ramyanshu Datta, Sankaranarayanan Gurumurthy, Sriram Sambamurthy, Adam Tate, Ramtilak Vemu for making sure things were running smoothly in the lab all the time. I am especially thankful to Debi Prather and Melanie Gulick for their kind caring assistance, and Andrew Kieschnick for professional techni-

cal support for CERC systems. I am grateful to all my friends who shared precious moments with me in Austin Texas.

I attempt to express my deep gratitude and indebtedness to my parents and brother for their loving and believing in me all these years.

Byoung Ho Kim

$The\ University\ of\ Texas\ at\ Austin$

December 2007

Predicting Performance Parameters of Analog and Mixed-Signal Circuits Using Built-In and Built-Off Self Test

Publication No.

Byoung Ho Kim, Ph.D. The University of Texas at Austin, 2007

Supervisor: Jacob A. Abraham

The widespread use of embedded mixed-signal cores in system-on-chip (SoC) or System-on-Package (SoP) design has been increasingly important in cost-effective manufacturing test for mixed-signal devices. A typical SoP encapsulates many of its internal functions, and its production test is performed by application of test signals to the SoP under control of external Automatic Test Equipment (ATE). However it is a problem that the external ATE does not have direct access to all the internal embedded functions of the SoP. Thus a classical test approach to SoP suffers from limited controllability and observability of its subsystems.

Built-in Self-Test (BIST) and Built-off Self-test (BOST) schemes have been suggested and developed to overcome the limitations of conventional test, such as limited test Input/Output (I/O) accessibility as well as high test cost. However most BIST/BOST approaches have limited test accuracy.

The focus of the dissertation is to develop a cost-effective performancebased test methodology based on BIST/BOST, while maintaining the same accuracy as conventional test. This dissertation proposes one BIST approach and two BOST schemes. Our BIST methodology presents a methodology for efficient prediction of circuit specifications with optimized signatures. The proposed Optimized Signature-Based Alternate Test (OSBAT) methodology accurately predicts the specifications of a Device Under Test (DUT) using a strong correlation mapping function. The approach overcomes the limitation that analytical expressions cannot precisely describe the nonlinear relationships between signatures and specifications. Our first BOST approach presents a practical methodology for effective prediction of individual dynamic performance parameters of differential devices with a cascaded Radio-Frequency (RF) transformer in loopback mode. The RF transformer produces differently weighted loopback responses, which are used to characterize the DUT dynamic performance. The approach overcomes the imbalance problem of Design for Test (DfT) circuitry on differential signaling, thereby accurately measuring the dynamic performance of differential mixed-signal circuits. The second BOST scheme is an efficient methodology for accurate prediction of aperture jitter using cost-effective loopback methodology. Aperture jitter is precisely separated from input and clock jitter as well as additive noise present in the DUT, by using an efficient loopback scheme. Hardware measurements were performed for all our approaches, and good results were obtained. This fact veri?es that all approaches can be practically used for production test in industry.

# **Table of Contents**

| Ackno      | wledg | ments                                                                                           | V           |

|------------|-------|-------------------------------------------------------------------------------------------------|-------------|

| Abstra     | act   |                                                                                                 | vii         |

| List of    | Table | es                                                                                              | xii         |

| List of    | Figu  | res                                                                                             | xiii        |

| Chapt      | er 1. | Introduction                                                                                    | 1           |

| 1.1        | Motiv | vation                                                                                          | 1           |

|            | 1.1.1 | Need for New Solution                                                                           | 4           |

| 1.2        | Contr | ribution                                                                                        | 7           |

|            | 1.2.1 | Development of Cost-Effective Methodology                                                       | 7           |

|            | 1.2.2 | Improvement of Controllability and Observability                                                | 9           |

|            | 1.2.3 | Overcoming Limitations of Conventional BIST Schemes                                             | 9           |

|            | 1.2.4 | Solutions to Challengeable Issues on High Speed Mixed-Signal Circuits                           | 11          |

| 1.3        | Orgai | nization and Approach Overview                                                                  | 14          |

| Chapt      | er 2. | Review of Analog and Mixed-Signal Testing                                                       | 17          |

| 2.1        | Hard  | ware Architecture of Self Test and ATE                                                          | 17          |

| 2.2        | State | of the Art for BIST and BOST approaches                                                         | 20          |

| Chapter 3. |       | Prediction of Mixed-Signal Dynamic Performanc<br>Using Optimized Signature-Based Alternate Test | e <b>24</b> |

| 3.1        | Motiv | vation of Approach                                                                              | 26          |

|            | 3.1.1 | Ternary Signal Representation (TSR)                                                             | 26          |

|            | 3.1.2 | Issues of TSR Technique                                                                         | 28          |

| 3.2        | Optin | nized Signature-Based Test Methodology                                                          | 30          |

|            | 3.2.1                             | Predict<br>Signatu | ion of Performance Parameters with Optimized ares                      | 30 |

|------------|-----------------------------------|--------------------|------------------------------------------------------------------------|----|

|            | 3.2.2                             | Extend             | ed OSBAT Method for Loopback Test                                      | 39 |

| 3.3        | Experimental Results              |                    |                                                                        | 42 |

|            | 3.3.1                             | Hardwa             | re Results                                                             | 42 |

|            |                                   | 3.3.1.1            | Hardware Measurement Set-up                                            | 42 |

|            |                                   | 3.3.1.2            | Hardware Measurement Results                                           | 44 |

|            | 3.3.2                             | Effect o           | of Non-Idealities                                                      | 50 |

|            |                                   | 3.3.2.1            | Instability of Comparator in Signature Generator                       | 50 |

|            |                                   | 3.3.2.2            | Effect of Sampling Time of Signature Generator                         | 52 |

|            |                                   | 3.3.2.3            | Effect of Training Set Size                                            | 54 |

|            | 3.3.3                             | Hardwa             | re Measurements for Loopback Test                                      | 54 |

| 3.4        | Sumn                              | nary               |                                                                        | 56 |

| Chapter 4. |                                   |                    | ormer-Coupled Loopback Test for Differential<br>-Signal Specifications | 61 |

| 4.1        | Imbal<br>forma                    |                    | ue of Differential Network Circuit and DUT Per-                        | 63 |

|            | 4.1.1                             | Imbalar            | nce Introduced by Single RF Transformer                                | 63 |

|            |                                   | 4.1.1.1            | Ideal Case (No Imbalance)                                              | 64 |

|            |                                   | 4.1.1.2            | Imbalance Case I (Magnitude)                                           | 65 |

|            |                                   | 4.1.1.3            | Imbalance Case II (Phase)                                              | 66 |

|            | 4.1.2                             | Analysi            | s of Imbalance Effect                                                  | 67 |

| 4.2        | Transformer-Coupled Loopback Test |                    |                                                                        | 68 |

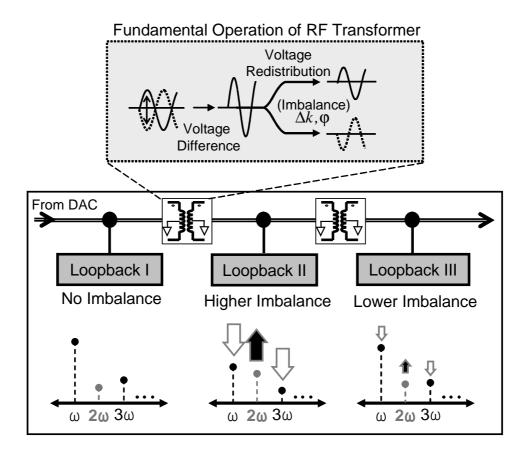

|            | 4.2.1                             | Qualita            | tive Analysis                                                          | 69 |

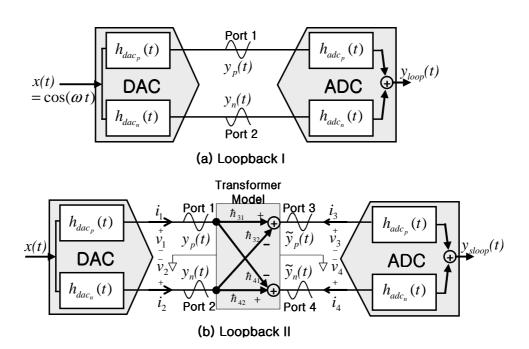

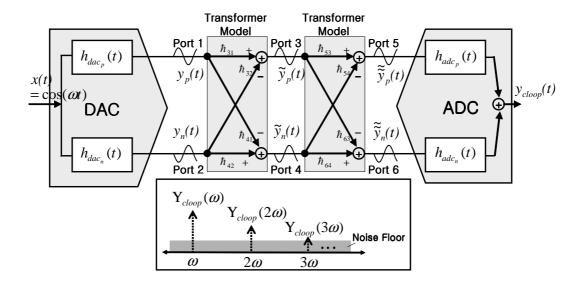

|            | 4.2.2                             | Quantit            | tative Analysis                                                        | 72 |

|            |                                   | 4.2.2.1            | Characterization of Harmonic Distortion Parameter                      | 72 |

|            |                                   | 4.2.2.2            | Characterization of Noise Parameters                                   | 78 |

|            |                                   | 4.2.2.3            | Non-linear Regression                                                  | 79 |

| 4.3        | Exper                             | rimental           | Results                                                                | 80 |

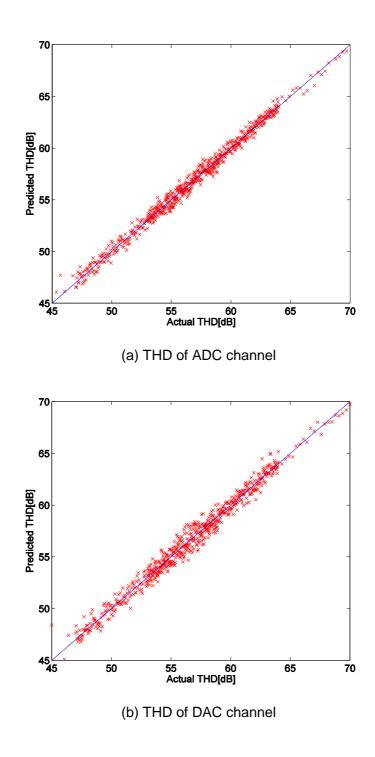

|            | 4.3.1                             | Simulat            | ion Results                                                            | 80 |

|            | 4.3.2                             | Hardwa             | ure Measurements                                                       | 84 |

|            |                                   |                    | Classification Accuracy                                                | 89 |

| 4 4        | Sumn                              |                    |                                                                        | 80 |

| Chapter 5.  |                                             | . Efficient Loopback Test for Aperture Jitter in Erbedded Mixed-Signal Circuits |     |  |

|-------------|---------------------------------------------|---------------------------------------------------------------------------------|-----|--|

| 5.1         |                                             | olems of Jitter Measurement in ed-Signal Circuits                               |     |  |

|             | 5.1.1                                       | Effect of Jitter on Mixed-Signal Device                                         | 93  |  |

|             | 5.1.2                                       | Previous Work                                                                   | 96  |  |

| 5.2         | Efficient Loopback Test for Aperture Jitter |                                                                                 | 97  |  |

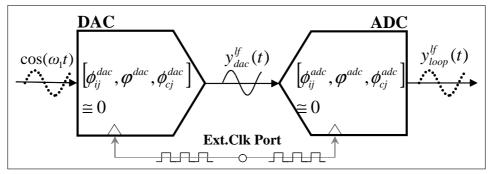

|             | 5.2.1                                       | Qualitative Analysis                                                            | 98  |  |

|             | 5.2.2                                       | Quantitative Analysis                                                           | 104 |  |

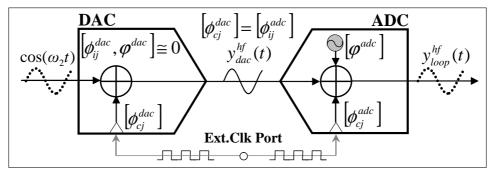

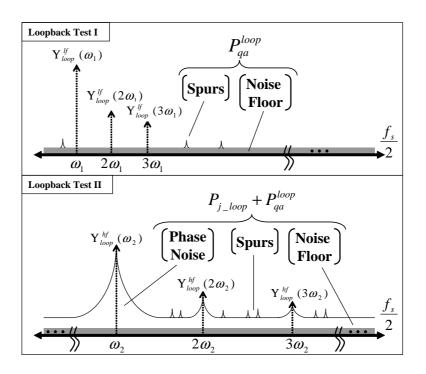

|             |                                             | 5.2.2.1 Loopback Test I                                                         | 104 |  |

|             |                                             | 5.2.2.2 Loopback Test II                                                        | 105 |  |

| 5.3         | B Experimental Results                      |                                                                                 |     |  |

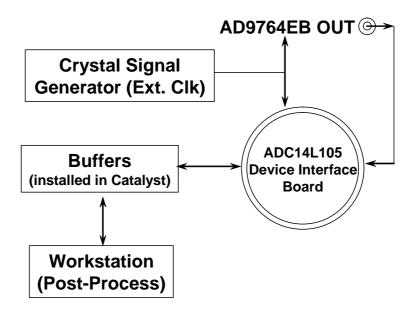

|             | 5.3.1                                       | Hardware Measurements                                                           | 110 |  |

|             | 5.3.2                                       | Repeatability of Jitter Prediction                                              | 116 |  |

|             | 5.3.3                                       | Classification Accuracy                                                         | 118 |  |

| 5.4 Summary |                                             | nary                                                                            | 119 |  |

| Chapter 6.  |                                             | Conclusion                                                                      | 120 |  |

| Bibliog     | graphy                                      | У                                                                               | 124 |  |

| Vita        | Vita                                        |                                                                                 |     |  |

# List of Tables

| 3.1 | DUT Specification                                                                      | 46  |

|-----|----------------------------------------------------------------------------------------|-----|

| 3.2 | Classification Accuracy                                                                | 46  |

| 3.3 | Specification Errors of OSBAT and TSR Technique for Hardware Measurements              | 50  |

| 3.4 | Correlation Coefficients between Actual and Predicted Values of Performance Parameters | 50  |

| 3.5 | OSBAT Prediction Errors for Difference Training Set Sizes                              | 54  |

| 3.6 | Specification Errors of Hardware Measurements                                          | 56  |

| 4.1 | Simulation Results for Specification Error                                             | 84  |

| 4.2 | Specification Errors of Hardware Measurements                                          | 85  |

| 4.3 | DUT Specifications                                                                     | 89  |

| 4.4 | Classification Accuracy                                                                | 89  |

| 5.1 | Parameters Used for Hardware Measurements                                              | 115 |

| 5.2 | Parameters Used for Repeatability                                                      | 118 |

| 5.3 | Repeatability of Hardware Measurements                                                 | 118 |

| 5.4 | Classification Accuracy                                                                | 118 |

# List of Figures

| Issue of Conventional Test due to Design Tolerance                                  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Need for BIST and BOST Schemes                                                      | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Typical Configurations of Self Test                                                 | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

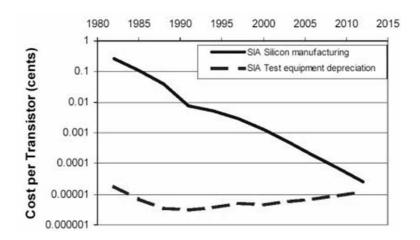

| Test Cost and Manufacturing Cost (Semiconductor Industry Association [72])          | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Simple Block Diagram of Mixed-Signal System                                         | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ATE Hardware Architecture                                                           | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Block Diagram of Self Test Logic                                                    | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Signature-Based Test and Conventional Test                                          | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Overview of TSR Technique                                                           | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

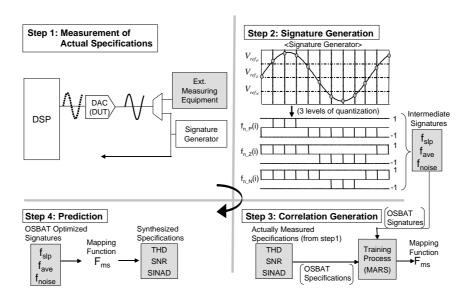

| OSBAT Methodology                                                                   | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

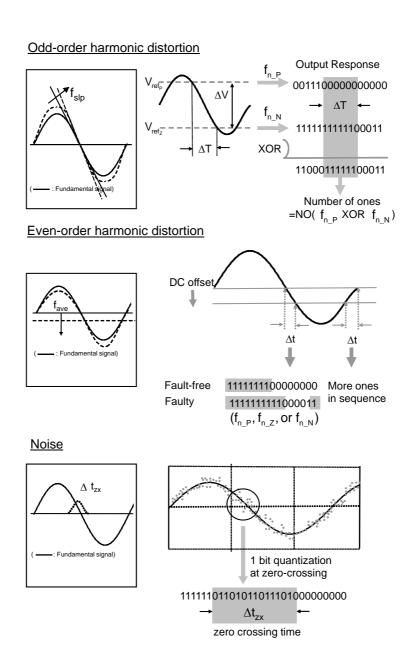

| Properties of Harmonic/Noise and Signature Generation (Step2 Details in Figure 3.3) | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

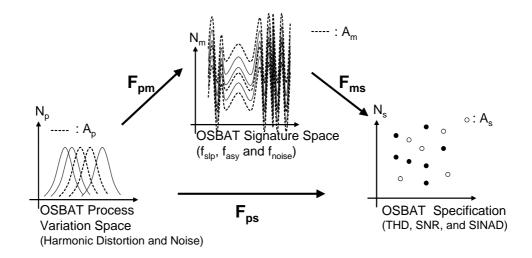

| Signature Space and Specification Space for OSBAT Method .                          | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

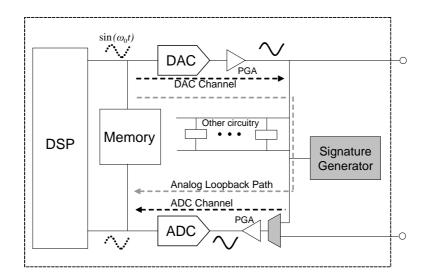

| Loopback Test Scheme for OSBAT Methodology                                          | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

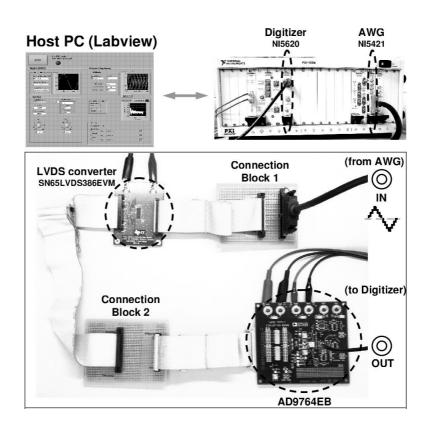

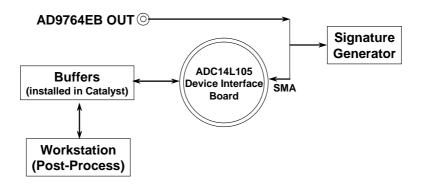

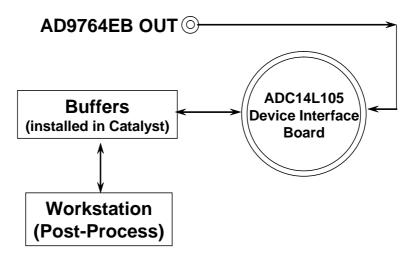

| Hardware Measurement Setup                                                          | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

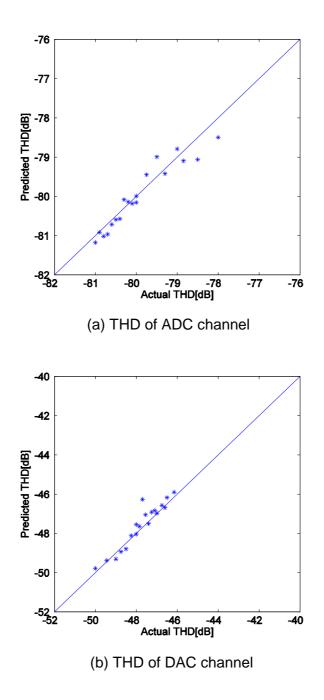

| THD Based on Proposed Method and TSR (Hardware Measurement Results)                 | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

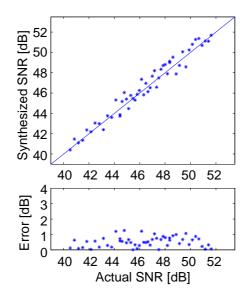

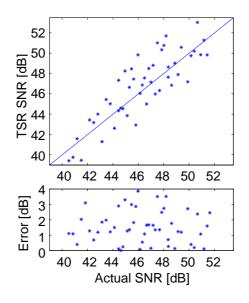

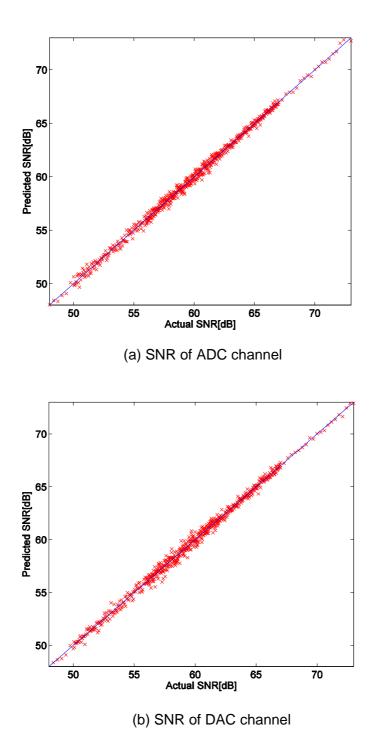

| SNR Based on Proposed Method and TSR (Hardware Measure-                             | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

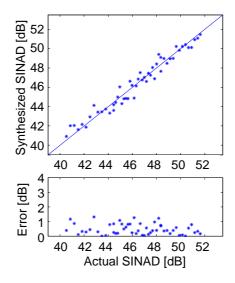

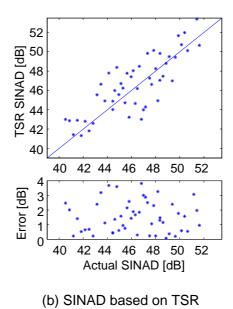

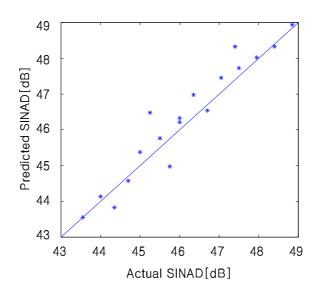

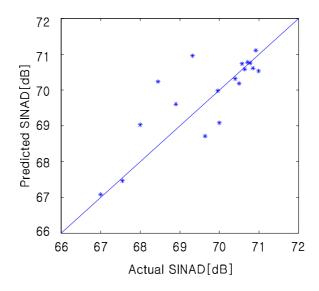

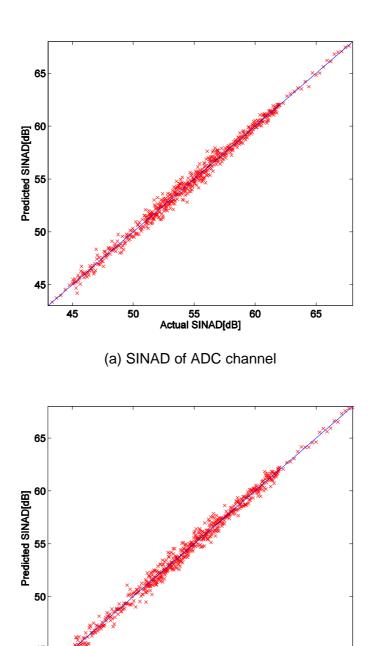

| SINAD Based on Proposed Method and TSR (Hardware Measurement Results)               | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

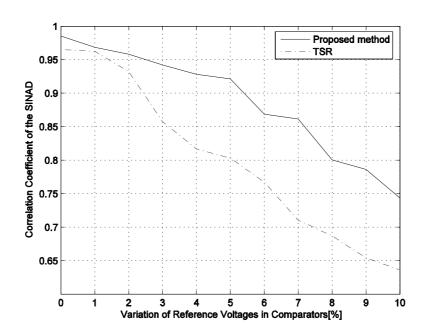

| Effect of Instability of Comparator on Correlation Coefficients                     | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

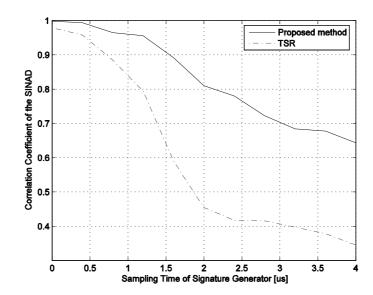

| Effect of Sampling Time Variation to Correlation Coefficient of SINAD               | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Hardware Measurement Setup for Loopback Test                                        | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| THD Results for Loopback Test (Hardware Measurement Result)                         | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                     | Need for BIST and BOST Schemes Typical Configurations of Self Test Test Cost and Manufacturing Cost (Semiconductor Industry Association [72]) Simple Block Diagram of Mixed-Signal System ATE Hardware Architecture Block Diagram of Self Test Logic Signature-Based Test and Conventional Test Overview of TSR Technique OSBAT Methodology Properties of Harmonic/Noise and Signature Generation (Step2 Details in Figure 3.3) Signature Space and Specification Space for OSBAT Method Loopback Test Scheme for OSBAT Methodology Hardware Measurement Setup THD Based on Proposed Method and TSR (Hardware Measurement Results) SNR Based on Proposed Method and TSR (Hardware Measurement Results) SINAD Based on Proposed Method and TSR (Hardware Measurement Results)  Effect of Instability of Comparator on Correlation Coefficients of SINAD  Effect of Sampling Time Variation to Correlation Coefficient of SINAD  Hardware Measurement Setup for Loopback Test |

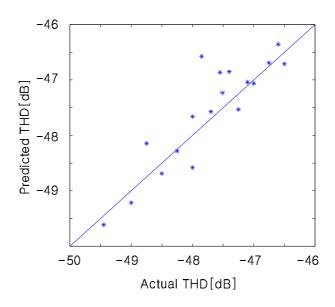

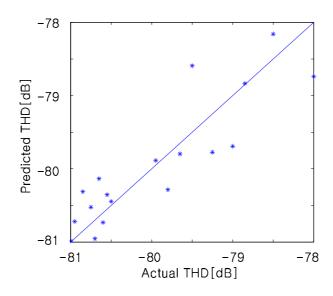

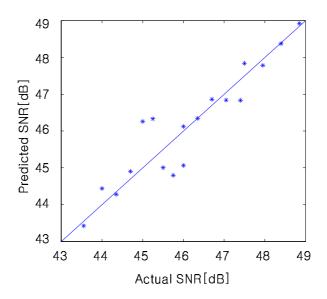

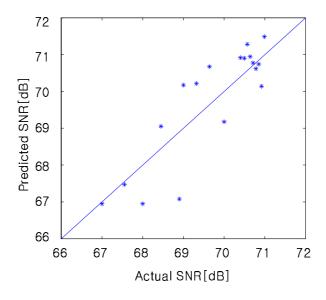

| 3.15 | THD Results for Loopback Test (Hardware Measurement Result)          | 58  |

|------|----------------------------------------------------------------------|-----|

| 3.16 | THD Results for Loopback Test (Hardware Measurement Result)          | 59  |

| 4.1  | Single Transformer as DND                                            | 64  |

| 4.2  | Proposed Loopback Test Scheme                                        | 70  |

| 4.3  | Characteristic of Cascaded RF Transformer on Loopback Paths          | 71  |

| 4.4  | $Loopback\ I$ and Cascaded Transformer Model on $Loopback\ II$ .     | 73  |

| 4.5  | Cascaded RF Transformer Model and Frequency Response on Loopback III | 76  |

| 4.6  | THD of DAC and ADC Channel (Simulation Results)                      | 81  |

| 4.7  | SNR of DAC and ADC Channel (Simulation Results)                      | 82  |

| 4.8  | SINAD of DAC and ADC Channel (Simulation Results)                    | 83  |

| 4.9  | Hardware Measurement Setup                                           | 84  |

| 4.10 | THD Results of DAC and ADC Channel                                   | 86  |

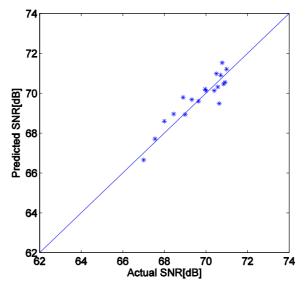

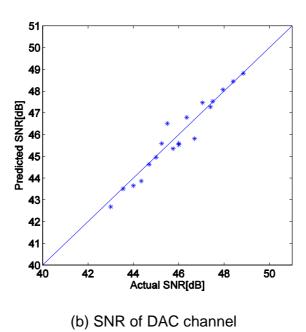

| 4.11 | SNR Results of DAC and ADC Channel                                   | 87  |

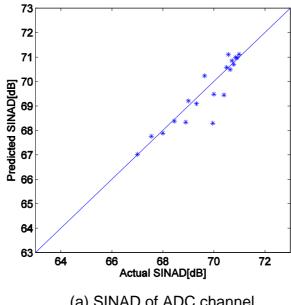

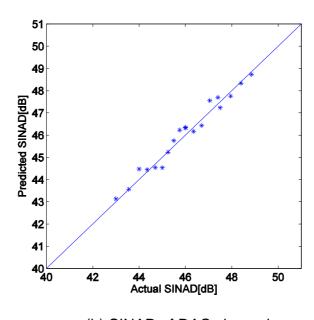

| 4.12 | SINAD Results of DAC and ADC Channel                                 | 88  |

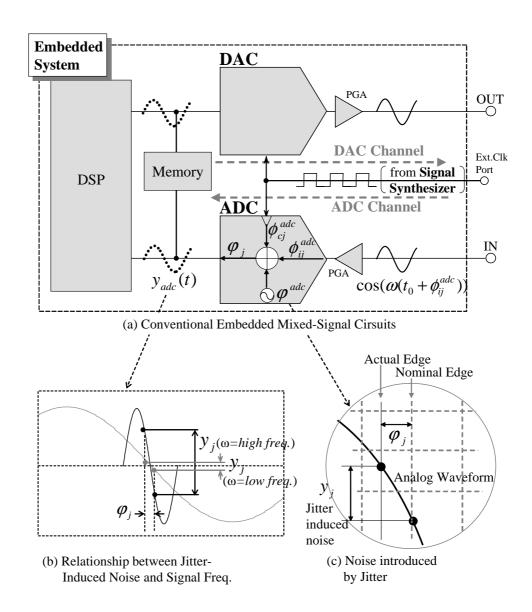

| 5.1  | Effect of Jitter on Conventional Embedded Mixed-Signal Device        | 95  |

| 5.2  | Proposed Loopback Scheme                                             | 100 |

| 5.3  | Contribution of Loopbacked Output on Spectral Response               | 102 |

| 5.4  | Relationship of Jitters in Our Loopback Scheme                       | 103 |

| 5.5  | Our Loopback Scheme for Quantitative Analysis                        | 107 |

| 5.6  | Loopbacked Spectral Response Based on Our Methodology                | 109 |

| 5.7  | Experiment Setup                                                     | 111 |

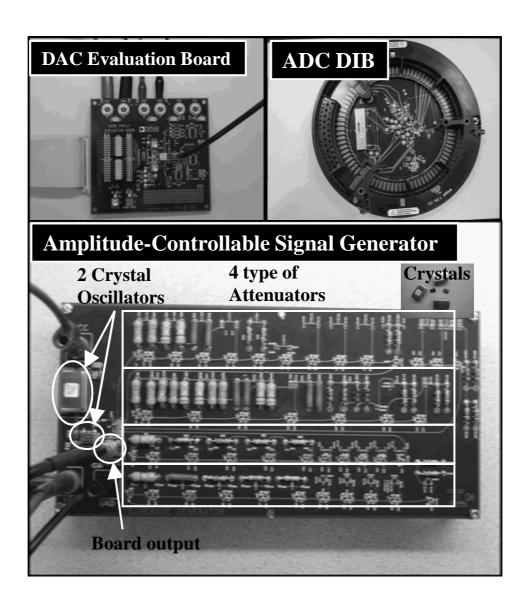

| 5.8  | DAC Evaluation and ADC DIB, and Crystals Signal Generator            | 113 |

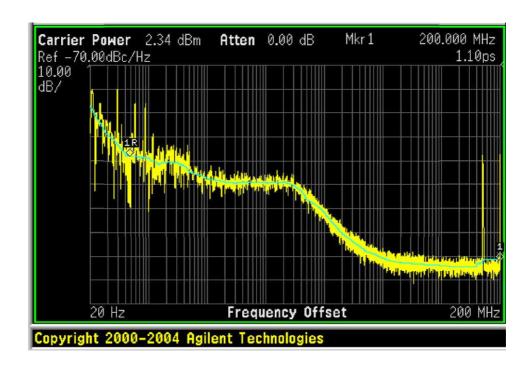

| 5.9  | Phase Noise of Clock Signal for Clock Jitter Estimation              | 114 |

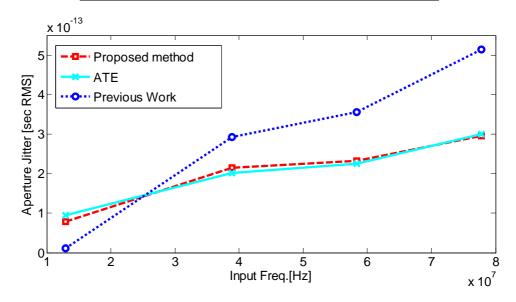

| 5.10 | Comparison between Proposed Method and Previous Work [61]            | 115 |

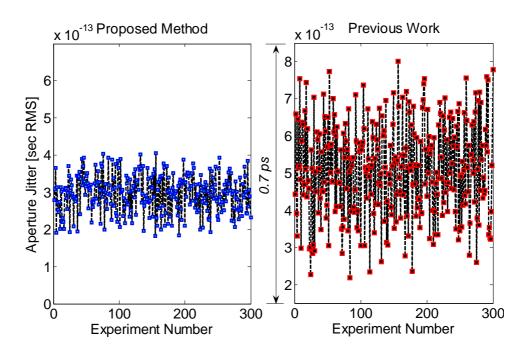

| 5.11 | Repeatability of Proposed Method and Previous Work [61]              | 117 |

## Chapter 1

### Introduction

#### 1.1 Motivation

The growing demand for multi-media, wireless communication, networking, and control systems has increased the importance of research in cost-effective manufacturing test for mixed-signal devices [29]. Most modern mixed-signal systems are of the 'big-D'-'small-A' (D-digital and A-analog) configuration. However, the 'small-A' takes up the majority of the production test time incurred in testing these devices [17], since it includes a large number of tests for analog circuit specifications. The extent of the problem can be gauged by the fact that the test cost is approaching 40% of the total manufacturing cost of these packages [5].

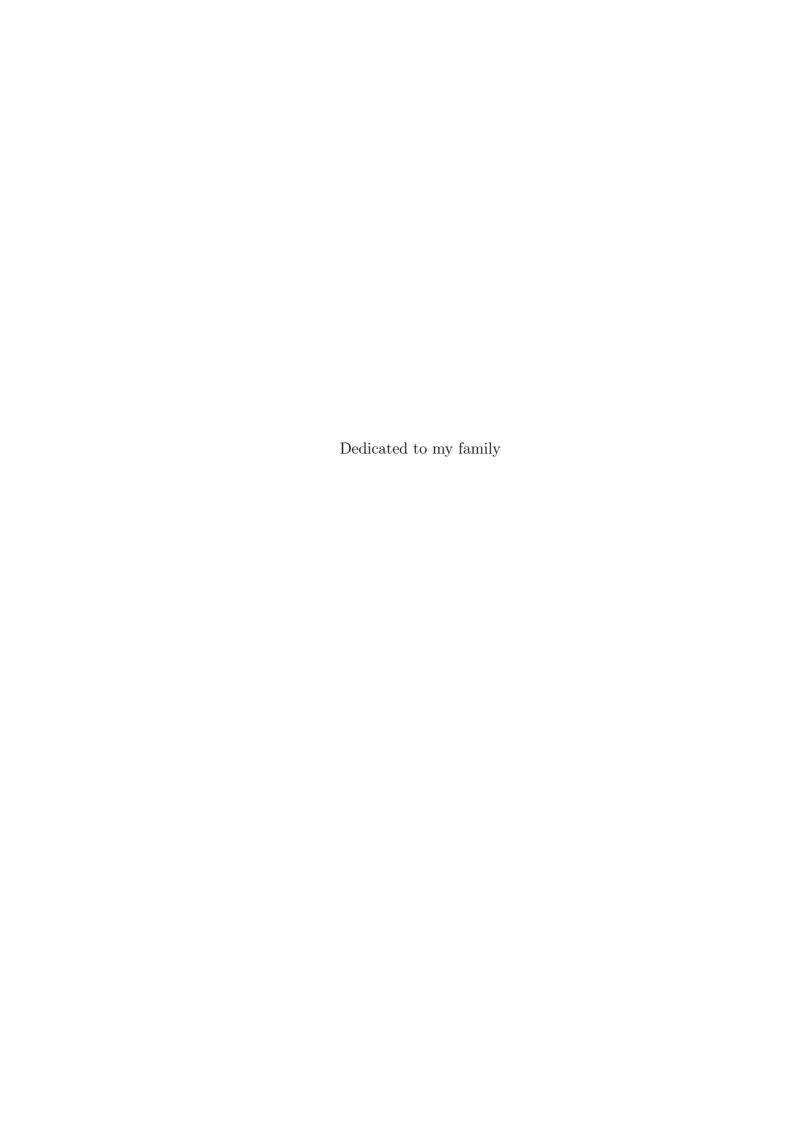

Also, analog test is a difficult task because of the necessity of dealing with the continuity of analog signal characteristics such as amplitude, frequency or phase of a voltage and since a tolerance is acceptable for the results. The analog specification for output of a non-faulty circuit can only be described within a tolerance margin as shown in Figure 1.1 [14, 49, 80]. Moreover, the ideal input waveform may not be applied to DUT, due to noise and tolerance specifications (or tolerances in the component values) of the circuit

Figure 1.1: Issue of Conventional Test due to Design Tolerance

such as signal generator, voltage controlled oscillator (VCO) and crystal oscillator, which produces the waveform. Thus the noisy or distorted input can affect the response of the DUT.

The problem of analog circuit testing becomes more difficult due to the integration of analog circuits as parts of the core in SoCs or SoPs. A typical SoP encapsulates many of its internal functions, and its production test is performed by application of test signals to the SoP under control of external ATE. It is a problem that the external ATE does not have direct access to all the internal embedded functions of the SoP. It may be possible to route some of the internal electrical signals out of the package to the external tester; however, these internal signals operate at frequencies that cannot be observed directly by an external tester due to the frequency limitations of the

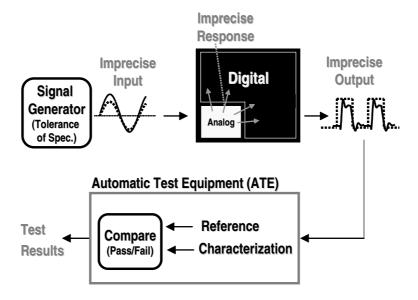

Figure 1.2: Need for BIST and BOST Schemes

encapsulating package and lower speed of external I/O. A similar speed and integrity concern is applicable to validating the subcomponents of the system. While traditional systems have test nodes to individually verify the operation of their subsystems, a classical test approach to SoP suffers from limited controllability and observability of its subsystems. Furthermore, the system specifications guaranteed by design depend on validation of associated subsystem specifications, which may no longer be accessible in a SoP configuration. This proposition is especially important for embedded passive components constituting a part of the package itself [5, 86].

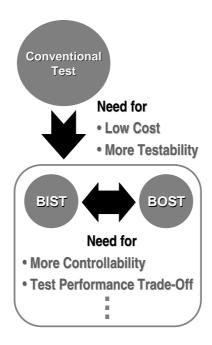

Figure 1.3: Typical Configurations of Self Test

#### 1.1.1 Need for New Solution

Consequently, the call for a testable SoP results in a conflict of interest between the degree of integration afforded by the design process and the level of testability achievable by an external tester. A viable solution is to place the ATE functionalities in close proximity of the SoP module to be tested. This improves the test-access speed, minimizes the test signal degradation by the cable parasitics of the external ATE, and increases controllability and observability of the signals internal to the DUT as shown in Figure 1.2. As widely accepted solutions, BIST [39, 53, 89] and BOST [5, 28] have been suggested and developed to allow test using much less expensive ATE as shown in Figure 1.3 [14].

A BIST scheme involves moving part of the required test resources (test stimuli generation, response evaluation, test control circuitry, etc.) from the ATE to the chip. Basically BIST pushes the external tester functionality into the package and even into the bare dies wherever possible. Another alternative, BOST migrates test functions of the external tester to the load board as well as the bare dies. The additional DfT circuitry on the load board retains the ability to apply high-speed stimulus to the system under test, capture the test response or provide some weight on the DUT output for characterization. Moreover in BOST scheme, post-processing in the processor available in the SoP is performed to analyze the output response, such as histogram [42], sine wave fitting [71] and oscillation-based technique [68]. In these approaches, the device is modified to incorporate some additional functions within the chip by reusing components such as Analog-to-Digital (ADC) and Digital-to-Analog (DAC) converters already available at the system level. As a result, without BOST and BIST very high-performance SoPs may not be economically testable. The test economics is greatly improved by having test functions on the load board (BOST) or the SoP itself (BIST). This allows high performance systems to be tested with a low-cost ATE without loss of test quality.

Various methodologies based on a BIST/BOST scheme have been proposed to reduce the test cost compared to conventional test. Many approaches based on fault-based test have been proposed based on a BIST/BOST scheme [48, 75, 86]. Motivated by the popularity of fault-based production testing of digital circuits, many researchers tried applying the methodology to the analog and mixed-signal domains [75]. In fault-based testing, a list of physically realistic faults are derived from process information, defect statistics, and circuit

layout. Tests are then developed to distinguish these faulty circuits from the fault-free circuit [81]. However the fault-based approach has limitations in testing analog and mixed-signal circuits.

- This approach requires DUT topology and the reference fault models [75]. It is hard to build the reference model of complicated circuits for the fault-based test. A poorly described model leads to lower test accuracy. Even though the method can increase fault coverage, the stimuli are targeted at detecting specific faults in specified components thereby covering selected faults.

- Secondly, although the methodologies can detect catastrophic faults effectively, such as open, short and bridge faults [76] resulting in reducing the test time and achieving a low-cost test as compared with a conventional performance-based test, they cannot detect parametric failures effectively. Furthermore even though it can detect parametric faults effectively by applying many sinusoidal signals, studying the steady state response of the DUTs is time consuming.

- Thirdly, analog circuits are tested for satisfying their specifications, not for faults [71]. Thus this type of test may not be a complete alternative to the existing performance-based test due to the lack of performance information.

In an attempt to overcome these drawbacks, many researchers have proposed performance-based test methodologies. In the performance-based test,

short duration and optimized stimulus is applied to a DUT. The response is analyzed to characterize the performance parameter of the DUT, without the need for reference model for the DUT. As an example of the approach, the signature-based test methodology includes analyzing the DUT response to generate the intermediate performance parameter called *performance-based signature* [54,65], which compresses or represents the output responses of a DUT. The signatures should be able to be easily found and strongly correlated with the DUT performance. Then the method involves deriving the relation between the signatures and the DUT performance [62]. The conventional test, which uses well-known Digital Signal Process (DSP) to characterize the specifications on the frequency domain, is also an example for the performance-based test. However this approach requires relatively long test time to analyze the output response for characterization of performance, and different instruments are sometimes needed for characterizing the specifications.

#### 1.2 Contribution

This dissertation investigates efficient performance-based test methodologies based on BIST/BOST, without loss of test quality. The primary contributions of the dissertation are discussed in this section.

#### 1.2.1 Development of Cost-Effective Methodology

CMOS and BI-CMOS technologies have made it possible to combine digital and analog circuits in a SoC and offer the possibility of designing high-

Figure 1.4: Test Cost and Manufacturing Cost (Semiconductor Industry Association [72])

quality analog circuits. Two factors dominate production costs in manufacturing of SoCs. These are the direct costs of test equipment and test time, and the indirect costs of test procedure development in conventional test [35]. Figure 1.4 shows that test cost approaches manufacturing cost as time goes by.

Analog signals are represented with much fewer parameters in this dissertation. Thus the acquisition of those parameters can be performed with simple DfT circuits. In addition the test response can be readily interpreted into performance parameters in a specification sheet. Thus it allows DUTs to be evaluated by comparing the measured performance directly against the specifications. As a result, our efficient approaches based on BIST/BOST architecture allow low-cost measurement without loss of test quality, thereby providing a complete alternative to the conventional mixed-signal test.

#### 1.2.2 Improvement of Controllability and Observability

As mentioned in the previous section, while traditional systems have test nodes to individually verify the operation of their subsystems, a classical test approach to SoP suffers from limited controllability and observability of its subsystems [5,86]. Consequently, the call for a testable SOP results in a conflict of interest between the degree of integration afforded by the design process and the level of testability achievable by an external tester.

DfT and self-test techniques have been proven to be very effective by the meaning of increasing the observability and the controllability of a DUT. Methodologies based on BIST and BOST schemes in this dissertation enhance the observability and controllability of mixed-signal circuits by splitting embedded analog and mixed-signal component into individual components using efficient DfT circuitry. Also high controllability and observability of the signals internal to the DUT are achieved for test stimulus application due to the fully digital generation method.

#### 1.2.3 Overcoming Limitations of Conventional BIST Schemes

BIST pushes the tester functions into the DUT in order to overcome the issues of conventional test as mentioned previously. BIST of analog and mixed-signal electronics provides the following major merits.

- On-chip generation of high-speed test stimulus using low-cost hardware

- High-speed on-chip response acquisition followed by analysis or response

#### compaction

Although this approach addresses the tester cost and test access limitation problems, large silicon area-overhead taken by these circuits, especially in mixed-signal testing, may not be feasible for all applications, and the addition of BIST circuitry can degrade the performance of the circuit being tested [18]. Basically the introduction of test circuitry into the device may violate original design constraints, e.g., device matching, parasitic loading, etc., and, as a result, additional design iterations may be needed during system design. Consequently, BIST is feasible only when it can be integrated into the system design flow.

A performance-based test approach based on BOST is a viable solution. Even though a BOST scheme requires a load board and has the access limitation for test nodes, its advantages can overcome the limitations of BIST approach as follows.

- BOST can significantly reduce the on-chip area overhead taken by the DfT circuits in the package under test by pushing most DfT circuits onto the load board, resulting in lower design cost.

- This scheme is also effective when the used DfT device is very sensitive to the noise generated from other circuits.

The DfT device on the load board is not affected from noise generated by circuits in on-chip system, thereby improving test accuracy, since the DfT

device can be installed physically more farther from other circuits. The DfT device sometimes needs to be characterized before it can be used to test DUTs. In such a case, the DfT device can be easily characterized on the load board. As mentioned before, BIST has the advantage to reuse devices already available at the system under test. It also means that if the needed DfT components are not available, the device should be carefully designed without affecting signal paths and the functionality of the original design in the system under test. This requires design efforts with the same quality as the original design. On the other hand, BOST uses the device as a DfT logic on the load board, which is commonly available for production test, resulting in lower test cost and no additional design efforts for DfT circuits. To summarize, BIST and BOST architectures are optimized for the different conditions of the ICs to be tested and DfT circuitry for the proposed approach. The broad range of different requirements of mixed-signal circuits can not be solved by BIST (or BOST) as a fixed unique solution. Careful selection of BIST and BOST schemes is needed to master the diversity of the problem. The approaches in this dissertation are performed based on efficient scheme to combine BIST and BOST features to overcome the limitations of conventional BIST.

# 1.2.4 Solutions to Challengeable Issues on High Speed Mixed-Signal Circuits

High-speed mixed-signal devices are designed using deep submicron process technologies, that generate a new class of defects and require faster, more accurate high-speed mixed-signal testing [19].

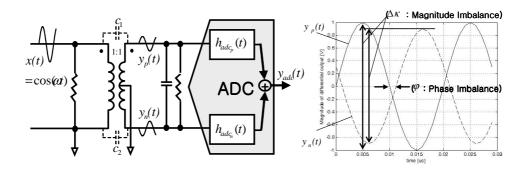

Many high-speed analog and mixed-signal circuits operate on a composite signal consisting of a differential signal pair. Most external test equipment used in conventional tests have single-ended I/O and use a coaxial cable to connect to the DUTs. However, no differential network device can avoid inherently the imbalance problem due to parasitic coupling capacitances in the differential terminals. The imbalance results in additional distortion or noise on the output of the DND. The distorted and noisy signal is delivered to the DUT input, thereby degrading the DUT performance [37].

Another challengeable issue of high-speed mixed-signal testing is the aperture jitter testing in high-speed ADC where aperture jitter is one of major limiting factors on the performance of mixed-signal circuits. Timing jitter introduced by sampling process is becoming a larger portion of the available timing margins, since it dramatically degrades the achievable Signal-to-Noise Ratio (SNR) of the data converters. Therefore this fact imposes stringent conditions on the allowable timing jitter in high-frequency signals. Thus jitter measurement is an important part in production testing of high-speed mixed-signal devices [84, 85].

However most mixed-signal BIST/BOST approaches have not been developed to deal with the issues in high-speed analog and mixed-signal testing due to the following reasons.

The magnitude and phase imbalance introduced by DfT circuitry significantly degrades DUT performance parameters, thereby reducing test accuracy and fault coverage.

- Jitter-induced noise present in DUT affects performance of DfT circuitry as well as DUT output, thereby degrading DUT performance.

- Even if a self-test approach is developed to overcome the above issues, this could lead to greater complexity in DfT circuit implementation.

Efficient Transformer-Coupled Loopback Test characterizes individual mixed signal specifications on differential signaling to overcome the imbalance effect due to differential signaling and realize cost-effective test. The proposed method uses an existing device, the RF transformer commonly used in the conventional test. It means that the RF transformer does not need to be designed, and the test cost is reduced. Furthermore the RF transformer has inherently wide input bandwidth. Therefore reuse of the RF transformer is possible to apply various frequency input signal.

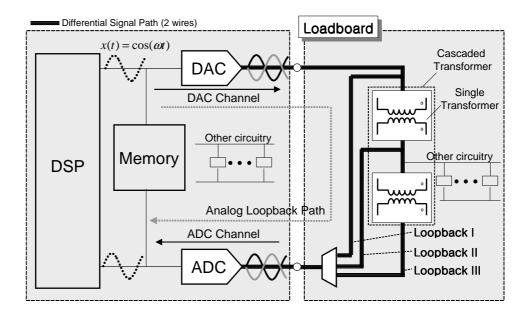

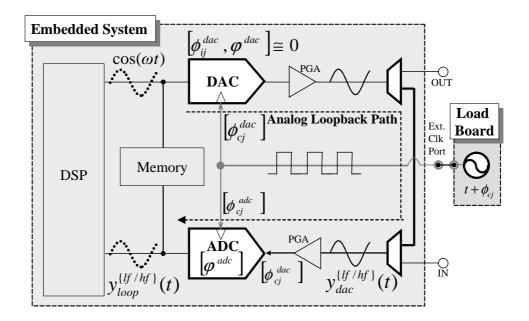

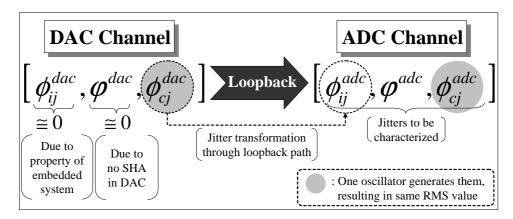

To improve prediction accuracy for aperture jitter, Efficient Loopback Test for Aperture Uncertainty in embedded mixed-signal circuits is proposed. The total six jitter components are present in DAC and ADC. Our efficient loopback test system allows us to characterize only three jitter components without the need for all the jitter components. As a result, our method allows us to predict aperture jitter of ADC using clock jittered-noisy DAC output. It further means that the proposed method replaces the need for expensive, low-jitter signal synthesizer to be essentially required in the conventional test.

#### 1.3 Organization and Approach Overview

The rest of this dissertation is organized as follows. Chapter 2 discusses the hardware architecture of self test and ATE and various approaches based on BOST and BIST.

Chapter 3 explains an efficient methodology called Optimized Signature-Based Alternate Test (OSBAT), to improve the accuracy in prediction of specifications using strong correlation mapping and to reduce test time and cost. A sinusoidal signal is applied to a DUT and the resultant output signal is manipulated into the optimized signatures by using low-cost comparators and digital circuits. To predict the performance parameters of a DUT, the correlation functions which map the obtained signatures to the specifications are generated by a regression technique. This approach provides improved performance on the problems associated with representing the exact relationship between signatures and specifications due to nonlinear characteristics. The results of hardware measurement with DACs (AD9764) show error reductions of THD, SNR and SINAD as 1.4dB, 2.3dB, and 2.1dB compared with the TSR technique. In addition, we evaluated the sensitivities of this technique to common non-idealities, such as the variations of reference voltages and sampling rate of BIST circuits. The results from our method with low sensitivity indicate that our predictive accuracy is reliable and stable. Also another set of hardware measurements was performed with commercial DACs and ADCs (AD9764 and National Semiconductor ADC14L105) to evaluate the performance of the proposed method on the application for loopback mode. The

results show that the proposed method deals with the fault masking problem in loopback tests, and produces lower errors when predicting specifications.

Chapter 4 discusses a BOST scheme based transformer-coupled loop-back test for individual mixed signal specifications on differential signaling. A cascaded or double RF transformer used as the DfT circuit provides improved performance with regard to the imbalance, due to the reduction in parasitic capacitances. Using the characteristics of a cascaded RF transformer on the loopback signal path, we obtain differently weighted loopback responses. Then the spectral responses are used to characterize the characteristic parameters including imbalance caused by DUTs to provide the information about the nonlinear behavior of a DUT. The mapping function for the characterization is derived by a neural network algorithm. We test Analog-to-Digital Converters (ADCs) and Digital-to-Analog Converters (DACs) to demonstrate our approach.

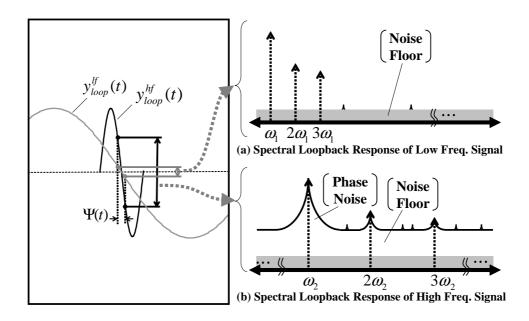

Chapter 5 explains efficient loopback test for aperture uncertainty in embedded mixed-signal circuits to improve prediction accuracy for aperture jitter and realize cost-effective test. A DUT is placed in a loopback mode that loops the output of one signal path back into the input of other signal path. Two tests are performed for the proposed method. In the first loopback test, a low frequency sinusoidal signal is applied to a DUT in loopback mode, and the spectral loopbacked response is characterized to find non-jitter related noise. Similarly in the second loopback test, a high frequency signal is applied and the resultant response is analyzed to find jitter induced-noise as well as non-jitter

related noise. As a result, characteristic parameters are obtained from their spectral response, and spectral equations are derived to characterize jitters present in DUTs. For predicting the aperture jitter of a DUT, the equations are solved by precisely separating the aperture jitter from input and clock jitters, and additive noise based on low-cost and efficient loopback scheme.

Chapter 6 summarizes this dissertation and draws conclusions of the completed work.

## Chapter 2

## Review of Analog and Mixed-Signal Testing

This chapter analyzes hardware architecture of self test compared with that of a recent ATE model. The comparison helps to understand how the hardware of self test can provide a complete alternative to the ATE. In addition, BIST and BOST approaches, which have been recently developed, are analyzed based on the understanding of the hardware architecture.

#### 2.1 Hardware Architecture of Self Test and ATE

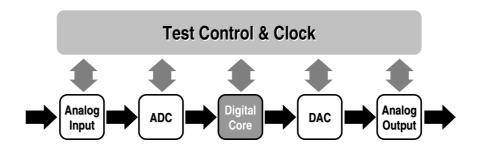

A common architecture for a mixed-signal circuit is shown in Figure 2.1. It includes analog input components, which are connected to the digital core (e.g. RAM, ROM or DSP) through an ADC. The digital output of the digital

Figure 2.1: Simple Block Diagram of Mixed-Signal System

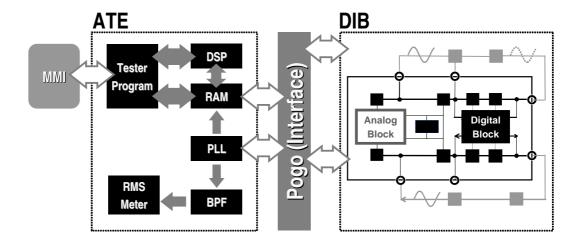

Figure 2.2: ATE Hardware Architecture

core is fed into a DAC, whose analog output is further transmitted to an analog output unit. By the transitional testing method, a ATE is applied and should provide both analog stimuli for the testing of analog parts (I/O blocks and ADC) and digital testing signals for the testing of digital components (DSP and DAC). Meanwhile, the ATE should be able to deal with the analog response as well as the digital response of the DUT. Such test environment is shown in Figure 2.2. The ATE is controlled through the tester program, and the tester hardware produces the testing analog and digital signals and feeds them into the DUT through pogo pins and Device Interface Board (DIB), which works as the interface between the ATE and the DUT. The digital response will be feed back directly into the load board and then returns to the ATE for further analyzing. The analog response is fed into the RMS meter on the ATE via a Band-Pass Filter (BPF) to get the testing parameters of the analog parts. The Phase Lock Loop (PLL) on the ATE provides the

Figure 2.3: Block Diagram of Self Test Logic

primary clock for the ATE, the DIB and the DUT as well. The tester program can be modified through the Man-Machine-Interface (MMI) that is typically a workstation based on a UNIX or WINDOWS operating system so that the ATE can carry out different testing tasks as well as test different DUTs.

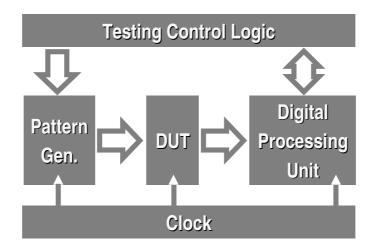

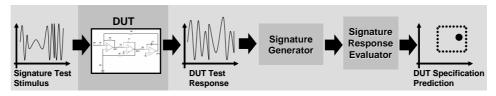

As an efficient alternative, self-test provides a convenient way to carry out the IC testing, whose architecture requires three additional components on chip, namely pattern generator, response processing unit, and testing controller as shown in Figure 2.3. Examples of pattern generators are a ROM with stored pattern or a chain of D-flip-flops. As a response processing unit, a comparator with a pre-set value or a linear feedback shift register (LFSR) is a typical implementation instance. A control unit is necessary to activate the test, manipulate the process and analyze the response. In general, several sub-tests can be carried out in one testing process. Sometimes the sampling rate of the DUT is different from that in other blocks. Hence the clock tree

stimulated by a primary clock provides the clocks with different rates to the different blocks. It should be pointed out that self-test has some drawbacks yet: it needs overhead, power and additional circuits. Of course, it also needs some layout efforts. However, self-test does provide many advantages in reducing the testing cost. It can overcome many of the signal quality problems associated with the parasitic effects introduced by cables connecting the equipment to the device. Generally, deriving from its nature of on-chip performed test tasks, self-test has the following advantages.

- Costly external test equipment can be avoided.

- Parasitic effects introduced by cables connecting the equipment to the device can be avoided.

- Testing technology can be kept up-to-date with newer-generation integrated circuits.

- Reduction of test time through parallelization.

- Analog multiplexers to make the internal nodes accessible need not to be included in the design.

## 2.2 State of the Art for BIST and BOST approaches

Many performance-based test methodologies based on BIST and BOST solutions have been proposed for mixed-signal testing in order to reduce the

costs associated with using testers and to enable testing of deeply embedded SoPs.

Azais [11]et al. presented a structure for the internal generation of a linear signal used with the histogram-based test technique. The structure is based on two highly linear ramp generators and a feedback control circuitry. In [33], the proposed BIST scheme in this work employs the delta-sigma modulation technique to generate the required linear ramp for testing the converters. Since they do not rely on the on-chip ADCs and DACs for stimulus generation and data conversion, the BIST strategy does not require the existence of both on-chip ADC and DAC, which makes it feasible for most mixed-signal IC's. However, a fundamental problem with these approaches is their need for a highly accurate signal to stimulate the DUT. Requirements for the stimulus input are typically substantially more precise than those of the DUT making the signal generator more challenging to design than the DUT itself and thereby raising the question of whether a test circuit is needed for the signal generator.

Several techniques [32, 59, 60, 83] have been published to generate onchip linear ramps, but the results either depend largely on the accuracy of the additional components in the test circuitry, or have not been proven experimentally. An on-chip ramp generator can perform monotonicity and histogram tests of ADCs, yet the linearity of the on-chip ramp generator itself needs to be very high. A FFT approximation algorithm was developed for on-chip sinusoidal signal generation and analysis in; however, the area and power penalties associated with FFT calculations are large as indicated by the fact that the BIST approach was implemented in the largest Xilinx Virtex-II series Field Programmable Gate Array (FPGA).

In [31,40], the authors attempt to test IP cores in an SoC by the embedded processor cores. The processor runs a test program that can deliver test patterns to the target IP cores via the PCI bus and then determine whether the chip is good or bad by verifying the test responses. This method mainly considers how to support scan testing using the system bus. One major problem with this method is that each core requires a buffer to hold the test data and a mechanism to convert the test data in each buffer into scan data for the associated core under test is needed. As a result, high area overhead is induced.

Simple and robust complete on-chip mixed-signal spectrum analyzers have been recently developed [47]. They performs the measurements in the analog domain, requiring small processing overhead. There is a special interest in the research community to look for solutions in the digital domain which aim to reduce the test cost and complexity. The advantage of this type of solutions are clear: robustness of digital circuitry, synthesis simplicity, reduced ATE requirements. However, the use of the approach is limited to low dynamic range applications.

Hanai et al. introduced the BOST approach for testing the electrical characteristics of high resolution ADC/DAC unit statically. In order to achieve high measurement accuracy, this methodology reduces the noise from inside

the tester by placing analog BOST on a performance board, and by placing a measuring circuit near the device to make the shortest length of wire. This minimizes the influence of external noise. Also the analog BOST includes the whole process from measuring to analyzing by self-control. The BOST is easily controlled by the circuitry implemented on the performance board and the processor installed in the tester. Therefore the test time can be reduced. However this approach requires the external conventional logic tester to generate noise caused by the characteristics of the long cable/wire between the performance board and the tester. Also the test cost is increased compared to on-chip test even though only fundamental functions of the conventional tester are used for the approach.

# Chapter 3

# Prediction of Mixed-Signal Dynamic Performance Using Optimized Signature-Based Alternate Test

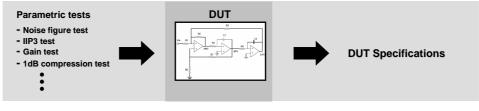

As mentioned in the previous chapters, short duration and optimized stimulus is applied to a DUT in the performance-based test. The response is analyzed to characterize the performance parameter of the DUT, without the need for a reference model for the DUT. Signature-based test is a common example of performance-based test. The signature test methodology includes applying a short duration test stimulus to the DUT and using the DUT response to estimate its performance as shown in Figure 3.1. Thus, compared to the conventional specification test, signature based test has the following advantages [62].

- 1. Multiple DUT specifications can be calculated using a single test response acquisition.

- 2. With conventional test, each specification test involves an overhead for setting up the instruments and the test configuration. On the other hand, the signature test approach uses a single test configuration and a single test stimulus, thereby reducing the overhead.

(a) Conventional Test

(b) Signature-Based Test

Figure 3.1: Signature-Based Test and Conventional Test

3. Finally, the instruments used to apply the signature test stimulus and measure the resulting response are much simpler and inexpensive, compared with the specialized instruments required for full specification test.

However there are several issues of the signature-based test as follows.

- 1. The analytical expressions using the signature resulting from the test cannot accurately represent the relationship between signatures and specifications.

- 2. The accuracy in the signature measurement is constrained by the BIST.

- 3. Unstable physical factors in the BIST circuitry can also cause signature values to be incorrect.

The Ternary Signal Representation (TSR) technique [89] improved the performance on the second problem mentioned above by using cost-effective BIST circuitry. However, the TSR technique still has the first and third problems. In short, if we use cost-effective BIST circuitry along with part of the TSR technique, the problems to be solved are the first and third problems.

This chapter proposes a novel methodology called Optimized Signature-Based Alternate Test (OSBAT), to improve the accuracy in prediction of specifications using strong correlation mapping and to reduce test time and cost. The purpose of this proposed methodology is to generate correlations between parameters for prediction of specifications with the predictive accuracy of statistical alternate test [78]. This technique will then accurately predict specifications of a DUT by using the strong correlation. As a result, the proposed approach overcomes the first and third limitations above by predictive accuracy of statistical alternate test. The method has been evaluated using simulations in our previous work [38].

# 3.1 Motivation of Approach

This section provides the overview of TSR technique as the motivation for the proposed methodology. The limitations of this technique are discussed.

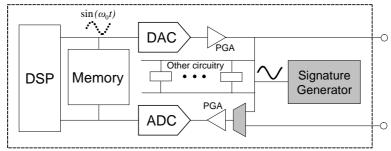

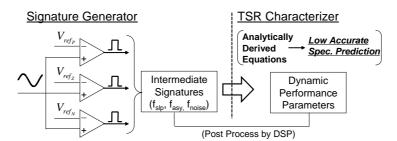

### 3.1.1 Ternary Signal Representation (TSR)

The theory of the TSR methodology is discussed in detail in [89]. Due to its non-linear behavior, a ADC/DAC module generates harmonic distortion

(a) BIST Circuitry of TSR Technique

(b) Signature Generation and Specification Prediction of TSR

Figure 3.2: Overview of TSR Technique

and noise when a pure signal is applied to its input. The TSR signature generator (Figure 3.2) is used to analyze and predict the dynamic performance from the resultant output of a system.

An overview of the TSR technique is given using the DAC as an example in Figure 3.2. To predict the performance parameters of a DAC, a pure sine wave is applied to the input of the DAC and the resultant output signal is analyzed by the TSR signature generator.

The signature generator consists of three comparators with different reference voltages: positive, zero, and negative. The digital signals quantized by the three comparators are used to generate DC offset  $(f_{asy})$ , slope  $(f_{slp})$ , and noise  $(f_{noise})$  of the fundamental signal by using the properties of harmonic distortion and noise. These intermediate signatures are discussed in Section 3.2.1 in detail. The TSR characterizer (Figure 3.2) then predicts the specifications of the DAC by using analytically derived equations with these signatures.

We define the TSR technique as the whole technique including the TSR signature generator and the TSR characterizer, and we assume that the TSR signature generator and the TSR characterizer are separate blocks.

### 3.1.2 Issues of TSR Technique

This section describes the solutions, which are provided by TSR technique, to overcome the limitations of signature-based test. The limitations of TSR technique are also discussed.

- 1. Conventional signature-based test cannot characterize accurate specifications of a DUT with signatures, because the correlation between them cannot be accurately derived due to lossy compression or high degree of dependence on mathematical relations. The TSR technique result shows a low error in prediction of specification [89]. However, the equations in the TSR characterizer cannot accurately describe the nonlinear relationship between the TSR signatures and the specifications, since the equations are analytically derived. Thus, there is a limit to the improvement of accuracy in measurement of specifications.

- 2. The accuracy in the signature measurement is constrained by the BIST. Methodologies minimizing the measurement error can lead to complexity in the BIST implementation. Thus, the measurement is limited by the BIST. This issue results in low accuracy measurement for signatures or specification parameters. The major advantages of using the TSR methodology are simple BIST circuitry and optimized signatures for cost-effective BIST. Thus, the TSR technique provides a solution to this problem [89].