US009413235B2

# (12) United States Patent

# Hunt et al.

#### (54) SYSTEM, METHOD AND APPARATUS FOR CONTROLLING CONVERTERS USING INPUT-OUTPUT LINEARIZATION

- (71) Applicants: Cirasys, Inc., Dallas, TX (US); The Board of Regents, The University of Texas System, Austin, TX (US)

- (72) Inventors: Louis R. Hunt, Plano, TX (US); Robert J. Taylor, Allen, TX (US)

- (73) Assignees: CIRASYS, INC., Dallas, TX (US); THE BOARD OF REGENTS, THE UNIVERSITY OF TEXAS SYSTEM, Austin, TX (US)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 172 days.

This patent is subject to a terminal disclaimer.

- (21) Appl. No.: 14/462,388

- (22) Filed: Aug. 18, 2014

## (65) **Prior Publication Data**

US 2014/0354255 A1 Dec. 4, 2014

#### **Related U.S. Application Data**

- (63) Continuation of application No. 12/487,242, filed on Jun. 18, 2009, now Pat. No. 8,810,221.

- (51) **Int. Cl.**

| H02M 3/156  | (2006.01) |

|-------------|-----------|

| <br>TT O OT |           |

- (52) U.S. Cl. CPC ...... *H02M 3/156* (2013.01)

- (58) Field of Classification Search

CPC . H02M 3/156; H02M 1/4225; H02M 3/1584; H02M 2003/00; H02M 3/005; H02M 3/157; H03F 2200/351; G05B 13/02; G05B 6/00

See application file for complete search history.

# (10) Patent No.: US 9,413,235 B2

## (45) **Date of Patent:** \*Aug. 9, 2016

(56) **References Cited**

## U.S. PATENT DOCUMENTS

| 4,630,187 A | 12/1986     | Henze            |  |

|-------------|-------------|------------------|--|

| 4,677,366 A | 6/1987      | Wilkinson et al. |  |

|             | (Continued) |                  |  |

#### FOREIGN PATENT DOCUMENTS

| WO | 2010148066 | 12/2010 |

|----|------------|---------|

| WO | 2012091850 | 7/2012  |

## OTHER PUBLICATIONS

Bodson, et al., "Differential-Geometric Methods for Control of Electric Motors," Int. J. of Robust and Nonlinear control 8, (1998), pp. 923-954.

(Continued)

Primary Examiner — Adolf Berhane

Assistant Examiner — Henry Lee, III

(74) Attorney, Agent, or Firm — Schultz & Associates, P.C.

## (57) ABSTRACT

A system, method and apparatus for controlling boost and buck-boost converters using input-output linearization and leading-edge modulation is provided. The controller includes a summing circuit connected to the converter to create a third voltage representing a difference between the first voltage and the second voltage. A gain circuit is connected to the summing circuit to adjust the third voltage by an appropriate gain. A modulating circuit is connected to the gain circuit, the converter, the first voltage, the second voltage and the second current to create a control signal based on the first voltage, the second voltage, the adjusted third voltage, the fourth voltage and the first current. The control signal is used to control the converter. Typically, the first voltage is a converter output voltage, the second voltage is a reference voltage, the fourth voltage is a converter input voltage, and first current is a converter inductor current.

#### 24 Claims, 8 Drawing Sheets

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 4,929,882 A    | 5/1990  | Szepesi            |

|----------------|---------|--------------------|

| 5,138,250 A    | 8/1992  | Capel              |

| 5,311,421 A    | 5/1994  | Nomura et al.      |

| 5,442,534 A    | 8/1995  | Cuk et al.         |

| 5,477,132 A    | 12/1995 | Canter et al.      |

| 5,708,433 A    | 1/1998  | Craven             |

| 5,804,950 A    | 9/1998  | Hwang et al.       |

| 5,886,586 A    | 3/1999  | Lai et al.         |

| 5,920,471 A    | 7/1999  | Rajagopalan et al. |

| 5,943,224 A    | 8/1999  | Mao                |

| 6,084,450 A    | 7/2000  | Smith et al.       |

| 6,366,070 B1   | 4/2002  | Cooke et al.       |

| 6,407,515 B1   | 6/2002  | Hesler et al.      |

| 6,462,962 B1   | 10/2002 | Cuk                |

| 6,538,905 B2   | 3/2003  | Greenfeld et al.   |

| 6,545,887 B2   | 4/2003  | Smedley et al.     |

| 6,674,272 B2   | 1/2004  | Hwang              |

| 6,956,360 B2   | 10/2005 | Matsuura et al.    |

| 7,103,425 B1   | 9/2006  | Marra, III et al.  |

| 7,239,257 B1   | 7/2007  | Alexander et al.   |

| 7,482,794 B2   | 1/2009  | Hunt et al.        |

| 7,489,186 B2   | 2/2009  | Segarra            |

| 7,602,166 B1   | 10/2009 | Kang               |

| 7,812,586 B2   | 10/2010 | Soldano et al.     |

| 7,851,941 B2   | 12/2010 | Walley             |

| 8,130,522 B2   | 3/2012  | Maksimovic         |

| 001/0030879 A1 | 10/2001 | Greenfeld et al.   |

| 003/0090253 A1 | 5/2003  | Balakrishnan       |

| 003/0199997 A1 | 10/2003 | Gao                |

| 003/0222627 A1 | 12/2003 | Hwang              |

| 006/0158910 A1 | 7/2006  | Hunt et al.        |

| 007/0046105 A1 | 3/2007  | Johnson et al.     |

| 007/0236200 A1 | 10/2007 | Canfield et al.    |

| 010/0141225 A1 | 6/2010  | Isham et al.       |

| 010/0164282 A1 | 7/2010  | Tseng et al.       |

| 010/0320978 A1 | 12/2010 | Hunt et al.        |

| 012/0146596 A1 | 6/2012  | Lin et al.         |

| 013/0301321 A1 | 11/2013 | Hunt               |

|                |         |                    |

2 2

2

2

2

## OTHER PUBLICATIONS

Ćuk, "Modelling, Analysis, and Design of Switching Converters," Dissertation, California Institute of Technology (1977), 317 pages. Deisch, C.W., "Simple Switching Control Method Changes Power Converter into a Current Source," IEEE Power Electronics Specialists Conference, 1978 Record, pp. 300-306.

Hunt, et al., "Design for Multi-Input Nonlinear Systems," Differential Geometric Control Theory, Birkhauser, Boston, R. W. Brockett, R. S. Millman, and H. J. Sussman, Eds., (1983), 268-298. Hunt, L.R., et al., "Global Transformations of Nonlinear Systems," IEEE Transactions on Automatic Control, vol. 28, Mo. 1, Jan. 1983, pp. 24-31.

Sidori, A. "Nonlinear Control Systems," 3rd Ed, Springer-Verlag London Limited (1995).

Ma, D., et al., "Enabling Power-Efficient DVFS Operations in Silicon," IEEE Circuits and Systems Magazine, First Quarter, 2010, 14-30.

Meyer, et al., "Applications of Nonlinear Transformations to Automatic Flight Control," Automatica, 20 (1984), 103-107.

Meyer, G., et al., "Nonlinear System Guidance in the Presence of Transmission Zero Dynamics," NASA Technical Memorandum 4661, Jan. 1995.

Middlebrook, et al., "A General Unified Approach to Modeling Switching-Converter Power Stages," IEEE Power Electronics Specialists Conference Record, Jun. 1976, pp. 18-34.

Mitchell, D. M., "DC-DC Switching Regulator Analysis, Reprint Edition," D.M. Mitchell Consultants, McGraw-Hill, Inc. (1988).

Ridley, Ray, "11 Ways to Generate Multiple Outputs," Switching Power Magazine, 2005, 1-12.

Ridley, "A New Small-Signal Model for Current-Mode Control," Ph. D. Dissertation, Virginia Polytechnic Institute and State University (1990) 15 pages. Sable, et al., "Elimination of the Positive Zero in Fixed Frequency

Sable, et al., "Elimination of the Positive Zero in Fixed Frequency Boost and Flyback Converters," Proceedings of 5th IEEE Applied Power Electronics Conference, 1990, pp. 205-211.

Sanders, "Nonlinear Control of Switching Power Converters," Ph.D. Dissertation, Massachusetts Institute of Technology (1989) 254 pages.

Shortt, Daniel J., "An Improved Switching Converter Model," Ph.D. Dissertation, Virginia Polytechnic Institute and State University (1982).

Sira-Ramirez, et al., "Exact Linearization in Switched Mode DC-to-DC Power Converters," Int. J. Control, 50 (1989), pp. 511-524.

Sira-Ramirez, "Switched Control of Bilinear Converters Via Pseudolinearization," IEEE Transactions on Circuits and Systems, vol. 36, No. 6, Jun. 1989, 8 pages.

Slotine, et al., "Applied Nonlinear Control," Prentice-Hall, Inc., Englewood Cliffs, 1991.

Su, R., "On the Linear Equivalents of Nonlinear Systems," Systems and Control Letters 2, (1982), 48-52.

Su, et al., "Linear Equivalents of Nonlinear Time-Varying Systems," International Symposium on Mathematical Theory of Networks and Systems (1981), 119-123.

Su, et al., "Robustness in Nonlinear Control," Differential Geometric Control Theory, Birkhauser, Boston, R. W. Brockett, R. S. Millman, and H. J. Sussman, Eds., (1983), 316-337.

Tang, Wei, "Average Current-Mode Control and Charge Control for PWM Converters," Ph. D. Dissertation, Virginia Polytechnic Institute and State University (1994).

Taylor, Robert J., "Feedback Linearization of Fixed Frequency PWM Converters," Ph.D. Dissertation, University of Texas at Dallas, published Nov. 2005, 173 pages.

FIG. 3A

FIG. 3B

FIG. 5

FIG. 7

FIG. 8

20

## SYSTEM, METHOD AND APPARATUS FOR CONTROLLING CONVERTERS USING INPUT-OUTPUT LINEARIZATION

#### CROSS-REFERENCE TO RELATED APPLICATIONS

This application is a continuation of application Ser. No. 12/487,242, filed Jun. 18, 2009. The patent application identified above is incorporated herein by reference in its entirety <sup>10</sup> to provide continuity of disclosure.

#### FIELD OF THE INVENTION

The present invention relates generally to providing modu-<sup>15</sup> lation signals to electrical circuits and, more particularly, to a system, method and apparatus for controlling converters using input-output linearization and leading-edge modulation.

#### BACKGROUND OF THE INVENTION

Power converters are used to convert one form of energy to another (e.g., AC to AC, AC to DC, DC to AC, and DC to DC) thereby making it usable to the end equipment, such as com- 25 puters, automobiles, electronics, telecommunications, space systems and satellites, and motors. Every application of power electronics involves some aspect of control. Converters are typically identified by their capability and/or configurations, such as, buck converters, boost converters, buck- 30 boost converters, boost-buck converters (Cuk), etc. For example, DC-DC converters belong to a family of converters known as "switching converters" or "switching regulators." This family of converters is the most efficient because the conversion elements switch from one state to another, rather 35 than needlessly dissipating power during the conversion process. Essentially there is a circuit with switches and two configurations (each can be modeled as linear systems) in which the converter resides according to the switch positions. The duty ratio (d) is the ratio indicating the time in which a 40 chosen switch is in the "on" position while the other switch is in the "off" position, and this d is considered to be the control input. Input d is usually driven by pulse-width-modulation (PWM) techniques.

Switching from one state to another and the accompanying 45 nonlinearity of the system causes problems. State space averaging reduces the switching problems to make the system, in general, a nonlinear averaged system for a boost converter or a buck-boost converter. But, control of the system under these nonlinear effects becomes difficult when certain performance 50 objectives must be met. For the most part linearization is done through a Taylor series expansion. Nonlinear terms of higher orders are thrown away and a linear approximation replaces the nonlinear system. This linearization method has proven effective for stabilizing control loops at a specific operating 55 point. However, use of this method requires making several assumptions, one of them being so-called "small signal operation." This works well for asymptotic stability in the neighborhood of the operating point, but ignores large signal effects which can result in nonlinear operation of the control 60 loop when, for example, an amplifier saturates during startup, or during transient modes, such as load or input voltage changes. Once nonlinear operation sets in, the control loop can have equilibrium points unaccounted for in the linearization. 65

One of the most widely used methods of pulse-width modulation is trailing-edge modulation (TEM), wherein the 2

on-time pulse begins on the clock and terminates in accordance with a control law. Unstable zero dynamics associated with TEM in the continuous conduction mode (CCM) prevent the use of an input-output feedback linearization because it would result in an unstable operating point. The other control method is leading-edge modulation (LEM), wherein the ontime pulse begins in accordance with a control law and terminates on the clock. The difference between LEM and TEM is that in TEM the pulse-width is determined by the instantaneous control voltage  $v_c$  prior to switch turn-off, whereas in LEM the pulse-width is determined by  $v_c$ , prior to switch turn-on.

There is, therefore, a need for a system, method and apparatus for controlling converters using input-output linearization that does not constrain stability to one operating point, but rather to a set of operating points spanning the expected range of operation during startup and transient modes of operation

#### SUMMARY OF INVENTION

The present invention provides a system, method and apparatus for controlling converters using input-output linearization that does not constrain stability to one operating point, but rather to a set of operating points spanning the expected range of operation during startup and transient modes of operation. In particular, the present invention uses leading edge modulation and input output linearization to compute the duty ratio of a boost converter or a buck-boost converter. The present invention can also be applied to other converter types. Moreover, the parameters in this control system are programmable, and hence the algorithm can be easily implemented on a DSP or in silicon, such as an ASIC.

Notably, the present invention provides at least four advantages compared to the dominant techniques currently in use for power converters. The combination of leading-edge modulation and input-output linearization provides a linear system instead of a nonlinear system. In addition, the "zero dynamics" becomes stable because the zeros of the linear part of the system are in the open left half plane. The present invention is also independent of stabilizing gain, as well as desired output voltage or desired output trajectory.

More specifically, the present invention provides a system that includes a boost or buck-boost converter having a first voltage at an output of the converter and a first current at an inductor within the converter, a reference voltage source having a second voltage, a fourth voltage from a voltage source providing an input voltage to the converter, and a PWM modulator/controller. The PWM modulator/controller includes a summing circuit connected to the converter and the reference voltage source to create a third voltage representing a difference between the first voltage from the output of the converter and the second voltage from the reference voltage source. A gain circuit is connected to the summing circuit to adjust the third voltage by a proportional gain or by any suitable type of controller, such as proportional (P), integral (I) or derivative (D) (or any combination of these three) controller. A modulating circuit is connected to the gain circuit, the converter to create a control signal that provides leadingedge modulation with input-output linearization based on the first voltage, the second voltage from the reference voltage source, the adjusted third voltage from the gain circuit, the fourth voltage from the voltage source or the input of the converter, and the first current from the inductor within the converter. The control signal is then used to control the converter. Whenever the converter is a boost converter, the control signal has a duty cycle defined by

10

15

$$d = \frac{(RR_cC + L)y - (L - R_sR_cC)Rx_1 - RR_cCu_0 + (R + R_c)LCk(y_0 - y)}{R(R_cCy - \frac{LR}{R + R_c}x_1)}.$$

Whenever the converter is a buck-boost converter, the control signal has a duty cycle defined by

$$d = \frac{(RR_cC + L)y + (L - R_cR_sC)Rx_1 + (R + R_c)LCk(y_0 - y)}{R\left(R_cCy + \frac{LR}{R + R_c}x_1 - R_cCu_0\right)}.$$

Note that the second voltage source can be integrated into the PWM modulator/controller. In addition, the PWM modulator/controller can be implemented using a digital signal processor, a field programmable gate array (FPGA) or conventional electrical circuitry. Moreover, the converter can be controlled with a proportional controller, or any suitable type of controller, such as a proportional (P), integral (I) or derivative (D) (or any combination of these three) controller, by replacing  $k(y_0-y)$  in the equation defining the duty cycle d with 25

$$\left(k_p + \frac{k_i}{s} + k_d s\right)(y_0 - y)$$

where  $k_p$ ,  $k_i$ , and  $k_d$  are the gains of the proportional, integral, and derivative terms of the controller.

The present invention also provides an apparatus that includes one or more electrical circuits that provide a control 35 signal to a boost converter such that a duty cycle of the control signal is defined as

$$d = \frac{(RR_cC + L)y - (L - R_sR_cC)Rx_1 - R_sC_cCu_0 + (R + R_c)LCk(y_0 - y)}{R(R_cCy - \frac{LR}{R + R_c}x_1)}.$$

Similarly, the present invention provides an apparatus that includes one or more electrical circuits that provide a control signal to a buck-boost converter such that a duty cycle of the control signal is defined as

$$d = \frac{(RR_cC + L)y + (L - R_cR_sC)Rx_1 + (R + R_c)LCk(y_0 - y)}{R\left(R_cCy + \frac{LR}{R + R_c}x_1 - R_cCu_0\right)}.$$

In either case, the apparatus may include a summing circuit, a gain circuit, a modulating circuit and various connections. The connections include a first connection to receive a first voltage from an output of the converter, a second connection to receive a second voltage from a reference voltage source, a 60 third connection to receive a first current from an inductor within the converter, a fourth connection to receive an input voltage from a voltage source providing an input to converter and a fifth connection to output a control signal to the converter. The summing circuit is connected to the first connection and the second connection to create a third voltage representing a difference between the first voltage from the 4

output of the converter and the second voltage from the reference voltage source. The gain circuit is connected to the summing circuit to adjust the third voltage by a proportional gain or by any suitable type of controller, such as proportional (P), integral (I) or derivative (D) (or any combination of these three) controller. The modulating circuit is connected to the gain circuit, the second connection, the third connection, the fourth connection and the fifth connection. The modulation circuit creates a control signal that provides leading-edge modulation with input-output linearization based on the first voltage from the output of the converter, the second voltage from the reference voltage source, the adjusted third voltage from the gain circuit, the fourth voltage from the voltage source or the input of the converter, and the first current from the inductor within the converter.

Moreover, the present invention can be sold as a kit for engineers to design and implement a PWM modulated converter (boost or buck-boost). The kit may include a digital signal processor, or field programmable gate array (FPGA), 20 and a computer program embodied on a computer readable medium for programming the digital signal processor, or FPGA, to control the PWM modulated converter. The computer program may also include one or more design tools. The digital signal processor, or FPGA, includes a summing circuit, a gain circuit, a modulating circuit and various connections. The various connections include a first connection to receive a first voltage from an output of the converter, a second connection to receive a second voltage from a reference voltage source, a third connection to receive a first 30 current from an inductor within the converter, a fourth connection to receive the input voltage from a voltage source providing an input to converter, and a fifth connection to output a control signal to the converter. The summing circuit is connected to the first connection and the second connection to create a third voltage representing a difference between the first voltage from the output of the converter and the second voltage from the reference voltage source. The gain circuit is connected to the summing circuit to adjust the third voltage by a proportional gain or by any suitable type of controller, such as proportional (P), integral (I) or derivative (D) (or any 40 combination of these three) controller. The modulating circuit is connected to the gain circuit, the second connection, the third connection, the fourth connection and the fifth connection. The modulation circuit creates a control signal that provides leading-edge modulation with input-output linearization based on the first voltage from the output of the converter, the second voltage from the reference voltage source, the adjusted third voltage from the gain circuit, fourth voltage from the voltage source or the input of the converter, and a first current from the inductor within the converter. Whenever the converter is a boost converter, the control signal has a duty 50 cycle defined by

$$d = \frac{(RR_{c}C + L)y - (L - R_{s}R_{c}C)Rx_{1} - RR_{c}Cu_{0} + (R + R_{c})LCk(y_{0} - y)}{R\left(R_{c}Cy - \frac{LR}{R + R_{c}}x_{1}\right)}.$$

55

Whenever the converter is a buck-boost converter, the control signal has a duty cycle defined by

$$t = \frac{(RR_cC + L)y + (L - R_cR_sC)Rx_1 + (R + R_c)LCk(y_0 - y)}{R\left(R_cCy + \frac{LR}{R + R_c}x_1 - R_cCu_0\right)}.$$

35

60

65

Furthermore, the present invention provides a method for controlling a boost or buck-boost converter using a PWM modulator/controller by receiving a first voltage from an output of the converter, a second voltage from a reference voltage source, a first current from an inductor within the converter, and creating a third voltage representing a difference between the first voltage from the output of the converter and the second voltage from the reference voltage source and a fourth voltage from a voltage source or the input of the converter. The third voltage is then adjusted by a proportional gain or by any suitable type of controller, such as proportional (P), integral (I) or derivative (D) (or any combination of these three) controller. The control signal is created that provides leadingedge modulation with input-output linearization based on the first voltage from the output of the converter, the second voltage from the reference voltage source, the adjusted third voltage, the fourth voltage from the voltage source or the input of the converter, and the first current from the inductor within the converter. The converter is then controlled using  $_{20}$ the control signal created by the PWM modulator/controller. Whenever the converter is a boost converter, the control signal has a duty cycle defined by

$$d = \frac{(RR_cC + L)y - (L - R_sR_cC)Rx_1 - RR_cCu_0 + (R + R_c)LCk(y_0 - y)}{R\left(R_cCy - \frac{LR}{R + R_c}x_1\right)}.$$

Whenever the converter is a buck-boost converter, the control signal has a duty cycle defined by

$$d = \frac{(RR_cC + L)y + (L - R_cR_sC)Rx_1 + (R + R_c)LCk(y_0 - y)}{R\left(R_cCy + \frac{LR}{R + R_c}x_1 - R_cCu_0\right)}.$$

Note that the converter can be controlled with a proportional controller, or any suitable type of controller, such as proportional (P), integral (I) or derivative (D) (or any combination of these three) controller, by replacing  $k(y_0-y)$  in the equation defining the duty cycle d with

$$\left(k_p + \frac{k_i}{s} + k_d s\right)(y_0 - y)$$

where  $k_p$ ,  $k_i$ , and  $k_d$  are the gains of the proportional, integral, <sup>50</sup> and derivative terms of the controller. Moreover, the control signal can be created using a first order system, or can be independent of a stabilizing gain, a desired output voltage or a desired output trajectory. Likewise, the present invention may include a computer program embodied within a digital <sup>55</sup> signal processor, or FPGA, wherein the steps are implemented as one or more code segments.

## BRIEF DESCRIPTION OF THE DRAWINGS

The above and further advantages of the invention may be better understood by referring to the following description in conjunction with the accompanying drawings.

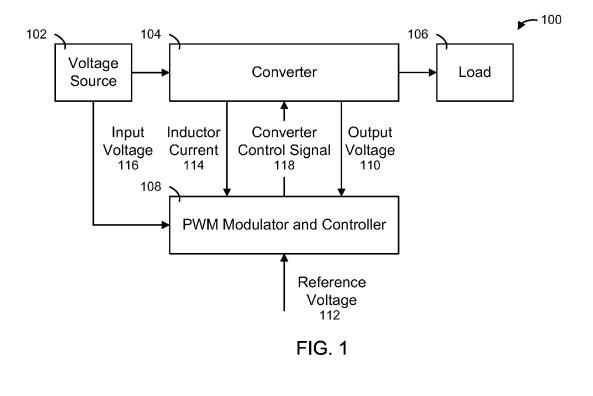

FIG. 1 is a block diagram of a system in accordance with the present invention.

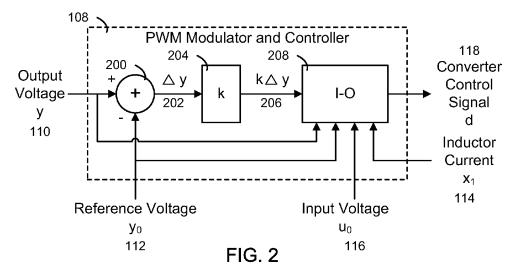

FIG. **2** is a block diagram of a modulator/controller in accordance with the present invention.

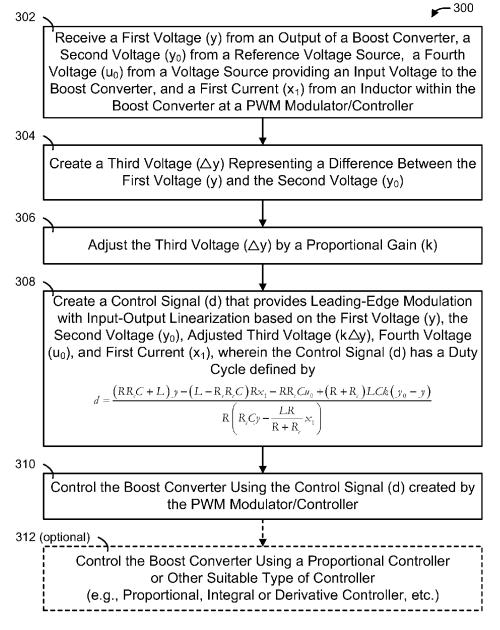

FIG. **3**A is a flow chart of a method for controlling a boost converter using a PWM modulator/controller in accordance with the present invention.

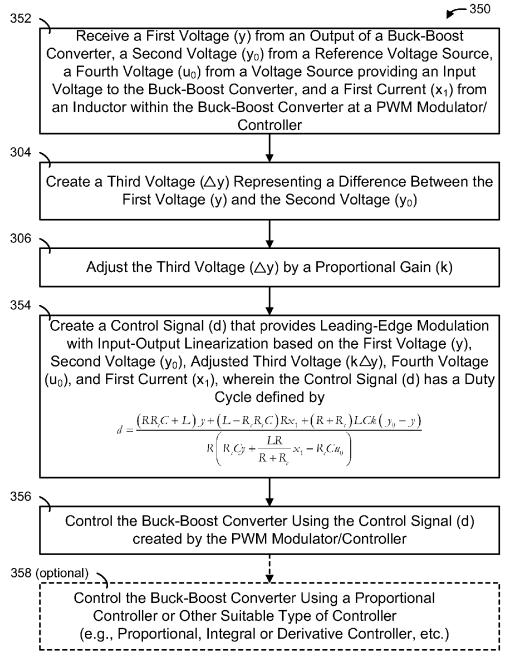

FIG. **3**B is a flow chart of a method for controlling a buck-boost converter using a PWM modulator/controller in accordance with the present invention.

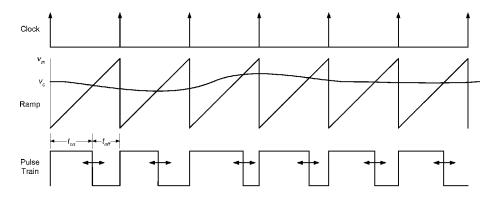

FIGS. **4**A and **4**B are graphs of trailing-edge modulation of a PWM signal and leading-edge modulation of a PWM

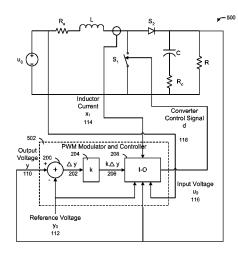

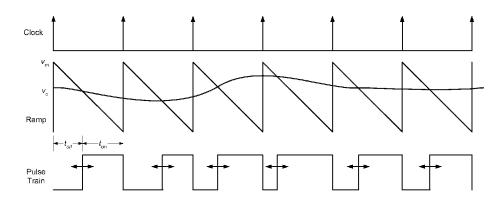

FIG. **5** is circuit diagram of a boost converter and a modulator/controller in accordance with the present invention.

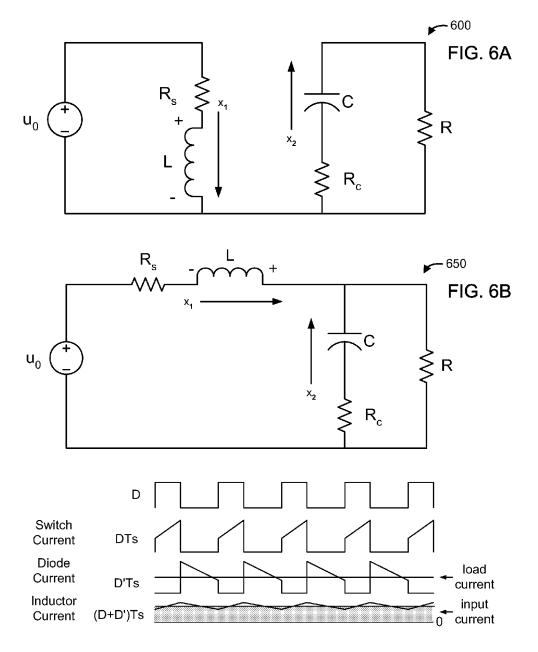

FIGS. **6**A and **6**B are linear circuit diagrams of a boost converter during time DTs and D'Ts, respectively in accordance with the present invention.

FIG. **7** is a graph of typical waveforms for the boost converter for the two switched intervals DTs and D'Ts in accordance with the present invention.

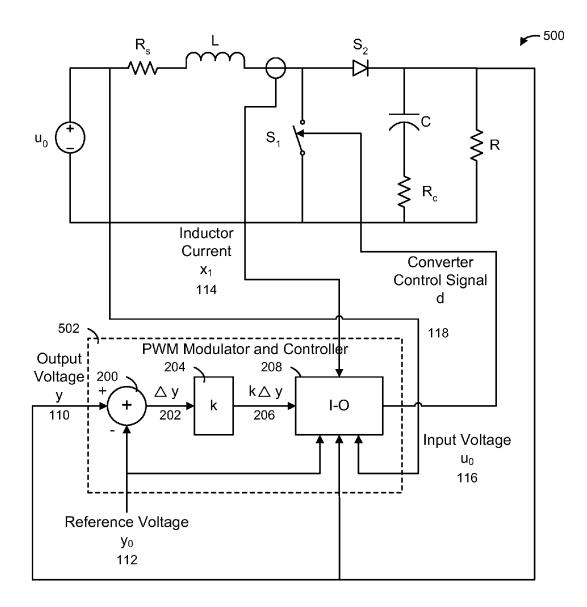

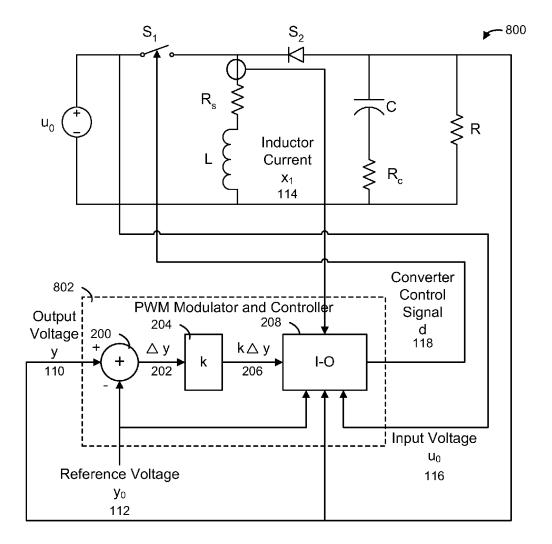

FIG. 8 is circuit diagram of a buck-boost converter and a modulator/controller in accordance with the present invention.

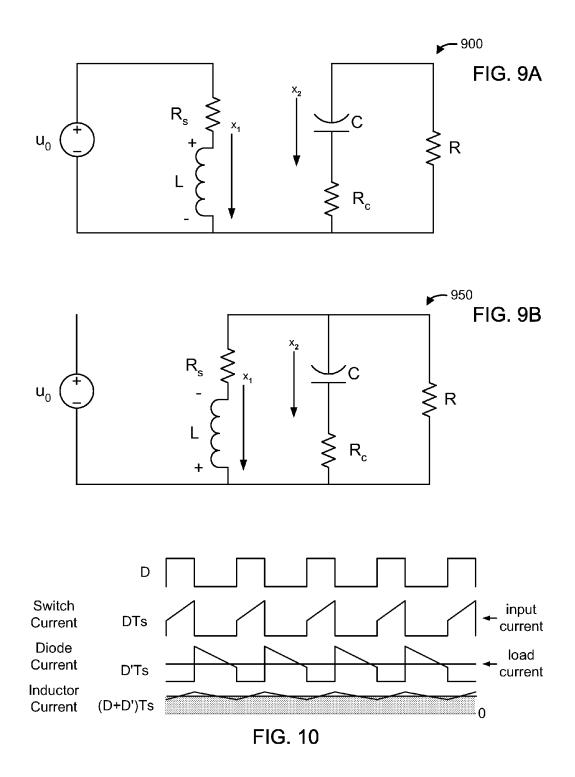

FIGS. **9**A and **9**B are linear circuit diagrams of a buckboost converter during time DTs and D'Ts, respectively in accordance with the present invention.

FIG. 10 is a graph of typical waveforms for the buck-boost converter for the two switched intervals DTs and D'Ts in<sup>25</sup> accordance with the present invention.

## DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENT

In the description that follows, like parts are marked throughout the specification and figures with the same numerals, respectively. The figures are not necessarily drawn to scale and may be shown in exaggerated or generalized form in the interest of clarity and conciseness.

While the making and using of various embodiments of the present invention are discussed in detail below, it should be appreciated that the present invention provides many applicable inventive concepts that can be embodied in a wide variety of specific contexts. The specific embodiments discussed herein are merely illustrative of specific ways to make and use the invention and do not delimit the scope of the invention.

The present invention provides a system, method and apparatus for controlling converters using input-output linearization that does not constrain stability to one operating point, but rather to a set of operating points spanning the expected range of operation during startup and transient modes of operation. In particular, the present invention uses leadingedge modulation and input-output linearization to compute the duty ratio of a boost converter or a buck-boost converter. The present invention can also be applied to other converter types. Moreover, the parameters in this control system are programmable, and hence the algorithm can be easily implemented on a DSP or in silicon, such as an ASIC.

Notably, the present invention provides at least four advantages compared to the dominant techniques currently in use for power converters. The combination of leading-edge modulation and input-output linearization provides a linear system instead of a nonlinear system. In addition, the "zero dynamics" becomes stable because the zeros of the linear part of the system are in the open left half plane. The present invention is also independent of stabilizing gain, as well as desired output voltage or desired output trajectory.

As previously described, trailing-edge modulation for boost and buck-boost converters operating in the continuous conduction mode gives rise to unstable zero dynamics where the linear part of the system about an operating point has a

right half plane zero. In contrast, the present invention employs leading-edge modulation, along with some very simple design constraints, that change the zero dynamics so that the linear part of the system has only open left half plane zeros. Since the nonlinear system now possesses stable zero 5 dynamics, input-output feedback linearization can be used. To apply this method, the actual output y is chosen as output function h(x), and y is repeatedly differentiated until the input u appears. The number of differentiations, r, is called the relative degree of the system. The present invention has a relative degree r=1. The linearizing transformation for d is solved and used for the control input. This transformation is local in nature, but it can be applied in a neighborhood of any state space operating point in DC-DC conversion.

It is desirable to choose any operating point for the nonlin- 15 a duty cycle defined by ear system. This operating point can be made locally asymptotically stable by the above process if a gain k is chosen to be positive. The gain k does not have to be adjusted for each operating point, i.e., no gain scheduling is required. However, the reference input will have to be walked up, which is typical 20 of soil-start operation, to insure convergence to the operating point. Note that Proportional (P), Integral (I), Derivative (D), Proportional-Integral (PI), and Proportional-Integral-Derivative (PID) control loops can be added for robustness.

Now referring to FIG. 1, a block diagram of a system 100 25 in accordance with the present invention is shown. The system includes a power source (voltage) 102 connected to a converter 104 that provides power to a load 106. The converter 104 is either a boost converter or a buck-boost converter. The converter 104 is also connected to the PWM 30 modulator/controller 108. The PWM modulator/controller 108 receives a first voltage 110 from an output of the converter 104, a second voltage (reference voltage) 112 from a voltage reference source (not shown), a first current 114 from an inductor within the converter, and a fourth voltage 116 35 signal is defined as from the voltage source 102 (i.e., the input voltage to the converter 104). A summing circuit within the PWM modulator and controller 108 creates a third voltage representing the difference between the first voltage 110 from the output of the converter 104 and the second voltage 112 from the reference 40 voltage source. Note that the source of the second voltage 112 (voltage reference source) can be integrated within or external to the PWM modulator/controller 108. The PWM modulator/controller 108 uses the first voltage 110, the second voltage 112, the first current 114 and the fourth voltage 116 to 45 generate a control signal 118 that is used to control the converter 104. The details of how the PWM modulator/controller 108 generates the control signal 118 will be described in more detail below. In addition, the PWM modulator/controller 108 can be implemented using a digital signal processor, an 50 FPGA, or conventional electrical circuitry.

Referring now to FIGS. 1 and 2, a block diagram of a modulator/controller 108 in accordance with the present invention is shown. The modulator/controller 108 includes a summing circuit 200, a gain circuit 204, a modulating circuit 55 a gain circuit, a modulating circuit and various connections. 208 and various connections. The connections include a first connection to receive a first voltage (output voltage (y)) 110 from the converter 104, a second connection to receive a second voltage (reference voltage  $(y_0)$ ) 112 from a reference voltage source (not shown), a third connection to receive a 60 first current (inductor current  $(x_1)$ ) 114 from the converter 104, a fourth connection to receive an input voltage  $(u_0)$  116 from the voltage source 102 (i.e., the input voltage to the converter 104), and a fifth connection to output a control signal (d) 118 to the converter 104. The summing circuit 200 is connected to the first connection and the second connection to create a third voltage ( $\Delta y$ ) 202 representing a difference

8

between the first voltage (y) **110** and the second voltage  $(y_0)$ 112. The gain circuit 204 is connected to the summing circuit **200** to adjust the third voltage ( $\Delta y$ ) **202** by a proportional gain (k), or by any suitable controller, such as proportional (P), integral (I) or derivative (D) (or any combination of these three) controller. The modulating circuit 208 is connected to the gain circuit 204, the second connection, the third connection, the fourth connection and the fifth connection. The modulation circuit 208 creates a control signal (d) 118 that provides leading-edge modulation with input-output linearization based on the first voltage (y) 110, the second voltage  $(y_0)$  112, the adjusted third voltage  $(k\Delta y)$  206, the first current  $(x_1)$  114 and the fourth voltage  $(u_0)$  116. Whenever the converter 104 is a boost converter, the control signal (d) 118 has

$$d = \frac{(RR_cC + L)y - (L - R_sR_cC)Rx_1 - RR_cCu_0 + (R + R_c)LCk(y_0 - y)}{R\left(R_cCy - \frac{LR}{R + R_c}x_1\right)}.$$

Whenever the converter 104 is a buck-boost converter, the control signal (d) 118 has a duty cycle defined by

$$t = \frac{(RR_{c}C + L)y + (L - R_{c}R_{s}C)Rx_{1} + (R + R_{c})LCk(y_{0} - y)}{R(R_{c}Cy + \frac{LR}{R + R_{c}}x_{1} - R_{c}Cu_{0})}$$

The present invention also provides an apparatus having one or more electrical circuits that provide a control signal 118 to a boost converter such that a duty cycle of the control

$$t = \frac{(RR_{c}C + L)y - (L - R_{s}R_{c}C)Rx_{1} - R_{c}Cu_{0} + (R + R_{c})LCk(y_{0} - y)}{R(R_{c}Cy - \frac{LR}{R + R_{c}}x_{1})}.$$

Similarly, the present invention provides an apparatus having one or more electrical circuits that provide a control signal 118 to a buck-boost converter such that a duty cycle of the control signal is defined as

$$d = \frac{(RR_cC + L)y + (L - R_cR_sC)Rx_1 + (R + R_c)LCk(y_0 - y)}{R\left(R_cCy + \frac{LR}{R + R}x_1 - R_cCu_0\right)}$$

In either case, the apparatus may include a summing circuit, The connections include a first connection to receive a first voltage (y) 110 from the converter 104, a second connection to receive a second voltage  $(y_0)$  **112** from a reference voltage source, a third connection to receive a first current  $(x_1)$  114 from the converter 104, a fourth connection to receive a fourth voltage  $(u_0)$  116 from the voltage source 102 (i.e., the input voltage to the converter 104), and a fifth connection to output a control signal (d) **118** to the converter **104**. The summing circuit 200 is connected to the first connection and the second connection to create a third voltage ( $\Delta y$ ) 202 representing a difference between the first voltage (y) 110 and the second voltage  $(y_0)$  112. The gain circuit 204 is connected to the

summing circuit **200** to adjust the third voltage ( $\Delta$ y) **202** by a proportional gain (k), or by any suitable controller, such as proportional (P), integral (I) or derivative (D) (or any combination of these three) controller. The modulating circuit **208** is connected to the gain circuit **204**, the second connection, the <sup>5</sup> third connection, the fourth connection and the fifth connection. The modulation circuit **208** creates a control signal (d) that provides leading-edge modulation with input-output linearization based on the first voltage (y) **110** from the output of the converter **104**, the second voltage ( $x_0$ ) **112** from the reference voltage source, the adjusted third voltage ( $x_{\Delta}$ y) **206** from the gain circuit **204**, the first current ( $x_1$ ) **114** from the inductor within the converter **104** and the fourth voltage to the 15 converter **104**).

The present invention can be sold as a kit for engineers to design and implement a PWM modulated converter (boost or buck-boost). The kit may include a digital signal processor, or FPGA, and a computer program embodied on a computer 20 readable medium for programming the digital signal processor, or FPGA, to control the PWM modulated converter. The computer program may also include one or more design tools. The digital signal processor, or FPGA, includes a summing circuit 200, a gain circuit 204, a modulating circuit 208 and 25 various connections. The connections include a first connection to receive a first voltage 110, a second connection to receive a second voltage 112, a third connection to receive a first current 114, a fourth connection to receive an input voltage **116**, and a fifth connection to output a control signal **118**. The summing circuit **200** is connected to the first connection and the second connection to create a third voltage  $(\Delta y)$  202 representing a difference between the first voltage and the second voltage. The gain circuit 204 is connected to the summing circuit 200 to adjust the third voltage ( $\Delta y$ ) 202 35 by a proportional gain (k) or by any suitable controller, such as proportional (P), integral (I) or derivative (D) (or any combination of these three) controller. The modulating circuit 208 is connected to the gain circuit 204, the second connection, the third connection, the fourth connection and the fifth 40 connection. The modulation circuit 208 creates a control signal 118 that provides leading-edge modulation with inputoutput linearization based on the first voltage (y) 110, the second voltage  $(y_0)$  112, the adjusted third voltage  $(k\Delta y)$  206, the first current  $(x_1)$  114 and the input voltage  $(u_0)$  116. 45 Whenever the converter 104 is a boost converter, the control signal (d) 118 has a duty cycle defined by

$$d = \frac{(RR_cC + L)y - (L - R_sR_cC)Rx_1 - RR_cCu_0 + (R + R_c)LCk(y_0 - y)}{R(R_cCy - \frac{LR}{R + R_c}x_1)}.$$

Whenever the converter **104** is a buck-boost converter, the control signal (d) **118** has a duty cycle defined by

$$d = \frac{(RR_{c}C + L)y + (L - R_{c}R_{s}C)Rx_{1} + (R + R_{c})LCk(y_{0} - y)}{R\left(R_{c}Cy + \frac{LR}{R + R_{c}}x_{1} - R_{c}Cu_{0}\right)}.$$

As implemented in the system of FIG. 1, the first voltage 110 is an output voltage from the converter 104, the second volt- 65 age 112 is a reference voltage, the first current 114 is an inductor current from the converter 104 and the fourth voltage

**116** is the voltage provided by the voltage source **102** as the input voltage of the converter **104**.

Now referring to FIG. **3A**, a flow chart **300** of a control method for a boost converter in accordance with the present invention is shown. The boost converter is controlled by receiving a first voltage (y) from an output of a boost converter, a second voltage (y<sub>0</sub>) from a reference voltage source, a first current (x<sub>1</sub>) from an inductor within the boost converter and a fourth voltage (u<sub>0</sub>) from the input of the converter at a PWM modulator/controller in block **302**. A third voltage ( $\Delta$ y) is created representing a difference between the first voltage (y) and the second voltage (y<sub>0</sub>) in block **304**. The third voltage (y<sub>0</sub>) is adjusted by a proportional gain (k) or any suitable type of controller, such as proportional (P), integral (I) or derivative (D) (or any combination of these three) by replacing k(y<sub>0</sub>-y) in the equation defining the duty cycle d with

$$\left(k_p + \frac{k_i}{s} + k_d s\right)(y_0 - y)$$

where  $k_p$ ,  $k_i$ , and  $k_d$  are the gains of the proportional, integral, and derivative terms of the controller in block **306**. If  $k_i$  and  $k_d$ are both zero, then the controller reduces to a proportional controller. If only  $k_d$  is zero, then the controller reduces to a proportional-integral (PI) controller. The control signal (d) is created in block **308** that provides leading-edge modulation with input-output linearization based on the first voltage (y), the second voltage ( $y_0$ ), the adjusted third voltage ( $k\Delta y$ ), the first current ( $x_1$ ) and the fourth voltage ( $u_0$ ), wherein the control signal (d) has a duty cycle defined by

$$d = \frac{(RR_cC + L)y - (L - R_sR_cC)Rx_1 - RR_cCu_0 + (R + R_c)LCk(y_0 - y)}{R\left(R_cCy - \frac{LR}{R + R_c}x_1\right)}.$$

The boost converter is then controlled using the control signal (d) created by the PWM modulator/controller in block **310**. In an optional embodiment, the boost converter is controlled in block **312** using a proportional controller, or any suitable type of controller, such as proportional (P), integral (I) or derivative (D) (or any combination of these three) by replacing  $k(y_0-y)$  in the equation defining the duty cycle d with

0

$$\left(k_p + \frac{k_i}{s} + k_d s\right)(y_0 - y)$$

5

where k<sub>p</sub>, k<sub>i</sub>, and k<sub>d</sub> are the gains of the proportional, integral, and derivative terms of the controller. If k<sub>i</sub> and k<sub>d</sub> are both

zero, then the controller reduces to a proportional controller. If only k<sub>d</sub> is zero, then the controller reduces to a proportional integral (PI) controller. Note that the control signal can be created using a first order system, or can be independent of a stabilizing gain, a desired output voltage or a desired output

trajectory. Likewise, the present invention may include a computer program embodied within a digital signal processor, or FPGA, wherein the steps are implemented as one or more code segments.

Now referring to FIG. **3**B, a flow chart **350** of a control method for a buck-boost converter in accordance with the present invention is shown. The buck-boost converter is controlled by receiving a first voltage (y) from an output of a

buck-boost converter, a second voltage  $(y_0)$  from a reference voltage source, a first current  $(x_1)$  from an inductor within the buck-boost converter and a fourth voltage  $(u_0)$  from voltage source providing an input to the buck-boost converter at a PWM modulator/controller in block **352**. A third voltage ( $\Delta y$ ) is created representing a difference between the first voltage (y) and the second voltage  $(y_0)$  in block **304**. The third voltage  $(y_0)$  is adjusted by a proportional gain (k), or any suitable type of controller, such as a proportional (P), integral (I) or deriva-10tive (D) (or any combination of these three) controller, by replacing  $k(y_0-y)$  in the equation defining the duty cycle d with

$$\left(k_p + \frac{k_i}{s} + k_d s\right)(y_0 - y)$$

where  $k_p$ ,  $k_i$ , and  $k_d$  are the gains of the proportional, integral, and derivative terms of the controller in block **306**. If  $k_i$  and  $k_{d}$  20 are both zero, then the controller reduces to a proportional controller. If only  $k_d$  is zero, then the controller reduces to a proportional-integral (PI) controller. The control signal (d) is created in block 354 that provides leading-edge modulation with input-output linearization based on the first voltage (y), 25 the second voltage  $(y_0)$ , the adjusted third voltage  $(k\Delta y)$ , the first current  $(x_1)$  and the fourth voltage  $(u_0)$ , wherein the control signal (d) has a duty cycle defined by

$$d = \frac{(RR_cC + L)y + (L - R_cR_sC)Rx_1 + (R + R_c)LCk(y_0 - y)}{R\left(R_cCy + \frac{LR}{R + R_c}x_1 - R_cCu_0\right)}.$$

The buck-boost converter is then controlled using the control signal (d) created by the PWM modulator/controller in block **356**. In an optional embodiment, the buck-boost converter is controlled in block 358 using a proportional controller, or any suitable type of controller, such as a proportional (P), integral  $_{40}$ (I) or derivative (D) (or any combination of these three) controller, by replacing  $k(y_0-y)$  in the equation defining the duty cycle d with

$$\left(k_p + \frac{k_i}{s} + k_d s\right)(y_0 - y)$$

where  $k_p$ ,  $k_i$ , and  $k_d$  are the gains of the proportional, integral, and derivative terms of the controller. If  $k_i$  and  $k_d$  are both 50 zero, then the controller reduces to a proportional controller. If only  $k_d$  is zero, then the controller reduces to a proportionalintegral (PI) controller. Note that the control signal can be created using a first order system, or can be independent of a stabilizing gain, a desired output voltage or a desired output 55 dard dot product on  $\Re^n$ . trajectory. Likewise, the present invention may include a computer program embodied within a digital signal processor, or FPGA, wherein the steps are implemented as one or more code segments.

A more detailed description of the models used in the 60 present invention will now be described. State space averaging allows the adding together of the contributions for each linear circuit during its respective time interval. This is done by using the duty ratio as a weighting factor on each interval. As shown below, this weighting process leads to a single set 65 of equations for the states and the output. But first, the system will be described by its state space equations.

Assume that a linear system (A, b) is described by

$$(t) = Ax(t) + bu(t) \tag{1}$$

where  $A \in \Re^{n \times n}$  is an 'n×n' matrix, and  $b \in \Re^n$  is an 'n×1' column vector.

As previously mentioned, the duty ratio d is the ratio indicating the time in which a chosen switch is in the "on" position while the other switch is in the "off" position. Ts is the switching period. The "on" time is then denoted as dTs. The general state equations for any type of converter consisting of two linear switched networks are as follows: For  $0 \le t \le dTs$ ,

$\dot{x}(t) = A_{\alpha}x(t) + b_{\alpha}u(t)$ (2a)

<sup>15</sup> dTs≤t≤Ts,

(2b)

(4)

The equations in (2a) can be combined with the equations in (2b) using the duty ratio, d, as a weighting factor. Thus,

$$\dot{x}(t) = (dA_{\alpha} + d'A_{\beta})x(t) + (db_{\alpha} + d'b_{\beta})u(t)$$

(3)

which can be written in the form of equation (1) as

$\dot{x}(t) = Ax(t) + bu(t)$

$\dot{x}(t)=A_{\rm B}x(t)+b_{\rm B}u(t)$

with

$A = dA_{\alpha} + d'A_{\beta}$

and

30

$$h=dh + d'h$$

where d'=1-d.

The buck cell is linear after state-space averaging and is therefore the easiest topology to control. On the other hand, the boost and buck-boost cells are nonlinear and have nonminimum phase characteristics. These nonlinear cells will be described.

Beginning with a vector field f(x) and a scalar function h(x), the Lie derivative of h with respect to f is denoted by L.h. The derivative is a scalar function and can be understood as the directional derivative of h in the direction of the vector field f.

Definition: For a smooth scalar function b:  $\mathfrak{R}^n \rightarrow \mathfrak{R}$  and a 45 smooth vector field f:  $\mathfrak{R}^n \rightarrow \mathfrak{R}^n$ , the Lie derivative of h with respect to f is

$$L_f b = \nabla b f.$$

(5)

or

$$L_{t}b = \langle \nabla b_{t}f \rangle \tag{6}$$

where  $\nabla$  represents the gradient and bold type represents a vector field,  $\nabla bf$  is matrix multiplication, and  $\langle \nabla b, f \rangle$  is stan-

Lie derivatives of any order can be defined as

$$L_{f}^{0}b = b$$

(7)

$$L_f^i b = \nabla (L_f^{i-1} b) f = L_f L_f^{i-1} b.$$

(8)

Also if g is another smooth vector field g:  $\mathfrak{R}^n \rightarrow \mathfrak{R}^n$ , then

$$L_g L_f b = \nabla (L_f b) g. \tag{9}$$

Now, add an output y to the nonlinear system  $\dot{x}=f(x)+g(x)u$ , where f(x) and g(x) are  $C^{\infty}$  vector fields on  $\mathbb{R}^n$ . Unlike inputstate linearization where a transformation is first found to generate a new state vector and a new control input, here the 5 (10)

15

20

and

$\eta = \begin{bmatrix} \cdot \cdot \cdot \\ \vdots \end{bmatrix}$

| output y is repeatedly differentiated until the input u appears, |

|------------------------------------------------------------------|

| thereby showing a relationship between y and u.                  |

For the nonlinear system

$\dot{x} = f(x) + g(x)u$

v=b(x)

and a point  $x_0$ , we differentiate y once to get

$$\dot{v} = \nabla b\dot{x} = \nabla bf(x) + \nabla bg(x)u = L_{f}b(x) + L_{g}b(x)u$$

This is differentiated repeatedly until the coefficient of u is non-zero. This procedure continues until for some integer  $r \le n$

$L_g L_f^i b(x) = 0$  for all x near  $x_0$  and  $0 \le i \le r-2$

$L_{g}L_{f}^{r-1}b(x_{0})\neq 0$

Then

$$u = -\frac{(L_f^r b(x) + v)}{L_g L_f^{r-1} b(x)}$$

(11)

and, for v=0, results in a multiple integrator system with  $_{\rm 25}$  transfer function

$$H(s) = \frac{1}{s^r} \tag{12}$$

State feedback can be added for pole placement with

$$v = c_0 b(x) + c_1 L_f b(x) + c_2 L_f^2 b(x) + \dots + c_{r-1} L_f^{r-1} b(x),$$

where  $c_0, c_1, \ldots, c_{r-1}$ , are constants to be chosen, and the <sup>35</sup> integer r is the relative degree of the system (2-10). It is the number of differentiations required before u appears.

The first r new coordinates are found as above by differentiating the output h(x)

$$\begin{aligned} \dot{z}_1 &= L_f b(x(t)) = z_2 \end{aligned} \tag{13} \\ \dot{z}_2 &= L_f^2 b(x(t)) = z_3 \\ & \cdots \\ \dot{z}_{r-1} &= L_f^{r-1} b(x(t)) = z_r \\ \dot{z}_r &= L_f^r b(x(t)) + L_g L_f^{r-1} b(x(t)) u(t) \end{aligned}$$

#### Since $x(t) = \Phi^{-1}(z(t))$ , let

$a(z) = L_g L_f^{r-1} b(\Phi^{-1}(z))$

#### $b(z) = L_f^r b(\Phi^{-1}(z))$

which is recognized from (11) that a(z) is the denominator term and b(z) is the numerator. Now

$\dot{z}_r = b(z(t)) + a(z(t))u(t)$

where a(z(t)) is nonzero for all z in a neighborhood of  $z^0$ . To find the remaining n-r coordinates, let

14 -continued

Here  $z_{r+1}, \ldots, z_n$  are added to  $z_1, \ldots, z_r$  to provide a legitimate coordinate system. With this notation we can write the new coordinates in normal form as

$$\begin{aligned} \dot{z}_1 &= z_2 \end{aligned} \tag{14}$$

$$\dot{z}_2 &= z_3 \\ \dots \\ \dot{z}_{r-1} &= z_r \\ \dot{z}_r &= b(\xi, \eta) + a(\xi, \eta) u \\ \dot{\eta} &= q(\xi, \eta) + p(\xi, \eta) u \\ \dot{\gamma} &= z_1 \end{aligned}$$

The equation for  $\eta$  represents the n-r equations for which no special form exists. The general equation, however, if the following condition holds

$L_g \Phi_i(x) = 0$

is reduced to

. ήq(ξ,η)

and the input u does not appear.

```

In general, the new nonlinear system is described by

\dot{\xi}_{=\mathcal{A}\xi_{+}B_{V}}

```

(15a,b,c)

$\dot{\eta} = q(\xi,\eta) + p(\xi,\eta)u$

$y=C\xi$

40

with the matrices A, B, and C in normal form, and

$v=b(\xi,\eta)+a(\xi,\eta)u$

45 If r=n, input-output linearization leads to input-state linearization. If r<n, then there are n-r equations describing the internal dynamics of the system. The zero dynamics, obtained by setting ξ=0 in equation (15b) and solving for η, are very important in determining the possible stabilization of the 50 system (10). If these zero dynamics are non-minimum phase then the input-output linearization in (11) cannot be used. If, however, the zero dynamics are minimum phase it means that pole placement can be done on the linear part of (15a) using (11) and the system will be stable.

55 In the sequel, the bold letter used to indicate vector fields will only be used when the context is ambiguous as to what is meant. Otherwise, non-bold letters will be used. For a boost converter the driving voltage u(t), the current x<sub>1</sub> through the inductor, and the voltage x<sub>2</sub> across the capacitor are restricted to be positive, nonnegative, and positive, respectively. Only the continuous conduction mode (CCM) is considered. The duty ratio d is taken to be the control input and is constrained by 0≤d≤1. The Ćuk-Middlebrook averaged nonlinear state equations are used to find a feedback transformation that 5 maps these state equations to a controllable linear system. This transformation is one-to-one with the restrictions on u(t), x<sub>1</sub> and x<sub>2</sub> just mentioned and with additional restrictions

involving ù. These additional restrictions are not needed if u(t) is a constant, as in DC-DC conversion. It is interesting to note that restrictions on u are unnecessary for the boost converter even if u(t) changes with time. The nonlinear system is said to be feedback linearizable or feedback linearized. Through the feedback transformation, the same second order linear system for every operating point can be seen.

The new switching model of the present invention will now be described in more detail. The physical component parasitics  $R_{a}$ , the DC series resistance of the filter inductor L, and  $R_{a}$ , the equivalent series resistance of the filter capacitor C, now need to be included since R<sub>c</sub> especially plays a central role in the analysis to follow.

The system in accordance with the present invention is of the form

$\dot{x} = f(x) + g(x)d$

v=b(x)(16)

With this in mind, the state equations are derived to include parasitics R<sub>s</sub> and R<sub>c</sub>.

There are four basic cells for fixed frequency PWM converters. They are the buck, boost, buck-boost, and boost-buck (Cuk) topologies. Many derivations extend the basic cells in 25 applications where isolation can be added between input and output via transformers, however, the operation can be understood through the basic cell. Each cell contains two switches. Proper operation of the switches results in a two-switch-state topology. In this regime, there is a controlling switch and a 30 passive switch that are either on or off resulting in two "on" states. In contrast, a three state converter would consist of three switches, two controlling switches and one passive switch, resulting in three "on" states.

The control philosophy used to control the switching 35 Equation (20) is the ideal duty ratio equation for the boost sequence is pulse-width-modulation (PWM). A control voltage  $v_c$  is compared with a ramp signal ("sawtooth"),  $v_m$ , and the output pulse width is the result of  $v_c > v_m$ . This is shown in FIG. 4A. A new cycle is initiated on the negative slope of the ramp. The pulse ends when  $v_c < v_m$  which causes modulation 40 to occur on the trailing edge. This gives it the name "trailingedge modulation."

The difference between leading-edge modulation (LEM) and the conventionally used trailing-edge modulation (TEM) is that in TEM (FIG. 4A) the pulse-width is determined by the 45 instantaneous control voltage v<sub>c</sub> prior to switch turn-off, whereas in LEM (FIG. 4B) the pulse-width is determined by v<sub>c</sub> prior to switch turn-on. The reason that sampling is "just prior" to switch commutation is that the intersection of  $v_c$  and  $v_m$  determines the new state of the switch. Notice that in FIG. 50 4B the sawtooth ramp  $v_m$  has a negative slope.

Now referring to FIG. 5, a circuit diagram 500 of a boost converter and a modulator/controller 502 in accordance with the present invention is shown. The specifics of the boost converter are well known. In this case, S2 is implemented 55 with a diode and S1 is implemented with an N-channel MOS-FET. FIGS. 6A and 6B are linear circuit diagrams 600 and 650 of the boost converter in FIG. 5 during time DTs and D'Ts, respectively. The converter 500 operates as follows:  $u_0$ provides power to the circuit during S1 conduction time (FIG. 60 6A) storing energy in inductor L. During this time S2 is biased off. When S1 turns off, the energy in L causes the voltage across L to reverse polarity. Since one end is connected to the input source, uo, it remains clamped while the other end forward biases diode S2 and clamps to the output. Current 65 continues to flow through L during this time (FIG. 6B). When S1 turns back on, the cycle repeats. FIG. 7 illustrates the

typical waveforms for the boost converter for the two switched intervals DTs and D'Ts.

The DC transfer function needs to be determined in order to know how the output, y, across the load R is related to the input  $u_0$  at zero frequency. In steady state, the volt-second integral across L is equal to zero. Thus,

$$\int_{0}^{T_{s}} v_{L} dt = 0$$

(17)

where Ts is the switching period.

Therefore, the volt-seconds during the on-time must equal the volt-seconds during the off-time. Using this volt-second balance constraint one can derive an equation for volt-seconds during the on-time of S1 (DTs) and another equation for volt-seconds during the off-time of S1 (D'Ts).

The parasitics are eliminated by setting  $R_s=0$  and  $R_c=0$ . During time DTs:

$$T_s v_L = D T_s u_0 \tag{18}$$

<sup>20</sup> During time D'Ts:

D

$$D'T_s v_L = D'T_s x_2 - D'T_s u_0 \tag{19}$$

Since by equation (17)

$$DT_s v_L = D'T_s v_L$$

the RHS of equation (18) is set equal to the RHS of equation (19) resulting in

$$\frac{x_2}{u_0} = \frac{1}{D'} \tag{20}$$

cell. If  $R_s$  and  $R_c$  are both non-zero then

$$\frac{y}{u_0 - x_1 R_s} = \frac{1}{D'} \tag{21}$$

The output y is

$$y = D' \frac{RR_c}{R + R_c} x_1 + \frac{R}{R + R_c} x_2$$

(22)

Now the state space averaged equations are derived during dTs:

$$\dot{x}_1 = \frac{1}{L}u - \frac{R_s}{L}x_1$$

$$\dot{x}_2 = -\frac{1}{C(R+R_c)}x_2$$

And during (1-d)Ts:

$$\begin{split} \dot{x}_1 &= \frac{1}{L} \Big[ - \Big( R_s + \frac{RR_c}{R + R_c} \Big) x_1 - \frac{R}{R + R_c} x_2 + u_0 \Big] \\ \dot{x}_2 &= \frac{R}{C(R + R_c)} x_1 - \frac{1}{C(R + R_c)} x_2 \end{split}$$

20

25

35

50

Combining, the averaged equations are:

$$\begin{split} \dot{x}_1 &= \frac{1}{L} u_0 - \frac{R_s}{L} x_1 - \frac{RR_c}{L(R+R_c)} x_1(1-d) - \frac{R}{L(R+R_c)} x_2(1-d) \end{split} \tag{23a,b,c} \\ \dot{x}_2 &= \frac{R}{C(R+R_c)} x_1(1-d) - \frac{1}{C(R+R_c)} x_2 \\ y &= \frac{R}{(R+R_c)} x_2 + \frac{RR_c}{(R+R_c)} x_1(1-d) \end{split}$$

where  $R_s$  is the dc resistance of L and  $R_c$  is the equivalent series resistance of C.

In standard form:

$$\begin{aligned} x_{1} &= \frac{u_{0}}{L} - \frac{R}{L(R+R_{c})} x_{2} - \\ & \left(\frac{R_{s}}{L} + \frac{RR_{c}}{L(R+R_{c})}\right) x_{1} + \left(\frac{RR_{c}}{L(R+R_{c})} x_{1} + \frac{R}{L(R+R_{c})} x_{2}\right) d \\ & \dot{x}_{2} &= -\frac{1}{C(R+R_{c})} x_{2} + \frac{R}{C(R+R_{c})} x_{1} - \frac{R}{C(R+R_{c})} x_{1} d \\ & y &= \frac{RR_{c}}{(R+R_{c})} x_{1} + \frac{R}{(R+R_{c})} x_{2} \end{aligned}$$

(24a,b,c)

Here it is assumed that leading-edge modulation is used so that sampling of the output y only takes place during the interval  $(1-d)T_s$ . Therefore, the weighting factor (1-d) in equation (23c) for y has been removed because when the <sup>30</sup> sample is taken the data represents both terms as shown in equation (24c). In the present analysis the effects of sampling (complex positive zero pair at one-half the sampling frequency) have been ignored.

The input-output linearization for the boost converter will now be discussed. The output, y, only needs to be differentiated once before the control d appears.

$$y = \frac{R}{R + R_c} (x_2 + R_c x_1) \tag{25}^{40}$$

$$\dot{y} = \frac{R}{R + R_c} (\dot{x}_2 + R_c \dot{x}_1)$$

(26a)

$$\dot{y} = \left(\frac{R}{R+R_c}\right) \left(\frac{1}{C(R+R_c)}(-x_2 + Rx_1 - Rx_1d) + \frac{R_c}{L}\left(u_0 - \frac{R}{R+R_c}x_2 - \frac{(26b)}{(R_s + \frac{RR_c}{R+R_c})x_1 + \left(\frac{RR_c}{R+R_c}x_1 + \frac{R}{R+R_c}x_2\right)d}\right) \right)$$

Substituting for  $x_2$  from (25), setting  $\dot{y}$  equal to  $k(y_0-y)$ , k>0, and solving for d we get,

$$d = \frac{(RR_cC + L)y - (L - R_sR_cC)Rx_1 - (27)}{R(R_cCu_0 + (R + R_c)LCk(y_0 - y))}$$

$$R\left(\frac{R_cCy - \frac{LR}{R + R_c}x_1\right)$$

where

$$R\left(R_c Cy - \frac{LR}{R + R_c} x_1\right) > 0.$$

<sup>60</sup>

Here  $y_0$  is the desired output corresponding to  $x_{10}$  and  $x_{20}$  through equation (25). The notation has changed and  $k=c_0$  in 65 equation (11), and the control input is now d instead of u. Here  $(x_{10}, x_{20})$  is an equilibrium point of the boost converter. The

proportional term  $k(y_0-y)$  can be replaced by any suitable controller, such as a proportional (P), integral (I) or derivative (D) (or any combination of these three) by replacing  $k(y_0-y)$ in the equation defining the duty cycle d with

$$\left(k_p + \frac{k_i}{s} + k_d s\right)(y_0 - y)$$

<sup>10</sup> where k<sub>p</sub>, k<sub>i</sub>, and k<sub>d</sub> are the gains of the proportional, integral, and derivative terms of the controller. If k<sub>i</sub> and k<sub>d</sub> are both zero, then the controller reduces to a proportional controller. If only k<sub>d</sub> is zero, then the controller reduces to a proportional-integral (PI) controller.

<sup>15</sup> The control is part of the transformation as shown in equa-

The control is part of the transformation as shown in equation (27) where it is seen that  $k(y-y_0)$  is in the numerator, and k is the proportional gain. The proportional term  $k(y_0-y)$  can be replaced by any suitable controller, such as a proportional (P), integral (I) or derivative (D) (or any combination of these three) by replacing  $k(y_0-y)$  in the equation defining the duty cycle d with

$$\left(k_p + \frac{k_i}{s} + k_d s\right)(y_0 - y)$$

where  $k_{\rho}$ ,  $k_i$ , and  $k_d$  are the gains of the proportional, integral, and derivative terms of the controller. If  $k_i$  and  $k_d$  are both zero, then the controller reduces to a proportional controller. If only  $k_d$  is zero, then the controller reduces to a proportionalintegral (PI) controller. The control implementation is shown in FIG. **2**.

Local linearization of the boost converter will now be discussed to obtain a transfer function. A Taylor Series linearization is used on the nonlinear system (24abc) to linearize about an operating point,  $x_{10}$ ,  $x_{20}$ , D and obtain the transfer function. We let

$$\hat{x}_1 = x_1 - x_{10}, \ \hat{x}_2 = x_2 - x_{20}, \ \hat{y} = y - y_0, \ \hat{d} = d - D.$$

which gives

$$\begin{split} \dot{\hat{x}}_1 &= \\ & \frac{1}{L} \bigg[ -\frac{(1-D)R}{R+R_c} \hat{x}_2 - \frac{(1-D)RR_c}{R+R_c} \hat{x}_1 - R_s \hat{x}_1 + \bigg( \frac{RR_c}{R+R_c} x_{10} + \frac{R}{R+R_c} x_{20} \bigg) \hat{d} \bigg] \\ & \dot{\hat{x}}_2 = \frac{1}{C(R+R_c)} \Big[ -\hat{x}_2 + (1-D)R\hat{x}_1 - Rx_{10}\hat{d} \bigg] \end{split}$$

In matrix form

$$\begin{bmatrix} \dot{x}_1 \\ \dot{x}_2 \end{bmatrix} = \begin{bmatrix} -\left(\frac{RR_c(1-D)}{L(R+R_c)} + \frac{R_s}{L}\right) & -\frac{(1-D)R}{L(R+R_c)} \\ \frac{R(1-D)}{C(R+R_c)} & -\frac{1}{C(R+R_c)} \end{bmatrix} \begin{bmatrix} \dot{x}_1 \\ \dot{x}_2 \end{bmatrix} + \begin{bmatrix} \frac{RR_cx_{10} + Rx_{20}}{L(R+R_c)} \\ -\frac{Rx_{10}}{C(R+R_c)} \end{bmatrix} \hat{d}.$$

Making the following substitutions, which can be derived by letting  $\dot{x}_1=0$ ,  $\dot{x}_2=0$ ,  $x_1=x_{10}$ ,  $x_2=x_{20}$ ,  $R_c=0$ , and  $R_s=0$  in (24ab):

$$x_{10} = \frac{u_0}{(1-D)^2 R}$$

and

$$x_{20} = \frac{u_0}{(1-D)}$$

15

40

50

55

60

$$\begin{bmatrix} \dot{x}_{1} \\ \dot{x}_{2} \end{bmatrix} = \begin{bmatrix} -\left(\frac{RR_{c}(1-D)}{L(R+R_{c})}\right) & -\frac{(1-D)R}{L(R+R_{c})} \\ \frac{R(1-D)}{C(R+R_{c})} & -\frac{1}{C(R+R_{c})} \end{bmatrix} \begin{bmatrix} \dot{x}_{1} \\ \dot{x}_{2} \end{bmatrix} + \begin{bmatrix} \frac{u_{0}}{L(R+R_{c})(1-D)} \left(\frac{R_{c}}{(1-D)} + R\right) \\ -\frac{u_{0}}{C(R+R_{c})(1-D)^{2}} \end{bmatrix} \hat{d}.$$

$$\hat{y} = \begin{bmatrix} \frac{RR_{c}}{R+R_{c}} & \frac{R}{R+R_{c}} \end{bmatrix} \hat{x}$$

$$(29)$$

Now a linear system is provided

$\dot{\hat{x}}A\hat{x}+B\hat{d}$

results in

$$\hat{y} = C\hat{x}c$$

(30) 20

where A is an  $n \times n$  matrix, B is an n-column vector, and C is an n-row vector.

To find the control-to-output transfer function, solve the matrix equation

$$G(s) = C[sI - A]^{-1}B.$$

and obtain

$$G(s) = \frac{1}{\Delta(s)} \left[ \frac{RR_c}{R + R_c} \frac{R}{R + R_c} \right] \left[ \begin{array}{c} s + \frac{1}{C(R + R_c)} & -\frac{(1 - D)R}{L(R + R_c)} \\ \frac{R(1 - D)}{C(R + R_c)} & s + \left(\frac{RR_c(1 - D)}{L(R + R_c)}\right) \\ \end{array} \right] \\ \left[ \frac{u_0}{L(R + R_c)(1 - D)} \left(\frac{R_c}{(1 - D)} + R\right) \\ -\frac{u_0}{C(R + R_c)(1 - D)^2} \\ \end{array} \right]^{35}$$

If we let powers greater than one of  $R_c$  equal zero, further evaluation results in

(31) 45 G(s) = $\frac{1}{\Delta(s)} \left[ \frac{u_0}{LCR(1-D)^2} \left[ (RR_c C(1-D) - L)s + 2R_c(1-D) + R(1-D)^2 \right] \right]$

where  $\Delta(s)$  is the determinant of is [sI-A] which is

$$\Delta(s) = s^{2} + \frac{L + R_{c}C(1-D)}{LC(R+R_{c})}s + \frac{R(1-D)(R_{c}+R(1-D))}{LC(R+R_{c})^{2}}$$

(32)

Taking the term in (31) associated with s, the zero of the linear system needs to be in the left-half plane, so this term needs to remain positive. Solving for R<sub>c</sub>C we have

$$R_c C > \frac{L}{R(1-D)} \tag{33}$$

Note that the inequality (33) can also be derived from the 65 denominator of (27) by setting  $(R+R_c)=R$ , i.e.,  $R \gg R_c$  and with the following substitution for  $x_1$ ,

$$x_1 = \frac{y}{R(1-D)}$$

At this point, the transfer function has been shown to be the linear approximation of the nonlinear system having a lefthalf plane zero under constraint (33). The zeros of the transfer function of the linear approximation of the nonlinear system at x=0 coincide with the eigenvalues of the linear approxima-10tion of the zero dynamics of the nonlinear system at  $\eta=0$ . Therefore, the original nonlinear system (24) has asymptotically stable zero dynamics. Furthermore, the following proposition is associated with the system (14).

20

Proposition. Suppose the equilibrium n=0 of the zero dynamics of the system is locally asymptotically stable and all the roots of the polynomial p(s) have negative real part. Then the feedback law

$$u = \frac{1}{a(\xi, \eta)} (-b(\xi, \eta) - c_o z_1 - c_1 z_2 - \dots - c_{r-1} z_r)$$

(34)

locally asymptotically stabilizes the equilibrium  $(\xi, \eta)=(0, \xi)$ 25 0).

The polynomial

$$p(s) = s^{r} + c_{r-1}s^{r-1} + \dots + c_{1}s + c_{0}$$

(35)

is the characteristic polynomial of the matrix A associated  $_{30}$  with the closed loop system (see equations (14) and (34) and recall that  $z=\xi$ )

$\dot{\xi} = A \xi + B v$

$$\dot{\eta}=q(\xi,\eta)$$

(36)

where  $\dot{\xi}=A\xi+Bv$  are the linear part of the system and  $\dot{\eta}=q(0, t)$  $\eta$ ) are the zero dynamics. The matrix A is given by

|     | 0      | 1        | 0        |   | 0 ]        |  |

|-----|--------|----------|----------|---|------------|--|

|     | 0      | 0        | 1        |   | 0          |  |

| A = | :      | :        | ÷        | ÷ | : .        |  |

|     | 0      | 0        | 0        |   | 1          |  |

|     | $-c_o$ | $-c_{1}$ | $-c_{2}$ |   | $-c_{r-1}$ |  |

and the vector B is given by

$$B = [0, \ldots, 0, 1]^T$$

The feedback law in equation (34) can be expressed in the original coordinates as

$$u = \frac{1}{L_g L_f^{-1} b(x)} (-L_f^r b(x) - c_o b(x) - c_1 L_f b(x) - \dots - c_{r-1} L_f^{r-1} b(x))$$

(37)

As shown in equation (26), the input d appears after only one differentiation so the relative degree is one. This means that the present invention is a single order linear system containing only one root, thus the present invention can be expressed in the new coordinates as

$\dot{\xi} = -k\xi + v$

$\dot{\eta} = q(\xi, \eta)$

The polynomial p(s) is simply p(s)=s+k, with k>0, so that the denominator is now a real pole in the open left half plane.

In accordance with the Proposition, the root of the polynomial p(s) has a negative real part, and as shown above, the present invention has asymptotically stable zero dynamics. 5 Therefore, it can be concluded that, given a control law of the form (37), the original nonlinear system (24) is locally asymptotically stable.

The following theorem has been proven.

Theorem 1: For a boost converter with asymptotically 10 where Ts is the switching period. stable zero dynamics (using leading-edge modulation), with constraint

$$R_c C > \frac{L}{R(1-D)} \tag{38}$$

and control law

$$d = \frac{1}{L_g L_f^{r-1} y} (-L_f^r y - k(y - y_o));$$

(39)

the nonlinear system

$\dot{\xi} = -k\xi + v$

$\dot{\eta}q(\xi,\eta),$

*y*=ξ

with v=0, is asymptotically stable at each equilibrium point (the characteristic polynomial p(s) has a root with negative real part) which means that the original nonlinear system

$\dot{x}=f(x)+g(x)d$

y=b(x)

is locally asymptotically stable at each equilibrium point  $(x_{10},$  $\mathbf{x}_{20}$ ) in the set

$S = \{(x_1, x_2), x \in \Re^n : x_1 \ge 0, x_2 > 0\}$

with  $0 \le d \le < 1$ .

Recall that  $(x_{10}, x_{20})$  corresponds to  $y_0$  through equation (25). Theorem 1 indicates local asymptotic stability. In practice, the reference input  $y_0$  is ramped up in a so-called "soft- 45 start" mode of operation. This theorem also guarantees local asymptotic stability at each operating point passed through by the system on its way up to the desired operating point.

Now referring to FIG. 8, a circuit diagram 800 of a buckboost converter and a modulator/controller 802 in accordance 50 with the present invention are shown. The details of buckboost converters are well known. In this case, S2 is implemented with a diode and S1 is implemented with an N-channel MOSFET. FIGS. 9A and 9B are linear circuit diagrams 900 and 950 of a buck-boost converter during time DTs and 55 D'Ts. The operation of the converter is as follows:  $u_0$  provides power to the circuit during S1 conduction time (FIG. 9A) storing energy in inductor L. During this time S2 is biased off. When S1 turns off, the energy in L causes the voltage across L to reverse polarity. Since one end is connected to circuit 60 return, it remains clamped while the other end forward biases diode S2 and clamps to the output. Current continues to flow through L during this time (FIG. 9B). When S1 turns back on, the cycle repeats. It should be noted that the output voltage is inverted, i.e., negative. FIG. 10 is a graph of typical wave- 65 forms for the buck-boost converter for the two switched intervals DTs and D'Ts. A typical embodiment of the buck-boost

converter where the output voltage is positive is the "flyback" converter where a transformer with phase reversal is used instead of an inductor.

It is again desirable to find the DC transfer function to know how the output, y, across the load R is related to the input u<sub>0</sub> at zero frequency. In steady state, the volt-second integral across L is again equal to zero. Thus,

Therefore, the volt-seconds during the on-time must equal the volt-seconds during the off-time. Using this volt-second balance constraint one can derive an equation for volt-seconds during the on-time of S1 (DTs) and another equation for <sup>15</sup> volt-seconds during the off-time of S1 (D'Ts).

The parasitics are eliminated by setting  $R_s=0$  and  $R_c=0$ . During time DTs:

$$DT_s v_L = DT_s u_0 \tag{43}$$

<sup>20</sup> During time D'Ts:

$\int_0^{T_s} v_1, dt=0$

$$D'T_s v_L = D'T_s x_2 \tag{44}$$

Since by equation (42)

$$DT_s v_L = D'T_s v_L$$

The RHS of equation (43) is set equal to the RHS of equation (44) to provide

$$\frac{x_2}{u_0} = \frac{D}{D'}$$

$$y = -x_2$$

(45)

35 Equation (45) is the ideal duty ratio equation for the buckboost cell. If  $R_s$  and  $R_c$  are both non-zero then

$$\frac{y}{u_0} - \frac{x_1 R_s}{D' u_0} = -\frac{D}{D'} \tag{46}$$

The output y is

$$y = -D' \frac{RR_c}{R + R_c} x_1 - \frac{R}{R + R_c} x_2$$

(47)

Once again it is seen in equation (46) that parasitic  $R_s$  should be minimized. For example if  $R_s=0$  and  $R_c=0$ , then equation (46) reduces to the ideal equation (45).

Now the state space averaged equations are derived during dTs:

$$\dot{x}_1 = \frac{1}{L}u - \frac{R_s}{L}x_1$$

$$\dot{x}_2 = -\frac{1}{C(R+R_c)}x_2$$

And during (1–d)Ts:

$$\dot{x}_1 = -\frac{R_s}{L}x_1 - \frac{RR_c}{L(R+R_c)}x_1 - \frac{R}{L(R+R_c)}x_2$$

25

(40) 30

(41)

40

15

40

-continued

$$z_2 = \frac{R}{C(R+R_c)} x_1 - \frac{1}{C(R+R_c)} x_2$$

Combining, the averaged equations are:

$$\begin{split} \dot{x}_1 &= \frac{1}{L} u_0 d - \frac{R_s}{L} x_1 - \frac{RR_c}{L(R+R_c)} x_1 (1-d) - \frac{Rx_2}{L(R+R_c)} (1-d) \end{split} \tag{48a} \\ \dot{x}_2 &= \frac{R}{C(R+R_c)} x_1 (1-d) - \frac{1}{C(R+R_c)} x_2 \\ y &= -\frac{RR_c}{(R+R_c)} x_1 (1-d) - \frac{R}{(R+R_c)} x_2 \end{split}$$

In standard form:

j

$$\dot{x}_{1} = -\frac{R}{L(R+R_{c})}x_{2} - \left(\frac{R_{s}}{L} + \frac{RR_{c}}{L(R+R_{c})}\right)x_{1} +$$

(50a, b, c) 20

$$\left(\frac{RR_{c}}{L(R+R_{c})}x_{1} + \frac{R}{L(R+R_{c})}x_{2} + \frac{u_{0}}{L}\right)d$$

$$\dot{x}_{2} = -\frac{1}{C(R+R_{c})}x_{2} + \frac{R}{C(R+R_{c})}x_{1} - \frac{R}{C(R+R_{c})}x_{1}d$$

25

$$y = -\frac{RR_{c}}{(R+R_{c})}x_{1} - \frac{R}{(R+R_{c})}x_{2}$$

Here it is assumed that leading-edge modulation is used so that sampling of the output y only takes place during the interval  $(1-d)T_s$ . Therefore, the weighting factor (1-d) in equation (49c) for y has been removed in equation (50c) because when the sample is taken the data represents both terms. In the present analysis the effects of sampling (com- 35 plex positive zero pair at one-half the sampling frequency) have been ignored.

The output, y, only needs to be differentiated once before the control d appears. Thus,

$$y = \frac{R}{R + Rc} (-R_c x_1 - x_2)$$

(51)

$$\dot{y} = \frac{R}{R+Rc}(-R_c \dot{x}_1 - \dot{x}_2)$$

(52a) 45

$$\dot{y} = \frac{R}{R+Rc} \left( -R_c \left( -\frac{R}{L(R+R_c)} x_2 - \left(\frac{R_s}{L} + \frac{RR_c}{L(R+R_c)}\right) x_1 + \left(\frac{RR_c}{L(R+R_c)} x_1 + \frac{R}{L(R+R_c)} x_2 + \frac{u_0}{L}\right) d \right) - 50$$

(52b)

$$\left(-\frac{1}{C(R+R_c)}x_2 + \frac{R}{C(R+R_c)}x_1 - \frac{R}{C(R+R_c)}x_1d\right)\right)$$

Substituting for  $x_2$  from (51), setting  $\dot{y}$  equal to  $k(y_0-y)$ , k>0, and solving for d provides,

$$d = \frac{(RR_cC + L)y + (L - R_cR_sC)Rx_1 + (53)}{R(R_cCy + \frac{LR}{R + R_c}x_1 - R_cCu_0)}$$

60

where

$$R\left(R_c Cy + \frac{LR}{R + R_c}x_1 - R_c Cu_0\right) > 0.$$

Here  $y_0$  is the desired output corresponding to  $x_{10}$  and  $x_{20}$  through equation (51). The notation has changed and  $k=c_0$  in equation (11), and the control input is now d instead of u. Here  $(x_{10}, x_{20})$  is an equilibrium point of our buck-boost converter. Implementation of the control is the same as shown in FIG. 2.

The same definitions are used, so the local linearization will be discussed.

To obtain the transfer function, a Taylor Series linearization is again used on the nonlinear system (50) to linearize 10 about an operating point,  $x_{10}$ ,  $x_{20}$ , D to provide

$$\hat{x}_1 = x_1 - x_{10}, \ \hat{x}_2 = x_2 - x_{20}, \ \hat{y} = y - y_0, \ \hat{d} = d - D.$$

This gives

$$\begin{split} \dot{\hat{x}}_1 &= -\Big(\frac{R_s}{L} + \frac{RR_c}{L(R+R_c)}(1-D)\Big)\hat{x}_1 - \\ &\frac{R}{L(R+R_c)}(1-D)\hat{x}_2 + \Big(\frac{RR_c}{L(R+R_c)}x_{10} + \frac{R}{L(R+R_c)}x_{20} + \frac{u_0}{L}\Big)\hat{\alpha}_1 \\ \dot{\hat{x}}_2 &= \frac{R}{C(R+R_c)}(1-D)\hat{x}_1 - \frac{1}{C(R+R_c)}\hat{x}_2 - \frac{R}{C(R+R_c)}x_{10}\hat{d} \end{split}$$

In matrix form

$$\begin{bmatrix} \dot{x}_1 \\ \dot{x}_2 \end{bmatrix} = \begin{bmatrix} -\left(\frac{R_s}{L} + \frac{RR_c(1-D)}{L(R+R_c)}\right) & -\frac{R(1-D)}{L(R+R_c)} \\ \frac{R(1-D)}{C(R+R_c)} & -\frac{1}{C(R+R_c)} \end{bmatrix} \begin{bmatrix} \hat{x}_1 \\ \hat{x}_2 \end{bmatrix} + \\ \begin{bmatrix} \frac{RR_cx_{10}}{L(R+R_c)} + \frac{Rx_{20}}{L(R+R_c)} + \frac{u_0}{L} \\ -\frac{Rx_{10}}{C(R+R_c)} \end{bmatrix} \hat{d}.$$

Making the following substitutions, which can be derived by letting  $\dot{x}_1=0$ ,  $\dot{x}_2=0$ ,  $x_1=x_{10}$ ,  $x_2=x_{20}$ ,  $R_c=0$ , and  $R_s=0$  in (50ab):

$$\begin{aligned} x_{10} &= \frac{Du_0}{(1-D)^2 R} \end{aligned} \tag{54} \\ \text{and} \\ x_{20} &= \frac{Du_0}{(1-D)} \\ \text{to get} \\ \begin{bmatrix} \dot{x}_1 \\ \dot{x}_2 \end{bmatrix} &= \begin{bmatrix} -\left(\frac{R_s}{L} + \frac{RR_c(1-D)}{L(R+R_c)}\right) - \frac{R(1-D)}{L(R+R_c)} \\ \frac{R(1-D)}{C(R+R_c)} - \frac{1}{C(R+R_c)} \end{bmatrix} \begin{bmatrix} \dot{x}_1 \\ \dot{x}_2 \end{bmatrix} + \\ \begin{bmatrix} \frac{Du_0}{(1-D)L} \left(\frac{R_c}{(R+R_c)(1-D)} + \frac{R}{(R+R_c)}\right) + \frac{u_0}{L} \\ \frac{u_0D}{C(R+R_c)(1-D)^2} \end{bmatrix} \begin{bmatrix} \dot{d} \\ \dot{d} \\ \dot{y} &= \begin{bmatrix} -\frac{RR_c}{R+R_c} & -\frac{R}{R+R_c} \end{bmatrix} \hat{x} \end{aligned}$$

Now the linear system

$$\dot{\hat{\mathbf{x}}} = A\hat{\mathbf{x}} + B\hat{d}$$

$$\hat{y} = C\hat{x}$$

(56)

is provided where A is an n×n matrix, B is an n-column vector, and C is an n-row vector.

<sup>65</sup> To find the control-to-output transfer function the matrix equation is solved

$G(s){=}C[sI{-}A]^{-1}B.$

10

15

20

25

30

After some algebra, letting powers greater than one of  $\mathrm{R}_c$  equal zero provides

$$G(s) = \frac{1}{\Delta(s)} \left\{ -\frac{u_0}{LCR(1-D)^2} \right.$$

$$\left. ([RR_cC(1-D) - LD]s + (1+D^2)R_c + R(1-D)^2) \right\}$$

(57)

where  $\Delta(s)$  is the determinant of [sI–A] which is

$$\Delta(s) = s^2 + \left(\frac{L + RR_cC(1-D)}{LC(R+R_c)}\right)s + \frac{R(1-D)[R_c + R(1-D)]}{LC(R+R_c)^2}$$

(58)