Copyright

by

Hung-Ming Chen

2003

# The Dissertation Committee for Hung-Ming Chen certifies that this is the approved version of the following dissertation:

# **Algorithms for VLSI Design Planning**

| Committee:                   |

|------------------------------|

| Aloysius K. Mok, Supervisor  |

|                              |

| Martin D.F. Wong, Supervisor |

| Donald S. Fussell            |

|                              |

| Mohamed G. Gouda             |

| Xiaoping Tang                |

|                              |

| Hai Zhou                     |

### Algorithms for VLSI Design Planning

by

Hung-Ming Chen, B.E., M.S.

#### **DISSERTATION**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

#### **DOCTOR OF PHILOSOPHY**

THE UNIVERSITY OF TEXAS AT AUSTIN

August 2003

### **Acknowledgments**

I am greatly indebted to my dissertation advisor Professor Martin D.F. Wong for bringing me to the area of VLSI design automation. His guidance and encouragement have been a tremendous assistance throughout my study. The fruitful discussions with him have inspired me to many stimulating thoughts for challenging problems. The criticism from him has led to a higher quality of my research work as well.

I would like to thank my co-advisor Professor Aloysius K. Mok and other members of my dissertation committee, Professors Mohamed G. Gouda, Donald S. Fussell, Hai Zhou, and Dr. Xiaoping Tang for their interests and constructive comments to my work. Special thanks go to Professor Mohamed G. Gouda, who provided me some useful thoughts both in research and living.

I thank all the members of the CAD group in UTCS, specifically Xia Chen, Yongseok Cheon, Li-Da Huang, Seokjin Lee, I-Chung Liu, Muzhou Shao, Yu Sun, and Gang Xu for helpful communications. Also I would like to thank Gloria Ramirez and Katherine Utz at the department's Graduate Office for their great help in administrative issues. In addition, I would like to thank other people who are outside of UTCS for their professional suggestions for my research work, including Professor Yaowen Chang from National Taiwan University, Dr. I-Min Liu and Dr. Minghorng Lai from Cadence Design Systems, and Hua Xiang from University of

Illinois at Urbana-Champaign.

I thank all my friends who have given me a pleasant time staying in Austin, including Chin-Tser Huang family, Hongming Yeh family, Li-San Wang family, Chloe Chang, Eric Lin family, Kiki Wang family, Joyce Wu, and Heng-Ru Lin.

Finally, I would like to give my wholehearted thanks to my parents for their love and care that I have consistently received throughout my life. Especially I would like to express my love and appreciation to my dearest wife, Yi-Chien Yang, for her understanding, encouragement and comfort in all these years. I couldn't reach such achievement without her love.

#### **Algorithms for VLSI Design Planning**

Publication No.

Hung-Ming Chen, Ph.D. The University of Texas at Austin, 2003

Supervisors: Aloysius K. Mok Martin D.F. Wong

With shrinking feature sizes, much more transistors can be integrated on a single chip. Moore's Law has been followed closely in the past decades, resulting in larger and faster chips every year. In order to design larger and faster chips in deep submicron (DSM) technology, it is necessary to perform early design planning. In this dissertation, we present several algorithms for a number of VLSI design planning problems.

First, we propose a method to integrate interconnect planning with floorplanning. Our approach is based on the Wong-Liu floorplanning algorithm. We perform pin assignment and fast global routing during every iteration of floorplanning. We use a multi-stage simulated annealing approach in which different interconnect planning methods are used in different ranges of temperatures to reduce running time. A temperature adjustment scheme is designed to give smooth transitions between different stages of simulated annealing.

Second, floorplanning problems typically have relatively small number of blocks (e.g., 50-100) but have a large number of nets (e.g. 20K). Since existing

floorplanning algorithms use simulated annealing which needs to examine a large number of floorplans, this has made interconnect-centric floorplanning computationally very expensive. We present approaches that can dramatically improve the run time of problems with large number of nets and at the same time improve solution quality.

Third, we propose a method for simultaneous power supply planning and noise avoidance in floorplan design. Without careful power supply planning in layout design, the design of chips will suffer from mostly signal integrity problems including IR-drop,  $\Delta I$  noise, and IC reliability. Post-route methodologies in solving signal integrity problem have been applied but they will cause a long turn-around time, which adds costly delays to time-to-market. We show that the noise avoidance in power supply planning problem can be formulated as a constrained maximum flow problem.

Fourth, I/O placement has been a concern in modern IC design. Due to flip-chip and multi-chip module technologies, I/O can be placed throughout the whole chip without long wires from the periphery of the chip. However, because of I/O placement constraints and I/O buffer site building cost, the decision of positions for placing I/O buffers has become critical. Our objective is to reduce the number of I/O buffer sites and to decide their positions in an existing standard cell placement. We formulate it as a minimum cost flow problem.

# **Table of Contents**

| Acknow  | vledgments                                                                                | V    |

|---------|-------------------------------------------------------------------------------------------|------|

| Abstrac | et e                                                                                      | vii  |

| List of | Γables                                                                                    | xii  |

| List of | Figures                                                                                   | xiii |

| Chapte  | r 1. Introduction                                                                         | 1    |

| 1.1     | Dissertation Overview                                                                     | 4    |

| Chapte  | r 2. Integrated Floorplanning and Interconnect Planning                                   | 7    |

| 2.1     | Introduction                                                                              | 7    |

| 2.2     | Efficient Interconnect Planning                                                           | 10   |

|         | 2.2.1 Pin Assignment                                                                      | 11   |

|         | 2.2.2 Simple-Geometry Routing                                                             | 11   |

|         | 2.2.3 Incremental Routing Cost Computation                                                | 15   |

| 2.3     | Multi-Stage Simulated Annealing                                                           | 18   |

|         | 2.3.1 Cost Function Transitions                                                           | 19   |

|         | 2.3.2 Temperature Adjustment                                                              | 21   |

| 2.4     | Experimental Results                                                                      | 24   |

| 2.5     | Concluding Remarks                                                                        | 25   |

| Chapte  | r 3. Faster and More Accurate Wiring Evaluation in Interconnect-<br>Centric Floorplanning | 28   |

| 3.1     | Introduction                                                                              | 29   |

| 3.2     | Wiring Evaluation in Interconnect Centric Floorplanning                                   | 31   |

| 3.3     | Faster Wiring Evaluation Based on Net Reduction                                           | 33   |

|         | 3.3.1 Problem Formulation                                                                 | 33   |

|    |      | 3.3.2 Algorithm for Net Reduction                                   | 35 |

|----|------|---------------------------------------------------------------------|----|

|    |      | 3.3.2.1 Bounded-Degree Hypergraph-to-Graph Transformation           | 36 |

|    |      | 3.3.2.2 Net Reduction by Multi-terminal Net Decomposition           | 38 |

|    | 3.4  | More Accurate Wiring Evaluation Based on Lagrangian Relaxation .    | 41 |

|    |      | 3.4.1 Problem Formulation                                           | 41 |

|    |      | 3.4.2 Lagrangian Relaxation                                         | 41 |

|    |      | 3.4.2.1 Simplification of Lagrangian Relaxation Subproblem          | 42 |

|    |      | 3.4.2.2 Solving Lagrangian Relaxation Subproblem                    | 43 |

|    |      | 3.4.2.3 Solving Lagrangian Dual Problem                             | 44 |

|    | 3.5  | Experimental Results                                                | 44 |

|    | 3.6  | Concluding Remarks                                                  | 45 |

| Րհ | apte | 4. Simultaneous Power Supply Planning and Noise Avoidance in        |    |

|    | шрес |                                                                     | 47 |

|    | 4.1  | Introduction                                                        | 48 |

|    | 4.2  | Floorplans with Power Supply Noise Considerations                   | 51 |

|    |      | 4.2.1 IR-Drop Requirement                                           | 55 |

|    |      | 4.2.2 $\Delta I$ Noise Constraint                                   | 55 |

|    |      | 4.2.3 Problem Formulation                                           | 57 |

|    | 4.3  | Power Supply Planning with Noise Avoidance                          | 58 |

|    |      | 4.3.1 Feasible Power Supply Region                                  | 59 |

|    |      | 4.3.2 Constrained Network Formulation                               | 60 |

|    |      | 4.3.3 Priority_Augmenting_Path Algorithm                            | 63 |

|    |      | 4.3.3.1 Complexity Analysis                                         | 64 |

|    |      | 4.3.4 Graph Reduction by Power Zones                                | 65 |

|    | 4.4  | Floorplanning with Power Supply Planning and Noise Avoidance Design | 67 |

|    | 4.5  | Experimental Results                                                | 68 |

|    | 46   | Concluding Remarks                                                  | 70 |

| Chapte                                      | r 5. I/O Buffer Site Placement in Area-Array IC Design | 73  |

|---------------------------------------------|--------------------------------------------------------|-----|

| 5.1                                         | Introduction                                           | 74  |

| 5.2                                         | I/O Buffer Site Placement in Area-Array IC Design      | 76  |

| 5.3                                         | The Algorithm                                          | 81  |

| 5.4                                         | Cell Re-Placement from I/O Buffer Site Planning        | 84  |

| 5.5                                         | Experimental Results                                   | 85  |

| 5.6                                         | Concluding Remarks                                     | 87  |

| Chapter 6. Conclusion and Future Directions |                                                        | 89  |

| Bibliog                                     | raphy                                                  | 94  |

| Vita                                        |                                                        | 104 |

# **List of Tables**

| 2.1 | Experimental results of our approach on MCNC examples, compared with the method in [65]                                                                                                                                                                               | 25 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Performance improvement of our approach on MCNC examples, compared with the method in [65]                                                                                                                                                                            | 25 |

| 3.1 | Speedup comparisons between floorplanner in [2] and our approaches using net reduction and Lagrangian relaxation global router                                                                                                                                        | 45 |

| 4.1 | Comparison of our approach with [65] and [35] on MCNC benchmarks. The wirelength data are described in Section 4.5                                                                                                                                                    | 69 |

| 5.1 | Number of cells, nets, and IO/terminals in some MCNC standard cell placement benchmarks                                                                                                                                                                               | 86 |

| 5.2 | Experimental results of our approach on MCNC benchmarks summarized in Table 5.1, compared with a greedy approach. With slight increase percentage in voltage drop threshold violation, much less number of I/O buffer sites can be obtained in minimizing wirelength. | 87 |

| 5.3 | Performance improvement of our approach on MCNC benchmarks, compared with a greedy approach [61]                                                                                                                                                                      | 88 |

# **List of Figures**

| 2.1  | Floorplanning greatly influences interconnect structure                                                                                                                                      | 8  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Floorplanning and interconnect planning                                                                                                                                                      | 9  |

| 2.3  | Pin assignment illustration                                                                                                                                                                  | 12 |

| 2.4  | L-shaped routing                                                                                                                                                                             | 13 |

| 2.5  | Z-shaped routing                                                                                                                                                                             | 15 |

| 2.6  | v(i,j) is the accumulated cost of shaded bin boundaries                                                                                                                                      | 16 |

| 2.7  | h(i,j) is the accumulated cost of shaded bin boundaries                                                                                                                                      | 17 |

| 2.8  | The routing cost in terms of $h(i, j)$ 's and $v(i, j)$ 's                                                                                                                                   | 17 |

| 2.9  | Normal curve of cost versus number of iterations                                                                                                                                             | 20 |

| 2.10 | Abormal curve (solid line) of cost versus number of iterations: quickly converges to suboptimal solution                                                                                     | 21 |

| 2.11 | Abormal curve (solid line) of cost versus number of iterations: takes a much longer time to converge                                                                                         | 22 |

| 2.12 | Temperature adjustment                                                                                                                                                                       | 23 |

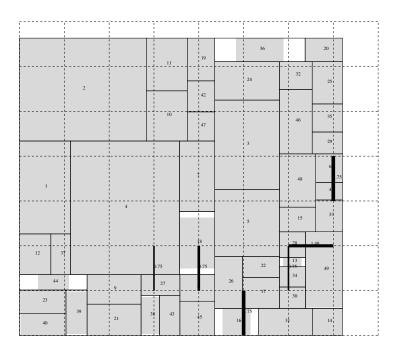

| 2.13 | Result of packing ami49 using interconnect planning approach                                                                                                                                 | 26 |

| 2.14 | Result of packing ami49 using original approach                                                                                                                                              | 26 |

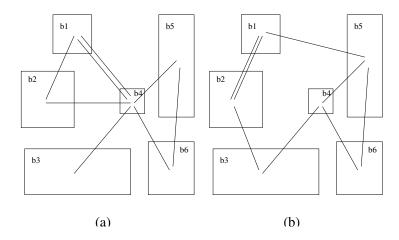

| 3.1  | Net reduction (a) Original netlist. (b) Reduced netlist                                                                                                                                      | 34 |

| 3.2  | A netlist with multi-terminal nets                                                                                                                                                           | 34 |

| 3.3  | Two net decomposition solutions for the example in Figure 3.2. (a) An illegal net decomposition since block $b_4$ exceeds its pin-limit. (b) A feasible net decomposition                    | 35 |

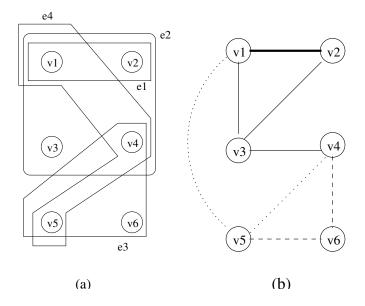

| 3.4  | Hypergraph-to-graph transformation. (a)A hypergraph with four hyperedges: e1, e2, e3, and e4. (b)A graph formed by combining four spanning trees corresponding to the four hyperedges in (a) | 37 |

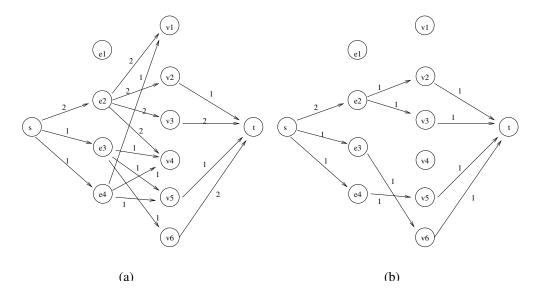

| 3.5  | (a)Flow network built upon the hypergraph model. (b) An integral maximum flow. The number besides each arc is the (a)capacity/(b)flow in the arc                                             | 40 |

| 3.6  | Spanning trees for hyperedges $e_2$ and $e_3$                                                                                                                                                | 40 |

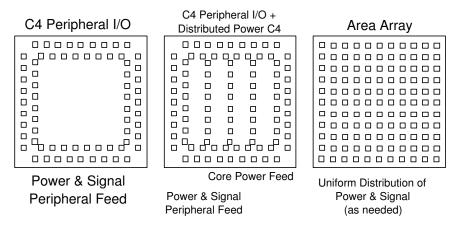

| 4.1 | C4 chip patterns from IBM online document                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 49 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

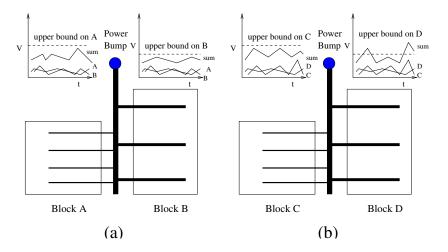

| 4.2 | $\Delta I$ noise constraint illustration when sharing power sources. Two examples of two blocks with a power supply bump. The V-t curves are voltage fluctuations for blocks and the superposition seen in power supply bump. (a) The power supply bump is clean since the voltage fluctuations of two blocks are within the upper bound on $\Delta V$ for both blocks. (b) The power supply bump is noisy since the voltage fluctuations of block C and D exceeds the upper bound on $\Delta V$ for block D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 53 |

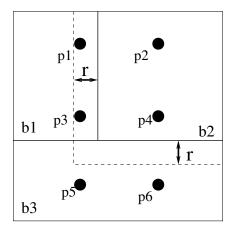

| 4.3 | Floorplanning affects power supply planning and noise avoidance. Block $b_3$ can get four power supply bumps to deliver power on the left floorplan while it can possibly only get three power supply bumps on the right one. This block may also suffer from $\Delta I$ noise constraint violation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 54 |

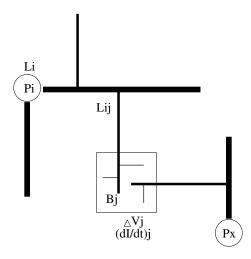

| 4.4 | The relationship between power supply bump and circuit block. The circuit block can obtain power from several power supply bumps, as long as the noise constraint holds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 57 |

| 4.5 | A floorplan and the available power supply bumps. A circuit block can use the power supply bumps within its feasible power supply region (FPSR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 59 |

| 4.6 | The network graph captures the power demand of the circuit blocks and the power that the amount of power supply bumps can provide in Figure 4.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 61 |

| 4.7 | Numeric examples include two max-flow solutions of the network graph from Figure 4.6. Those number are calculated from technology and given IP parameters. (a) The solution with randomly choosing augumenting path. The darker numbers and the edge show that there is a $\Delta I$ noise constraint violation. The number on the edge is the amount of flow on that edge. The number inside the parentheses on the edges between power supply bumps and blocks is the amount of inductive induced voltage drop on that edge. The number inside the parentheses above the block node is the upper bound on $\Delta V$ for the block. For example, $e(p1,b1)$ has $0.15 \text{mV}$ for inductive induced voltage drop, which does not exceed $\Delta V_1 = 0.23 \text{mV}$ . But for $e(p3,b2)$ , it has $0.3 \text{mV}$ , which exceeds $\Delta V_2 = 0.23 \text{mV}$ , indicating a violation. (b) The solution using the algorithm in Section 4.3.3. There is no $\Delta I$ noise constraint violation. | 71 |

| 4.8 | The power zones in a floorplan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 72 |

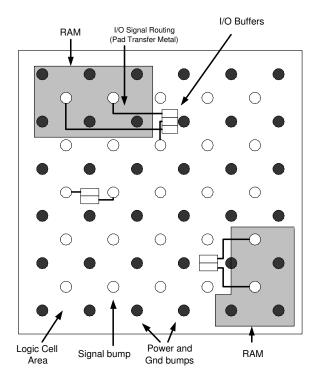

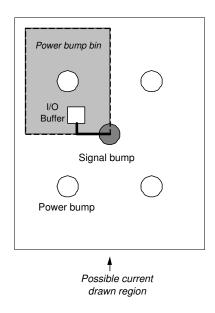

| 5.1 | Area-array footprint ASIC. The Vdd and Gnd bumps are uniformly distributed across the die with signal bumps in fixed interspersed locations. I/O buffers are associated with some specified signals bump and connected by pad transfer metal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 75 |

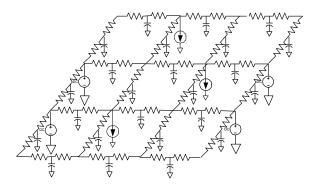

| 5.2 | Power supply network in area-array design for efficient analysis. Power grids are modeled as linear RC networks, power sources are modeled as simple constant voltage sources, and power drains are modeled as independent time-varying currents | 77 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.3 | The relationship between signal bump, power bump, power bump bin, I/O buffer possible positions, and possible current drawn region.                                                                                                              | 80 |

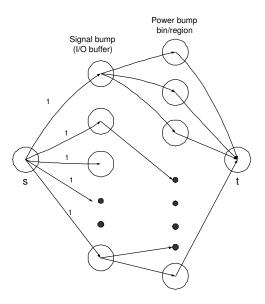

| 5.4 | Network construction for IBSP. Some signal bump (corresponding I/O buffer) vertex $io_i$ only connects to power bump bin vertices which are inside the possible current drawn region for $io_i$                                                  | 81 |

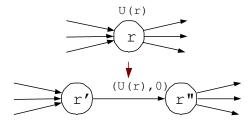

| 5.5 | Vertex splitting for capacitated vertices. The new edge has capacity $U(r)$ and cost 0 [66]                                                                                                                                                      | 82 |

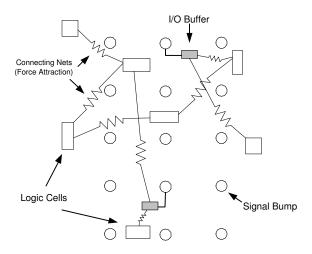

| 5.6 | Force-directed based cell re-placement. With fixed I/O buffer locations, use force attraction to refine existing placement                                                                                                                       | 85 |

## **Chapter 1**

### Introduction

With the rapid development of Very Large Scale Integration (VLSI) fabrication technologies, we have reached an era where the minimum feature sizes of the leading processes is well below .25  $\mu$ m. Such processes are called deep submicron (DSM) processes. With shrinking feature sizes, much more transistors can be integrated on a single chip performing different tasks pre-designed in intellectual properties (IPs). Moore's Law has been followed closely and a huge value in the electronic market has been introduced. However, at the same time, many new problems arise. Those problems will force the change of traditional design flow in electronic design automation (EDA). EDA is one of the key enablers of the semiconductor industry and no chip is designed without EDA [38, 50]. In fact, semiconductors (or technologies) drive EDA technology, especially in physical design. Synthesis, placement and routing are enabled by multiple technology constraints, for example, a logic library, usually in the form of standard cells of the same height and similar size which simplifies placement and routing, decouples technology from logic and enables synthesis. Furthermore, not long ago interconnect was assumed to have negligible delay and digital circuits were modeled with "lumped" components so that secondary effects like crosstalk could not be analyzed. Power consumption issues were limited to the power grid. All that has changed.

With rapid feature size scaling, the circuit performance is increasingly determined by the interconnects instead of devices [19]. Although the use of new interconnect materials (e.g., copper) is helpful in reducing interconnect delay, they do not provide the ultimate solution to the increasing performance mismatch between devices and interconnects. Even with the projected improvements in interconnect performance, the global interconnects remain the performance bottleneck. In conventional VLSI designs, much emphasis has been to design and optimization of logic and devices. The interconnection was done by either layout designers or automatic place-and-route tools as an afterthought. Now we need an interconnect-centric design flow for further interconnect planning throughout the physical design process.

In physical design phase, the typical netlist usually contains large number of nets. Also since for many designs under 0.25  $\mu$ m interconnect delay actually becomes larger than circuit delay [19], wire delays cannot be ignored in logic design any more. Moreover, as the technology node approaches .10  $\mu$ m, inductance becomes noticeable for long wires at high speed such as busses of several mm of length operating at more than 1-2 GHz [24]. This is already a problem for microprocessor design. Current solutions do placement and synthesis (or re-synthesis) together, or start with wire planning, so that wire behavior can be more accurately estimated from early on in the design process. Therefore, a good quality of floorplan with large number of global interconnects is absolutely desired.

Generating satisfactory power supply to meet the requirements of different components in a single chip is becoming difficult in DSM regime due to reduced

power supply voltage, tighter noise margin, and DC voltage drop [7]. Among the approaches of handling/estimating power delivery [44], the planning of mesh power rail followed by hierarchical power/ground (P/G) networks designs is still a major method to design high performance integrated circuits (ICs) [3, 62, 68, 69]. Nevertheless, post-floorplanning power supply synthesis alone cannot guarantee high-quality power supply under limited routing resources. In many cases, when the circuit block locations and sizes are fixed, the constraints such as voltage drop and current density are so tight that there is no feasible power network design capable of keeping power supply noise within a specified margin. In addition, during manufacturing, the number of silicon failures are caused by signal integrity problems, such as IR-drop,  $\Delta$ I noise, and electromigration. These problems are on the rise due to the lack of existing design tools and methodologies to address these issues effectively.

In order to keep up the performance in technology advances, flip-chip and multi-chip module (MCM) technologies now allows high-performance ICs and microprocessors to be built with many more power and I/O connections than in the past, among which area array bonding is considered a rather better one. Besides helping solve the power delivery engineering problems, to effectively alleviate voltage drop problem we need to focus on the placement of highly power hungry buffers, I/O buffers. Since area-array style allows I/O buffers to be placed anywhere on the die, we need to be aware of I/O buffer placement constraints to better the design.

#### 1.1 Dissertation Overview

We investigate and develop several algorithms in VLSI design planning. We first describe several results that we have already obtained [14–17, 35], and then present our conclusion and future directions.

In chapter 2, we propose a method to combine interconnect planning with floorplanning. Our approach is based on the Wong-Liu floorplanning algorithm. We perform pin assignment and fast global routing during every iteration of floorplanning. We use a multi-stage simulated annealing approach in which different interconnect planning methods are used in different ranges of temperatures to reduce running time. A temperature adjustment scheme is designed to give smooth transistions between different stages of simulated annealing. Experimental results show that our approach performs well.

Deeper in the integration of interconnect planning and floorplanning, we found that the previous approach is not enough for large netlist. Since existing floorplanning algorithms use simulated annelaing which needs to examine a large number of floorplans, the increasing number of nets has made interconnect-centric floorplanning computationally very expensive. Moreover, there is almost no systematic way to resolve the congestion problem in such magnitude of number of nets in a given floorplan. In chapter 3, we present a simple yet effective approach to significantly reduce the runtime of interconnect-centric florplanning algorithms. Our idea is to group common nets between two blocks into a single net. We also present a more accurate global router for wiring evaluation based on Lagrangian Relaxation. The new router helps further congestion reduction while doing interconnect plan-

ning in floorplanning. We have incorporated our algorithms into [17] and observed dramatic improvement in runtime. For a 33-block 15K-net problem, we reduced runtime from over 23 hours to less than 50 minutes while getting comparable solution quality.

Meanwhile, without careful power supply planning in layout, the design of chips will suffer from mostly signal integrity problems including IR-drop,  $\Delta I$  noise, and IC reliability. Post-route methodologies in solving signal integrity problem have been applied but they will cause a long turn-around time, which adds costly delays to time-to-market. In chapter 4, we study the problem of simultaneous power supply planning and noise avoidance as early as in the floorplanning stage. We show that the noise avoidance in power supply planning problem can be formulated as a constrained maximum flow problem and present an efficient yet effective heuristic to handle the problem. Experimental results are encouraging.

Futhermore, along with careful power planning in layout design, I/O placement is becoming critical in modern IC design. The design will suffer from mainly hot-spot problem and long interconnect length if there is no planning on placing I/O buffers. There is a certain amount of cost to generate an I/O buffer site, which can been treated as a cluster of I/O buffers. We cannot just place I/O buffers greedily to minimize IR drop and wirelength since this will end up generating more I/O buffer sites and increase the design cost. In chapter 5, we study the problem of I/O buffer site placement in area-array ASIC designs and propose an algorithm to solve the problem with respect to design cost reduction. With slight increase in the percentage of voltage drop threshold violation, we can obtain much smaller design cost in

I/O buffer site placement.

Finally we conclude the dissertation with a summary of our results and a discussion of future directions in chapter 6.

# **Chapter 2**

### **Integrated Floorplanning and Interconnect Planning**

In this chapter, we propose a method to combine interconnect planning with floorplanning. Our approach is based on the Wong-Liu floorplanning algorithm. When the positions, orientations, and shapes of the cells are decided, the pin positions and routing of the interconnects are decided as well. We use a multi-stage simulated annealing approach in which different interconnect planning methods are used in different ranges of temperatures to reduce running time. A temperature adjustment scheme is designed to give smooth transistions between different stages of simulated annealing. Experimental results show that our approach performs well.

#### 2.1 Introduction

With VLSI technology entering the DSM era, devices are scaled down to smaller sizes and placed at an ever increasing proximity. At the same time, with the increase of die dimensions, more functions are integrated into one chip. All these significantly increase the communication between different components, thus increasing the amount of interconnect on a chip. Moreover, the scaling down of fabrication geometry also makes interconnect delay a dominant factor in total circuit delay [20]. These trends make interconnect planning a neccessary step in DSM

design [48].

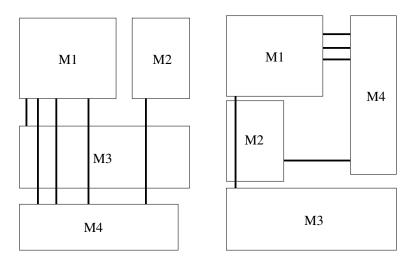

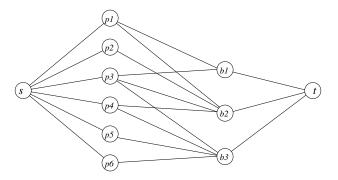

Figure 2.1: Floorplanning greatly influences interconnect structure

Global interconnects have significant influence on system performance in DSM technologies. Floorplanning, the process of placing functional blocks on the chip, can significantly affect the global interconnect structure. (Figure 2.1 shows two floorplans and their corresponding interconnect structures.) Many floorplanning algorithms have been proposed in the past 20 years [29, 43, 45, 49, 52, 60, 65]. All these algorithms focus on placing the circuit blocks using simple interconnect cost (e.g., total wire length) to guide the optimization. Without accurate interconnect planning during the floorplanning process, it is difficult for these algorithms to meet performance constraints due to unexpected "long" global interconnects resulted in the later routing stage.

In this chapter we propose a method to combine interconnect planning with floorplanning. Our approach is based on the Wong-Liu floorplanning algorithm [65].

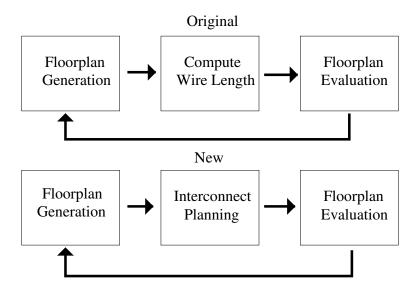

Recall that the Wong-Liu algorithm uses Polish expressions to represent floorplans and searches for an optimal floorplan using simulated annealing by iteratively generating Polish expressions. Every time a Polish expression (i.e., a floorplan) is examined, the shape of the blocks are optimized and the total wire length is used as the interconnect cost. Instead of using the total wire length, we propose to perform careful interconnect planning with respect to the current floorplan being considered and obtain a much more accurate interconnect cost. The comparison of the original approach and our new approach is shown in Figure 2.2.

Figure 2.2: Floorplanning and interconnect planning

The interconnect planning step performs pin assignment and simple-geometry routing based on L-shaped and Z-shaped wires. Taking advantage of the nature of simulated annealing, we use different interconnect planning methods in different ranges of temperatures to reduce the running time. In particular, we use the conventional wire length estimation by half-perimeter of net bounding box when tem-

perature is high, use a more accurate interconnect cost based on L-shaped routing when temperature is in the medium range, and finally use Z-shaped routing when temperature is low. In order to implement our multiple cost function scheme, we found that it was necessary to introduce a temperature adjustment method to cope with the intrinsic discontinuities resulted in the process of switching cost functions.

The rest of the chapter is organized as follows. We introduce the algorithms for interconnect planning in Section 2.2. Section 2.3 discusses the multi-stage simulated annealing approach. Section 2.4 reports the experimental results for MCNC benchmarks and Section 2.5 concludes the chapter.

### 2.2 Efficient Interconnect Planning

To simplify our discussion, we assume there are two layers for the routing of global interconnects – one layer for vertical wires and the other layer for horizontal wires. (However, our approach is applicable to designs with more than two layers.) We allow different layers to have different design rules, i.e., the minimum wire width and the minimum spacing in each layer are different. In order to estimate congestion/routability, we divide the floorplan into a number of bins by a grid the same way that it is typically done in global routing [57]. For each bin boundary, we define its *capacity* as the maximum number of nets that can cross it. Clearly, the capacity of each boundary can be easily computed based on its length (or width) and the design rules (i.e., minimum wire width and minimum wire spacing) for that layer. If the number of nets crossing a bin boundary exceeds the capacity of the bin boundary, we say there is *overflow*. Each global routing solution gives us the num-

ber of nets crossing each bin boundary, thus giving us detailed congestion/overflow information. Our goal is to plan the interconnects to avoid congestion/overflow as much as possible.

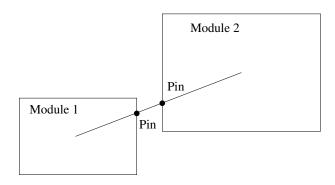

#### 2.2.1 Pin Assignment

The first step of interconnect planning is pin assignment. After module sizes and positions are fixed in a given floorplan, we determine the pin positions on each module. A simple strategy is used for efficiency. For each net, we connect the centers of the modules in this net and get the intersection points on the module boundaries as pin positions, as shown in Figure 2.3. This simple heuristic makes sense since it tries to minimize total wire length. Note that each module boundary is partitioned into a number of boundary segments by the grid. Since each boundary segment can only accommodate a limited number of pins, we should make sure that the number of pins we assign to each boundary segment does not exceed its capacity. If segment overflow occurs, we redistribute some of the pins to neighboring segments. Another guideline for pin assignment is to evenly distribute the pins so that no boundary segments are too crowded.

#### 2.2.2 Simple-Geometry Routing

After pin assignment, pin positions are known. We then perform simple-geometry based global routing to connect the pins. For a net with n pins where n > 2, we first construct a minimum spanning tree connecting the pins using the Manhattan distance metric. The net is then decomposed into a set of two-terminal

Figure 2.3: Pin assignment illustration

nets which correspond to the edges of the minimum spanning tree. After that, we have a set of nets with only two pins. For each of them, we connect the two pins using simple-geometry routing based on L-shaped or Z-shaped wires. Since the algorithms for L-shaped routing and Z-shaped routing are similar, they will be described together. Before we do simple-geometry routing, we map the pin positions of the nets to the corresponding bins. We use a sequential routing approach, that is, we route one net at a time. There are two steps in our simple-geometry routing algorithms. The first step is to use a stochastic approach to obtain the initial global congestion information. The second step is to utilize the information from the first step to route nets one by one.

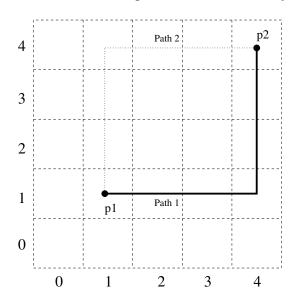

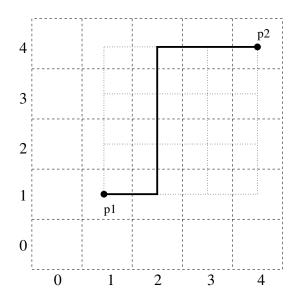

In the first step, we estimate the congestion on each bin boundary by the expected number of nets crossing that boundary. Consider a two-pin net with pins  $p_1 = (x_1, y_1)$  and  $p_2 = (x_2, y_2)$ . If only L-shaped routes are allowed, there are at most two routes to connect the two pins, as shown in Figure 2.4. Assume that each possible route is equally likely, we can add 1/2 to each bin boundary on the two routes as the net's contribution to the expected number of nets crossing that

boundary. For Z-shaped routing, we compute the expected number of nets crossing each bin boundary as follows. Let m denote the total number of Z-shaped routes connecting  $p_1$  and  $p_2$ . As we can see, if  $x_1 = x_2$  or  $y_1 = y_2$ , then m = 1. Otherwise, m can be computed as follows.

$$m = |x_1 - x_2| + |y_1 - y_2|$$

For each bin boundary e, let  $m_e$  be the number of possible Z-shaped routes for the net to cross e. We again assume all routes are equally likely. Clearly, the net's contribution to the epxected number of nets crossing e is  $m_e/m$ . For the example shown in Figure 2.5 for Z-shaped routing, m=6 and  $m_e=1$  where e is the right boundary of bin(2,3). Thus the net's contribution to the expected number of nets crossing e is  $m_e/m=1/6$ . Putting contributions from different nets together, we can get the expected number of crossing nets on each boundary.

Figure 2.4: L-shaped routing

In the second step, we route one net at a time. When routing a net, we first remove its contribution from the expected number of crossing nets at each bin boundary. Then we determine a routing path with minimum crossing cost. The cost of crossing a bin boundary depends on a few factors. We use  $X_e$  to represent the overflow amount on bin boundary e. If there is no overflow on bin boundary e, let  $Y_e$  to be the difference between the current crossing and the capacity of e, and use Z to represent the overlapping length with previously routed wires belonging to the same (multi-pin) net. We determine a routing path which minimizes the following quantity:  $\alpha \sum X_e^2 + \beta \sum 1/Y_e^2 - \gamma Z^2$ . The first part is a *penalty* term, meaning that the global router is penalized because of going through the congested bin boundary. The second term is a *prevention* term, that is, the global router prevents from taking the path that is reaching saturation of the capacity. The third term is a reward that the router follows previous routes for those two-terminal nets within a multi-terminal net. After routing a net, if the route crosses a bin boundary e, its contribution to the expected number of nets crossing e will become 1 to reflect the real route. If the current crossing of the bin boundary exceeds the capacity, mark this net to be riped-up and re-routed.

For all nets that are needed to be riped-up and re-routed, we process them in the order from the most congested net, which is crossing the maximum number of congested bin boundaries, to the less congested ones trying to remove overflow as much as possible. Then we examine the results by getting the total square overflow terms of all bin boundaries. If the current overflow status exceeds the former one, recover the net to its original route.

Figure 2.5: Z-shaped routing

#### 2.2.3 Incremental Routing Cost Computation

A direct method to determine the path with minimum crossing cost connecting two points is as follows. For each possible path, L-shape or Z-shape, we need to sum up the crossing costs for all bin boundaries along the path to get the routing cost of this path. In this way, the time complexity of examining all L-shaped/Z-shaped paths joining two points is  $O(n^2)$  in the worst case, where the grid size is  $n \times n$ , since the total number of bin boundaries crossed by all L-shaped and Z-shaped paths between two points can be  $O(n^2)$ . It then follows that the total time to route N nets is  $O(Nn^2)$ .

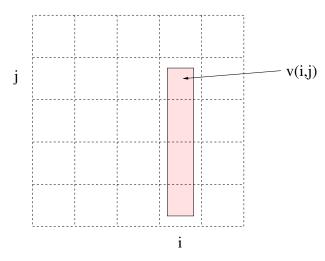

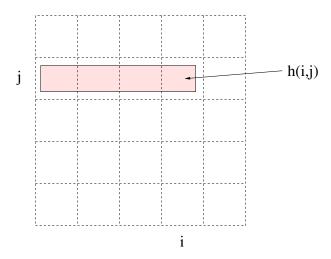

In the following we present the idea of incremental routing cost computation which significantly speed up the cost function computation. For each (i, j), we define v(i, j) as the accumulated crossing cost starting from the top bin boundary

of bin(i,0) to that of bin(i,j-1). Similarly, we define h(i,j) as the accumulated crossing cost starting from the right bin boundary of bin(0,j) to that of bin(i-1,j). (See Figure 2.6, 2.7.) Note that all h(i,j)'s for a row can be computed in O(n) time, and all v(i,j)'s for a column can be computed in O(n) time. Thus all h(i,j)'s and v(i,j)'s can be precomputed in  $O(n^2)$  time.

Figure 2.6: v(i, j) is the accumulated cost of shaded bin boundaries

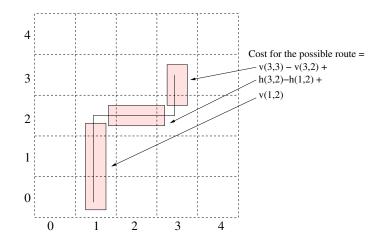

Note that the routing cost for each L-shaped/Z-shaped path can be expressed in terms of h(i,j)'s and v(i,j)'s. (The number of h(i,j) or v(i,j) terms in a L-shaped path is at most 4 and that for a Z-shaped path is at most 6.) For example, the routing cost of the Z-shaped path in Figure 2.8 can be computed by v(3,3)-v(3,2)+h(3,2)-h(1,2)+v(1,2). So if all the h(i,j)'s and v(i,j)'s are precomputed, the time for evaluating all L-shaped/Z-shaped paths between two points is O(n) since there are O(n) such paths and the routing cost of each path can be computed in O(1) time. After we route a path, we need to update the h(i,j)'s and v(i,j)'s on at most three columns/rows, and therefore can be done in O(n) time. If

Figure 2.7: h(i, j) is the accumulated cost of shaded bin boundaries

there are N nets, the total time for updating h(i,j)'s and v(i,j)'s is O(Nn). As a result, the total time for routing N nets is  $O(n^2 + Nn)$ , which compares well with the  $O(Nn^2)$  time direct method. The speed-up is roughly from cubic to quadratic in runtime.

Figure 2.8: The routing cost in terms of h(i, j)'s and v(i, j)'s

#### 2.3 Multi-Stage Simulated Annealing

Among our two interconnect planning approaches, Z-shaped routing is more accurate than L-shaped routing. But Z-shaped routing is also more expensive than L-shaped routing. Using Z-shaped routing all along will give the most accurate estimation. However, based on the characteristics of simulated annealing, we can speed up the procedure without sacrificing the quality of solutions.

The Wong-Liu floorplanning algorithm [65] is based on simulated annealing which is a technique for solving general optimization problems. The algorithm moves from one solution to another, trying to find the optimum solution. It accepts a move with the probability  $e^{-\Delta C/T}$ , where  $\Delta C$  is the increase of cost by that move and T is the current temperature. When the temperature is very high, different estimation methods for the cost will not show much difference on  $-\Delta C/T$ . That means it does not affect much in performance if we use rough cost function at the beginning of annealing. When temperature gradually decreases, we use more accurate cost estimation. The L-shaped routing estimation is more accurate than the simple center-to-center or half-perimeter estimation. Similarly, the Z-shaped routing is more accurate than the L-shaped routing estimation. Therefore, we will start with the the center-to-center or half-perimeter estimation, gradually transfer to L-shaped routing, and finally switch to Z-shaped routing. This multi-stage approach is very effective in reducing total running time.

In fact, multi-stage simulated annealing is just a method to combine different approaches together in one process. It should be reasonable if those different approaches used in multi-stage simulated annealing are not totally different, which

means they have a certain degree of correlation. In this chapter we use a three-stage simulated annealing approach. The first stage is to get a good initial solution by using only the half-perimeter wire length estimation. The second stage is to estimate interconnect cost by using L-shaped global routing. The third stage is to estimate interconnect cost by using Z-shaped global routing. The transitions between stages are not very abrupt since they evolve from simple to complex, from rough to accurate. However, even for very similar estimations, we still need to find a way to take care of any possible discontinuity in switching cost functions.

#### 2.3.1 Cost Function Transitions

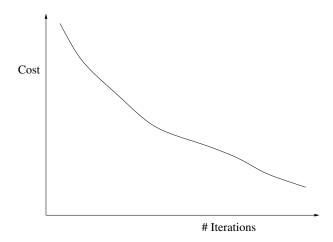

The cost function used in [65] is  $A + \lambda W$ , where A is the total area of the packing, W is the half-perimeter estimation of the interconnect cost, and  $\lambda$  is a constant which controls the relative importance of these two terms and is usually set such that the area term and the interconnect term are approximately balanced. The normal curve of cost versus the number of iterations of simulated annealing process is shown in Figure 2.9.

In our approach, we use the cost function  $\Psi = \alpha A + \beta W + \gamma O$ , where A and W are the same as in [65] and O is the sum of the square of overflow in routings. Although the format of cost function is identical for three stages of the process, the content of each term is different. The term W in stage 1 is obtained by applying half-perimeter method of net bounding boxes; the term W in stages 2 and 3 are obtained by applying pin assignment and summing the net length from pin positions. The term O in stage 1 is zero; the term O in stages 2 and 3 is obtained

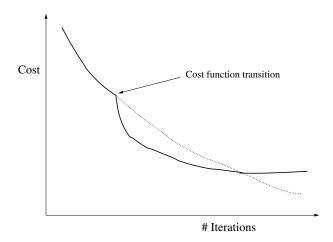

Figure 2.9: Normal curve of cost versus number of iterations

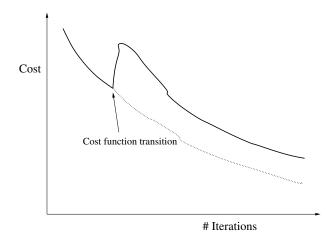

by applying simple-geometry routing and computing the congestion/routability estimation of bin boundaries. Because of the difference of cost functions used in different stages during simulated annealing process, discontinuities may occur when switching stages. One possible scenario is that the annealing process will suddenly converge to suboptimal solution when cost function transition occurs, as shown in Figure 2.10. The other possible scenario is that the annealing process will take much longer time to converge to optimal solution when cost function transition occurs, as shown in Figure 2.11. The discontinuities happen because the temperature is too low for the former scenario and is too high for the latter one when switching cost functions. In order to cope with the discontinuities resulted in the process of switching cost functions, we introduce a temperature adjustment method, which is described in the next subsection.

Figure 2.10: Abormal curve (solid line) of cost versus number of iterations: quickly converges to suboptimal solution

#### 2.3.2 Temperature Adjustment

Simulated annealing uses temperature to control the probability in accepting uphill moves. We use a temperature schedule of the form  $T_k = r * T_{k-1}, k = 1, 2, 3, \ldots$  The initial temperature  $T_0$  is determined by performing a sequence of random moves and computing the quantity  $\Delta_{avg}$ , the average value of the magnitude of change in cost per move. We should have  $e^{-\Delta_{avg}/T_0} = P \cong 1$  so that there will be a high probability of acceptance at high temperatures. This suggests that  $T = -\Delta_{avg}/ln(P)$  is a good choice for  $T_0$ .

In [65], a single cost function is used to evaluate the quality of a solution. However, in our approach, we use different cost functions in different stages. We know that one major term to decide the acceptance of a solution in simulated annealing is  $e^{-\Delta C/T}$ . Take the transition between the first stage and the second stage as an example, the difference of cost in the second stage is typically larger than that

Figure 2.11: Abormal curve (solid line) of cost versus number of iterations: takes a much longer time to converge

in the first stage. That is,  $-\Delta C_{old}>>-\Delta C_{new}$ . Therefore, the probability of accepting uphill moves in the iterative-based process will decrease suddenly and the simulated annealing process will end prematurely. For example, when we encounter the stage transfer from half-perimeter estimation to L-shaped routing, suppose the current temperature is 100, the average  $\Delta C_{old}$  is 20 and the average  $\Delta C_{new}$  is 100. The probability of accepting uphill moves is  $e^{-\Delta C_{old}/T}=0.8$  before switching cost function but it is  $e^{-\Delta C_{new}/T}=0.36$  after cost function transition. This abrupt decrease in acceptance probability would result in quick convergence to suboptimal solution because the current temperature is too low to sustain the annealing process. Similarly, it is possible that after cost function transition, the acceptance probability will substantially increase. In this case, that the current temperature is too high results in slow convergence of the annealing process.

In our approach, in addition to calculating the starting temperature of the

Figure 2.12: Temperature adjustment

first stage, we also determine the starting temperature of the second and the third stages by calculating random move cost with the same approach. When we reach the transition between first and second stages or between second and third stages, we compute the starting temperature of the second or the third stage T' by getting the new average value of the magnitude of change in cost per move, and using the current acceptance ratio,  $P_{curr\_acpt}$ , as a reference probability:  $T' = -\Delta'_{avg}/ln(P_{curr}\_{acpt})$ .

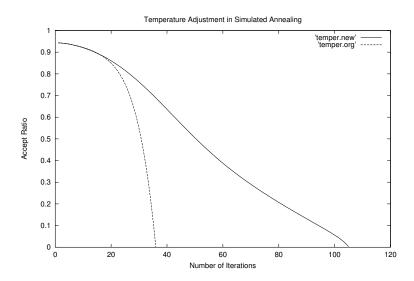

Although we use the current acceptance ratio to compute the new initial temperature during transition, the acceptance ratio will rise. The reason is that for the very first initial temperature estimation, we measure the term by random walks, but there exists very few random walk when transition occurs. We handle this by reducing the temperature much faster than the usual cooling ratio, until the accep-

tance ratio goes back on track. Experimental results show that this approach is really helping the continuity of the simulated annealing process and the quality of performance. (Figure 2.12 shows the effectiveness of applying temperature adjustment approach. The curve would have been the one in dotted line: it suddenly drops because of the abnormal end of the process.)

#### 2.4 Experimental Results

We have tested our approach on some MCNC building blocks examples. All experiments were carried out on a 300MHz Pentium II Intel Processor. In order to compare the performance of the interconnect planning approach with that of the original approach [65] in terms of routability, we perform pin assignment and use Zshaped routing to route the nets in the final floorplans produced by the conventional approach. Figure 2.13 shows the floorplan obtained by our pin assignment and interconnect planning approach. Figure 2.14 shows the floorplan obtained by the original approach. The dashed lines are the grid lines, and the thickness of line in the boundaries denotes the degree of overflow. We can see significant difference in Figure 2.13 and Figure 2.14 for ami49 benchmark in terms of wire overflow, while the packing areas are about the same (Table 2.1 and 2.2). For the five MCNC benchmarks shown in these two tables, we observe that the new approach produces floorplans which are much more routable than the ones produced by the original floorplanner. Note that the maximum violation in Table 2.1 indicates the maximum amount of overflow occurred in any bin boundary after interconnect planning, while the total violations indicate the total amount of overflow occurred in a floorplan. In fact, the new method achieves a significant percentage of improvement in maximum violation and total violations without any area overhead.

Table 2.1: Experimental results of our approach on MCNC examples, compared with the method in [65]

|       |    | Our Floorplanner |          |               |         | Floorplanner in [65] |          |         |

|-------|----|------------------|----------|---------------|---------|----------------------|----------|---------|

| Data  | n  | Time             | Dead     | Total         | Max     | Dead                 | Total    | Max     |

|       |    | (sec)            | Space(%) | $Vios(\mu m)$ | Vio(μm) | Space(%)             | Vios(μm) | Vio(μm) |

| apte  | 9  | 277.6            | 0.99     | 0.51          | 0.27    | 0.86                 | 10.31    | 3.45    |

| xerox | 10 | 589.7            | 0.14     | 0.0           | 0.0     | 0.07                 | 23.92    | 8.88    |

| hp    | 11 | 141.2            | 0.30     | 0.76          | 0.68    | 0.61                 | 15.16    | 3.34    |

| ami33 | 33 | 2220             | 3.66     | 1.55          | 0.64    | 5.68                 | 15.96    | 2.64    |

| ami49 | 49 | 4041             | 2.93     | 7.68          | 2.75    | 3.21                 | 38.62    | 6.75    |

Table 2.2: Performance improvement of our approach on MCNC examples, compared with the method in [65]

|       |    |      | Improvement |        |  |

|-------|----|------|-------------|--------|--|

| Data  | n  | #net | Total       | Max    |  |

|       |    |      | Vios(%)     | Vio(%) |  |

| apte  | 9  | 97   | 95          | 92     |  |

| xerox | 10 | 203  | 100         | 100    |  |

| hp    | 11 | 83   | 95          | 80     |  |

| ami33 | 33 | 123  | 90          | 76     |  |

| ami49 | 49 | 408  | 80          | 59     |  |

## 2.5 Concluding Remarks

This chapter presents a method to integrate floorplanning with interconnect planning. Simple-geometry routing is used to efficiently plan wires during module packing. A congestion cost is combined into the Wong-Liu simulated annealing

Figure 2.13: Result of packing ami49 using interconnect planning approach

Figure 2.14: Result of packing ami49 using original approach

based floorplanner, and a multi-stage simulated annealing strategy is used to effectively reduce the running time. We further develop a temperature adjustment approach to cope with the discontinuities resulting from switching cost functions. Experimental results show that our approach works well.

## **Chapter 3**

# Faster and More Accurate Wiring Evaluation in Interconnect-Centric Floorplanning

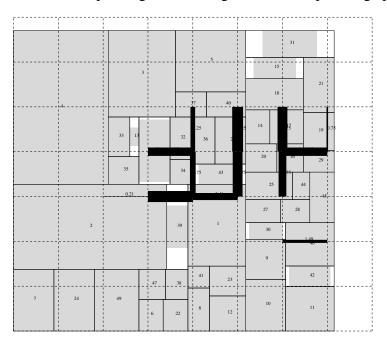

Floorplanning problems typically have relatively small number of blocks (e.g., 50-100) but have a large number of nets (e.g. 20K). Since existing floorplanning algorithms use simulated annelating which needs to examine a large number of floorplans, the increasing number of nets has made interconnect-centric floorplanning computationally very expensive. Moreover, there is almost no systematic way to resolve the congestion problem in such magnitude of number of nets in a given floorplan. In this chapter, we present a simple yet effective idea to significantly reduce the runtime of interconnect-centric florplanning algorithms. Our idea is to group common nets between two blocks into a single net. This faster wiring evaluation technique is very effective. We also present a more accurate global router for wiring evaluation based on Lagrangian Relaxation. The new router helps further congestion reduction while doing interconnect planning in floorplanning. We have incorporated our algorithms into [17] and observed dramatic improvement in runtime. For a 33-block 15K-net problem, we reduced runtime from over 23 hours to less than 50 minutes.

#### 3.1 Introduction

With VLSI technology entering the DSM era, devices are scaled down to smaller sizes and placed at an ever increasing proximity. Meanwhile, with the increase of die sizes, more functions are integrated into one chip. All these significantly increase the communication between different elements. In physical design, the netlist is generated after the partitioning step while the circuits are restructured and funcitonal blocks are obtained. The subsequent floorplanning, placement, and routing steps use the netlist to perform various kinds of optimizations to meet certain constraints. Due to the interconnect-dominant factor in modern VLSI design, communication between components is increasing dramatically. Most of logic hierarchy are flatten during placement and route, so it is very possible that there are hundreds of thousands of nets, while there are only tens of functional blocks in contrast. It goes without saying that the complexity of evaluating such netlists with enormous size of nets is extremely high. How to model and evaluate those high-density interconnection is becoming one of the most challenging issues in modern high-performance VLSI design.

Very recently, interconnect planning (especially global interconnects) is the key issue in modern VLSI physical design [47, 48]. However, with tens or hundreds of thousands of interconnect in standard-cell or full-custom design after circuits partitioning, interconnect planning is time-comsuming. Many floorplanning algorithms, including slicing and non-slicing, have been proposed in past decades [17, 29, 43, 45, 49, 65], but they did not take interconnect planning into account except [17]. In [17], we integrate floorplanning and efficient interconnect planning.

Since every wiring evaluation step uses a simple-geometry global router, [17] can only process moderate-sized netlists (e.g. 1000 nets) but will not be efficient to solve problems with very large netlists (e.g. 10K nets). Furthermore, [17] used a heuristic global router to sequentially route global interconnects, the performance of which depends on the ordering of nets to be routed.

Since existing floorplanning algorithms use simulated annealing which needs to examine a large number of floorplans, the increasing number of nets has made interconnect-centric floorplanning computationally very expensive. In this chapter, we present a simple yet effective idea to significantly reduce the runtime of interconnect-centric floorplanning algorithms. Our approach is to group common nets between two blocks into a single net. Before grouping the nets, multi-terminal nets are first decomposed into two-terminal nets. Bounded-degree hypergraph-tograph transformation is used to preserve the constraint for pin-limit in a block. This net reduction technique is very effective. Suppose we are given a problem with 50 blocks and 20K nets. After net reduction, we can have at most 1250 nets (which is the case when we have connections between all pairs of blocks). This is a significant reduction from 20K nets. If we need linear time to process the nets each time we examine a candidate floorplan, then we would have more than 15X speedup in runtime after net reduction. In our experiments, for a problem with 33 blocks and 15K nets, the floorplanning algorithm in [17] took more than 23 hours to run on the original netlist in 300MHz machines, but took less than 50 minutes after net reduction. Meanwhile, we present a more accurate global router for wiring evaluation in this chapter. We use Lagrangian relaxation technique to systematically route

global interconnects, trying to minimize the maximum violation against the routing resources. This Lagrangian relaxation router is performing well. It successfully minimizes the maximum violation and total violations compared with router in [17] when given a candidate floorplan.

The rest of the chapter is organized as follows. Section 3.2 describes the wiring evaluation. Faster wiring evaluation and the algorithm for net reduction are presented in Section 3.3; more accurate wiring evaluation and Lagrangian relaxation technique application are presented in Section 3.4. Experimental results are shown in Section 3.5 and the concluding remarks are presented in Section 3.6.

## 3.2 Wiring Evaluation in Interconnect Centric Floorplanning

In physical design, the netlist is generated after partitioning step while the circuits are restructured and funcitonal blocks are obtained. The subsequent floor-planning, placement, and routing steps use the netlist to perform various kinds of optimizations to meet certain constraints. In the literature of floorplanning research, the focus of optimization was to minimize the total packing area as well as the wiring cost. In modern VLSI design, the size of design becomes much larger, thus the complexity of netlist is extremely higher than ever. Since the interconnect-centric floorplanning tool plays more important role in physical design, how to model and evaluate large number of interconnections has become one of the most challenging issues in modern high-performance VLSI design.

Our approach to speedup the wiring evaluation for such a huge netlist in floorplanning is net reduction. The idea is to group common nets between two

blocks into a single net. Before grouping the nets, it is necessary for multi-terminal nets to be decomposed into two-terminal nets first. We use bounded-degree hypergraph-to-graph transformation to accomplish the decomposition. The main objective of this approach is to meet the constraint that the connection of each block is within its pin-limit. It may look like the general connectivity approaches in [59, 64], which are different from this net reduction in terms of the objectives. In [59, 64], they use general connectivity model to estimate the wirelength and timing evaluation during placement. In our approach, however, in addition to get "connectivity matrix", we perform global routing based on the net regrouping result.

After net reduction, we can use another approach to further reduce the congestion occurred in floorplanning. This approach is based on Lagrangian relaxation and the objective is to minimize the maximum violation against routing resources in a given floorplan. The update of Lagrangian multipliers will help reduce the local congestion in a systematical way, trying to balance the routing among routing regions. Because of the nature of Lagrangian relaxation, that is, it takes longer runtime to converge to optimal solutions, we perform it at the end of the process. Combining the net reduction and Lagrangian relaxation based global router makes the interconnect-centric floorplanning more efficient and effective.

To effectively evaluate wiring results, we give some general definitions to some subjective terms in this chapter. In order to measure routability, we divide the floorplan into a number of bins by a grid the same way in [17]. For each bin boundary, we define its *capacity* as the maximum number of nets that can cross it. If the number of nets crossing a bin boundary exceeds the capacity of the bin boundary,

there is *overflow* in that bin boundary. We estimate the *maximum overflow* among all bin boundaries and *total overflow* for all overflow occurred as important part of our objectives to evaluate the quality of a floorplan. In the following sections, we describe the details of efficient wiring evaluation in Section 3.3 and those of effective wiring evaluation in Section 3.4.

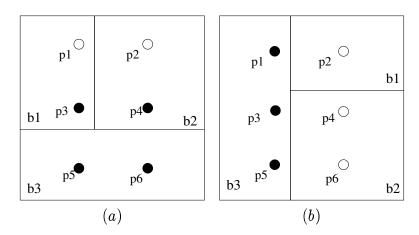

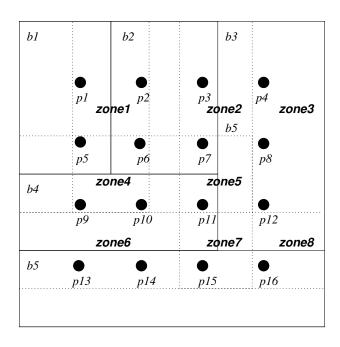

### 3.3 Faster Wiring Evaluation Based on Net Reduction

In this section, we present an approach, *net reduction*, to significantly reduce the runtime of interconnect-centric floorplanning algorithms. Net reduction is a technique to help interconnect cost evaluation for huge netlists. For two-terminal nets, net reduction is easy to be accomplished by grouping them into wider nets (See Figure 3.1). For multi-terminal nets, however, net decomposition is needed to perform the net reduction. Arbitrary net decomposition will need to pay the price of crowding the connections into a block. As an example, Figure 3.2 shows a netlist with one two-terminal net and three multi-terminal nets in a floorplan containing six blocks. Without loss of generality, assume that the pin-limit for block  $b_4$  is 3. In Figure 3.3, with the same number of wider nets, (a) shows an illegal net decomposition since the connection of block  $b_4$  is 6, which exceeds the pin-limit, while (b) shows a feasible net decomposition.

#### 3.3.1 Problem Formulation

Based on the objective illustrated above, we can state the net reduction problem as follows.

Figure 3.1: Net reduction (a) Original netlist. (b) Reduced netlist.

Figure 3.2: A netlist with multi-terminal nets.

Figure 3.3: Two net decomposition solutions for the example in Figure 3.2. (a) An illegal net decomposition since block  $b_4$  exceeds its pin-limit. (b) A feasible net decomposition.

**Problem 3.3.1.** Given a floorplan of blocks  $b_1, \dots, b_n$ , and their pin-limit  $d_1, \dots, d_n$ , respectively, and given a netlist of nets (multi-terminal and two-terminal)  $e_1, \dots, e_m$ , find a net reduction solution such that the resultant nets are two-terminal nets (regrouping to wider nets) and that the solution meets the constraint that the connection for each block is within its pin-limit.

#### 3.3.2 Algorithm for Net Reduction

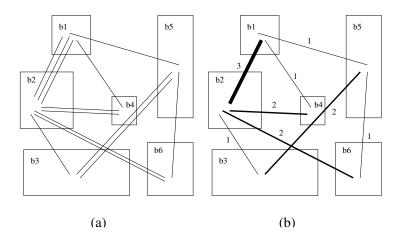

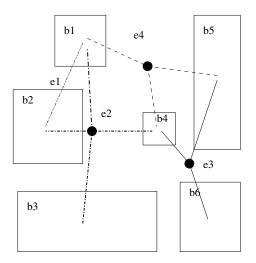

Our algorithm for net reduction is similar to the work in [41] for board-level routing for FPGA-based logic emulation. According to the objective in the problem formulation, we observe that if we can model the netlist as a hypergraph by representing the functional blocks in a floorplan as *vertices* and the nets as *hyperedges*, the problem of net decomposition can be seen as a bounded-degree hypergraph-tograph transformation, where the bounded degree is the pin-limit for a block.

We introduce the bounded-degree hypergraph-to-graph transformation and use it to decompose those nets and create the corresponding spanning trees. Then we present the net reduction algorithm based on the transformation and resultant spanning trees. The last step of the algorithm is to group all decomposed two-terminal nets into wider interconnect.

#### 3.3.2.1 Bounded-Degree Hypergraph-to-Graph Transformation

We want to solve the problem of transforming a hypergraph to a graph by modelling each hyperedge as a spanning tree so that the degree of each vertex v in the resultant graph does not exceed some given bound  $\sigma_v$ . This problem is studied as the *bounded-degree hypergraph-to-graph transformation problem*. Figure 3.4 shows a transformation of a hypergraph to a graph where the degrees of all vertices are bounded by 3. Each hyperedge is transformed to a spanning tree that connects all the vertices in the hyperedge. In general, the degree bound  $\sigma_v$  can be different for different vertex v.

To model a hyperedge of  $p(\geq 2)$  vertices as a spanning tree that connects the p vertices, clearly the sum of the degrees of the vertices in the spanning tree must be 2(p-1) and the degree of each vertex must be at least one. On the other hand, it can be shown that given any vector  $d=(d_1,\ldots,d_p)\in \mathbf{N}^p$  such that  $\sum_{i=1}^p d_i=2(p-1)$  and  $d_1,\ldots,d_p\geq 1$ , we can always construct a spanning tree of p vertices whose degrees are equal to the p elements of vector d. We can easily construct an efficient algorithm for generating a spanning tree given any valid degree specification vector. Furthermore, we can guarantee to get a *minimum-height* spanning tree, which is

Figure 3.4: Hypergraph-to-graph transformation. (a)A hypergraph with four hyperedges: e1, e2, e3, and e4. (b)A graph formed by combining four spanning trees corresponding to the four hyperedges in (a).

good for performance.

Now we describe the algorithm for the bounded-degree hyper-graph-to-graph transformation problem. Suppose we are to transform a hypergraph H=(V,E) to a graph G given the degree bound  $\sigma_v$  of each vertex v in V. We construct a flow network  $W=(\mathcal{N},\mathcal{A})$  as follows. The node set  $\mathcal{N}$  is  $\{e_1,\ldots,e_{|E|},v_1,\ldots,v_{|V|},s,t\}$  where node  $e_i$  corresponds to hyperedge  $e_i$  in E ( $i=1,\ldots,|E|$ ), node  $v_j$  corresponds to vertex  $v_j$  in V ( $j=1,\ldots,|V|$ ), node s is the source, and node t is the sink. For every hyperedge  $e_i$ , if it connects p vertices, then there is an arc from node s to node s to node s is an arc from node s to node s is the source, and for every vertex s connected by hyperedge s, there is an arc from node s to node s is node s to node s in s to node s in s

t with capacity  $c(v_j, t) = \sigma_{v_j} - deg_H(v_j)$ , where  $deg_H(v_j)$  is the degree of vertex  $v_j$  in H. For example, to transform the hypergraph in Figure 3.4(a) to a graph where the degree of each vertex is bounded by 3, we construct the network shown in Figure 3.5(a).