# Copyright

by

Li Ji

2014

# The Thesis Committee for Li Ji Certifies that this is the approved version of the following thesis:

# $SiO_x$ -Based Resistive Switching Memory Integrated in a Nanopillar Structure Fabricated by Nanosphere Lithography

| APPROVED BY    |          |

|----------------|----------|

| SUPERVISING CO | MMITTEE: |

| Supervisor: |                |  |

|-------------|----------------|--|

|             | Edward T. Yu   |  |

|             | John G. Ekerdt |  |

# $SiO_x$ -Based Resistive Switching Memory Integrated in a Nanopillar Structure Fabricated by Nanosphere Lithography

by

Li Ji, B. E.

#### **THESIS**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

#### MASTER OF SCIENCE IN ENGINEERING

The University of Texas at Austin

August 2014

### **Dedication**

To my parents and my wife

#### Acknowledgements

I would like to express my sincere gratitude to my research advisor, Prof. Edward T. Yu, for his advice, guidance, and endless support for my research. His keen insight and commitment to research has and will continue to inspire me in my professional endeavors. I am indebted to Prof. John G. Ekerdt, Prof. Allen J. Bard and Prof. Jack C. Lee for help and guidance in many aspects of research.

The work described herein would not have been possible without the help from my roommate, Yao-Feng Chang. He has extended my vision to the field of RRAM and has helped me on the measurements and analysis of data. Special thanks go to Dr. Ping-Chun Li for valuable advice and suggestions.

Finally, I would like to appreciate my parents, Liji Wu and Jian Li, for their love and support throughout my education. I am also grateful for my wife, Lufang Zhang, for her love, trust and understanding.

#### **Abstract**

SiO<sub>x</sub>-Based Resistive Switching Memory Integrated in a Nanopillar **Structure Fabricated by Nanosphere Lithography**

Li Ji, M.S.E.

The University of Texas at Austin, 2014

Supervisor: Edward T. Yu, John G. Ekerdt

A highly compact, one diode-one resistor (1D-1R) SiOx-based resistive switching memory device with nano-pillar architecture has been achieved for the first time using nano-sphere lithography. The average nano-pillar height and diameter are 1.3 µm and 130 nm, respectively. Low-voltage electroforming using DC bias and AC pulse response in the 50ns regime demonstrate good potential for high-speed, low-energy nonvolatile memory. Nano-sphere deposition, oxygen-plasma isolation, and nano-pillar formation by deep-Sietching are studied and optimized for the 1D-1R configurations. Excellent electrical performance, data retention and the potential for wafer-scale integration are promising for future non-volatile memory applications.

vi

## **Table of Contents**

| List of Tables  |                                                                   | viii |

|-----------------|-------------------------------------------------------------------|------|

| List of Figures |                                                                   | ix   |

| Chapter 1: Inta | roduction                                                         | 1    |

| 1.1 R           | Reemergence of Memristor                                          | 1    |

| 1.1             | Classification of RRAM by Switching Modes                         | 5    |

| 1.2             | Classification of RRAM by Switching Mechanisms                    | 7    |

| 1.3             | Advantages of intrinsic SiO <sub>x</sub> based unipolar type RRAM | 8    |

| 1.4             | Purpose of this work                                              | 9    |

| Chapter 2: Fab  | prication Processes                                               | 11   |

| 2.1 S           | ubstrate preparation                                              | 11   |

| 2.2 H           | Iard mask fabrication                                             | 11   |

| 2.3 N           | Vanopillars fabrication                                           | 12   |

| 2.4 S           | EM Characterizations                                              | 15   |

| Chapter 3: Res  | sults and Discussion                                              | 17   |

| 3.1 N           | Measurement setups                                                | 17   |

| 3.2 R           | Results of 1R architecture                                        | 17   |

| 3.3 R           | Results of 1D-1R architecture                                     | 20   |

| Chapter 4: Con  | nclusion and Future Work                                          | 23   |

| 4.1 C           | Conclusion                                                        | 23   |

| 4.2 F           | uture work                                                        | 23   |

| Bibliography    |                                                                   | 24   |

| Vita            |                                                                   | 32   |

## **List of Tables**

| Table 1: | Potential Evaluation for Emerging Research Memory Devices. Cited  |

|----------|-------------------------------------------------------------------|

|          | from The 2013 International Technology Roadmap for Semiconductors |

|          | (ITRS)4                                                           |

# **List of Figures**

| Figure 1. | The four fundamental two-terminal circuit elements: resistor, capacitor,             |  |  |  |  |  |  |

|-----------|--------------------------------------------------------------------------------------|--|--|--|--|--|--|

|           | inductor and memristor [2].                                                          |  |  |  |  |  |  |

| Figure 2: | Taxonomy of emerging memory devices. Cited from The 2013                             |  |  |  |  |  |  |

|           | International Technology Roadmap for Semiconductors (ITRS)3                          |  |  |  |  |  |  |

| Figure 3. | I-V characteristics in a bipolar type RRAM. The arrows indicate the                  |  |  |  |  |  |  |

|           | voltage sweep directions. Compliance current is applied during set                   |  |  |  |  |  |  |

|           | process. Graphics are reproductions from Ref. [42]5                                  |  |  |  |  |  |  |

| Figure 4. | I-V characteristics in a unipolar type RRAM. The arrows indicate the                 |  |  |  |  |  |  |

|           | voltage sweep directions. Compliance current is applied during set                   |  |  |  |  |  |  |

|           | process. Graphics are reproductions from Ref. [42]6                                  |  |  |  |  |  |  |

| Figure 5. | Resistance Modulation Geometry. Cited from tutorial of 43 <sup>rd</sup> IEEE         |  |  |  |  |  |  |

|           | Semiconductor Interface Specialist Conference (SISC), by Dirk Wouters                |  |  |  |  |  |  |

|           | from IMEC7                                                                           |  |  |  |  |  |  |

| Figure 6. | Schematic of a typical crossbar structure. Cited from Crossbar Inc.                  |  |  |  |  |  |  |

|           | (https://www.crossbar-inc.com/)                                                      |  |  |  |  |  |  |

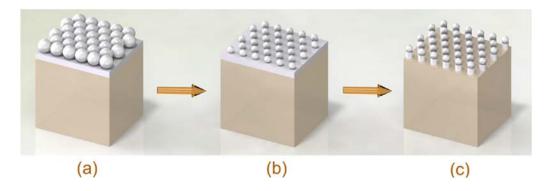

| Figure 7. | The process flow for hard mask fabrication with Nanosphere                           |  |  |  |  |  |  |

|           | Lithography technique. The brown cubic box represents silicon                        |  |  |  |  |  |  |

|           | substrate. The white thin film represents SiO <sub>x</sub> . The white spheres       |  |  |  |  |  |  |

|           | represent for polystyrene nanospheres. (a) Nanosphere deposition on 60               |  |  |  |  |  |  |

|           | nm SiO <sub>x</sub> . (b) Reactive-ion etching (RIE) oxygen plasma shrinks the       |  |  |  |  |  |  |

|           | diameter of nanospheres. (c) RIE plasma for SiO <sub>x</sub> dry etching to transfer |  |  |  |  |  |  |

|           |                                                                                      |  |  |  |  |  |  |

|           | the pattern into SiO <sub>x</sub> layer                                              |  |  |  |  |  |  |

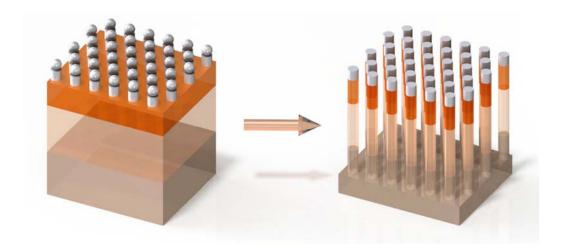

| Figure 9.  | Schematic of 1D-1R pillar fabrication via deep silicon etch process. The       |

|------------|--------------------------------------------------------------------------------|

|            | different colors in substrate represents different doping concentration.       |

|            | Nanospheres were removed by ultrasonic bath in toluene14                       |

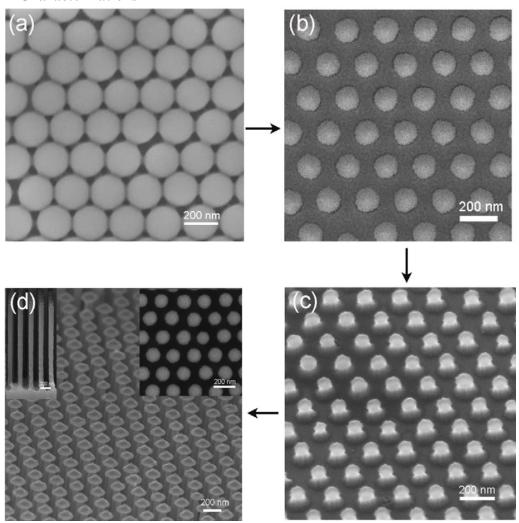

| Figure 10. | SEM characterization for each process. (a) nanosphere deposition, (b)          |

|            | RIE oxygen plasma shrinks the diameter of nanospheres, (c) RIE plasma          |

|            | for $SiO_x$ dry etching to transfer the pattern into $SiO_x$ layer and (d) top |

|            | view, cross section view and tilted view of nanopillars after deep silicon     |

|            | etch process. The scale bars in every images are 200nm in length15             |

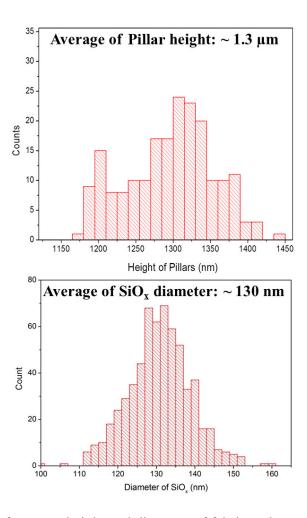

| Figure 11. | Statistics of average height and diameter of fabricated nanopillars. The       |

|            | average pillar height is around 1300 nm and the average pillar diameter        |

|            | is around 130 nm                                                               |

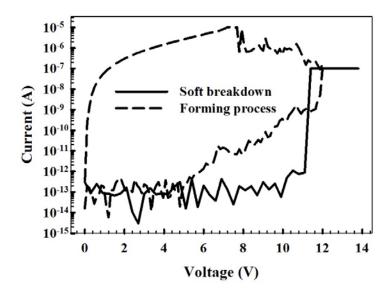

| Figure 12. | Double sweep forming process. The first run is soft breakdown, with            |

|            | compliance current fixed at 100 nA (solid line). The second run is             |

|            | forming process without any compliance current (dash line)17                   |

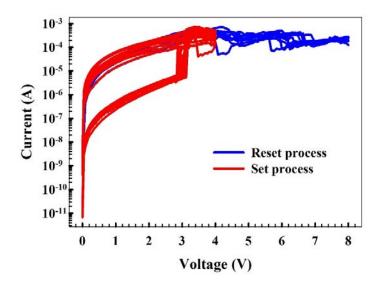

| Figure 13. | I-V characteristics for set and reset process for 1R structure samples.18      |

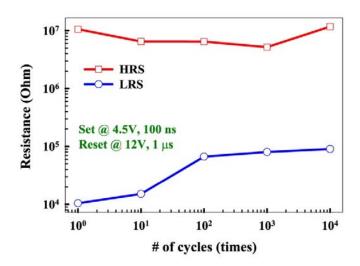

| Figure 14. | Endurance tests of 1R structure samples                                        |

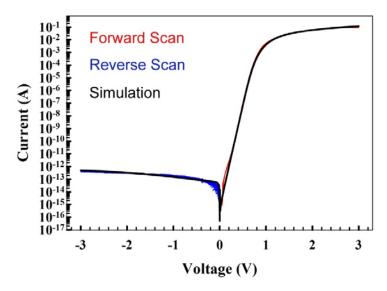

| Figure 15. | Characterizations and simulation of p-n Si diode used as 1D element in         |

|            | 1D-1R structure. Red line, blue line and black line are forward scan,          |

|            | reverse scan and simulation results, respectively20                            |

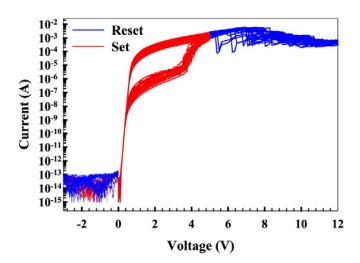

| Figure 16. | I-V results of set and reset process for 1D-1R structure samples21             |

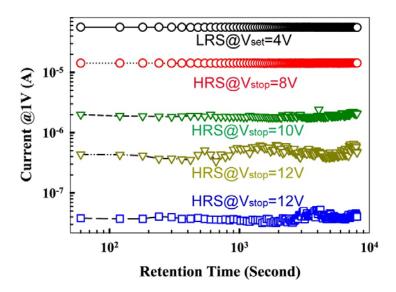

| Figure 17. | Retention measurement results of multi-level operation by controlling          |

|            | the reset stop voltage                                                         |

#### **Chapter 1: Introduction**

#### 1.1 Reemergence of Memristor

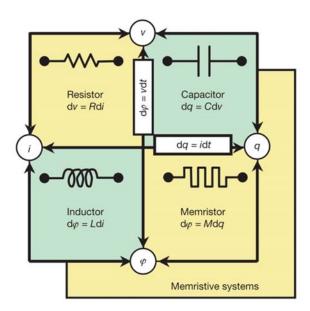

The capacitor, resistor, and inductor, were considered as the three basic electrical circuit elements for a long time. In 1971, Leon Chua postulated the fourth basic circuit element naming in the *memristor* (memory + resistor), in which the nonlinear resistance can be memorized indefinitely by controlling the flow of the electrical charge or the magnetic flux, as shown in Figure 1[1].

Figure 1. The four fundamental two-terminal circuit elements: resistor, capacitor, inductor and memristor [2].

The observations of such behavior, mainly in oxides insulators, have been reported for over 40 years [3-6]. The early observations of resistance switching were not robust enough for real applications and remain only for scientific studies. Through there were

initial attempts to validate Chua's theory for practical design, the complexity involved in implementing memristors made them impractical for commercial products. The recent revival of interest in such resistive switching started in late 1990s, with perovskite oxides such a SrTiO<sub>3</sub> and SrZrO<sub>3</sub>. In 2004 *International Electron Devices Meeting* (IEDM), Samsung presented a paper demonstrating NiO cells integrated with conventional complementary metal-oxide-semiconductor (CMOS) in a one-transistor-one-resistor (1T1R) device architecture [7]. This work suggested a memory technology based on resistive switching may be feasible. Particularly in 2008, a paper in *Nature* by a group from Hewlett Packard (HP) demonstrated memristive behavior in crossbar memory arrays based on TiO<sub>2</sub> and credited the work of Leon Chua in 1970s to the phenomenon they observed[2]. Since the reemergence of this missing memristor, the research output has grown exponentially with publications in conferences and journals.

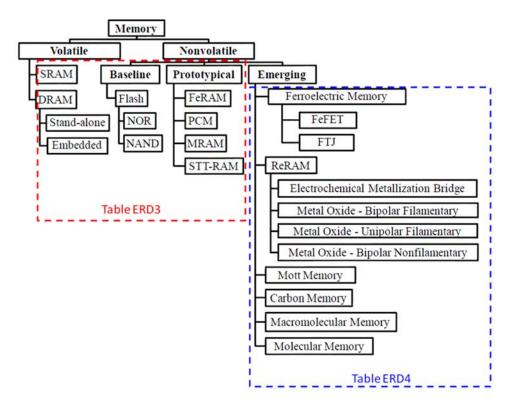

Within the semiconductor industry, it is considered that the transistor based flash memory technologies are approaching the end of scaling, because the building block of current CMOS technology will be difficult to scale below 10 nm regime due to increasing tunneling current, loss of gate control and increased threshold fluctuations. In addition, for a charge-storage memory, it becomes difficult to control or retain electrons with continuing shrinking of dimensions. Hence, to meet markets' fast growing demand for portable electronic devices, many concepts and studies for non-field-effect-transistor (non-FET) based memories have been pursued as potential alternatives for Flash memory, such as carbon memory[8], Mott memory[9], Ferroelectric-RAM (FeRAM)[10-14], Organic-RAM (ORAM)[15-17], Resistive-RAM (RRAM)[16, 18-39], as shown in Figure 2, which illustrates the taxonomy of emerging memory devices cited from *The 2013 International Technology Roadmap for Semiconductors* (the 2013 ITRS) [40].

Figure 2: Taxonomy of emerging memory devices. Cited from *The 2013 International Technology Roadmap for Semiconductors* (ITRS).

A new memory will ideally combine the best features of current memories including the high density of DRAM, fast speed of SRAM and nonvolatile property of flash memory with a CMOS compatible fabrication technology. Table 1 is the list of the Overall Potential Assessment (OPA) for all emerging memory devices of becoming a viable, manufacturable memory. Among all of them, RRAM stands out with a highest OPA score. Overall RRAM assessment is similar to or better than existing CMOS-based nonvolatile memories (Flash). A clear advantage of RRAM is scalability owing to the filamentary conduction and switching mechanisms. The smallest feature can be scaled down to 5 nm [41]. The simple device structure, metal-insulator-metal stack, and fab-friendly materials also contribute to high raging in CMOS compatibility. For FeRAM and Ferroelectric

Tunnel Junction (FTJ) memory, the major challenge is the control of ferroelectric-semiconductor interface. The scalability of both beyond 22 nm generation is uncertain. Mott memory is considered to have fast speed but suffers from the operation temperature and reliability. Organic-based RAM, Macromolecular Memory and Molecular Memory, face severe reliability challenges [40].

Table 1: Potential Evaluation for Emerging Research Memory Devices. Cited from *The 2013 International Technology Roadmap for Semiconductors* (ITRS).

|                                        |             | Scalability | Speed | Energy<br>Efficiency | ON/OFF "1"/"0"<br>Ratio | Operational<br>Reliability | Room<br>Temperature<br>Operation | CMOS<br>Technological<br>Compatibility | CMOS Architectura<br>Compatibility |

|----------------------------------------|-------------|-------------|-------|----------------------|-------------------------|----------------------------|----------------------------------|----------------------------------------|------------------------------------|

| FeFET                                  | 2.00        | 1           | +     | 1                    | 1                       | 1                          | ł                                | Ŧ                                      | +                                  |

| OPA = 17.4                             | 1.00        | 2.0         | 2.4   | 2.3                  | 2.1                     | 1.7                        | 2.4                              | 2.3                                    | 2.4                                |

| OFA - 17.4                             | 3.00 7      | 2.0         | 2.4   | 2.3                  | 2.1                     | 1.7                        | 2.4                              | 2.3                                    | 2.4                                |

| FTJ                                    | 2.00 -      | 1           | 1     | 1                    | +                       | +                          |                                  | +                                      | 1                                  |

| OPA = 17.3                             | 1.00        | 2.3         | 2.2   | 2.2                  | 2.1                     | 1.7                        | 2.4                              | 2.1                                    | 2.2                                |

| RRAM                                   | 2.00        | 1           | 1     | 1                    | +                       | 1                          | Ť                                | 1                                      | 1                                  |

| OPA = 18.7                             | .5000       | 2.9         | 2.5   | 2.1                  | 2.2                     | 1.6                        | 2.5                              | 2.4                                    | 2.4                                |

| Mott                                   | 3<br>2<br>1 | 1           | Ŧ     | 1                    | 1                       | 1                          | ł                                | +                                      | 1                                  |

| OPA = 16.6                             | 16.6        | 2.1         | 2.4   | 2.1                  | 2.2                     | 1.7                        | 1.9                              | 2.0                                    | 2.2                                |

| Macromolecular                         | 2.00        | 1           | 1     | 1                    | ŧ                       | Ţ                          | 1                                | +                                      | +                                  |

| OPA = 13.9                             |             | 1.8         | 1.7   | 1.7                  | 1.6                     | 1.3                        | 2.2                              | 1.7                                    | 1.8                                |

| Molecular                              | 2.00        | †           | 1     | 1                    | 1                       | Į                          | +                                | 1                                      | 1                                  |

| OPA = 13.9                             |             | 2.6         | 1.7   | 2.0                  | 1.3                     | 1.1                        | 2.0                              | 1.6                                    | 1.8                                |

| Carbon-based                           | 2.00        | +           | +     | 1                    | 1                       | t                          | Ŧ                                | 1                                      | 1                                  |

| OPA = 17                               |             | 2.2         | 2.2   | 2.0                  | 2.3                     | 1.7                        | 2.4                              | 2.0                                    | 2.2                                |

| Color so<br>OPA ≥<br>16 < OPA<br>OPA ≤ | 20<br>< 20  |             |       |                      |                         |                            |                                  |                                        |                                    |

#### 1.1 Classification of RRAM by Switching Modes

The architecture of RRAM is simple. The resistive switching element is a two-terminal devices with an active resistive switching layer sandwiched between two metal electrodes. The switching event from High Resistance State (HRS) to Low Resistance State (LRS) is called the *set* process. Conversely, the switch from LRS to HRS is named the *reset* process. For a fresh sample, a sufficiently large voltage (> set voltage) is usually applied to remove the initial resistance state for the subsequent cycles. This process is called *forming* process. It is worth noting that an enforced compliance current is usually applied during set process to avoid a permanent dielectric breakdown. This can be done by a semiconductor parameter analyzer (for individual device tests) or by a memory cell selection transistor/diode or a series resistor (in more realistic circuit implementations) [42]. Based on the different phenomenological behavior, the switching modes of RRAM can be generally classified into two switching modes: unipolar and bipolar.

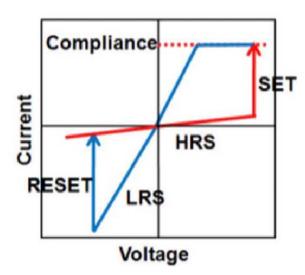

Figure 3. I-V characteristics in a bipolar type RRAM. The arrows indicate the voltage sweep directions. Compliance current is applied during set process. Graphics are reproductions from Ref. [42].

Figure 3 is the I-V characteristic of a typical bipolar type RRAM. The change of resistance is dependent on voltage sweeping polarity. Set occurs at one polarity while reset occurs only at the other polarity. This type of switching behavior can be observed in many metal oxides, such as perovskite oxides, TiO<sub>2</sub>, HfO<sub>2</sub> or metal-doped SiO<sub>2</sub>.

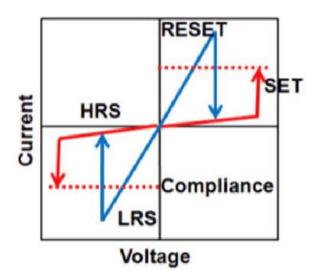

Figure 4. I-V characteristics in a unipolar type RRAM. The arrows indicate the voltage sweep directions. Compliance current is applied during set process. Graphics are reproductions from Ref. [42].

Figure 4 is a representative I-V characteristic for unipolar type RRAM. The resistance switching depends only on the amplitude of voltage but not on the polarity, whether it is positively or negatively biased. As shown in Figure 4, the change from HRS to LRS is the set voltage. The reset process, from LRS to HRS, doesn't require a compliance current. This type of behavior is usually observed in highly insulating oxides, such as nickel oxide [24, 43-51], aluminum oxide [19, 52, 53], zinc oxide [23, 32, 54-56] and silicon oxide [57-82].

#### 1.2 Classification of RRAM by Switching Mechanisms

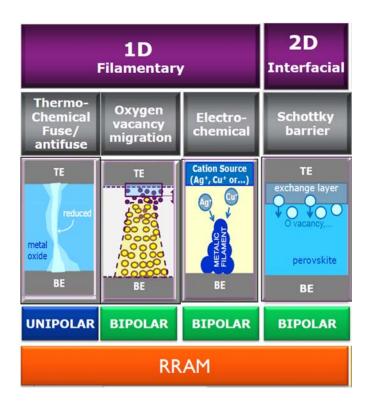

Based on the switching mechanism, RRAM can be categorized as (i) 1D filamentary type, including thermochemical fuse/antifuse, oxygen vacancy migration and electrochemical switching or (ii) 2D interfacial type, based on the change of Schottky barrier height between oxide/metal interfaces, as illustrated in Figure 5.

Figure 5. Resistance Modulation Geometry. Cited from tutorial of 43<sup>rd</sup> IEEE Semiconductor Interface Specialist Conference (SISC), by Dirk Wouters from IMEC.

For a unipolar type thermochemical fuse/antifuse RRAM, a conducting filament is formed during the forming process. During the reset process, the conducting filament is antifused or ruptured due to the Joule heating effects when a high current flowing through

it. During the set process, the filament is fused when a sufficiently applied with high electric filed is applied

Oxygen vacancies are considered to be the origin of resistive switching phenomena in various transition metal oxides, such as NiO [24, 49, 50, 83-85], SrTiO<sub>3</sub> [86-90] and TiO<sub>2</sub> [91]. For example, the movement of oxygen vacancies, particularly at the boundary of metal electrode and oxide interface, changes the valence of transition-metal ions (*e.g.*, between Ti<sup>3+</sup> and Ti<sup>4+</sup> in TiO<sub>2</sub>) and thus changes the conducting state [92].

Electrochemical RRAM or Redox type RAM (ReRAM) is based on mobil metal anions or cations embedded in a solid state electrolyte. The reduction-oxidization (redox) electrochemical process will create or annihilate of a metallic conducting path (metal filament), resulting in the switching between HRS and LRS. This type is intrinsically bipolar due owing to the polarity dependence of the electrochemical redox process. The ReRAM are usually metal doped systems, such as CuS [93] and metal doped SiO<sub>2</sub> [94-97].

#### 1.3 Advantages of intrinsic SiO<sub>x</sub> based unipolar type RRAM.

Owing to its low cost, high quality Si/SiO<sub>x</sub> interface and excellent insulating properties, SiO<sub>2</sub> has been used as MOSFET gate oxide for many decades. The compatibility with CMOS technology makes SiO<sub>x</sub> an excellent candidate for RRAM applications. In addition, the resistive switching behavior has been observed as early as 1962 by Hickmott [3] and has been modeled by Dearnaley in 1970s [5]. They observed that a simple device with Au/SiO<sub>x</sub>/Al structure can form an active device based on its repeatable negative resistance phenomenon. Recently, Tour's group from Rice University reported resistive switching behaviors based on SiO<sub>x</sub>, indicating that this traditionally passive material can be converted to an active memory element by external electrical activation [60, 62, 63, 65, 77, 80, 81, 98].

In addition, intrinsic SiO<sub>x</sub> shows unipolar type behavior and this property allows its integration into one-diode-one-resistor architecture, which yields the high density and reduced complexity. The purpose of many memory systems is to store massive amounts of data, and therefore memory capacity (or memory density) is one of the most important system parameters. A functional memory cell usually comprises two components: the 'storage node' and the 'select device', the latter of which allows a given memory cell in an array to be addressed for read or write. Both components impact scaling limits for memory. In a two-dimensional layout using planar select transistors the cell layout area is Acell = (6-8) F<sup>2</sup> (F is the smallest feature size in a technology node). In order to reach the highest possible memory density for 2D structure, a vertical selector can be used. As discussed above, for a bipolar type RRAM, the set and reset process have opposite voltage polarity. So it cannot be integrated into simple 1D-1R architecture. For a unipolar type, set and reset process have same polarity so opposite voltage is not required during operation and it is applicable for 1D-1R architecture. Since no transistors are involved, the scale down problem for transistors will not be a limiting factor in RRAM application. This provides the highest density attainable in a 2D planar structure (4F<sup>2</sup>). Furthermore, this planar structure is conductive to multi-layer integration (3D stacking) and multi-level operation, further increasing the storage capacity.

#### 1.4 Purpose of this work

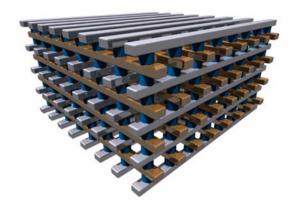

Due to the simple MIM structure, RRAM can be easily incorporated into a cross bar structure, as shown in Figure 6.

Figure 6. Schematic of a typical crossbar structure. Cited from Crossbar Inc. (https://www.crossbar-inc.com/)

However, the crossbar structure can lead to undesirable misreading of the state within a memory cell due to the *sneak path* issue between adjacent cells. The purpose of embedded diode elements is essentially to minimize leakage current through unselected paths (sneak paths). In this work, we fabricated 1D-1R nanopillar devices consisting of a SiO<sub>x</sub> resistive switching element and p-n diode integrated in nanopillar structure. Nanosphere lithography was used because of its low cost, wafer-scale fabrication capability and high throughout in deep sub-micrometer region.

#### **Chapter 2: Fabrication Processes**

#### 2.1 Substrate preparation

(100) n-type silicon wafers were purchased from a commercial vendor (University Wafer Inc.) with resistivity of 0.001-0.005 ohm-cm. 3 nm Ti and 100 nm Au were successively deposited onto the backside of the wafer as bottom contact via e-beam evaporation (PVD, CHA Industries). 60 nm thick SiO<sub>x</sub> was deposited on the front side of wafer using the same method. Prior to each deposition, samples were dipped into buffered oxide etch solution (6:1) to remove the native oxide.

#### 2.2 Hard mask fabrication

Figure 7. The process flow for hard mask fabrication with Nanosphere Lithography technique. The brown cubic box represents silicon substrate. The white thin film represents SiO<sub>x</sub>. The white spheres represent for polystyrene nanospheres. (a) Nanosphere deposition on 60 nm SiO<sub>x</sub>. (b) Reactive-ion etching (RIE) oxygen plasma shrinks the diameter of nanospheres. (c) RIE plasma for SiO<sub>x</sub> dry etching to transfer the pattern into SiO<sub>x</sub> layer.

$18M\Omega$  deionized water and 200nm polystyrene nanospheres (Polysciences Inc.) were used for nanosphere mask preparation. 200nm nanospheres were chosen due to a trade-off between minimum feature size and larger-scale uniformity. Polystyrene

nanosphere solution was dropped on top of microscope coverslips. This was then introduced to air-water interface in petri dish filled with  $18M\Omega$  DI water. The polystyrene solution spread out at the air-water interface forming monolayer. Prior to monolayer formation, a prepared silicon substrate with  $SiO_x$  coating was immersed at the bottom of petridish. The monolayer was then transferred to immersed substrate by slightly lifting the substrate. Then the sample was dried in air. The diameter of each NS in the monolayer was reduced by reactive ion etching (Oxford 80 RIE) in oxygen-plasma (80 sccm O2; power 60 W; pressure 100 mTorr; 1 minute). The power, partial pressure, and time of etching were optimized to obtain the desired size. The 1R array is formed by RIE (5 sccm Ar + 5 sccm O2 + 80 sccm CF4; Power 100 W; pressure: 200 mTorr) to transfer the treated NS pattern into the SiOx layer (Figure 7c, with average diameter of 130 nm). The NS layer was removed by sonication in toluene for 15 min.

#### 2.3 Nanopillars fabrication

Figure 8. Schematic of Deep Silicon Etch (DSE) process.

For high aspect ratio nanopillar fabrication, the Deep Si Etching (DSE) process was utilized as illustrated in Figure 8. The first etching process is aimed to expose the Si surface by Ar ion-bombardment (physical reaction) with SF<sub>6</sub> chemical reaction). The exposed Si surface is then passivated isotropically by C<sub>4</sub>F<sub>8</sub>-induced fluoro-carbon polymer deposition to limit isotropic etching in the next cycle. The main etch process is used to anisotropically bombard the bottom fluoropolymer and re-expose the Si surface to SF<sub>6</sub> chemical reactions. Then, repeating cycling of deposition and main etching.

Figure 9. Schematic of 1D-1R pillar fabrication via deep silicon etch process. The different colors in substrate represents different doping concentration. Nanospheres were removed by ultrasonic bath in toluene.

Figure 9 is the schematic for 1D-1R fabrication process flow via deep silicon etch process. The only difference between 1R and 1D-1R is the difference of substrate doping level. For 1R, the substrate is (100) N<sup>++</sup> Si wafer with resistivity of 0.001-0.005 ohm-cm. For 1D-1R, a P<sup>++</sup>/N<sup>+</sup>/N<sup>++</sup> epitaxial Si wafer is used as substrate (P<sup>++</sup>: thickness 0.3 um, Boron (B), concentration  $5\times10^{19}$  cm<sup>-3</sup>/ N<sup>+</sup>: thickness 0.6 um, Arsenic (As), concentration  $5\times10^{16}$  cm<sup>-3</sup>/ N<sup>++</sup>: substrate, Phosphorus (P), concentration  $1-7\times10^{19}$  cm<sup>-3</sup>).

#### 2.4 SEM Characterizations

Figure 10. SEM characterization for each process. (a) nanosphere deposition, (b) RIE oxygen plasma shrinks the diameter of nanospheres, (c) RIE plasma for SiO<sub>x</sub> dry etching to transfer the pattern into SiO<sub>x</sub> layer and (d) top view, cross section view and tilted view of nanopillars after deep silicon etch process. The scale bars in every images are 200nm in length.

Figure 10 shows the SEM images after several key process steps. We could see compact hexagonal pattern of nanospheres with perfect arrangement in Figure 10 (a). After the oxygen plasma treatment, the diameter of nanosphere is reduces while the good

uniformity is preserved, as shown in Figure 10 (b). In Figure 10 (c), we can clearly observe the patterned  $SiO_x$  dots underneath nanospheres with a sharp contrast. Figure 10 (d) is the final nanopillar structure. The cross section view shows the nanopillars are straight and smooth. No scallops are observed, indicating a good optimization in etch recipe.

Figure 11. Statistics of average height and diameter of fabricated nanopillars. The average pillar height is around 1300 nm and the average pillar diameter is around 130 nm.

Figure 11 shows the average height and diameter of nanopillars are 1300 nm and 130 nm, respectively, with an aspect ratio  $\sim 10:1$ .

#### **Chapter 3: Results and Discussion**

#### 3.1 Measurement setups

The electrical measurement was performed by Agilent B1500 Semiconductor Device Analyzer (Agilent Inc.). Samples were kept in a Lakeshore Cryotronics vacuum chamber with pressure lower than 1 mTorr. Bottom contact of the samples were connected to the chuck of chamber. A tungsten (W) probe tip (~10 µm radius) was used as a top electrode, directly contacting with SiO<sub>x</sub> active layer. Voltage was applied to the top electrode with the bottom electrode grounded.

#### 3.2 Results of 1R architecture

Figure 12. Double sweep forming process. The first run is soft breakdown, with compliance current fixed at 100 nA (solid line). The second run is forming process without any compliance current (dash line).

Figure 12 shows the results of an electroforming process. Here we utilized a double sweep method, with 1<sup>st</sup> sweep under fixed 100 nA compliance current and 2<sup>nd</sup> sweep without any compliance current. The purpose of soft breakdown is to avoid hard

breakdown and increase forming yield. A second forming sweep was done using forward/backward sweep, where current fluctuations are observed. During the backward sweep, the current keeps increasing and fluctuations are still present until hits a point after which the I-V curve becomes smooth, indicating a stable LRS is reached.

Figure 13. I-V characteristics for set and reset process for 1R structure samples.

The set process is a forward/backward scan without any compliance current. The current level has an abrupt change at 3 V during the forward scan. So the set voltage is around 3 V. For reset process, it is a forward scan from 0 V to 8 V. The current decrease as the voltage increases in range of 5 V to 8 V, during which the device is changed to HRS. Choosing 1 V as the reading voltage, the HRS/LRS ratio is around 50, satisfying the requirement of programming.

Figure 14. Endurance tests of 1R structure samples.

Endurance of HRS and LRS for 1R structure sample is shown in Figure 14. One order of magnitude difference in resistance between the HRS and LRS is maintained after  $10^4$  cycles. For endurance measurement, the devices were programed by applying a pulse, which is used in real-world circuit operation. For the set process, the pulse height and width are 4.5 V and 100ns. For the reset process, the height and width are 12 V and 1  $\mu$ s, respectively.

#### 3.3 Results of 1D-1R architecture

Figure 15. Characterizations and simulation of p-n Si diode used as 1D element in 1D-1R structure. Red line, blue line and black line are forward scan, reverse scan and simulation results, respectively.

For the characterizations of 1D-1R devices, the quality of diode should be checked first. Figure 15 shows the 100 cycles of nanopillars diode. The maximum current reaches 100 mA, high enough for the requirement of reset process. The reverse current is suppressed below pA regime, indicating the high quality of the diodes. The simulation was performed in standard TCAD software and the results fit well with experimental results.

Figure 16. I-V results of set and reset process for 1D-1R structure samples.

switching cycles for 1D-1R devices are shown in Figure 16. The set voltage is around 4 V and the reset voltage is in range of 6-8 V, both of which are slightly larger than those observed in 1R devices. In addition, the current change during set process is more gradual. All these may be due to the series resistance involved with insertion of diode. It is worth noting that the reverse current level is smaller than 1 pA, attributed to the integrated p-n diode.

Figure 17. Retention measurement results of multi-level operation by controlling the reset stop voltage.

As shown in Figure 17, by controlling the reset stop voltage, the HRS level can be well controlled, confirming the potential for multi-level operation. When increasing the reset stop voltage, the current level of HRS is reduced. This is attributed the length of filaments can be modulated by the reset stop voltage. For all states, no obvious degradation are observed after 10<sup>4</sup> switching cycles.

#### **Chapter 4: Conclusion and Future Work**

#### 4.1 Conclusion

We have demonstrated high density nanopillar shaped RRAM based on SiO<sub>x</sub>. Nanosphere lithography technique was used for the fabrication of nanopillars structures. SiO<sub>x</sub> served both as active memory layer and self-aligned hard mask. To solve the sneak path issue, epitaxial silicon p-n diodes were integrated vertically into nanopillars. Good resistive switching characteristics and reliability are obtained.

#### 4.2 Future work

As described in measurement setups section, all data were obtained under vacuum (< 1 mTorr). Under ambient condition, the devices would become inactive after several switching cycles. The reason is still unknown. On possible mechanism is that the resistive switching behavior comes from the mobile proton in SiO<sub>x</sub>, when exposed in an oxygen rich environment, proton will be oxidized, resulting in the loss of capability of switching. A similar phenomena has been observed as early as in 1997, in *Nature* [57].

The future work will focus on how to efficiently protect the active device area from the oxidation environment. One possible way is to use high quality Si<sub>3</sub>N<sub>4</sub>, grown by plasma-enhanced-atomic-layer-deposition (PEALD), as the protection layer.

#### **Bibliography**

- [1] L. O. Chua, "Memristor-the missing circuit element," *IEEE Transactions on Circuit Theory*, vol. 18, pp. 507, 1971.

- [2] D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, "The missing memristor found," *Nature*, vol. 453, pp. 80, 2008.

- [3] T. W. Hickmott, "Low frequency nagative resistance in thin anodic oxide films," *Journal of Applied Physics*, vol. 33, pp. 2669, 1962.

- [4] J. F. Gibbons and W. E. Beadle, "Switching properties of thin NiO films," *Solid-State Electronics*, vol. 7, pp. 785, 1964.

- [5] Dearnale.G, A. M. Stoneham, and D. V. Morgan, "Electrical phenomena in amorphous oxide films," *Reports on Progress in Physics*, vol. 33, pp. 1129, 1970.

- [6] J. G. Simmons, "Conduction in thin dielectric films," *Journal of Physics D-Applied Physics*, vol. 4, pp. 613, 1971.

- [7] I. Baek, M. Lee, S. Seo, M.-J. Lee, D. Seo, D.-S. Suh, *et al.*, "Highly scalable nonvolatile resistive memory using simple binary oxide driven by asymmetric unipolar voltage pulses," in *IEEE International Electron Devices Meeting*, pp. 587 2004

- [8] V. Meunier, S. V. Kalinin, and B. G. Sumpter, "Nonvolatile memory elements based on the intercalation of organic molecules inside carbon nanotubes," *Physical review letters*, vol. 98, p. 056401, 2007.

- [9] M. D. Pickett, G. Medeiros-Ribeiro, and R. S. Williams, "A scalable neuristor built with Mott memristors," *Nat Mater*, vol. 12, pp. 114, 2012.

- [10] Y. Kaneko, Y. Nishitani, M. Ueda, E. Tokumitsu, and E. Fujii, "A 60 nm channel length ferroelectric-gate field-effect transistor capable of fast switching and multilevel programming," *Applied Physics Letters*, vol. 99, p. 182902, 2011.

- [11] J. Muller, E. Yurchuk, T. Schlosser, J. Paul, R. Hoffmann, S. Muller, *et al.*, "Ferroelectricity in HfO 2 enables nonvolatile data storage in 28 nm HKMG," in *Symposium on VLSI Technology*, pp. 25, 2012

- [12] S. Sakai and R. Ilangovan, "Metal-ferroelectric-insulator-semiconductor memory FET with long retention and high endurance," *IEEE Electron Device Letters*, vol. 25, pp. 369, 2004.

- [13] W. Fu, Z. Xu, X. Bai, C. Gu, and E. Wang, "Intrinsic memory function of carbon nanotube-based ferroelectric field-effect transistor," *Nano letters*, vol. 9, pp. 921, 2009.

- [14] Z. Wen, C. Li, D. Wu, A. Li, and N. Ming, "Ferroelectric-field-effect-enhanced electroresistance in metal/ferroelectric/semiconductor tunnel junctions," *Nature materials*, vol. 12, pp. 617, 2013.

- [15] M. Reed, J. Chen, A. Rawlett, D. Price, and J. Tour, "Molecular random access memory cell," *Applied physics letters*, vol. 78, pp. 3735-3737, 2001.

- [16] J. J. Kim, B. Cho, K. S. Kim, T. Lee, and G. Y. Jung, "Electrical Characterization of Unipolar Organic Resistive Memory Devices Scaled Down by a Direct Metal -Transfer Method," *Advanced Materials*, vol. 23, pp. 2104, 2011.

- [17] Y. Kuang, R. Huang, Y. Tang, W. Ding, L. Zhang, and Y. Wang, "Flexible single-component-polymer resistive memory for ultrafast and highly compatible nonvolatile memory applications," *IEEE Electron Device Letters*, vol. 31, pp. 758, 2010.

- [18] M. Fujimoto, H. Koyama, M. Konagai, Y. Hosoi, K. Ishihara, S. Ohnishi, *et al.*, "TiO2 anatase nanolayer on TiN thin film exhibiting high-speed bipolar resistive switching," *Applied Physics Letters*, vol. 89, pp. 223509, 2006.

- [19] C.-Y. Lin, C.-Y. Wu, C.-Y. Wu, C. Hu, and T.-Y. Tsenga, "Bistable resistive switching in Al2O3 memory thin films," *Journal of the Electrochemical Society*, vol. 154, pp. G189, 2007.

- [20] C.-Y. Lin, C.-Y. Wu, C.-Y. Wu, T.-C. Lee, F.-L. Yang, C. Hu, *et al.*, "Effect of top electrode material on resistive switching properties of ZrO2 film memory devices," *IEEE Electron Device Letters*, vol. 28, pp. 366, 2007.

- [21] Y. Sato, K. Kinoshita, M. Aoki, and Y. Sugiyama, "Consideration of switching mechanism of binary metal oxide resistive junctions using a thermal reaction model," *Applied Physics Letters*, vol. 90, Jan 15 2007.

- [22] R. Waser and M. Aono, "Nanoionics-based resistive switching memories," *Nature Materials*, vol. 6, pp. 833, 2007.

- [23] W.-Y. Chang, Y.-C. Lai, T.-B. Wu, S.-F. Wang, F. Chen, and M.-J. Tsai, "Unipolar resistive switching characteristics of ZnO thin films for nonvolatile memory applications," *Applied Physics Letters*, vol. 92, pp. 022110, 2008.

- [24] J. Y. Son and Y. H. Shin, "Direct observation of conducting filaments on resistive switching of NiO thin films," *Applied Physics Letters*, vol. 92, pp. 222106, 2008.

- [25] W.-Y. Chang, K.-J. Cheng, J.-M. Tsai, H.-J. Chen, F. Chen, M.-J. Tsai, *et al.*, "Improvement of resistive switching characteristics in TiO2 thin films with embedded Pt nanocrystals," *Applied Physics Letters*, vol. 95, pp. 042104, 2009.

- [26] Y. S. Chen, H. Y. Lee, P. S. Chen, P. Y. Gu, C. W. Chen, W. P. Lin, *et al.*, "Highly Scalable Hafnium Oxide Memory with Improvements of Resistive Distribution and Read Disturb Immunity," in *IEEE International Electron Devices Meeting*, pp. 1, 2009.

- [27] H. Y. Lee, P.-S. Chen, T.-Y. Wu, Y. S. Chen, F. Chen, C.-C. Wang, *et al.*, "HfOx Bipolar Resistive Memory With Robust Endurance Using AlCu as Buffer Electrode," *IEEE Electron Device Letters*, vol. 30, pp. 703, 2009.

- [28] U. Russo, D. Ielmini, C. Cagli, and A. L. Lacaita, "Self-Accelerated Thermal Dissolution Model for Reset Programming in Unipolar Resistive-Switching Memory (RRAM) Devices," *IEEE Transactions on Electron Devices*, vol. 56, pp. 193, 2009.

- [29] Y. Sato, K. Tsunoda, M. Aoki, and Y. Sugiyama, "Novel Circuitry Configuration with Paired-Cell Erase Operation for High-Density 90-nm Embedded Resistive Random Access Memory," *Japanese Journal of Applied Physics*, vol. 48, pp. 04C075, 2009.

- [30] X. Sun, B. Sun, L. Liu, N. Xu, X. Liu, R. Han, *et al.*, "Resistive Switching in CeOx Films for Nonvolatile Memory Application," *IEEE Electron Device Letters*, vol. 30, pp. 334, 2009.

- [31] M. K. Yang, J.-W. Park, T. K. Ko, and J.-K. Lee, "Bipolar resistive switching behavior in Ti/MnO2/Pt structure for nonvolatile memory devices," *Applied Physics Letters*, vol. 95, pp. 042105, 2009.

- [32] W.-Y. Chang, C.-A. Lin, J.-H. He, and T.-B. Wu, "Resistive switching behaviors of ZnO nanorod layers," *Applied Physics Letters*, vol. 96, pp. 242109, 2010.

- [33] L. Goux, Y. Y. Chen, L. Pantisano, X. P. Wang, G. Groeseneken, M. Jurczak, *et al.*, "On the Gradual Unipolar and Bipolar Resistive Switching of TiN\HfO2\Pt Memory Systems," *Electrochemical and Solid State Letters*, vol. 13, pp. G54, 2010.

- [34] D.-H. Kwon, K. M. Kim, J. H. Jang, J. M. Jeon, M. H. Lee, G. H. Kim, *et al.*, "Atomic structure of conducting nanofilaments in TiO2 resistive switching memory," *Nature Nanotechnology*, vol. 5, pp. 148, 2010.

- [35] K. Nagashima, T. Yanagida, K. Oka, M. Taniguchi, T. Kawai, J.-S. Kim, *et al.*, "Resistive Switching Multistate Nonvolatile Memory Effects in a Single Cobalt Oxide Nanowire," *Nano Letters*, vol. 10, pp. 1359, 2010.

- [36] M. Wang, W. J. Luo, Y. L. Wang, L. M. Yang, W. Zhu, P. Zhou, *et al.*, "A Novel Cu(x)Si(y)O Resistive Memory in Logic Technology with Excellent Data Retention and Resistance Distribution for Embedded Applications," in *Symposium on VISI Technology*, pp. 89, 2010.

- [37] G. Bersuker, D. C. Gilmer, D. Veksler, P. Kirsch, L. Vandelli, A. Padovani, *et al.*, "Metal oxide resistive memory switching mechanism based on conductive filament properties," *Journal of Applied Physics*, vol. 110, pp. 124518, 2011.

- [38] S. Yu, Y. Wu, R. Jeyasingh, D. Kuzum, and H. S. P. Wong, "An Electronic Synapse Device Based on Metal Oxide Resistive Switching Memory for Neuromorphic Computation," *IEEE Transactions on Electron Devices*, vol. 58, pp. 2729, 2011.

- [39] S. Yu, Y. Wu, and H. S. P. Wong, "Investigating the switching dynamics and multilevel capability of bipolar metal oxide resistive switching memory," *Applied Physics Letters*, vol. 98, pp. 103514, 7 2011.

- [40] International Technology Roadmap for Semiconductors, 2013 Edition, Internet: http://www.itrs.net/Links/2013ITRS/Summary2013.htm

- [41] C.-L. Tsai, F. Xiong, E. Pop, and M. Shim, "Resistive random access memory enabled by carbon nanotube crossbar electrodes," *ACS Nano*, vol. 7, pp. 5360, 2013.

- [42] H. S. P. Wong, H. Y. Lee, S. M. Yu, Y. S. Chen, Y. Wu, P. S. Chen, et al., "Metal-Oxide RRAM," *Proceedings of the IEEE*, vol. 100, pp. 1951, 2012.

- [43] D. C. Kim, M. J. Lee, S. E. Ahn, S. Seo, J. C. Park, I. K. Yoo, *et al.*, "Improvement of resistive memory switching in NiO using IrO2," *Applied Physics Letters*, vol. 88, pp. 232106, 2006.

- [44] K. Tsunoda, K. Kinoshita, H. Noshiro, Y. Yarnazaki, T. Iizuka, Y. Ito, *et al.*, "Low power and high speed switching of Ti-doped NiOReRAM under the unipolar voltage source of less than 3 V," in *IEEE International Electron Devices Meeting*, pp. 767, 2007.

- [45] S. I. Kim, J. H. Lee, Y. W. Chang, S. S. Hwang, and K.-H. Yoo, "Reversible resistive switching behaviors in NiO nanowires," *Applied Physics Letters*, vol. 93, pp. 033503,2008.

- [46] C. Yoshida, K. Kinoshita, T. Yamasaki, and Y. Sugiyama, "Direct observation of oxygen movement during resistance switching in NiO/Pt film," *Applied Physics Letters*, vol. 93, pp. 042106, 2008.

- [47] G.-H. Buh, I. Hwang, and B. H. Park, "Time-dependent electroforming in NiO resistive switching devices," *Applied Physics Letters*, vol. 95, pp. 142101, 2009.

- [48] J. S. Choi, J. S. Kim, I. R. Hwang, S. H. Hong, S. H. Jeon, S. O. Kang, *et al.*, "Different resistance switching behaviors of NiO thin films deposited on Pt and SrRuO3 electrodes," *Applied Physics Letters*, vol. 95, pp. 022109, 2009.

- [49] L. Goux, J. G. Lisoni, X. P. Wang, M. Jurczak, and D. J. Wouters, "Optimized Ni Oxidation in 80-nm Contact Holes for Integration of Forming-Free and Low-Power Ni/NiO/Ni Memory Cells," *IEEE Transactions on Electron Devices*, vol. 56, pp. 2363, 2009.

- [50] K. Oka, T. Yanagida, K. Nagashima, H. Tanaka, and T. Kawai, "Nonvolatile Bipolar Resistive Memory Switching in Single Crystalline NiO Heterostructured Nanowires," *Journal of the American Chemical Society*, vol. 131, pp. 3434, 2009.

- [51] H. D. Lee, B. Magyari-Kope, and Y. Nishi, "Model of metallic filament formation and rupture in NiO for unipolar switching," *Physical Review B*, vol. 81, pp. 193202, 2010.

- [52] K. M. Kim, B. J. Choi, B. W. Koo, S. Choi, D. S. Jeong, and C. S. Hwang, "Resistive switching in Pt/Al2O3/TiO2/Ru stacked structures," *Electrochemical and Solid State Letters*, vol. 9, pp. G343, 2006.

- [53] Y. Wu, B. Lee, and H. S. P. Wong, "Al2O3-Based RRAM Using Atomic Layer Deposition (ALD) With 1-mu A RESET Current," *IEEE Electron Device Letters*, vol. 31, pp. 1449, 2010.

- [54] N. Xu, L. Liu, X. Sun, X. Liu, D. Han, Y. Wang, *et al.*, "Characteristics and mechanism of conduction/set process in TiN/ZnO/Pt resistance switching random-access memories," *Applied Physics Letters*, vol. 92, pp. 232112, 2008.

- [55] N. Xu, L. F. Liu, X. Sun, C. Chen, Y. Wang, D. D. Han, *et al.*, "Bipolar switching behavior in TiN/ZnO/Pt resistive nonvolatile memory with fast switching and long retention," *Semiconductor Science and Technology*, vol. 23, 2008.

- [56] S.-M. Lin, J.-S. Huang, W.-C. Chang, T.-C. Hou, H.-W. Huang, C.-H. Huang, *et al.*, "Single-Step Formation of ZnO/ZnWOx Bilayer Structure via Interfacial Engineering for High Performance and Low Energy Consumption Resistive Memory with Controllable High Resistance States," *ACS Applied Materials & Interfaces*, vol. 5, pp. 7831, 2013.

- [57] K. Vanheusden, W. L. Warren, R. A. B. Devine, D. M. Fleetwood, J. R. Schwank, M. R. Shaneyfelt, *et al.*, "Non-volatile memory device based on mobile protons in SiO2 thin films," *Nature*, vol. 386, pp. 587, 1997.

- [58] R. G. Gateru, J. O. Orwa, and J. M. Shannon, "Polarity-dependent forming in ion bombarded amorphous silicon memory devices," *Journal of Applied Physics*, vol. 97, pp. 024506, 2005.

- [59] S. H. Jo, K.-H. Kim, and W. Lu, "Programmable Resistance Switching in Nanoscale Two-Terminal Devices," *Nano Letters*, vol. 9, pp. 496, 2008.

- [60] J. Yao, L. Zhong, D. Natelson, and J. M. Tour, "Etching-dependent reproducible memory switching in vertical SiO2 structures," *Applied Physics Letters*, vol. 93, pp. 253101, 2008.

- [61] S. H. Jo, K. H. Kim, and W. Lu, "High-Density Crossbar Arrays Based on a Si Memristive System," *Nano Letters*, vol. 9, pp. 870, 2009.

- [62] J. Yao, L. Zhong, Z. X. Zhang, T. He, Z. Jin, P. J. Wheeler, *et al.*, "Resistive Switching in Nanogap Systems on SiO2 Substrates," *Small*, vol. 5, pp. 2910, 2009.

- [63] J. Yao, Z. Z. Sun, L. Zhong, D. Natelson, and J. M. Tour, "Resistive Switches and Memories from Silicon Oxide," *Nano Letters*, vol. 10, pp. 4105, 2010.

- [64] B. J. Choi, A. B. K. Chen, X. Yang, and I. W. Chen, "Purely Electronic Switching with High Uniformity, Resistance Tunability, and Good Retention in Pt-Dispersed SiO2 Thin Films for ReRAM," *Advanced Materials*, vol. 23, pp. 3847, 2011.

- [65] J. Yao, L. Zhong, D. Natelson, and J. M. Tour, "Silicon Oxide: A Non-innocent Surface for Molecular Electronics and Nanoelectronics Studies," *Journal of the American Chemical Society*, vol. 133, pp. 941, 2 2011.

- [66] M. Cavallini, Z. Hemmatian, A. Riminucci, M. Prezioso, V. Morandi, and M. Murgia, "Regenerable Resistive Switching in Silicon Oxide Based Nanojunctions," *Advanced Materials*, vol. 24, pp. 1197, 2 2012.

- [67] Y.-F. Chang, P.-Y. Chen, B. Fowler, Y.-T. Chen, F. Xue, Y. Wang, *et al.*, "Understanding the resistive switching characteristics and mechanism in active SiOx-based resistive switching memory," *Journal of Applied Physics*, vol. 112, pp. 233301, 2012.

- [68] Y. T. Chen, B. Fowler, Y. Z. Wang, F. Xue, F. Zhou, Y. F. Chang, *et al.*, "Tristate Operation in Resistive Switching of SiO2 Thin Films," *IEEE Electron Device Letters*, vol. 33, pp. 1702, 2012.

- [69] Y. Wang, Y.-T. Chen, F. Xue, F. Zhou, Y.-F. Chang, B. Fowler, *et al.*, "Memory switching properties of e-beam evaporated SiOx on N++ Si substrate," *Applied Physics Letters*, vol. 100, pp. 083502, 2012.

- [70] Y. F. Chang, L. Ji, Y. Z. Wang, P. Y. Chen, F. Zhou, F. Xue, *et al.*, "Investigation of edge- and bulk-related resistive switching behaviors and backward-scan effects in SiOx-based resistive switching memory," *Applied Physics Letters*, vol. 103, pp. 193508, 2013.

- [71] Y. T. Chen, T. C. Chang, P. C. Yang, J. J. Huang, H. C. Tseng, H. C. Huang, *et al.*, "Improvement of Resistive Switching Characteristics by Thermally Assisted Forming Process for SiO2-Based Structure," *IEEE Electron Device Letters*, vol. 34, pp. 226, 2013.

- [72] B. J. Choi, A. C. Torrezan, K. J. Norris, F. Miao, J. P. Strachan, M.-X. Zhang, et al., "Electrical Performance and Scalability of Pt Dispersed SiO2 Nanometallic Resistance Switch," *Nano Letters*, vol. 13, pp. 3213, 2013.

- [73] C. He, J. Li, X. Wu, P. Chen, J. Zhao, K. Yin, *et al.*, "Tunable Electroluminescence in Planar Graphene/SiO2 Memristors," *Advanced Materials*, vol. 25, pp. 5593, 2013.

- [74] C. Li, H. Jiang, and Q. Xia, "Low voltage resistive switching devices based on chemically produced silicon oxide," *Applied Physics Letters*, vol. 103, pp. 062104, 2013.

- [75] A. Mehonic, A. Vrajitoarea, S. Cueff, S. Hudziak, H. Howe, C. Labbe, *et al.*, "Quantum Conductance in Silicon Oxide Resistive Memory Devices," *Scientific Reports*, vol. 3, pp. 2708, 2013.

- [76] H. C. Tseng, T. C. Chang, Y. C. Wu, S. W. Wu, J. J. Huang, Y. T. Chen, *et al.*, "Impact of Electroforming Current on Self-Compliance Resistive Switching in an ITO/Gd:SiOx/TiN Structure," *IEEE Electron Device Letters*, vol. 34, pp. 858, 2013.

- [77] G. Wang, A. C. Lauchner, J. Lin, D. Natelson, K. V. Palem, and J. M. Tour, "High-performance and low-power rewritable SiOx 1 kbit one diode-one resistor crossbar memory array," *Advanced Materials*, vol. 25, pp. 4789, 2013.

- [78] Y. Z. Wang, B. Fowler, F. Zhou, Y. F. Chang, Y. T. Chen, F. Xue, et al., "Effects of sidewall etching on electrical properties of SiOx resistive random access memory," *Applied Physics Letters*, vol. 103, pp. 253105, 2013.

- [79] X. Yang, B. J. Choi, A. B. K. Chen, and I. W. Chen, "Cause and Prevention of Moisture-Induced Degradation of Resistance Random Access Memory Nanodevices," ACS Nano, vol. 7, pp. 2302, 2013.

- [80] G. Wang, A.-R. O. Raji, J.-H. Lee, and J. M. Tour, "Conducting-Interlayer SiOx Memory Devices on Rigid and Flexible Substrates," ACS Nano, vol. 8, pp. 1410, 2014.

- [81] G. Wang, Y. Yang, J.-H. Lee, V. Abramova, H. Fei, G. Ruan, et al., "Nanoporous Silicon Oxide Memory," *Nano Letters*, vol. 24, pp.4694, 2014.

- [82] Y. Wang, K. Chen, X. Qian, Z. Fang, W. Li, and J. Xu, "The x dependent two kinds of resistive switching behaviors in SiOx films with different x component," *Applied Physics Letters*, vol. 104, pp. 012112, 2014.

- [83] S. Brivio, G. Tallarida, D. Perego, S. Franz, D. Deleruyelle, C. Muller, *et al.*, "Low-power resistive switching in Au/NiO/Au nanowire arrays," *Applied Physics Letters*, vol. 101, pp. 223510, 2012.

- [84] K. Oka, T. Yanagida, K. Nagashima, M. Kanai, T. Kawai, J.-S. Kim, et al., "Spatial Nonuniformity in Resistive-Switching Memory Effects of NiO," *Journal of the American Chemical Society*, vol. 133, pp. 12482, 2011.

- [85] G.-S. Park, X.-S. Li, D.-C. Kim, R.-J. Jung, M.-J. Lee, and S. Seo, "Observation of electric-field induced Ni filament channels in polycrystalline NiO(x) film," *Applied Physics Letters*, vol. 91, pp. 222103, 2007.

- [86] E. Mikheev, B. D. Hoskins, D. B. Strukov, and S. Stemmer, "Resistive switching and its suppression in Pt/Nb:SrTiO3 junctions," *Nat Commun*, vol. 5, 2014.

- [87] H. Lee, H. Kim, T. N. Van, D.-W. Kim, and J. Y. Park, "Nanoscale Resistive Switching Schottky Contacts on Self-Assembled Pt Nanodots on SrTiO3," *ACS Applied Materials & Interfaces*, vol. 5, pp. 11668, 2013.

- [88] M. Janousch, G. I. Meijer, U. Staub, B. Delley, S. F. Karg, and B. P. Andreasson, "Role of oxygen vacancies in Cr-doped SrTiO3 for resistance-change memory," *Advanced Materials*, vol. 19, pp. 2232, 2007.

- [89] K. Szot, W. Speier, G. Bihlmayer, and R. Waser, "Switching the electrical resistance of individual dislocations in single-crystalline SrTiO3," *Nature Materials*, vol. 5, pp. 312, 2006.

- [90] Y. Watanabe, J. G. Bednorz, A. Bietsch, C. Gerber, D. Widmer, A. Beck, *et al.*, "Current-driven insulator-conductor transition and nonvolatile memory in chromium-doped SrTiO3 single crystals," *Applied Physics Letters*, vol. 78, pp. 3738, 2001.

- [91] B. Choi, D. Jeong, S. Kim, C. Rohde, S. Choi, J. Oh, *et al.*, "Resistive switching mechanism of TiO2 thin films grown by atomic-layer deposition," *Journal of Applied Physics*, vol. 98, pp. 033715, 2005.

- [92] A. Sawa, "Resistive switching in transition metal oxides," *Materials today*, vol. 11, pp. 28, 2008.

- [93] T. Sakamoto, H. Sunamura, H. Kawaura, T. Hasegawa, T. Nakayama, and M. Aono, "Nanometer-scale switches using copper sulfide," *Applied physics letters*, vol. 82, pp. 3032, 2003.

- [94] C. Schindler, S. P. Thermadam, R. Waser, and M. N. Kozicki, "Bipolar and Unipolar Resistive Switching in Cu-Doped SiO2," *IEEE Transactions on Electron Devices*, vol. 54, pp. 2762, 2007.

- [95] C. Schindler, S. C. P. Thermadam, R. Waser, and M. N. Kozicki, "Bipolar and unipolar resistive switching in Cu-doped SiO2," *IEEE Transactions on Electron Devices*, vol. 54, pp. 2762, 2007.

- [96] C. Schindler, M. Weides, M. N. Kozicki, and R. Waser, "Low current resistive switching in Cu-SiO2 cells," *Applied Physics Letters*, vol. 92, pp. 122910, 2008.

- [97] S. Tappertzhofen, I. Valov, T. Tsuruoka, T. Hasegawa, R. Waser, and M. Aono, "Generic relevance of counter charges for cation-based nanoscale resistive switching memories," *ACS Nano*, vol. 7, pp. 6396, 2013.

- [98] J. Yao, L. Zhong, D. Natelson, and J. M. Tour, "In situ imaging of the conducting filament in a silicon oxide resistive switch," *Scientific Reports*, vol. 2, pp. 242, 2012.

Vita

Li Ji received the B.S. degree in Microelectronics from Xiamen University in

China, in 2011. He entered the University of Texas at Austin in 2011 as a graduate research

assistant in Nanoscale Characterization and Devices Laboratory, supervised by Prof.

Edward T. Yu.

Permanent email address: nmgjili@utexas.edu & nmgjili@gmail.com

This thesis was typed by Li Ji.

32