Copyright

by

Renee Elizabeth Nieh

2002

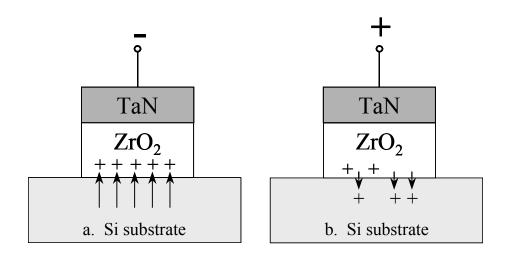

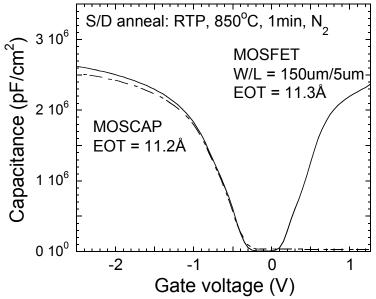

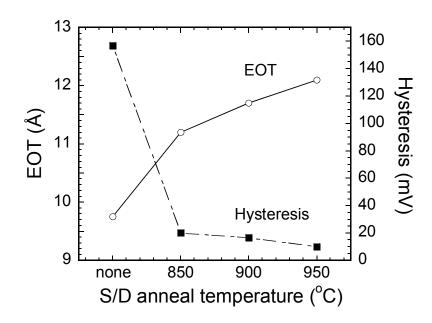

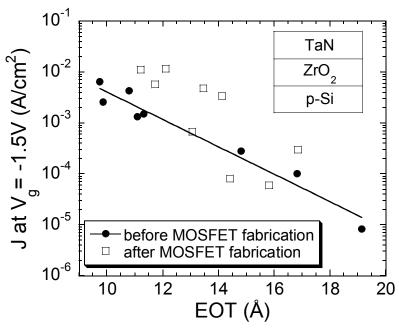

## The Dissertation Committee for Renee Elizabeth Nieh Certifies that this is the approved version of the following dissertation:

# An evaluation of the electrical, material, and reliability characteristics and process viability of $ZrO_2$ and $ZrO_xN_y$ for future generation MOS gate dielectric

| Committee:              |

|-------------------------|

|                         |

| Jack C. Lee, Supervisor |

| Russ Dupuis             |

|                         |

| Dean Neikirk            |

| Mircea Driga            |

| V: l., V., !!           |

| Vidya Kaushik           |

# An evaluation of the electrical, material, and reliability characteristics and process viability of $ZrO_2$ and $ZrO_xN_y$ for future generation MOS gate dielectric

by

Renee Elizabeth Nieh, B.S., M.S.

#### **Dissertation**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

**Doctor of Philosophy**

The University of Texas at Austin

August 2002

## Acknowledgements

First, I would like to thank my husband Ryan and my family for providing me with the love and support I needed to earn this degree. Mom and Dad – thanks for instilling in me the appreciation for education and encouraging me in all my endeavors. Ryan – thanks for being my best friend, for keeping me so happy, and filling our home with love and laughter. To my brother Leon, thanks for showing me that anything can be accomplished with hard work and perseverance. To my in-laws, Gary, Cheri, Jennifer, and Lori – thanks for your friendship and patience.

Of course, none of this would be possible without my wonderful research group composed of Professor Jack Lee and the current grad students – Sundar, Jeong, Katsu, Chang Seok, Rino, Hag-Ju, Akbar, and Young Hee. Thanks also to the past gate dielectrics group members Byoung Hun, Laegu, Yongjoo, Easwar, Aaron, Keith, and especially Wen-Jie who set such a good example for the rest of us. I also enjoyed working with the past ferroelectrics group members: Cedric, Tony, Balu, Patrick, Razak, and Eric. I really appreciate all the helpful discussions and support of the past and current group members, and the teamwork it took for us all to get our New KJL processing done! To Dr. Lee, thanks for letting us have so much freedom in our work, but also guiding us when we needed help – it was the perfect balance.

Thanks also to the wonderful MER support staff. Without the help of the clean room technicians – Bill, Jesse, and Steve – none of us would ever get any research done! I cannot describe how much I appreciated all their help, patience, and

efficiency at repairing all the equipment. To Brenda, thanks for keeping the clean room clean and for your friendship. As for the administrative staff, Carol and Kay were amazingly efficient at taking care of any problems or travel arrangements in a friendly manner. Thanks to James, William, and David for keeping the MER facilities running smoothly and safely. I would also like to express my gratitude to my committee members: Dr. Russ Dupuis, Dr. Dean Neikirk, Dr. Mircea Driga, and Dr. Vidya Kaushik for their time and careful consideration of my work.

As for assistance with material analysis, thanks go to the incredible TEM lab at Motorola Austin and SEMATECH, José for the XPS analysis, and Chang Seok for the XRD analysis. Also, I enjoyed my internship at Motorola and all the friendly people I met while working there – Bich-Yen, Vidya, Bruce, Michael, and Murali.

For the fellowships that kept me funded for the past five years, I thank UT-Austin, the ECE department, Cockrell Foundation, Intel, and GTE. Thanks also to Texas Advanced Technology Program, SRC/SEMATECH, Cypress Semiconductor, Intel, and Matsushita Electronics for funding our research.

Finally, thanks to all my friends who help to keep me sane when the going got rough – Susan and Sheryl – the best roommate/suitemate a girl could ask for, Bao for his constant stream of thoughtful and supportive emails, my MER friends – Mike, Xin, Xiangdong, Yang-Yu, Songjoo, Chonghoo, and Tat – and to the folks at the LIPS lab – Dave, Cheryl, Karl, Anuj, Stacy, Jason, Joon, Kyoung, Scott, Austin, Lisa, Matt, Sarah, Dung, Andrea, Tom, Haidong, Steve, and Christine – for all those fun dinners, trips, movies, and games.

An evaluation of the electrical, material, and reliability characteristics and process viability of  $ZrO_2$  and  $ZrO_xN_y$  for future generation MOS gate dielectric

Publication No. \_\_\_\_\_

Renee Elizabeth Nieh, Ph.D. The University of Texas at Austin, 2002

Supervisor: Jack C. Lee

Over the past decades, continuing advancements in processes and tools and the introduction of new materials have facilitated the rapid downscaling of metal-oxide-semiconductor (MOS) technology. The 90 nm technology node and beyond will face one of the toughest challenges of the semiconductor industry – the replacement of conventional silicon dioxide (SiO<sub>2</sub>) gate dielectric with a high-k dielectric material. SiO<sub>2</sub> has been used as the gate oxide since the inception of the MOSFET, but is reaching its physical scaling limits (~10-15Å) due to excessive gate leakage current and reliability issues. High-k materials are required to reduce leakage current while maintaining a low equivalent oxide thickness (EOT). However, the integration of high-k dielectrics into the MOS process will be a serious challenge.

One promising high-k candidate is zirconium oxide ( $ZrO_2$ ) since it is has demonstrated thermal stability on Si, a dielectric constant ~20, a bandgap of 5.8 eV, low EOT (= 10Å), and bw gate leakage. In this research, sputter-deposited  $ZrO_2$  and

nitrogen-incorporated  $ZrO_2$  ( $ZrO_xN_y$ ) were evaluated in terms of electrical, material, and reliability characteristics to determine their viability as high-k gate dielectrics. Initially, platinum-gated MOS capacitors were studied to optimize the  $ZrO_2$  deposition process and demonstrate low EOT (8.2Å) and low leakage. Unfortunately, both  $ZrO_2$  and  $ZrO_xN_y$  were found to be incompatible with the polysilicon gate electrode process due to the formation of Zr-silicide and consequently, high leakage. However, dual metal gate electrodes will eventually replace polysilicon because of the polysilicon depletion effect.

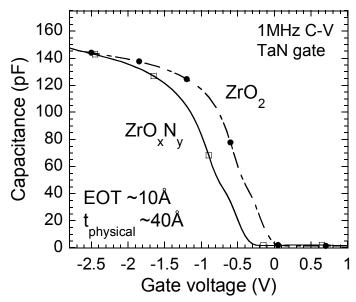

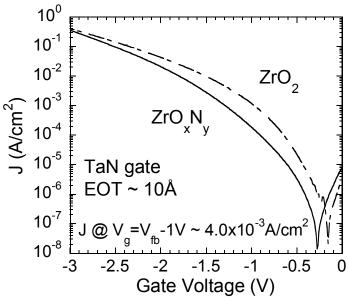

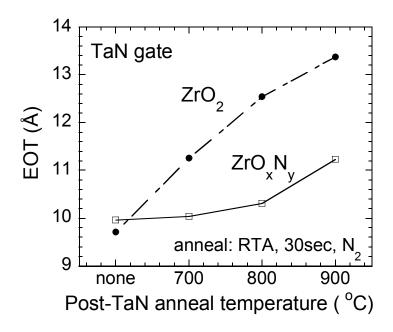

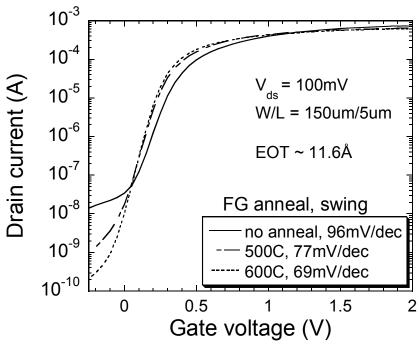

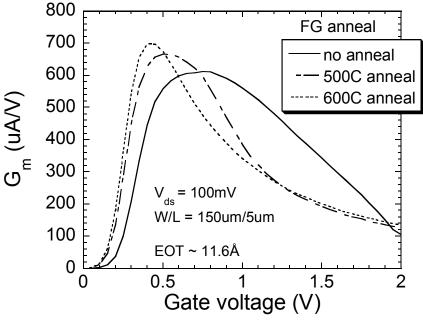

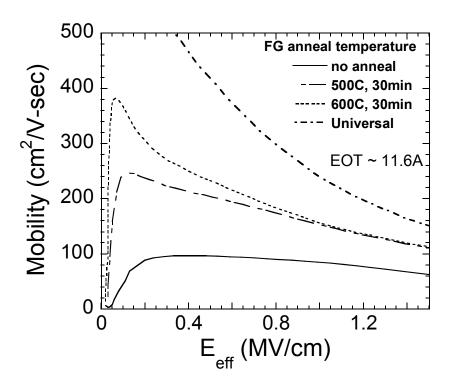

Tantalum nitride (TaN) is a promising NMOS metal gate candidate due to its thermal stability and low resistivity. Both TaN-gated MOS capacitors and self-aligned transistors using ZrO<sub>2</sub> and ZrO<sub>x</sub>N<sub>y</sub> were fabricated to demonstrate process viability and characterized to yield low EOT (9.5Å), low leakage, negligible frequency dispersion, low C-V hysteresis, good thermal stability, and well behaved transistor characteristics. In addition, a high temperature (500-600°C) forming gas anneal was found to improve mobility, subthreshold swing, and transconductance. Overall, ZrO<sub>2</sub> and ZrO<sub>x</sub>N<sub>y</sub> have demonstrated extremely promising electrical, material, and reliability characteristics as well as process viability and require further investigation as potential high-k gate dielectrics.

# **Table of Contents**

| Chapter 1    | Introd                                          | uction and Background                                                                              | 1  |  |  |

|--------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------|----|--|--|

| 1.1          | Challe                                          | enges to Moore's law: 90 nm and beyond                                                             | 1  |  |  |

| 1.2          | Scaling limits of SiO <sub>2</sub>              |                                                                                                    |    |  |  |

| 1.3          | Motiv                                           | ation for various high-k gate dielectric candidates                                                | 6  |  |  |

|              | 1.3.1                                           | Moderate high-k materials: Oxynitrides and Si <sub>3</sub> N <sub>4</sub>                          | 7  |  |  |

|              | 1.3.2                                           | Ultra high-k: Barium Strontium Titanate (BST)                                                      | 7  |  |  |

|              | 1.3.3                                           | Mid-range high-k: Ta <sub>2</sub> O <sub>5</sub> , TiO <sub>2</sub> , BeO, MgO, HfO <sub>2</sub> , |    |  |  |

|              |                                                 | and ZrO <sub>2</sub>                                                                               | 10 |  |  |

|              | 1.3.4                                           | Requirements for high-k dielectrics                                                                | 11 |  |  |

| 1.4          | Motivation for ZrO <sub>2</sub> gate dielectric |                                                                                                    |    |  |  |

|              | 1.4.1                                           | ZrO <sub>2</sub> material properties.                                                              | 13 |  |  |

| 1.5          | Outline                                         | e                                                                                                  | 15 |  |  |

| 1.6          | Refere                                          | nces                                                                                               | 17 |  |  |

|              |                                                 |                                                                                                    |    |  |  |

| Chapter 2    | ZrO <sub>2</sub> I                              | Process Optimization and Initial MOSCAP                                                            |    |  |  |

| $(Pt/ZrO_2)$ | charact                                         | erization                                                                                          | 21 |  |  |

| 2.1          | Motiv                                           | ation                                                                                              | 21 |  |  |

| 2.2          | Proces                                          | ss optimization                                                                                    | 22 |  |  |

|              | 2.2.1                                           | Pt/ZrO <sub>2</sub> /Si MOSCAP process flow and measurement                                        | 22 |  |  |

|              | 2.2.2                                           | Oxidation of Zr                                                                                    | 25 |  |  |

|              | 2.2.3                                           | Zr deposition process optimization.                                                                | 26 |  |  |

|              | 2.2.4                                           | PDA process optimization.                                                                          | 29 |  |  |

| 2.3          | Basic                                           | ZrO <sub>2</sub> characteristics.                                                                  | 33 |  |  |

|              | 2.3.1                                           | Interfacial layer                                                                                  | 33 |  |  |

|              | 2.3.2                                           | ZrO <sub>2</sub> materials characteristics.                                                        | 36 |  |  |

|              | 2.3.3                                           | Pt/ZrO <sub>2</sub> MOSCAP characteristics                                                         | 38 |  |  |

| 2.4       | Summary           |                                                                                   |    |  |  |  |

|-----------|-------------------|-----------------------------------------------------------------------------------|----|--|--|--|

| 2.5       | Refere            | ences                                                                             | 44 |  |  |  |

|           |                   |                                                                                   |    |  |  |  |

| Chapter 3 | Polysi            | licon gate electrode on ZrO <sub>2</sub>                                          | 47 |  |  |  |

| 3.1       | Motiv             | ation                                                                             | 47 |  |  |  |

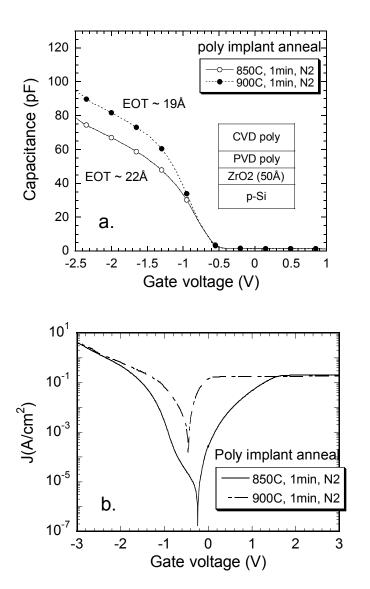

| 3.2       | Poly/Z            | ZrO <sub>2</sub> and Poly/ZrO <sub>x</sub> N <sub>y</sub> NMOSCAP characteristics | 49 |  |  |  |

|           | 3.2.1             | Poly/ZrO <sub>2</sub> /Si MOSCAP process flow and measurement                     | 49 |  |  |  |

|           | 3.2.2             | ZrO <sub>2</sub> incompatibility with the poly process                            | 50 |  |  |  |

|           | 3.2.3             | Possible solutions to the incompatibility of ZrO <sub>2</sub> with poly           | 53 |  |  |  |

|           | 3.2.4             | ZrO <sub>x</sub> N <sub>y</sub> with poly gate                                    | 55 |  |  |  |

| 3.3       | Summ              | ary                                                                               | 58 |  |  |  |

| 3.4       | Refere            | ences                                                                             | 60 |  |  |  |

|           |                   |                                                                                   |    |  |  |  |

| Chapter 4 | TaN/Z             | rO <sub>2</sub> MOSCAP and MOSFET characteristics                                 | 63 |  |  |  |

| 4.1       | Motiv             | ation                                                                             | 63 |  |  |  |

| 4.2       | TaN/Z             | CrO <sub>2</sub> MOSCAP characteristics                                           | 68 |  |  |  |

|           | 4.2.1             | TaN/ZrO <sub>2</sub> MOSCAP/MOSFET process flow and                               |    |  |  |  |

|           |                   | measurement                                                                       | 68 |  |  |  |

|           | 4.2.2             | Evaluation of TaN/ZrO <sub>2</sub> MOSCAP electrical characteristics              | 71 |  |  |  |

| 4.3       | TaN/Z             | CrO <sub>2</sub> NMOSFET characteristics                                          | 82 |  |  |  |

| 4.4       | Summ              | ary                                                                               | 88 |  |  |  |

| 4.5       | Refere            | ences                                                                             | 91 |  |  |  |

|           |                   |                                                                                   |    |  |  |  |

| Chapter 5 | Nitrog            | en incorporation into the ZrO <sub>2</sub> gate stack                             | 95 |  |  |  |

| 5.1       | Motiv             | ation                                                                             | 95 |  |  |  |

| 5.2       | NH <sub>3</sub> S | i surface nitridation (SN)                                                        | 97 |  |  |  |

|           | 5.2.1             | TaN/ZrO <sub>2</sub> NMOSCAP with SN process flow and                             |    |  |  |  |

|           |                   | measurement                                                                       | 97 |  |  |  |

|           | 5.2.2             | Characterization of TaN/ZrO <sub>2</sub> NMOSCAPs with SN                         | 99 |  |  |  |

| 5.3       | Nitrogen-incorporated ZrO <sub>2</sub> or ZrO <sub>x</sub> N <sub>y</sub> |                                                                                |     |  |  |  |

|-----------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----|--|--|--|

|           | 5.3.1                                                                     | TaN/ZrO <sub>x</sub> N <sub>y</sub> NMOSCAP/NMOSFET process flow               |     |  |  |  |

|           |                                                                           | and measurement.                                                               | 106 |  |  |  |

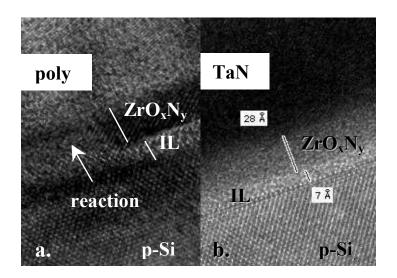

|           | 5.3.2                                                                     | Comparison of ZrO <sub>2</sub> and ZrO <sub>x</sub> N <sub>y</sub> material    |     |  |  |  |

|           |                                                                           | characteristics                                                                | 108 |  |  |  |

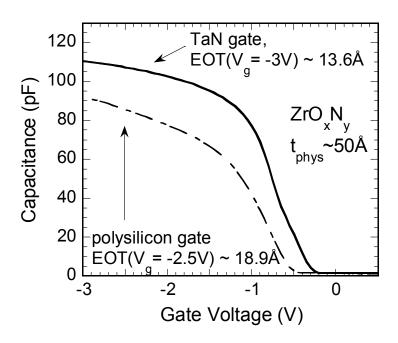

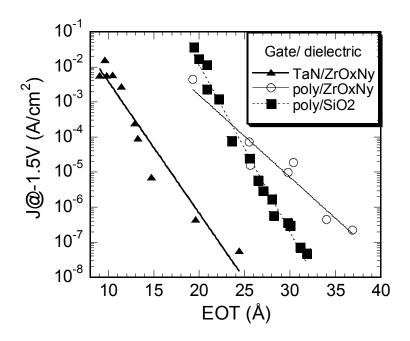

|           | 5.3.3                                                                     | Comparison of ZrO <sub>2</sub> and ZrO <sub>x</sub> N <sub>y</sub> NMOSCAP     |     |  |  |  |

|           |                                                                           | characteristics                                                                | 113 |  |  |  |

|           | 5.3.4                                                                     | Comparison of ZrO <sub>2</sub> and ZrO <sub>x</sub> N <sub>y</sub> NMOSFET     |     |  |  |  |

|           |                                                                           | characteristics                                                                | 119 |  |  |  |

|           | 5.3.5                                                                     | Comparison of ZrO <sub>2</sub> and ZrO <sub>x</sub> N <sub>y</sub> reliability |     |  |  |  |

|           |                                                                           | characteristics                                                                | 125 |  |  |  |

| 5.4       | High                                                                      | temperature forming gas annealing of ZrO <sub>x</sub> N <sub>y</sub> NMOSFETs  | 129 |  |  |  |

|           | 5.4.1                                                                     | High temperature FG anneal process flow and device                             |     |  |  |  |

|           |                                                                           | measurement                                                                    | 130 |  |  |  |

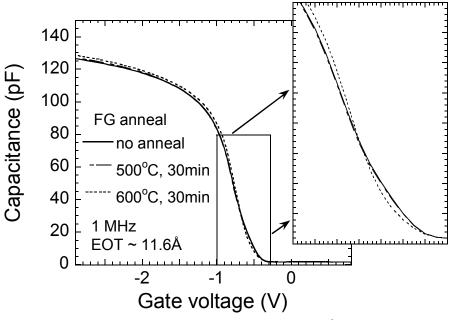

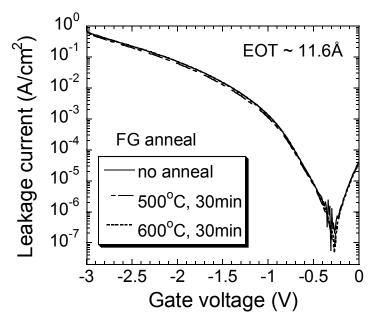

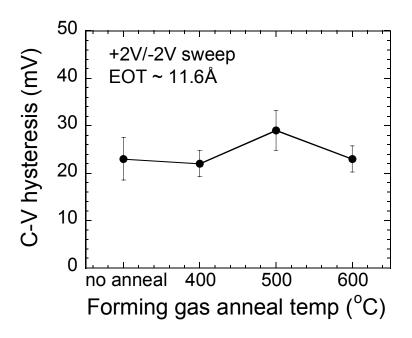

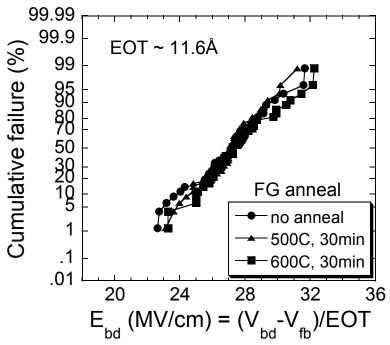

|           | 5.4.2                                                                     | NMOSCAP/NMOSFET characteristics after high                                     |     |  |  |  |

|           |                                                                           | temperature FG anneal                                                          | 131 |  |  |  |

| 5.5       | Sumn                                                                      | nary                                                                           | 137 |  |  |  |

| 5.6       | Refere                                                                    | ences                                                                          | 141 |  |  |  |

| Chapter 6 | Concl                                                                     | usion and future work                                                          | 145 |  |  |  |

| 6.1       |                                                                           | nary and conclusion                                                            |     |  |  |  |

| 6.2       |                                                                           | e work                                                                         |     |  |  |  |

|           |                                                                           |                                                                                |     |  |  |  |

| Bibliogra | phy                                                                       |                                                                                | 152 |  |  |  |

| Vita      |                                                                           |                                                                                | 166 |  |  |  |

#### **CHAPTER 1**

# **Introduction and Background**

# 1.1 Challenges to Moore's law: 90 nm and beyond

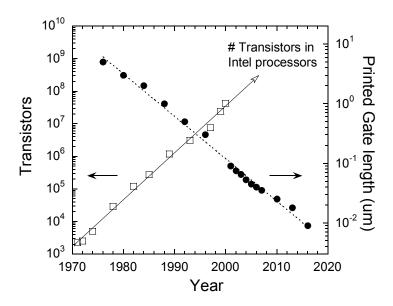

The most crucial element in the success of the silicon semiconductor industry has been its continued ability to downscale transistor dimensions over the last few decades. Innovations in fabrication processes and the introduction of new materials and tools have allowed chipmakers to follow Moore's law each generation. Fig 1.1 illustrates how the number of metal oxide semiconductor field effect transistors (MOSFETs) in Intel processors has doubled with each technology generation as printed gate lengths have shrunk exponentially [1]. As gate lengths have been scaled to 90 nm and lower, new problems have arisen:

- ➤ SiO<sub>2</sub> minimum scaling limits

- ➤ Polysilicon depletion (PD) effect

- Quantum mechanical (QM) effects

- ➤ Non-scalability of threshold voltage (V<sub>t</sub>)

- ➤ Mobility degradation

- ➤ Ultra-shallow Source/Drain junctions and S/D resistance

- ➤ Both adequate drive current and turn-off

Figure 1.1 The number of transistors in Intel processors increases and transistor gate lengths decrease exponentially over the years [1].

The first three challenges –  $SiO_2$  minimum scaling limits (section 1.2), the PD effect, and QM effects – will be discussed at length since they are the key motivations behind the need for high-k gate dielectrics.

Heavily doped polysilicon (poly) has been used as the gate electrode material since the 1970s. Poly gate electrodes have worked well in complementary metal oxide semiconductor (CMOS) processes for several reasons. First, the workfunction can be manipulated to be either p-type or n-type depending on the dopant and doping level. Additionally, poly gates lend themselves well to the self-aligned MOSFET process since they can be doped during the source/drain (S/D) implant, activated during S/D annealing, and can withstand the high temperatures required for CMOS processing.

The poly depletion (PD) effect is caused when the MOSFET is turned on and the poly gate electrode is depleted at the poly/SiO₂ interface. This thin depletion layer adds to the equivalent oxide thickness (EOT) and consequently, reduces the gate capacitance and drain current. Although PD only adds a 1-4 angstroms (Å) to the EOT, this represents a large percentage since EOT values will be less than 10Å by 2004 [2]. Additionally, PD has been reported to get worse as the gate length gets shorter (≤ 35 nm) due to vertical fringing gate fields [3]. Increasing the poly doping can reduce PD, but achieving uniform doping is difficult due to the constraints of dopant (boron) diffusion into the gate oxide and maintaining the correct S/D junction depth and width during activation annealing [4]. Ultimately, PD will force the replacement of poly by dual metal gate electrodes.

Like PD, the quantum mechanical (QM) effect results in an increase in EOT. At gate lengths below 0.25 μm, the combination of high channel doping and thin gate oxides results in high electric fields at the Si surface. These high fields result in a splitting of the conduction band into discrete sub-bands, causing quantization of the carriers perpendicular to the SiO<sub>2</sub>/Si interface [5,6]. As a result, carriers in the channel actually travel a few angstroms (Å) below the gate dielectric/silicon interface leaving a thin charge depletion region. This depletion region has a dielectric constant of Si (11.7) and thus reduces the gate stack capacitance, and the EOT is increased ~3-5Å [7]. Unfortunately, there is no known solution to avoid the EOT increase caused by QM.

## 1.2 Scaling limits of SiO<sub>2</sub>

One of the industry's biggest scaling challenges – the replacement of silicon dioxide (SiO<sub>2</sub>) as the MOSFET gate dielectric – must be addressed in order for the scaling to continue in the coming years. SiO<sub>2</sub> has been used as the gate dielectric material in MOS technology since the inception of the MOSFET in 1960. The ability to grow high-quality insulating oxide on silicon was one of the major reasons Si was chosen as the 'mainstream' semiconductor material. High temperature growth of the oxide directly from the silicon offered many desirable properties such as an excellent interface, thickness controllability, high thermal stability, and good reliability. Thus, replacement of SiO<sub>2</sub> with a deposited material that can offer comparable properties will prove to be a difficult challenge.

So, what is the driving force behind the replacement of SiO<sub>2</sub>? The 2001 Edition of the International Technology Roadmap for Semiconductors (ITRS) predicts that the gate dielectric must have an equivalent oxide thickness (EOT) of 11-15Å in 2003 [2]. A SiO<sub>2</sub> layer of 11-15Å thick is only around 3-4 monolayers of SiO<sub>2</sub>, which creates several problems.

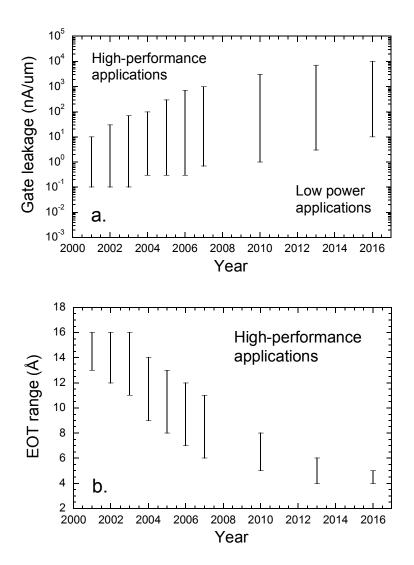

First, a physical thickness of 11-15Å is so thin that electrons can directly tunnel through the SiO<sub>2</sub>, resulting in excessively high gate leakage current. High leakage is a great concern, particularly for low power applications, and high performance applications as well. Figures 1.2a and 1.2b show the predicted gate

dielectric leakage limits and equivalent oxide thickness (EOT) range for in the coming years, respectively [2].

Figure 1.2 (a) The predicted range of acceptable gate leakage current over the years where the upper limit represents high performance and the lower limit represents low power applications [2].

(b) The range of EOT for high performance applications in the coming years [2].

Additionally,  $SiO_2$  thickness uniformity across a 300 mm wafer becomes even more crucial for such a thin film, since even a monolayer difference in thickness represents a large percentage difference and thus can result in varying threshold voltage ( $V_t$ ) across the wafer. Reliability also becomes a huge concern for such a thin  $SiO_2$  dielectric.

# 1.3 Motivation for various high-k gate dielectric candidates

Materials with a dielectric constant higher than that of  $SiO_2$ , known as high-k dielectrics, have been under intense investigation in order to identify a  $SiO_2$  replacement. High-k materials can provide the same capacitance as a very thin layer of  $SiO_2$  although they are physically thicker as shown in equation 1.1 where C represents capacitance; k is dielectric constant;  $\varepsilon_0$  is the permittivity of free space - a constant; A is capacitor area, and t is dielectric thickness.

$$C = k\varepsilon_o \frac{A}{t} \tag{1.1}$$

There is a wide range of high-k materials with a wide range of dielectric constants as shown in table 1.1.

|   | SiO <sub>2</sub> | Si <sub>3</sub> N <sub>4</sub> | $Al_2O_3$ | ZrSiO <sub>4</sub> | HfSiO <sub>4</sub> | $ZrO_2$ | HfO <sub>2</sub> | $Ta_2O_5$ | TiO <sub>2</sub> | BST  |

|---|------------------|--------------------------------|-----------|--------------------|--------------------|---------|------------------|-----------|------------------|------|

| k | 3.9              | 7                              | ~10       | ~13                | ~15                | ~22     | ~25              | ~23       | ~80              | ~300 |

Table 1.1 Various gate dielectrics and their dielectric constants [8,9,10]

Materials at both ends of the spectrum will be discussed before concentrating more closely on the mid-range high-k materials.

### 1.3.1 Moderate high-k materials: Oxynitrides and Si<sub>3</sub>N<sub>4</sub>

Oxynitrides have been under investigation for gate dielectric application for over a decade. It was discovered that the introduction of nitrogen into  $SiO_2$  via NO,  $N_2O$ , or  $NH_3$  annealing, termed oxynitride, not only raised the dielectric constant slightly ( $k \sim 5.5$ , depending on nitrogen content [11,12]) but also had the added benefits of improved reliability, increased resistance to boron penetration, and better interfacial quality [13]. Nitride,  $Si_3N_4$  ( $k \sim 7$ ), has also been considered as a gate dielectric, and is attractive because it is already used in MOS technology. In addition, research on oxide/ $Si_3N_4$  stack structures has demonstrated MOSFETs with 70  $\mu$ m gate length [14].

Unfortunately, these oxynitrides, as well as  $oxide/Si_3N_4$  stacks, and  $Si_3N_4$  are still limited by their relatively low dielectric constants, and thus cannot be scaled much lower than 10Å. Consequently, these dielectrics will only last a few generations due to limitations dictated by low power applications and scalability.

#### 1.3.2 Ultra high-k: Barium Strontium Titanate (BST)

Initial research into high-k MOS gate dielectrics focused on ultra high-k materials such as barium strontium titanate (BST) because it had already been

investigated for giga-bit DRAM applications [15,16,17]. EOT values of less than 1Å have been achieved with DRAM metal-insulator-metal (MIM) capacitors using BST [15]. However, researchers soon discovered that BST in metal-insulator-semiconductor (MIS) capacitors yielded much higher EOTs due to the formation of a relatively thick (~30Å) Si<sub>x</sub>O<sub>y</sub> interfacial layer between the BST and silicon substrate. The growth of this Si<sub>x</sub>O<sub>y</sub> layer resulted from reaction and interdiffusion between the BST and substrate [18], and it was concluded that BST was not thermodynamically stable in contact with silicon.

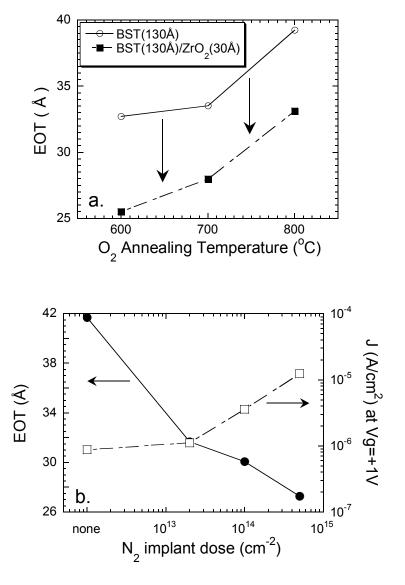

Various barrier layers and surface treatment techniques were used in an attempt to prevent this interfacial reaction. Barrier layers of Si<sub>3</sub>N<sub>4</sub> [18], Ta<sub>2</sub>O<sub>5</sub>, TiO<sub>2</sub> [18], and ZrO<sub>2</sub> [19] did reduce the interfacial layer thickness, and thus the EOT, but not substantially enough to make BST a viable gate dielectric. Figure 1.3a shows the EOT reduction (~7Å) of Pt/BST/ZrO<sub>2</sub>/Si capacitors as compared to Pt/BST/Si capacitors with the same BST thickness after various oxygen anneal temperatures [19]. Additionally, experiments using nitrogen (N<sub>2</sub>) implantation into the Si substrate prior to BST deposition also resulted in reduced EOT values [20]. The nitrogen incorporated at the BST/Si interface served to decrease the interdiffusion and reaction between the BST and Si. As shown in figure 1.3b, the EOT decreased with increasing N<sub>2</sub> implant dose, but the drawback was that the leakage increased as a result of both lower EOT and increased implant damage with increasing dose [20].

Although the introduction of high-k barrier layers and the  $N_2$  implantation technique did help scale the EOT of BST, they did not improve the scalability significantly enough to justify the added process complexity.

Figure 1.3 (a) EOT comparison of Pt/BST and Pt/BST/ZrO<sub>2</sub> stack structures for different oxygen annealing temperatures [19]. (b) EOT and leakage (J) dependence on N<sub>2</sub> implant dose of BST on N<sub>2</sub>-implanted Si [20].

## 1.3.3 Mid-range high-k: Ta<sub>2</sub>O<sub>5</sub>, TiO<sub>2</sub>, BeO, MgO, HfO<sub>2</sub>, and ZrO<sub>2</sub>

Of the mid-range high-k dielectrics, Ta<sub>2</sub>O<sub>5</sub> and TiO<sub>2</sub> were initially studied, but were also found to have problems with interfacial layer formation between the high-k material and the silicon substrate. Focus was then shifted towards identifying high-k materials that were thermodynamically stable in contact with silicon.

In 1996, Hubbard and Schlom performed a thermodynamic analysis to determine which binary metal oxides were theoretically stable in contact with silicon up to temperatures  $\sim 700^{\circ}$ C [21]. Chemical equations were analyzed to determine the change in Gibbs free energy and thus the favored state of a system; if the Gibbs free energy was lowered for any of the equations, it was an indication of instability of the oxide with silicon. The chemical equations were as follows where  $MO_x$  represents the binary metal oxide [21]:

$$Si + MO_x \rightarrow M + SiO_2$$

(1.2)

$$Si + MO_x \rightarrow MSi_z + SiO_2$$

(1.3)

$$Si + MO_x \rightarrow MO_w + SiO_2$$

(1.4)

$$Si + MO_x \rightarrow MSi_z + MSi_xO_v$$

(1.5)

$$Si + MO_x \rightarrow M + MSi_xO_v$$

(1.6)

Equations 1.2 and 1.3 test for the formation of metal products (M) and silicides ( $MSi_z$ ), respectively, with  $SiO_2$ . Equations 1.4-1.6 tested for the formation of other

binary oxides ( $MO_w$ ) as well as ternary phases ( $MSi_xO_y$ ). From these calculations, it was found that  $Ta_2O_5$  was not thermodynamically stable, as it tended to dissociate into metallic Ta, thus failing equation 1.2. Furthermore,  $TiO_2$  was also found to be unstable at temperatures around 700°C because it tended to form a silicide,  $TiSi_x$ , thus failing equation 1.3.

Due to insufficient thermodynamic data, Hubbard and Schlom were not able to verify the thermal stability of HfO<sub>2</sub>, although later studies have demonstrated stability via excellent device and materials characteristics [22,23]. HfO<sub>2</sub> is a promising candidate for high-k gate dielectric and will be mentioned periodically in chapters 3-5.

Hubbard and Schlom were able to verify the stability of three binary oxides: ZrO<sub>2</sub>, BeO, and MgO. Since BeO and MgO have fairly low dielectric constants of 6.8 and 9.8 [8], respectively, they are of little interest as oxynitrides and oxide/nitride stack structures have comparable dielectric constants and are more well established processes. Because ZrO<sub>2</sub> has a reported dielectric value ranging from 17-27 [24,25] and was deemed thermally stable by Hubbard and Schlom, it has received much attention as a promising high-k gate dielectric candidate.

## 1.3.4 Requirements for high-k dielectrics [26,27]

As mentioned earlier, the replacement of thermally grown SiO<sub>2</sub> with a deposited high-k gate dielectric will be particularly difficult due to the excellent

interface properties between Si and SiO<sub>2</sub>. Some of the required characteristics of high-k gate dielectrics are listed below.

## Material characteristics and process compatibility:

- ➤ Thermal stability on Si (section 1.3.3)

- $\triangleright$  High dielectric constant ( $\ge 15$ )

- ➤ Large bandgap and barrier heights

- ➤ High crystalline temperature (preferably amorphous phase)

- ➤ Compatibility with gate electrode material

- Resistant to interfacial layer growth (EOT increase) during thermal processing

- ➤ Low lattice mismatch and similar thermal expansion coefficient with Si

- ➤ High density to prevent impurity diffusion

- > Etchability

- ➤ Mass production deposition process capability

#### Electrical and reliability characteristics:

- ➤ Scalable EOT < 10Å

- ➤ Low gate leakage current

- ➤ Negligible capacitance-voltage (C-V) hysteresis (< 20mV)

- ➤ Negligible frequency dispersion

- ➤ Density of interface states (D<sub>it</sub>) comparable to SiO<sub>2</sub>

- ➤ Mobility comparable to SiO<sub>2</sub> (80-90%)

➤ Good reliability (no charge trapping, high breakdown voltage, sufficient 10 year lifetime operating voltage, etc...)

## 1.4 Motivation for ZrO<sub>2</sub> gate dielectric

Past studies on ZrO<sub>2</sub> have focused on its use in optical and mechanical applications, and thus concentrated on a much thicker range of films than required for gate dielectric application (<100Å) [28,29]. Deposition techniques include chemical vapor deposition (CVD) [24,30,31], electron beam evaporation, pulsed laser deposition [32], atomic layer deposition (ALD) [33], RF sputtering, and DC sputtering [29]. More recent studies have focused on ZrO<sub>2</sub> for gate applications and have produced encouraging results, which will be discussed in detail in chapters 2-5.

## 1.4.1 ZrO<sub>2</sub> material properties

Many of ZrO<sub>2</sub> material properties make it an attractive MOS gate dielectric material as summarized in table 1.2. ZrO<sub>2</sub> has a sufficiently high dielectric constant of around 17-27 [24-25] and is stable in contact with Si [21], which should result in a scalable EOT. ZrO<sub>2</sub>'s hardness, chemically inert behavior, and durability [32] make it attractive for mechanical applications. Additionally, it has a reported refractive index ranging from 1.84-2.23 [34] and a fairly high density of 5.74 g/cm<sup>3</sup>, which may help to prevent impurity diffusion. As for ZrO<sub>2</sub>'s energy bandgap, it is reportedly 5.8 eV with calculated band offsets of 1.4 eV for electrons and 3.3 eV for holes [35], which should be sufficiently large enough for low gate leakage current. It has a high

melting point of around 2950K. Finally, it was reported that ZrO<sub>2</sub> could be etched with dilute hydrofluoric (HF) solution, which is commonly used in current MOS processing to remove SiO<sub>2</sub> [25].

| Material property              | ZrO <sub>2</sub>                       | SiO <sub>2</sub>                   |

|--------------------------------|----------------------------------------|------------------------------------|

| Dielectric constant            | 17 - 22                                | 3.9                                |

| Bandgap                        | 5.8 eV                                 | 9.0 eV                             |

| Band offset for electrons      | 1.4 eV                                 | 3.5 eV                             |

| Band offset for holes          | 3.3 eV                                 | 4.4 eV                             |

| Refractive index               | 1.84 - 2.23                            | 1.46                               |

| Density                        | 5.74 g/cm <sup>3</sup>                 | 2.27 g/cm <sup>3</sup>             |

| Lattice mismatch with (100) Si | 2.1%                                   | _                                  |

| Thermal expansion coefficient  | 1.2 x 10 <sup>-5</sup> K <sup>-1</sup> | $5.0 \times 10^{-7} \text{K}^{-1}$ |

| Melting point                  | ~ 2677°C                               | ~ 1600°C                           |

| Etchability                    | HF solution                            | HF solution                        |

Table 1.2 Material properties of ZrO<sub>2</sub> and SiO<sub>2</sub>

$ZrO_2$ 's lattice parameters  $a_0$ ,  $b_0$ , and  $c_0$  are 5.148Å, 5.203Å, and 5.316Å, respectively, which correspond to a lattice mismatch of 5.2%, 4.2%, and 2.1% with silicon [25]. These values indicate that the lowest lattice mismatch, 2.1%, occurs in the (100) plane – the most common silicon orientation used in MOS processing today.

The thermal expansion coefficient of  $ZrO_2$  is  $\sim 1.2 \times 10^{-5}$  K<sup>-1</sup>, as compared to Si  $(2.6 \times 10^{-6} \text{ K}^{-1})$  and  $SiO_2$   $(5.0 \times 10^{-7} \text{ K}^{-1})$ . Both the low lattice mismatch and comparable thermal expansion coefficient with Si will ensure low mechanical stress/strain between the films.

#### 1.5 Outline

Chapter 1 has given an introduction to scaling challenges facing the semiconductor industry in the coming years. The combination of the limits to SiO<sub>2</sub> gate dielectric scaling, the poly depletion, and quantum mechanical effects will force the implementation of high-k gate dielectric materials. Of the high-k materials mentioned, ZrO<sub>2</sub> is a promising candidate since it possesses many of the material characteristics required by high-k gate dielectrics. Chapters 2-5 will investigate ZrO<sub>2</sub> in greater detail in terms of its electrical, material, and reliability characteristics as well as its compatibility with conventional CMOS processing.

Chapter 2 focuses on the process optimization and materials characterization of sputter deposited ZrO<sub>2</sub> films. Initially, platinum (Pt) electrodes are used to evaluate ZrO<sub>2</sub> MOS capacitor (MOSCAP) properties such as EOT scalability, frequency dispersion, C-V hysteresis, and gate leakage current. Interfacial layer composition is described as well.

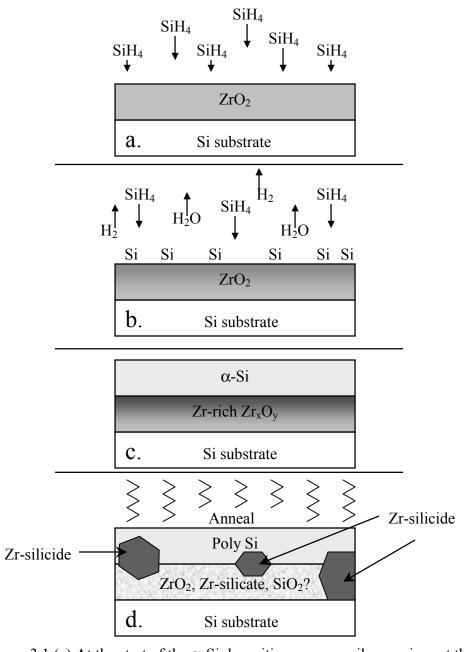

Chapter 3 discusses the experiments performed on  $ZrO_2$  and nitrogen-incorporated  $ZrO_2$  ( $ZrO_xN_y$ ) with polysilicon gate electrode. Despite numerous

attempts to optimize the MOSCAP fabrication process, it is discovered that the poly deposition process is not compatible with ZrO<sub>2</sub> or ZrO<sub>x</sub>N<sub>y</sub>. An explanation for this incompatibility is given.

Chapter 4 details the work performed on both MOSCAPs and MOSFETs using tantalum nitride (TaN) gate electrode. The motivation behind using TaN gate is presented along with MOSCAP and MOSFET characteristics such as C-V, frequency dispersion, C-V hysteresis, J-V,  $I_d$ - $V_g$ ,  $I_d$ - $V_d$ , and mobility.

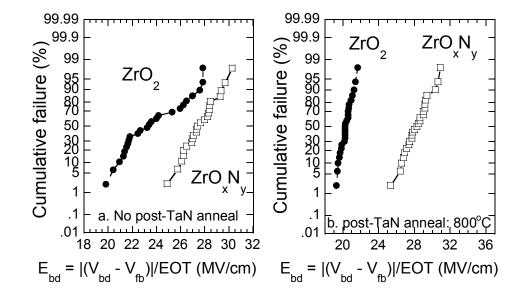

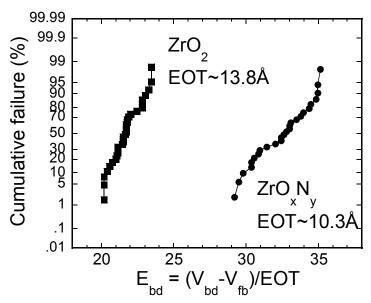

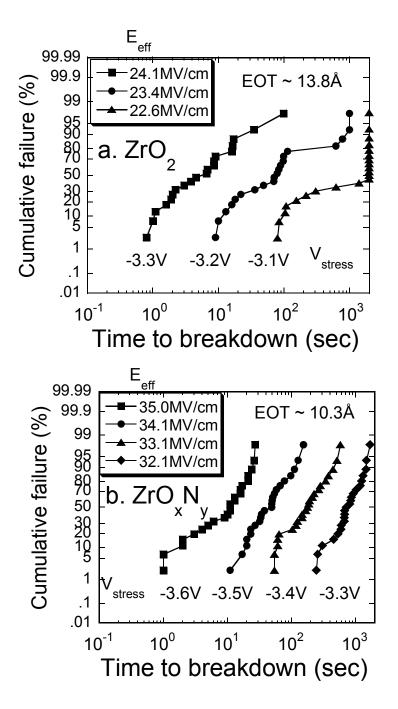

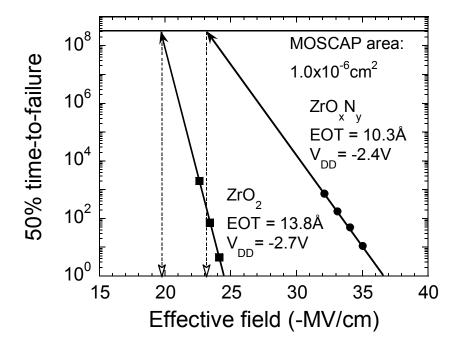

Chapter 5 investigates two types of nitrogen incorporation into the ZrO<sub>2</sub> gate dielectric: Si surface nitridation prior to ZrO<sub>2</sub> deposition and nitrogen-incorporated ZrO<sub>2</sub> (ZrO<sub>x</sub>N<sub>y</sub>). Both processes yield improvements such as improved thermal stability and higher breakdown voltage. TaN/ZrO<sub>x</sub>N<sub>y</sub> and TaN/ZrO<sub>2</sub> MOSFET characteristics such as I<sub>d</sub>-V<sub>g</sub>, I<sub>d</sub>-V<sub>d</sub>, and mobility are compared in addition to reliability tests such as time zero dielectric breakdown (tzdb), time dependent dielectric breakdown (tddb), and 10-year lifetime operating voltage. Finally, the effects of high temperature forming gas annealing on MOSCAP and MOSFET characteristics, including mobility, are investigated.

Finally, Chapter 6 summarizes the results yielded by the fabrication and the electrical, materials, and reliability characterization of these  $ZrO_2$  and  $ZrO_xN_y$  MOSCAPs and MOSFETs. In addition, suggestions are given for possible future work on  $ZrO_2$  and  $ZrO_xN_y$  gate dielectrics.

#### 1.6 References

- [1] S. Borkar, "Obeying Moore's Law beyond 0.18 micron," Proceedings of the 13<sup>th</sup> Annual IEEE International ASIC/SOC Conference, p. 26, 2000.

- [2] International Technology Roadmap for Semiconductors, 2001 edition. Semiconductor Industry Association, 2001.

- [3] C.-H. Choi, P.R. Chidambaram, R. Khamankar, C.F. Machala, Z. Yu, and R.W. Dutton, "Gate Length Dependent Polysilicon Depletion Effects," IEEE Electron Device Letters, vol. 23, no. 4, p. 224, 2002.

- [4] R. Rios, N.D. Arora, and C.-L. Huang, "An Analytic Polysilicon Depletion Effect Model for MOSFET's," IEEE Electron Device Letters, vol. 15, no. 4, p. 129, 1994.

- [5] R. Rios, N.D. Arora, C.-L. Huang, N. Khalil, J. Faricelli, and L. Gruber, "A Physical Compact MOSFET Model, Including Quantum Mechanical Effects, for Statistical Circuit Design Applications," International Electron Devices Meeting, IEDM Technical Digest, p. 937, 1995.

- [6] R. Rios and N.D. Arora, "Determination of Ultra-thin Gate Oxide Thicknesses for CMOS Structures using Quantum Effects," International Electron Devices Meeting, IEDM Technical Digest, p. 613, 1994.

- [7] K. Yang, Y.C. King, and C. Hu, "Quantum Effect in Oxide Thickness Determination from Capacitance Measurement," Technical Digest of Symposium on VLSI Technology, p. 77, 1999.

- [8] R.D. Shannon, "Dielectric polarizabilities of ions in oxides and fluorides," Journal of Applied Physics, vol. 73, no. 1, p. 348, 1993.

- [9] G.D. Wilk, R.M. Wallace, and J.M. Anthony, "Hafnium and zirconium silicates for advanced gate dielectrics," Journal of Applied Physics, vol. 15, no. 1, p. 484, 2000.

- [10] S. Ezhilvalavan and T. Tseng, "Conduction mechanisms in amorphous and crystalline Ta<sub>2</sub>O<sub>5</sub> thin films," Journal of Applied Physics, vol. 83, no. 9, p. 4797, 1998.

- [11] J. Vuillod, "Preparation and characterization of plasma enhanced chemical vapor deposited silicon nitride and oxynitride films," Journal of Vacuum Science & Technology A, vol. 5, no. 4, p. 1675, 1987.

- [12] J.A. Diniz, P.J. Tatsch, and M.A.A. Pudenzi, "Oxynitride films formed by low energy NO<sup>+</sup> implantation into silicon," Applied Physics Letters, vol. 69, no. 15, p. 2214, 1996.

- [13] H. Hwang, W. Ting, D.-L. Kwong, and J.C. Lee, "Electrical and reliability characteristics of ultrathin oxynitride gate dielectric prepared by rapid thermal processing in N<sub>2</sub>O," International Electron Devices Meeting, IEDM Technical Digest, p. 421, 1990.

- [14] A. Ono, K. Fukasaku, T. Fukuda, N. Ilezawa, K. Imai, and T. Horiuchu, "A 70µm Gate Length CMOS technology with 1.0V Operation," Technical Digest of Symposium on VLSI Technology, p. 14, 2000.

- [15] N. Fukushima, K. Abe, M. Izuha, T. Schimizu, and T. Kawakubo, "Epitaxial (Ba,Sr)TiO<sub>3</sub> Capacitors with Extremely High Dielectric Constant for DRAM Applications," International Electron Devices Meeting, IEDM Technical Digest, p. 257, 1997.

- [16] R.B. Khamankar, M.A. Kressley, M.R. Visokay, T. Moise, G. Xing, S. Nemoto, Y. Okuno, S.J. Fang, A.M. Wilson, J.F. Gaynor, T.Q. Hurd, D.L. Crenshaw, S. Summerfelt, and L. Colombo, "A Novel BST Storage Capacitor Node Technology Using Platinum Electrodes for Gbit DRAMs," International Electron Devices Meeting, IEDM Technical Digest, p. 245, 1997.

- [17] T. Chen, D. Hadad, V. Balu, B. Jiang, S. Kuah, P.C. McIntyre, S.R. Summerfelt, J.M. Anthony, and J.C. Lee, "Ir-Electroded BST Thin Film Capacitors for 1 Giga-bit DRAM Application," International Electron Devices Meeting, IEDM Technical Digest, p. 679, 1996.

- [18] Y. Jeon, B.H. Lee, K. Zawadski, W. Qi, A. Lucas, R. Nieh, and J.C. Lee, "Effect of Barrier Layer on the Electrical and Reliability Characteristics of High-k Gate Dielectric films," International Electron Devices Meeting, IEDM Technical Digest, p. 797, 1998.

- [19] R. Nieh, "High-k Gate Dielectrics for Future MOS Technology," Master's Thesis. The University of Texas at Austin, 1999.

- [20] R. Nieh, W.J. Qi, Y. Jeon, B.H. Lee, A. Lucas, L. Kang, J.C. Lee, M. Gardner, and M. Gilmer, "Nitrogen (N<sub>2</sub>) implantation to suppress growth of interfacial oxide in MOCVD BST and sputtered BST films," Materials Research Society Symposium Proceedings Series, vol. 567, p. 521, 1999.

- [21] K.J. Hubbard and D.G Schlom, "Thermodynamic stability of binary oxides in contact with silicon," Journal of Materials Research, vol. 11, no. 11, p. 2757, 1996.

- [22] B.H. Lee, "Technology Development and Process Integration of Alternative Gate Dielectric Material; Hafnium Oxide," Ph.D. dissertation, The University of Texas at Austin, 2000.

- [23] L. Kang, "Study of HfO<sub>2</sub> as a Future Gate Dielectric and Implementation of Polysilicon Electrodes for HfO<sub>2</sub> films," Ph.D. dissertation, The University of Texas at Austin, 2000.

- [24] M. Balog, M. Schieber, M. Michman, and S. Patai, "The chemical vapour deposition and characterization of ZrO<sub>2</sub> films from organometallic compounds," Thin Solid Films, vol. 47, p. 109, 1977.

- [25] C.S. Hwang and H.J. Kim, "Deposition and characterization of ZrO<sub>2</sub> thin films on silicon substrate by MOCVD," Journal of Materials Research, vol. 8, no. 6, p. 1361, 1993.

- [26] G.D. Wilk, R.M. Wallace, and J.M. Anthony, "High-k gate dielectrics: Current status and materials properties considerations," Journal of Applied Physics, vol. 89, no. 10, p. 5243, 2001.

- [27] J.S. Suehle, E.M. Vogel, M.D. Edelstein, C.A. Richter, N.V. Nguyen, I. Levin, D.L. Kaiser, H. Wu, and J.B. Bernstein, "Challenges of High-k Gate Dielectrics for Future MOS Devices," 6<sup>th</sup> International Symposium on Plasma-Induced Damage, p. 90, 2001.

- [28] M.A. Cameron and S.M. George, "ZrO<sub>2</sub> film growth by chemical vapor deposition using zirconium tetra-*tert*-butoxide," Thin Solid Films, vol. 348, p. 90, 1999.

- [29] W.W. Davison and R.C. Buchanan, "ZrO<sub>2</sub> Thin Films for Packaging and Microelectronics Applications," Advances in Ceramics: Ceramic Substrates and Packages for Electronic Application, vol. 26, p. 513, 1989.

- [30] M. Balog, M. Schieber, M. Michman, and S. Patai, "The Characteristics of Growth of Films of Zirconium and Hafnium Oxides (ZrO<sub>2</sub>, HfO<sub>2</sub>) by Thermal Decomposition of Zirconium and Hafnium β-Diketonate Complexes in the Presence and Absence of Oxygen," Journal of the Electrochemical Society: Solid-state Science and Technology, vol. 126, no. 7, p. 1203, 1979.

- [31] M. Balog, M. Schieber, S. Patai, and M. Michman, "Thin Films of Metal oxides on Silicon by Chemical Vapor Deposition with Organometallic Compounds," Journal of Crystal Growth, vol. 17, p. 298, 1972.

- [32] A.C. Greenwald, N.M. Kalkhoran, F. Namavar, A.E. Kaloyeros, and I. Stathakos, "Heteroepitaxial Si-ZrO<sub>2</sub>-Si by MOCVD," Materials Research Society Symposium Proceedings, vol. 335, p. 123, 1993.

- [33] K. Kukli, K. Forsgren, M. Ritala, M. Leskelä, J. Aarik, and A. Hårsta, "Dielectric Properties of Zirconium Oxide Grown by Atomic Layer Deposition from Iodide Precursor," Journal of the Electrochemical Society, vol. 148, p. F227, 2001.

- [34] P.J. Martin, R.P. Netterfield, and W.G. Sainty, "Modification of the optical and structural properties of dielectric ZrO<sub>2</sub> films by ion-assisted deposition," Journal of Applied Physics, vol. 55, no. 1, p. 235, 1984.

- [35] J. Robertson, E. Riassi, J.-P. Maria, and A.I. Kingon, "Band alignments of high-k dielectrics on Si and Pt," Materials Research Society Symposium Proceedings Series, vol. 592, 1999.

#### **CHAPTER 2**

# ZrO<sub>2</sub> Process Optimization and

# Initial MOSCAP (Pt/ZrO<sub>2</sub>) characterization

#### 2.1 Motivation

The purpose of this chapter is to describe the preliminary work performed on ZrO<sub>2</sub> gate dielectrics. The results from this chapter will lay the groundwork for the experiments in chapters 3-5. Initially, experiments were performed to optimize the ZrO<sub>2</sub> deposition process in terms of both low EOT and low gate leakage current. These sputter-deposited ZrO<sub>2</sub> films were tested using techniques such as X-ray photoelectron spectroscopy (XPS), transmission electron microscopy (TEM), atomic force microscopy (AFM), and X-ray diffraction (XRD) in order to answer questions about the ZrO<sub>2</sub> composition, interfacial layer composition, morphology, and surface roughness.

Platinum (Pt) gate electrodes were used to fabricate MOSCAPs in order to evaluate these ZrO<sub>2</sub> films. Pt was chosen as an evaluation gate electrode for several reasons. First, Pt has a high resistance to corrosion and is thermally stable [1]. Thus, Pt is not prone to reaction with oxygen to form platinum oxide or prone to reaction with the ZrO<sub>2</sub> gate dielectric. Secondly, Pt has a low resistivity and a high melting point (1172°C) so it can withstand thermal processing [2]. Finally and practically, Pt was readily available, and the clean room had the facilities to deposit and pattern it.

However, it should be noted that Pt gate electrodes are not likely to be used in future MOS technology. First, Pt is a fairly expensive material. Secondly, although Pt is a fairly inert material, it can react with Si at relatively low temperatures (~450°C) to form platinum silicide (PtSi) [2,3]. Consequently, with only a thin dielectric film separating the two, it is possible that the Pt gate electrode and silicon substrate could react to form PtSi after the high temperature processing necessary for self-aligned MOSFET fabrication. However, MOSCAP processing does not require high temperature annealing after Pt gate deposition, so the threat of PtSi formation can be avoided. Thus Pt was an acceptable candidate for an evaluation gate electrode material.

## 2.2 Process optimization

#### 2.2.1 Pt/ZrO<sub>2</sub>/Si MOSCAP process flow and measurement

Pt/ZrO<sub>2</sub>/Si MOSCAPs were fabricated using the process flow in table 2.1.

- 1. Piranha clean

- 2. Field oxidation ~3500Å at 950°C

- 3. Active area patterning (Buffered oxide etch):  $5 \times 10^{-5}$  cm<sup>2</sup>

- 4. Piranha clean/HF dip/DI water rinse

- 5. Zr deposition ~20-40Å: DC magnetron sputtering

- 6. Post deposition anneal (PDA)

- 7. Pt deposition ~1500Å: DC magnetron sputtering

- 8. Pt electrode patterning (aqua regia)

- 9. Post-Pt anneal

- 10. Backside aluminum deposition

Table 2.1 Pt/ZrO<sub>2</sub>/Si MOSCAP fabrication process

The starting materials were (100) p-type silicon wafers with a resistivity of  $\sim$ 5-25  $\Omega$ -cm. A 3500Å wet field oxidation was performed in conventional MRL furnaces at 950°C. Wafers were then 1:1 contact patterned and etched using buffered oxide etch (BOE) to form the active areas of the capacitors (5x10<sup>-5</sup> cm<sup>2</sup>). Immediately prior to Zr deposition, the active patterned wafers were piranha cleaned, dipped in HF solution (1:40, HF:H<sub>2</sub>O), and rinsed in deionized (DI) water.

Both Zr and Pt were deposited using a Kurt J. Lesker sputtering machine with a base pressure  $\leq 5.0 \times 10^{-7}$  Torr. Around 20-40Å of Zr was deposited via DC magnetron sputtering of a four inch Zr (99.9%) target. The optimized ZrO<sub>2</sub> deposition conditions were a sputtering power of 200W, an argon (Ar) ambient at 30 mTorr, and temperature of ~25°C. The deposition rate was approximately 120Å of ZrO<sub>2</sub> per minute. Section 2.2.3 will explain how these conditions were chosen.

Post deposition annealing (PDA) served to fully oxidize and densify the ZrO<sub>2</sub>, and was performed in either a conventional furnace or a rapid thermal process (RTP) at temperatures ranging from 500-900°C in nitrogen at atmospheric pressure. Some samples were also annealed after Pt deposition using similar conditions as the PDA. Pt was deposited using DC magnetron sputtering at 300°C at an Ar pressure of 20 mTorr. Pt was wet-etched using aqua regia (H<sub>2</sub>O:HCL:HNO<sub>3</sub>, 5:7:1) at 80°C. Aluminum was deposited on the wafer backside to improve the contact during measurements. ZrO<sub>2</sub> thickness was measured both before and after PDA using a single wavelength ellipsometer with the refractive index (n) fixed at 2.0 for thin films

( $\leq$  60Å). For thicker films, the ellipsometer iterated n to be  $\sim$  1.9-2.0, which agreed with reported values [4,5].

MOSCAP capacitance-voltage (C-V) characteristics were measured using a HP 4194A Impedance/Gain-Phase Analyzer, and leakage current density-voltage (J-V) characteristics were measured using a HP 4156 Precision Semiconductor Parameter Analyzer. J-V measurements were performed by sweeping the MOSCAP gate voltage from 0V to -3V. Then, to prevent any stress-induced leakage effects, gate voltage was swept from 0V to +3V on a different device nearby. For J-V measurements, the optic lights were kept on to provide minority carriers. For all other measurements, the lights were turned off.

Capacitance equivalent thickness (CET) was calculated from the accumulation capacitance ( $C_A$ ) of 1 MHz C-V curves using equation 2.1 where A is capacitor area ( $5 \times 10^{-5} \text{ cm}^2$ ); k is the dielectric constant of SiO<sub>2</sub> (3.9), and  $\epsilon_o$  is the permittivity of free space (8.85 x  $10^{-14}$  F/cm).

$$CET = (k\varepsilon_0 A)/C_A \qquad (2.1)$$

The equivalent oxide thickness (EOT) was determined by deducting the quantum mechanical effect (~2Å) from the CET using the NCSU CVC program [6]; the term EOT will be used throughout this dissertation and implies the quantum mechanical deduction. As for material characterization techniques, XPS was used to analyze the ZrO<sub>2</sub> and interfacial layer (IL) film composition. TEM was used to investigate ZrO<sub>2</sub> and IL thickness, AFM for ZrO<sub>2</sub> surface roughness, and XRD for ZrO<sub>2</sub> crystallinity.

#### **2.2.2 Oxidation of Zr [7]**

One of the most interesting results was the oxidation of the Zr films during the post deposition anneal (PDA) in N<sub>2</sub> ambient. The oxidation could be attributed to two factors. The first factor was that oxygen adsorbs onto the Zr film from the air, and thus the top layers of Zr films could react with this oxygen to form ZrO<sub>2</sub> [8]. The second factor was the presence of residual oxygen in the RTP chamber or furnace during the PDA. Despite the fact that only N<sub>2</sub> was flowing during PDA, both the RTP and furnace were atmospheric pressure systems, so it was impossible to remove all traces of oxygen. The residual oxygen could easily diffuse through the ZrO<sub>2</sub> during the PDA to oxidize the remaining Zr, and finally the Si substrate as well [9].

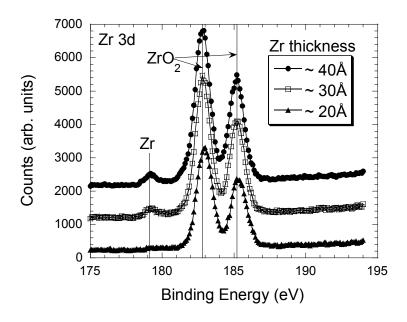

X-ray photoelectron spectroscopy (XPS) data (figure 2.1) confirmed that thin Zr films (~20-40Å) could form ZrO<sub>2</sub> when exposed to air at room temperature. Figure 2.1 shows sputter-deposited Zr films of varying thickness that have been brought into atmosphere, but have not been annealed. As shown, all three films were at least partially oxidized because they all show distinct ZrO<sub>2</sub> chemical bonding energy peaks. Films with an original Zr thickness of 20Å show no signs of a Zr binding energy peak, indicating that they were fully oxidized upon exposure to air. However, thicker Zr films (~30-40Å) were only partially oxidized, and still show a small Zr peak. Thus, the PDA served to fully oxidize and densify the ZrO<sub>2</sub> film.

Figure 2.1 XPS data from three Zr films (~20-40Å) that have been oxidized by exposure to air at room temperature [7].

## 2.2.3 Zr deposition process optimization

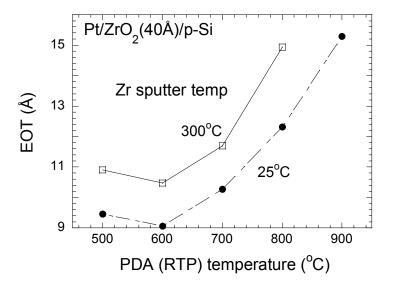

The Zr deposition parameters were optimized in terms of temperature, ambient, target power, and deposition pressure in order to yield ZrO<sub>2</sub> films with low EOT and low leakage current. Deposition temperatures ranging from room temperature (~25°C) to 500°C were attempted, and it was discovered that the higher the deposition temperature, the higher the EOT. This behavior was attributed to outgassing of oxygen from the chamber walls at higher temperatures resulting in interfacial layer growth and higher EOT. Figure 2.2 shows that the EOT of ZrO<sub>2</sub> films deposited at 25°C have lower EOT (~2Å) than those deposited at 300°C. Thus, room temperature was chosen as the optimal deposition temperature.

As for deposition ambient, Ar-only and Ar +  $O_2$  were investigated. Although past experiments using reactively sputtered  $ZrO_2$  (Ar +  $O_2$  ambient) have yielded good electrical and material characteristics [10], samples sputtered in Ar-only have yielded similar characteristics. In addition, the Ar +  $O_2$  process was less repeatable since the  $O_2$  flow into the chamber was controlled manually in cycles [10]. During each cycle, when the  $O_2$  mass flow controller was initially opened, the pressure increased ~20-40 mTorr before settling back down to its set point value. Also, studies have shown that Si with a thin layer of  $ZrO_2$  on top is particularly vulnerable to plasma anodization, which causes rapid  $SiO_2$  growth at the  $ZrO_2/Si$  interface [11], and thus increase in EOT. Consequently, an Ar-only ambient was chosen.

Sputtering target powers ranging from 100-300W were studied. Higher power (300W) resulted in increased sputter damage to the Si substrate, and thus increased leakage current. Low power (100W) had a lower deposition rate, and therefore films were less dense, and also had higher leakage current. Films sputtered at 200W had a high enough deposition rate to yield dense films, and low enough power to minimize sputter damage to the substrate.

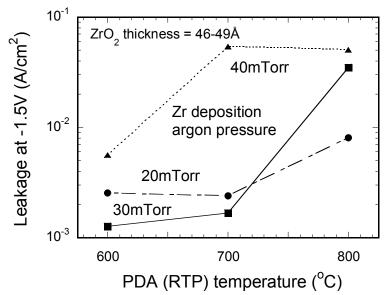

Finally, deposition pressures (Ar-only) of 20-40 mTorr were investigated. High pressure (40 mTorr) resulted in lower deposition rates, and thus less dense film, and higher leakage as seen in figure 2.3. A deposition pressure of 30 mTorr yielded slightly lower leakage characteristics than 20 mTorr at PDA temperatures of 600-700°C (figure 2.3). At 800°C PDA, samples deposited at 20 mTorr had lower

leakage, but as seen in section 2.2.4, the optimal PDA temperature was ~600°C. Consequently, 30 mTorr was chosen to be the optimal deposition pressure.

Figure 2.2 EOT versus PDA temperature for ZrO<sub>2</sub> sputtered at 25°C and 300°C.

Figure 2.3 Leakage at  $V_g$ = -1.5 versus PDA temperature for Zr deposition pressure ranging from 20-40 mTorr.

## 2.2.4 PDA process optimization

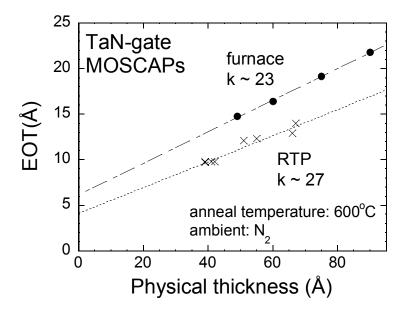

As mentioned earlier, the post deposition anneal (PDA) occurred in either a rapid thermal process (RTP) or a conventional horizontal furnace at temperatures ranging from 500-800°C in  $N_2$  at atmospheric pressure. Because the furnace was a hot-walled process, the wafers were loaded into an ambient at temperatures  $\geq$  400°C. When the wafers were loaded, air (i.e. moisture and  $O_2$ ) could flow into the furnace, and as a result, the amount of residual oxygen in the furnace was fairly high compared to the RTP system. The RTP system was a cold-walled system, meaning that the wafers were loaded at room temperature, and that the chamber could be purged prior to annealing to remove residual  $O_2$ . Therefore, it was not surprising to find that the EOT of RTP annealed samples was lower than that of furnace annealed samples (figure 2.4). Because the RTP was a more controllable process in terms of minimizing residual  $O_2$  and moisture, and thus minimizing EOT and yielding good  $ZrO_2$  film quality, it was chosen as the optimal PDA process.

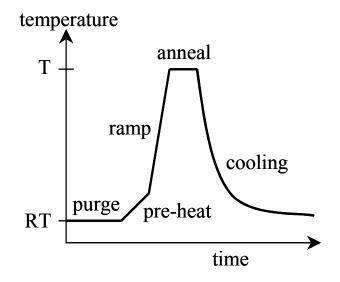

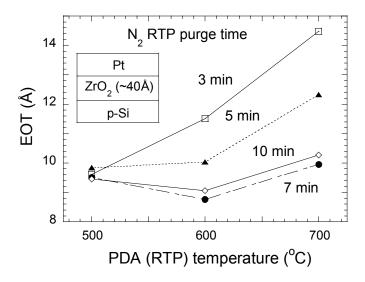

The next step was to optimize the RTP anneal itself. Figure 2.5 shows the basic steps in a RTP anneal: purge, pre-heat, temperature ramp-up, anneal, and cooling. The variables investigated to attain the optimal PDA conditions were purge time, anneal temperature, and anneal time. It was found that residual oxygen in the RTP chamber contributed to interfacial layer growth and thus increased EOT. As expected, longer  $N_2$  purge (8-10 slm) times lowered the amount of residual  $O_2$  and lowered EOT. As seen in figure 2.6, a 7-minute purge time was sufficient to minimize  $O_2$  in the RTP chamber.

Figure 2.4 EOT versus ZrO<sub>2</sub> physical thickness for furnace and RTP annealed samples.

Figure 2.5 Cartoon depiction of a RTP anneal: temperature vs. time.

Figure 2.6 EOT versus PDA temperature shows 7-minute purge was sufficient to minimize EOT growth during annealing [7].

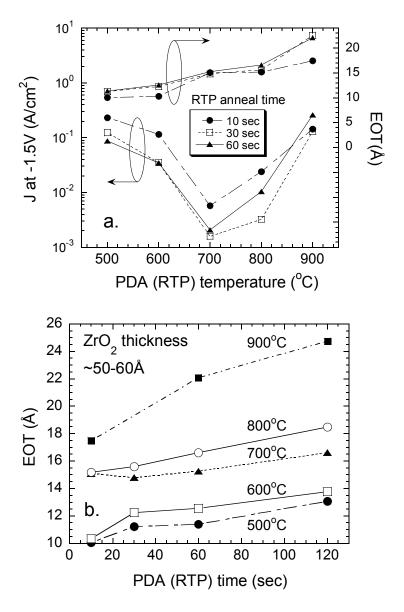

Although the residual  $O_2$  was minimized with the 7-minute purge, it could not be removed completely from the RTP chamber. As a result, EOT values increased with increasing PDA annealing temperature (figure 2.7a) and annealing time (figure 2.7b).

In order to maintain both low EOT and low leakage current, PDA (RTP) conditions were set to a purge time of 7 minutes, anneal temperature of 500-600°C, and anneal time of 10-30 seconds.

Figure 2.7 (a) Leakage current and EOT vs. PDA temperature shows increasing EOT with increasing temperature [7]. (b) EOT vs. PDA time shows increasing EOT with increasing time and temperature [7].

# 2.3 Basic ZrO<sub>2</sub> characteristics

### 2.3.1 Interfacial layer

Although ZrO<sub>2</sub> is thermally stable on Si [12], oxygen can still diffuse through the ZrO<sub>2</sub> to react with the Si to form an interfacial layer (IL). This diffusion can be enhanced by annealing at high temperatures for longer times (figure 2.7). Studies have shown that the growth of this IL can be prevented or controlled by performing the Zr deposition and annealing *in situ* in a vacuum system [13,14]. However, the existence of an IL can be advantageous if it has interface qualities similar to that of SiO<sub>2</sub> on Si. Thus, the IL was investigated in terms of thickness controllability, composition, and morphology.

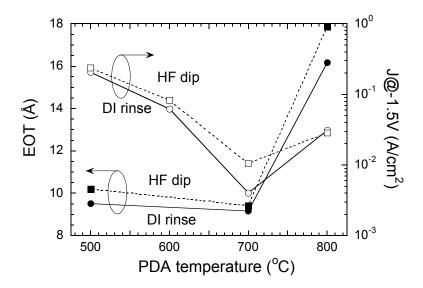

As discussed in section 2.2.4, optimization of the PDA conditions minimized IL growth. From figure 2.4, the IL grown during RTP PDA had an EOT of ~4Å. One concern was that the wafer clean prior to Zr deposition – piranha, HF dip, DI water rinse – may contribute to the IL since the DI water may leave a monolayer or more of SiO<sub>2</sub> on the Si substrate. This concern was addressed with an experiment that compared a HF-last clean with a DI water-last clean. As shown in figure 2.8, there was no significant difference between the EOT or the leakage current (J) of the HF-last and the DI water-last process. Consequently, the DI water rinse-last clean was adopted since it made the wafers safer to handle than the HF-last clean.

Figure 2.8 EOT and J versus PDA temperature are similar for two different cleans - HF-last and DI water-last.

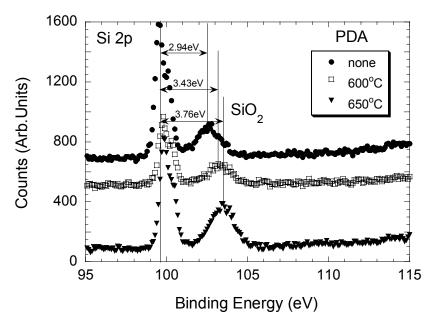

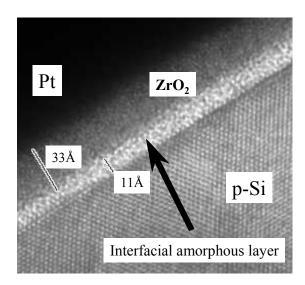

By controlling the PDA conditions, the IL layer thickness could be controlled, but the IL composition was in question. From XPS data, it can be seen that the IL was not  $SiO_2$ , but a  $Zr_xSi_yO_z$  or Zr-silicate layer (figure 2.9). As the PDA temperature increased, the composition shifted from a Zr-silicate towards a more stoichiometric  $SiO_2$ . TEM pictures confirmed that the IL was a Zr-silicate, and not  $SiO_2$ . The TEM in figure 2.10 was taken from a  $Pt/ZrO_2/p$ -Si MOSCAP with an EOT of 12.6Å. If a k of 20 is assumed for the  $ZrO_2$  (33Å) layer, the EOT of the  $ZrO_2$  layer is  $\sim$ 6.4Å. Then the k of the IL (11Å) is calculated to be  $\sim$ 7, which is higher than that of  $SiO_2$  (3.9), indicating that the IL must be a Zr-silicate; additionally, the IL was amorphous (figure 2.10). These results have been confirmed in other  $ZrO_2$  studies where the amorphous Zr-silicate IL had a reported k ranging from 5 to 11 [15,16,17].

Figure 2.9 XPS spectra show that the IL was a Zr-silicate that converts to more stoichiometric SiO<sub>2</sub> after 650°C PDA [10].

Figure 2.10 TEM of Pt/ZrO<sub>2</sub>/Si MOSCAP with EOT of 12.6Å and an amorphous IL composed of Zr-silicate with a dielectric constant of 7.

### 2.3.2 ZrO<sub>2</sub> materials characteristics

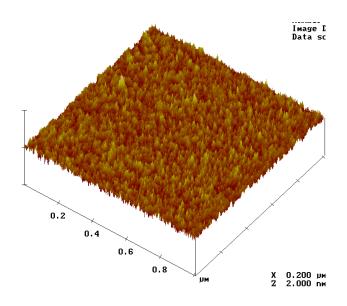

To investigate materials characteristics such as composition, surface roughness, and crystallinity, the ZrO<sub>2</sub> films were subjected to XPS, TEM, AFM, and XRD. XPS data showed that the ZrO<sub>2</sub> films were stoichiometric with Zr:O having a 1:2 ratio. From the TEM in figure 2.10, the ZrO<sub>2</sub> showed smooth interfaces with both the IL/Si substrate and Pt. AFM analysis confirmed that a 50Å-thick ZrO<sub>2</sub> film after PDA was very smooth with a surface roughness value of ~1Å rms (figure 2.11). Other groups have reported similar results with AFM showing surface roughness values of 1-2Å rms [15,18].

Figure 2.11 AFM picture of ZrO<sub>2</sub> (50Å) after 500°C PDA shows surface roughness of 1Å (rms).

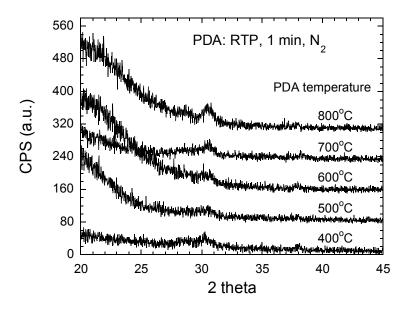

Film crystallization is a concern for high-k gate dielectrics due to possible issues with leakage current paths or impurity diffusion along grain boundaries. In

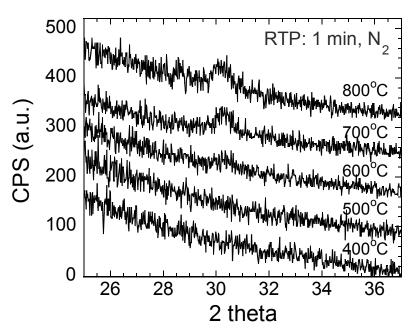

addition, non-uniform grain size and orientation of a polycrystalline dielectric may lead to inconsistent characteristics from device to device [19]. Glancing angle XRD analysis of ZrO<sub>2</sub> (100Å) showed signs of film crystallization after 400°C annealing (figure 2.12). Unfortunately, this crystallization temperature was rather low, although it agreed with other published results [10,20]. However, despite the crystallization, ZrO<sub>2</sub> films yielded low leakage current and consistent electrical characteristics from device to device. ZrO<sub>2</sub> crystallization will be discussed further in section 5.3.2.

Figure 2.12 XRD analysis of ZrO<sub>2</sub> (100Å) films annealed up to 800°C show crystallization after 400°C annealing.

In conclusion, the  $ZrO_2$  films demonstrated stoichiometry, smooth interfaces with the IL/Si and Pt, surface roughness of 1Å rms, and crystallization after 400°C annealing.

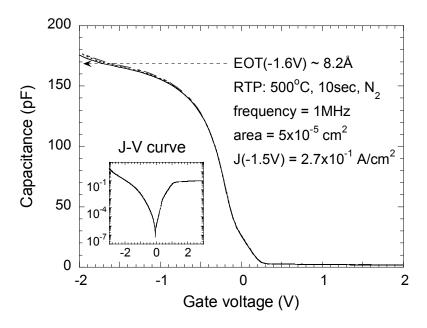

### 2.3.3 Pt/ZrO<sub>2</sub> MOSCAP characteristics [7]

Overall, the Pr/ZrO<sub>2</sub>/Si MOSCAPs produced extremely promising results. The MOSCAPs yielded well behaved C-V curve characteristics and demonstrated EOTs as low as 8.2Å (figure 2.13). Three C-V curves are featured in figure 2.13 to demonstrate the consistent characteristics across the sample. The 8.2Å EOT was calculated from the 1 MHz capacitance at -1.6V; this gate voltage was chosen because capacitance began to increase for voltages lower than -1.6V due to increasing leakage current. This sample had a relatively low leakage current of 2.7x10<sup>-1</sup> A/cm<sup>2</sup> at a gate voltage of -1.5V and a ZrO<sub>2</sub> physical thickness of ~35Å. The leakage current characteristics were also well behaved as shown in the inset to figure 2.13.

Figure 2.13 C-V curves of Pt/ZrO<sub>2</sub>(35Å)/p-Si MOSCAP yielded low EOT ( $\sim$ 8.2Å) and low leakage current (2.7x10<sup>-1</sup> A/cm<sup>2</sup> at V<sub>g</sub>= -1.5V) [7].

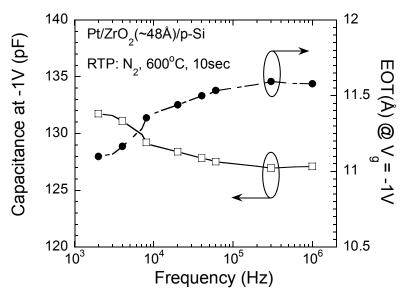

One concern regarding high-k dielectrics is C-V frequency dispersion, which was not a problem with  $ZrO_2$ . Figure 2.14 shows both the capacitance and EOT versus frequency of a  $Pt/ZrO_2(\sim48\text{Å})/p$ -Si capacitor. The EOT only varied from 11.1-11.6Å, and the capacitance varied  $\sim1.3\%$  per decade in the frequency range of 2 kHz to 1 MHz (figure 2.14). The measurement voltage of -1V was chosen so that leakage current would not adversely affect the capacitance values. Leakage at -1V was on the order of  $1.4\times10^{-4}$  A/cm<sup>2</sup>. Other studies have reported negligible  $ZrO_2$  frequency dispersion < 2% per decade [21,10] for frequencies up to 46 GHz [22].

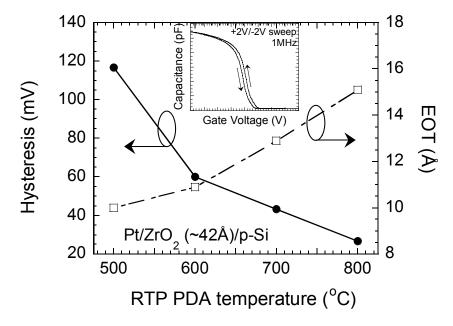

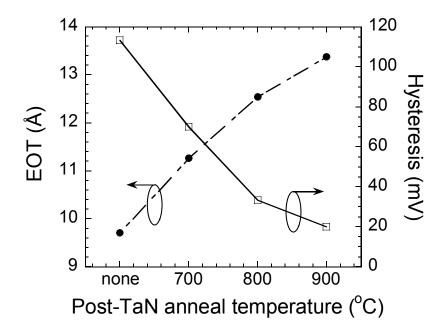

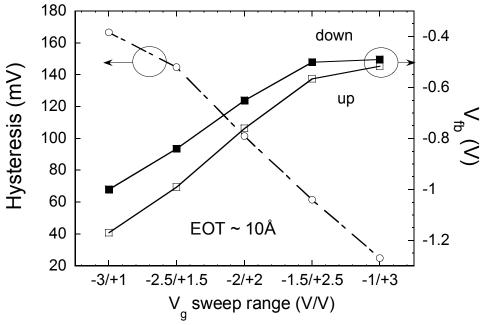

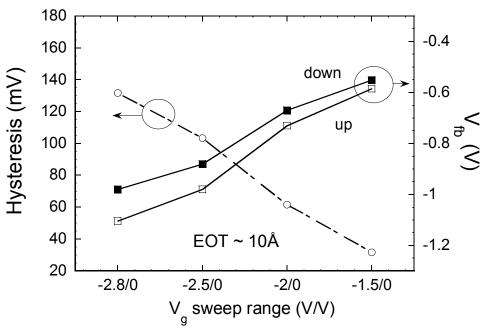

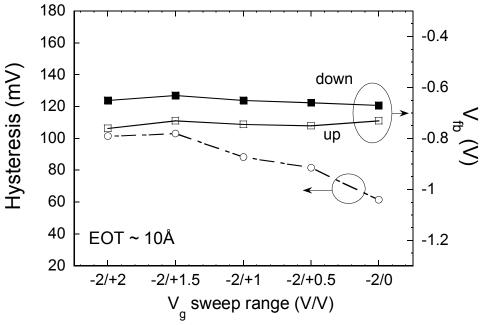

Another concern for high-k gate dielectrics is C-V hysteresis, which results in threshold voltage ( $V_t$ ) instability. These  $ZrO_2$  films typically exhibited a counterclockwise hysteresis loop as shown in the inset to figure 2.15. Hysteresis was measured from 1 MHz C-V curves by sweeping the gate voltage back and forth from -2V to +2V four times before measuring the change in flat band voltage. Typical hysteresis values were  $\sim 50\text{-}60\text{mV}$  for films with EOT < 11Å. Acceptable hysteresis values are considered to be  $\leq 20\text{mV}$ . Hysteresis could be reduced to 20mV with high temperature PDA ( $800^{\circ}\text{C}$ ), but at the cost of increased EOT as shown in figure 2.15. It was speculated that hysteresis might partially be due to damage caused by the Pt sputtering process. Post-Pt RTP annealing was performed at temperatures ranging from  $500\text{-}800^{\circ}\text{C}$  in order to cure the sputtering damage. Indeed the post-Pt annealing did reduce hysteresis, but once again with the tradeoff of increased EOT values similar to the trend shown in figure 2.15. C-V hysteresis will be discussed in more detail in section 4.2.2.

Figure 2.14 Capacitance and EOT at -1V versus C-V frequency of a Pt/ZrO<sub>2</sub>(~48Å)/p-Si MOSCAP showed negligible frequency dispersion [7].

Figure 2.15 C-V Hysteresis decreased while EOT increased with increasing PDA temperature. Inset shows the typical counterclockwise behavior of the C-V hysteresis [7].

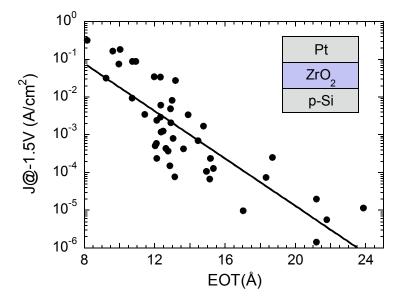

As mentioned earlier, leakage current for these RTP-oxidized  $ZrO_2$  films was fairly low. Figure 2.16 shows the trend of leakage current values measured at -1.5V versus EOT of  $Pt/ZrO_2/p$ -Si capacitors. The gate voltage  $(V_g)$  value of -1.5V was chosen because it approximated a  $V_g$  of flat-band voltage minus 1V. Leakage varied for similar EOT values based on processing conditions. As expected, leakage current decreased with increasing PDA annealing temperature as a result of increased IL thickness.

Overall, the Pt/ZrO<sub>2</sub>/Si MOSCAP characteristics were well behaved and demonstrated low EOT scalability (~8.2Å), negligible frequency dispersion, manageable hysteresis, and low leakage current.

Figure 2.16 Leakage current vs. EOT of Pt/ZrO<sub>2</sub>/p-Si MOSCAPs was low.

## 2.4 Summary

In summary, chapter 2 discussed the optimization of the ZrO<sub>2</sub> process as well as data yielded from the evaluation of Pt-gate MOSCAPs. The Pt/ZrO<sub>2</sub>/Si MOSCAP fabrication process was described in detail as well as the material and electrical characterization techniques. It was found that a thin Zr layer could easily be converted to ZrO<sub>2</sub> by exposure to air, followed by further oxidation and densification in a post deposition anneal (PDA). Both the Zr and the PDA procedures were optimized in terms of both low EOT and low leakage current.

Although ZrO<sub>2</sub> was stable on Si, excess exposure to oxygen resulted in interfacial layer growth. This interfacial layer was composed of an amorphous Zr-silicate layer with a dielectric constant ~5-11, whose Zr concentration (and thus k) decreased with high temperature annealing. ZrO<sub>2</sub> exhibited good material properties such as smooth interfaces with both the Pt electrode and Si substrate; ZrO<sub>2</sub> surface roughness was ~1Å rms. XRD analysis revealed that ZrO<sub>2</sub> was already crystallized after 400°C annealing, although device leakage was low and uniform from device to device.

As for MOSCAP characteristics, EOTs as low as 8.2Å were achieved with low leakage current. C-V characteristics such as dispersion and hysteresis were negligible with the proper process conditions. The leakage current versus EOT trend of ZrO<sub>2</sub> demonstrated encouraging low leakage current. Overall, the results were extremely promising, and ZrO<sub>2</sub> has proven itself a viable candidate for high-k gate

dielectric material. The following chapters will delve deeper into the device and materials characteristics of  $ZrO_2$ .

### 2.5 References

- [1] J.H. Kim, S.I. Woo, B.Y. Nam, and W.J. Yoo, "Anisotropic Etching Characteristics of Platinum Electrode for Ferroelectric Capacitor," IEEE Transactions on Electron Devices, vol. 46, no. 5, p. 984, 1999.

- [2] C.M. Soriano, "Platinum," IEEE Potentials, vol. 16, no. 5, p. 29, 1998.

- [3] S.P. Murarka, "Rapid thermal processing for reproducible formation of the self-aligned silicides of cobalt and platinum," Proceedings of the IEEE/SEMI Advanced Semiconductor Manufacturing Conference, p. 211, 1992.

- [4] M.A. Russak, C.V. Jahnes, and E.P. Katz, "Reactive magnetron sputtered zirconium oxide and zirconium silicon oxide," Journal of Vacuum Science & Technology A, vol. 7, no. 3, p. 1248, 1989.

- [5] M.A. Cameron and S.M. George, "ZrO<sub>2</sub> film growth by chemical vapor deposition using zirconium tetra-*tert*-butoxide," Thin Solid Films, vol. 348, p. 90, 1999.

- [6] J.R. Hauser and K. Ahmed, *Characterization and Metrology for ULSI Technology*, (AIP, New York, 1998), p. 235.

- [7] R. Nieh, W.J. Qi, B.H. Lee, L. Kang, Y. Jeon, K. Onishi, S. Gopalan, C.S. Kang, E. Dharmarajan, R. Choi, and J.C. Lee, "Processing effects and electrical characterization of ZrO<sub>2</sub> formed by the RTP oxidation of Zr," Proceedings of the 5th International Symposium on Low and High Dielectric Constant Materials: Materials Science, Processing, and Reliability Issues Session of the 197th Electrochemical Society Meeting, p. 214, 2000.

- [8] E.E. Khawaja, F. Bouamrane, A.B. Hallak, M.A. Daous, and M.A. Salim, "Observation of oxygen enrichment in zirconium oxide films," Journal of Vacuum Science & Technology A, vol. 11, no. 3, p. 580, 1993.

- [9] B.W. Busch, W.H. Schulte, E. Garfunkel, T. Gustafsson, W.-J. Qi, R. Nieh, and J.C. Lee, "Oxygen exchange and transport in thin zirconia films on Si(100)," Physical Review B, vol. 62, no. 20, p. R13290, 2000.

- [10] W.J. Qi, "Study on High-k Dielectrics as Alternative Gate Insulators for 0.1μm and Beyond ULSI Applications," Ph.D. dissertation, The University of Texas at Austin, 2000.

- [11] B. Pelloie, J. Perriere, J. Siejka, P. Debenest, A. Straboni, and B. Vuillermoz, "Investigation of ionic transport mechanisms during plasma anodization of Si and Si through ZrO<sub>2</sub>," Journal of Applied Physics, vol. 63, no. 8, p. 2620, 1988.

- [12] K.J. Hubbard and D.G Schlom, "Thermodynamic stability of binary oxides in contact with silicon," Journal of Materials Research, vol. 11, no. 11, p. 2757, 1996.

- [13] J.-P. Maria, D. Wicaksana, A.I. Kingon, B. Busch, H. Schulte, E. Garfunkel, and T. Gustafsson, "High temperature stability in lanthanum and zirconia-based gate dielectrics," Journal of Applied Physics, vol. 90, no. 7, p. 3476, 2001.

- [14] H. Watanabe, "Interface engineering of a ZrO<sub>2</sub>/SiO<sub>2</sub>/Si layered structure by *in situ* reoxidation and its oxygen-pressure-dependent thermal stability," Applied Physics Letters, vol. 78, no. 24, p. 3803, 2001.

- [15] J.P. Chang and Y.-S. Lin, "Dielectric properties and conduction mechanism of ultrathin zirconium oxide films," Applied Physics Letters, vol. 79, no. 22, p. 3666, 2001.

- [16] B.-O. Cho, J. Wang, L. Sha, and J.P. Chang, "Tuning the electrical properties of zirconium oxide thin films," Applied Physics Letters, vol. 80, no. 6, p. 1052, 2002.

- [17] T.P. Ma, "High-k Gate Dielectrics for Scaled CMOS Technology," Proceedings of the 6<sup>th</sup> International Conference on Solid-State and Integrated Circuit Technology, p. 297, 2001.

- [18] J.P. Chang, Y.-S. Lin, and K. Chu, "Rapid thermal chemical vapor deposition of zirconium oxide for metal-oxide-semiconductor field effect transistor application," Journal of Vacuum Science & Technology B, vol. 19, no. 5, p. 1782, 2001.

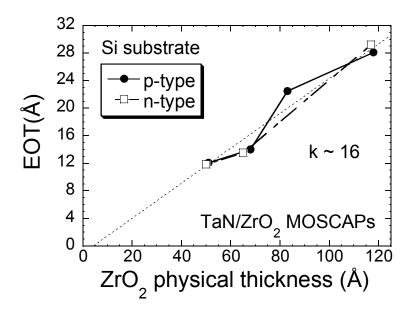

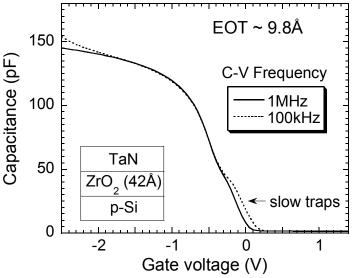

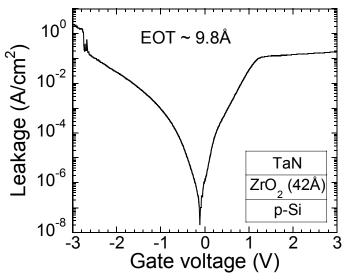

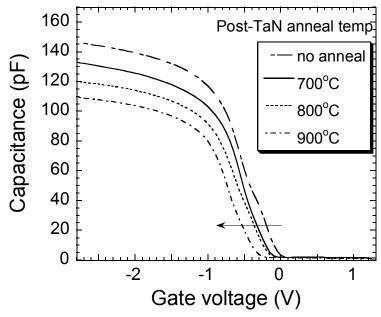

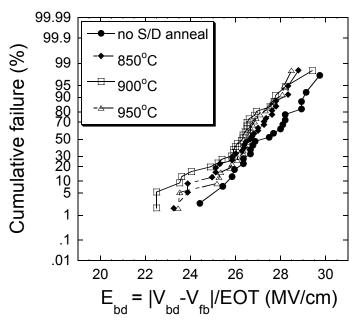

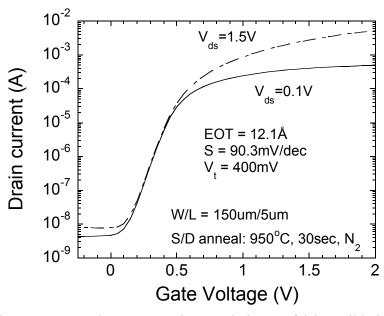

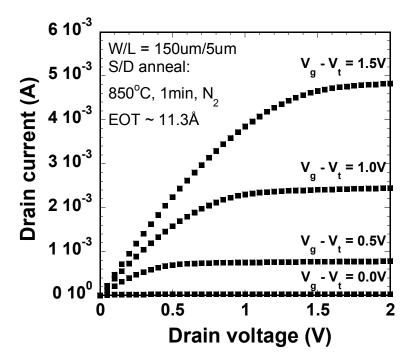

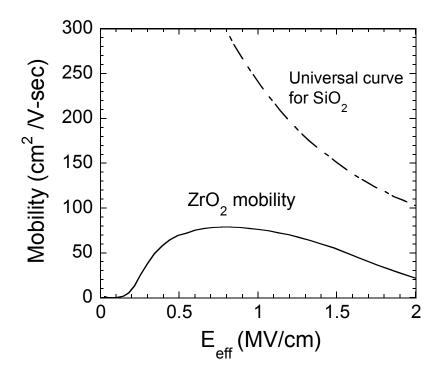

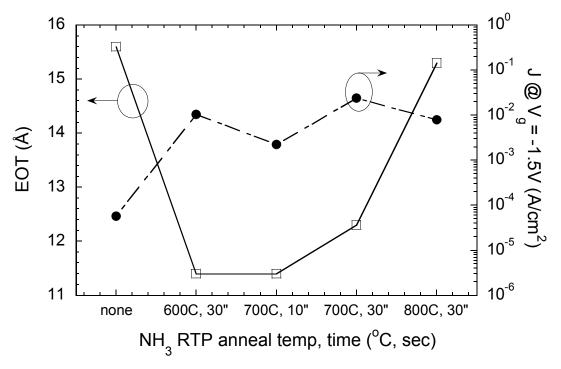

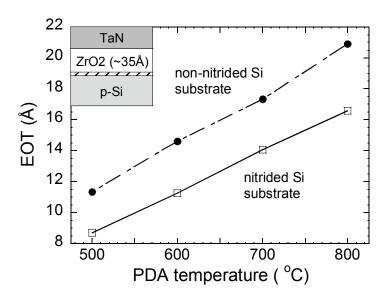

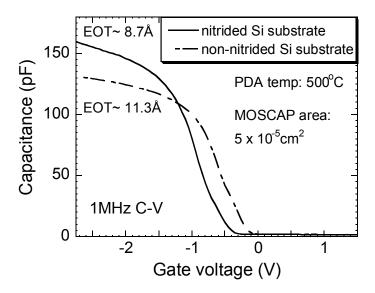

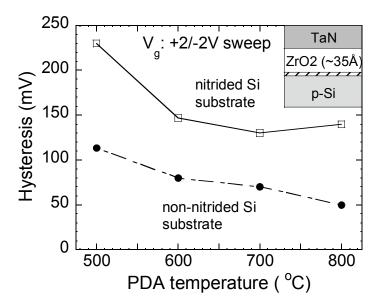

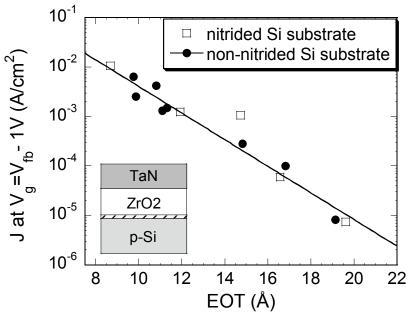

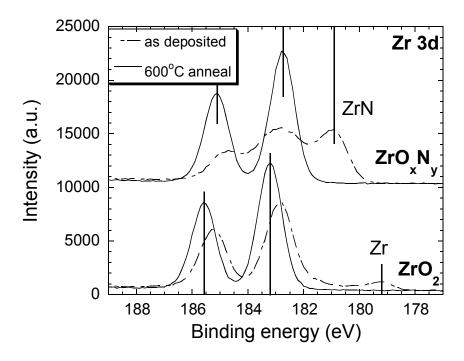

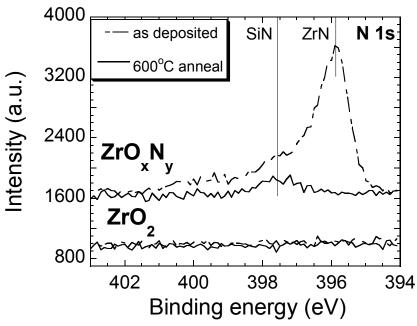

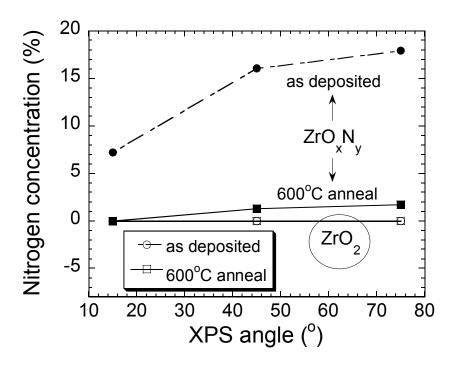

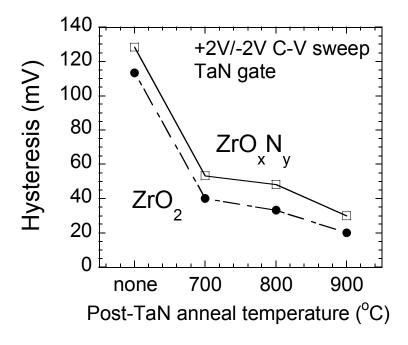

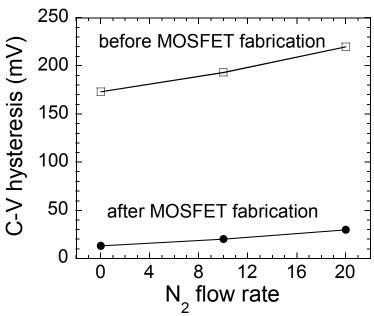

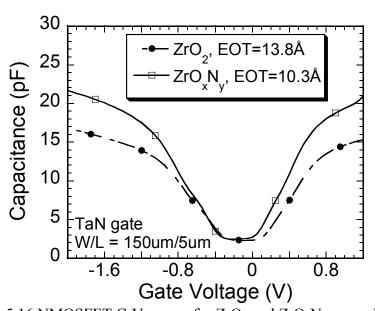

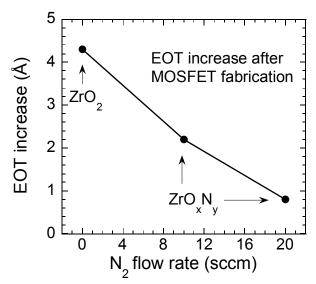

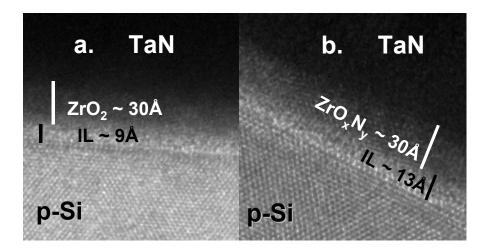

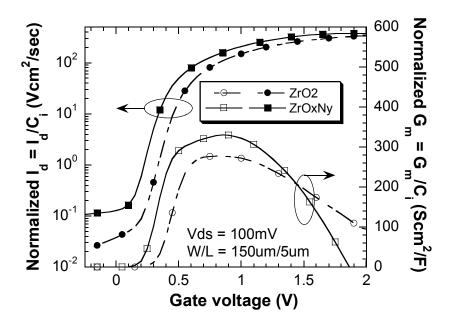

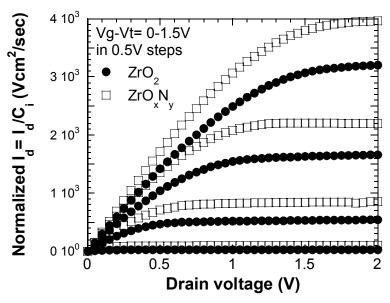

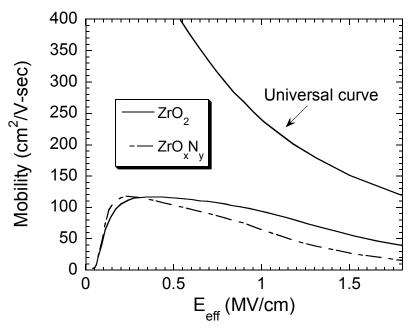

- [19] G.D. Wilk, R.M. Wallace, and J.M. Anthony, "High-k gate dielectrics: Current status and materials properties considerations," Journal of Applied Physics, vol. 89, no. 10, p. 5243, 2001.