Copyright by Sangkug Lym 2019 The Dissertation Committee for Sangkug Lym certifies that this is the approved version of the following dissertation:

# Efficient Deep Neural Network Model Training by Reducing Memory and Compute Demands

Committee:

Mattan Erez, Supervisor

Andreas Gerstlauer

Michael Orshansky

Sujay Sanghavi

Jason Clemons

# Efficient Deep Neural Network Model Training by Reducing Memory and Compute Demands

by

Sangkug Lym

### DISSERTATION

Presented to the Faculty of the Graduate School of The University of Texas at Austin in Partial Fulfillment of the Requirements for the Degree of

## DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN

December 2019

Dedicated to my wife, Jung Min Lee and my parents, Chun Geun Lim and Young Seok Choi.

## Acknowledgments

First and foremost, I would like to thank my advisor Mattan Erez. Without his advice and guidance, I could have not accomplished this dissertation. He provided insightful critiques on my research work from high-level directions to technical details. He was always available and willing to join me in discussions to resolve my curiosity and problems. Importantly, I am very grateful to him for giving me great freedom in exploring and deciding research topics. This dissertation was impossible without his strong support for me to pursue what I desired to do and his willingness to expand his research expertise. Other than just research, I also learned many life lessons from him. I was privileged that I could pursue my Ph.D. with Mattan and no words can describe how much I appreciate him as an adviser.

I am grateful for the superb collaborators and mentors at NVIDIA: Donghyuk Lee, Micheal O'Connor, Niladrish Chatterjee, Jason Clemons, Burc Eryilmaz, Michael Andersch, and John Tran. I especially thank Donghyuk Lee for closely working with me. I appreciate their knowledge, experience, and advice. Thanks to their help, I could learn many important details on GPU architecture and industry-level deep learning performance optimization techniques. My experience at NVIDIA became the tipping point to research deep learning accelerators and led to this dissertation. I also thank many outstanding collaborators and managers at Microsoft including Haishan Zhu, Ming Liu, Taesik Na, and Eric Chung. My internship at Microsoft was important in expanding my knowledge boundary associated with deep learning acceleration to FPGA and data center context. Also, technical discussions with my collaborators at Microsoft helped advance my thought process.

I also would like to show appreciation to professors and academic collaborators for their advice and feedback to improve my work. Especially, I thank Sujay Sanghavi for providing critical feedback on the algorithm side of my work and Songjun Lee at Hanyang University for encouraging me to start Ph.D. studies. I also thank my student collaborators: Wei Wen at Duke University and Heonjae Ha at Stanford University for their feedback that improves the quality of my research.

In addition, I am fortunate to know many talented graduate students during my Ph.D. I would like to give special thanks to Yongkee Kwon, Siavash Zangeneh, Benjamin Cho, Esha Choukse, Kyushick Lee, and Chun-Kai Chang for sharing their experience and motivating me to continuously improve my work through active discussions. I am also thankful to the senior members who encouraged me and provided me many research tips: Jungrae Kim, Don Wan Kim, Seong-Lyong Gong, and Wooseok Lee. I also thank other my Ph.D. friends at our research group: Song Zhang, Wenqi Yin, Tianhao Zheng, Anyesha Ghosh, Majid Jalili, Mike Sullivan. And, I am grateful for the friendship with many others: Alex Hsu, Ben Lin, Ali Fakhrzadehgan, Tian Tan, Jeageun Jung, Mochamad Asri, Kishore Punniyamurthy, Kamyar Mirzazad Barijou, Zhuoran Zhao, and Shuang Song.

Lastly but not least, I would like to express the deepest gratitude to my loving family. I thank my parents Chungeun Lim and Youngseok Choi and my brother Sanghyun Lym for their strong support for my decision to pursue Ph.D. studies. Most importantly, I thank my wife Jung Min Lee for being always there with me. This dissertation would never have been made without her love and care. Lastly, I would like to say to her that we made it together.

Sangkug Lym

December 2019, Austin, TX

# Efficient Deep Neural Network Model Training by Reducing Memory and Compute Demands

Publication No.

Sangkug Lym, Ph.D. The University of Texas at Austin, 2019

Supervisor: Mattan Erez

Deep neural network models are commonly used in various real-life applications due to their high prediction accuracy for different tasks. In particular, CNN (convolutional neural network) models have become the de facto choices for most vision applications such as image classification, object segmentation, and object detection. Modern CNN models contain hundreds of million of parameters and training them requires millions of computation- and memory access-heavy iterations. To reduce this expensive CNN model training cost, this dissertation presents computation and memory cost-efficient training mechanisms with a combination of workload scheduling, learning algorithm, and accelerator architecture optimizations. This dissertation also introduces a performance model for data-parallel accelerators as a fast and accurate method to estimate the performance impact of the proposed architectural optimizations and to help fine-grain accelerator design space exploration. The first part of this dissertation discusses reducing the memory bandwidth demand for CNN training. I first analyze data reuse opportunities in CNN training and show that CNN training has high data locality between network layers but that conventional training mechanisms fail to utilize this inter-layer locality. Then, I develop a CNN training scheduling mechanism that modifies the network execution ordering in a way that captures the inter-layer locality while supporting high compute resource utilization. I also introduce a training accelerator that adopts architectural optimizations that hide additional data transfers caused by the proposed scheduling modification and realize effective training speedup. The proposed training accelerator has 45 mixed precision FLOPS and, with the memory bandwidth-efficient network training scheduling, beats a state-of-the-art GPU that has  $\sim 3X$  higher peak FLOPs.

The second part of this dissertation focuses on reducing the computation cost of CNN training. To reduce computations during training, I use neural network model pruning from the beginning of training. The insight is that a fully trained CNN model contains many non-critical parameters and pruning such parameters during training has only a minor impact on the learning quality. I also choose to structurally prune these parameters to provide high data parallelism avoiding complex data indexing, thus maintaining high compute resource utilization. For the practical implementation of pruning while training, I propose three algorithmic optimizations. Theses optimizations are designed to remove the need for the memory accesses caused by tensor reshaping, reduce the number of training runs in finding the desired pruning hyper-parameters, and maintain high data parallelism even for processing a highly pruned CNN model. Overall, the proposed algorithm speeds up the training of commonly used state-of-the-art image classifiers by 39% with only 1.9% accuracy loss.

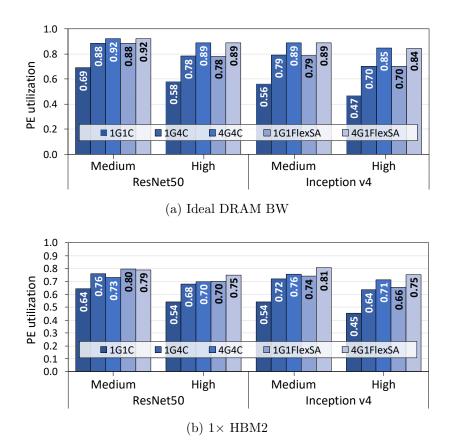

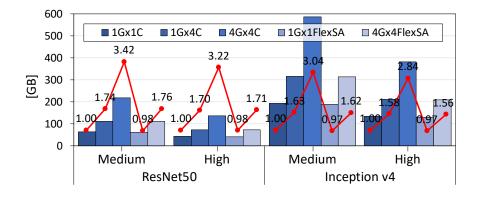

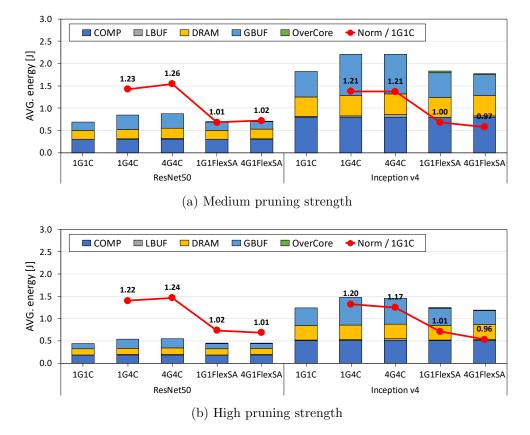

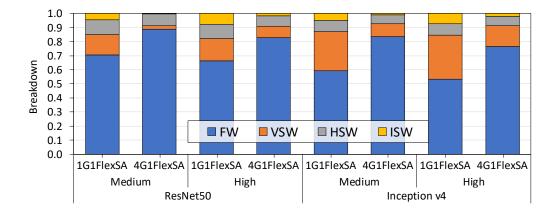

The third part of this dissertation deals with training pruned CNN models on accelerators with large systolic arrays. I first show my observation that processing structurally-pruned CNN models on a large systolic array severely underutilizes its PEs (processing elements) because the reduced number of channels decreases parallelism. Then, I show that naively splitting a large core into multiple small cores improves PE utilization but decreases input reuse and incurs >4% area overhead. To improve PE utilization and maintain high input reuse, I propose a flexible systolic array architecture that can reconfigure its structure to one of several modes, each designed for efficient execution of CNN layers with different dimensions. I also develop compile-time heuristics that optimize mapping the layer workload to the flexible systolic array resources for both high performance and energy efficiency. My new mechanisms increase PE utilization by 36% compared to a single large-core design and improve training energy efficiency by 18% compared to many-small-core designs.

The last part of this dissertation is about developing an accelerator performance model for accurate CNN execution time estimation. For accurate performance modeling, I introduce a memory traffic model that predicts the data traffic at different levels of the GPU memory system hierarchy. This involves an in-depth analysis of the memory access patterns of data-parallel convolution kernels and the spatial locality. I demonstrate that the proposed performance model can provide guideline to fine-tune the GPU resources for efficient CNN performance scaling.

# Table of Contents

| Ackno   | wledgments                                                  | v     |

|---------|-------------------------------------------------------------|-------|

| Abstra  | nct                                                         | viii  |

| List of | Tables                                                      | xvii  |

| List of | Figures                                                     | xviii |

| Chapte  | er 1. Introduction                                          | 1     |

| 1.1     | High Memory Bandwidth Needs in CNN Training                 | 2     |

| 1.2     | Model Pruning for Cost-efficient CNN Training               | 3     |

| 1.3     | Efficient Pruned Model Training on High-Throughput Acceler- |       |

|         | ators                                                       | 3     |

| 1.4     | The Need for an Accurate Performance Model                  | 5     |

| 1.5     | Thesis Statement                                            | 6     |

| 1.6     | Contributions                                               | 6     |

| 1.7     | Dissertation Organization                                   | 10    |

| Chapte  | er 2. Background                                            | 11    |

| 2.1     | CNN Architecture and Training                               | 11    |

| 2.2     | Neural Network Model Pruning for Fast Inference             | 16    |

|         | 2.2.1 Trial-and-Error Based Structured Model Pruning        | 16    |

|         | 2.2.2 Model Pruning with Parameter Regularization           | 17    |

| 2.3     | Training Accelerator Architecture                           | 17    |

|         | 2.3.1 GPU Architecture                                      | 17    |

|         | 2.3.2 Systolic-Arrays                                       | 18    |

| 2.4     | Data-parallel Convolution GEMM                              | 19    |

|         |                                                             |       |

| Chapt | er 3.           | CNN Training with Inter-layer Data Reuse                | 21       |

|-------|-----------------|---------------------------------------------------------|----------|

| 3.1   | Data            | Reuse in CNN Training                                   | 21       |

| 3.2   |                 | bry BW-Efficient CNN Training with                      | <b>.</b> |

|       |                 | Batch Serialization                                     | 24       |

|       | 3.2.1           | I I I I I I I I I I I I I I I I I I I                   | 24       |

|       | 3.2.2           | Layer Grouping Optimizes Reuse                          | 25       |

|       | 3.2.3           | Data Reuse Within a Multi-Branch Module                 | 28       |

|       | 3.2.4           | Feature Normalization in MBS                            | 29       |

| 3.3   | Efficie<br>Wave | ent MBS Training on the Core Accelerator                | 31       |

|       | 3.3.1           | MBS Training on a Systolic Array                        | 31       |

|       | 3.3.2           | Gapless Waves with Per-Register Weight Double Buffering | 34       |

|       | 3.3.3           | WaveCore Processor Architecture                         | 35       |

|       | 3.3.4           | Area and Peak Power Estimation                          | 37       |

| 3.4   | Evalu           | ation                                                   | 39       |

|       | 3.4.1           | Evaluation Methodology                                  | 39       |

|       | 3.4.2           | Evaluation Results                                      | 41       |

|       |                 | 3.4.2.1 Sensitivity to Global Buffer Size               | 43       |

|       |                 | 3.4.2.2 Sensitivity to DRAM BW                          | 44       |

|       |                 | 3.4.2.3 Performance Comparison to GPU                   | 45       |

|       |                 | 3.4.2.4 Systolic Array Utilization                      | 46       |

| 3.5   | Relat           | $\operatorname{ed}$ work                                | 47       |

|       | 3.5.1           | Inter-layer Data Reuse in Inference                     | 47       |

|       | 3.5.2           | Layer Fusion                                            | 48       |

|       | 3.5.3           | Compiler Techniques for Graph Scheduling                | 49       |

| 3.6   | Discu           | ssion                                                   | 49       |

|       |                 | Feature Normalization for CNNs with Few Channels        | 49       |

|       | 3.6.2           | Different Core Designs for Matrix Operations            | 50       |

|       | 3.6.3           | Resource Pipelining using Fine-grain Layer Fusion       | 52       |

|       | 3.6.4           | Balancing Matrix and Vector Computing Units             | 53       |

|       | 3.6.5           | Applying MBS to Other DNN Models                        | 54       |

| 3.7   | Sumn            | nary                                                    | 55       |

|       |                 |                                                         |          |

| Chapter 4. |        |            | Iodel Training with Dynamic Sparse Model figuration                     | 57 |

|------------|--------|------------|-------------------------------------------------------------------------|----|

| 4.1        | Motiv  | ration for | Continuous Model Pruning During Training                                | 57 |

| 4.2        | Mode   | l Prunin   | g Mechanism                                                             | 61 |

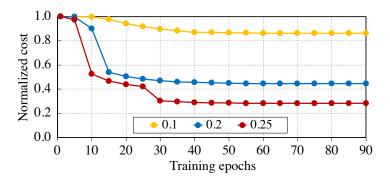

|            | 4.2.1  | Regular    | ization Penalty Coefficient Setup                                       | 63 |

|            | 4.2.2  | Layer F    | temoval by Overlapping Regularization Groups .                          | 64 |

| 4.3        | Dyna   | mic Netv   | vork Reconfiguration                                                    | 65 |

|            | 4.3.1  | Early V    | Veight Pruning                                                          | 65 |

|            | 4.3.2  | Robust     | ness to Reconfiguration Interval                                        | 67 |

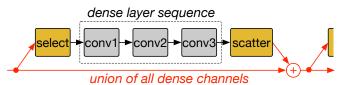

|            | 4.3.3  | Channe     | l Union for CNNs with Short-cut Connections .                           | 68 |

|            | 4.3.4  | Dynam      | ic Mini-batch Adjustment                                                | 71 |

| 4.4        | Evalu  | ation .    |                                                                         | 73 |

|            | 4.4.1  | Evaluat    | ion Methodology                                                         | 73 |

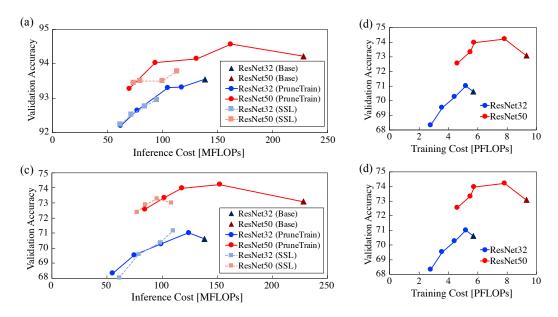

|            | 4.4.2  | Model 1    | Pruning and Training Acceleration                                       | 73 |

|            | 4.4.3  | Compar     | rison to Prior Work                                                     | 78 |

|            |        | 4.4.3.1    | Comparison to Pruning From a Pre-trained Model                          | 78 |

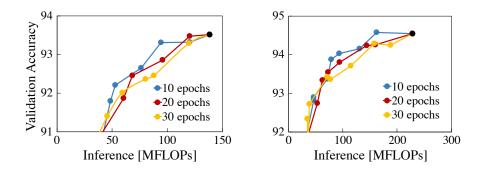

|            |        | 4.4.3.2    | Comparison to Trial-and-Error Based Pruning .                           | 79 |

|            | 4.4.4  | Optimiz    | zation and Sensitivity Evaluation                                       | 80 |

|            |        | 4.4.4.1    | Dynamic Mini-Batch Size Adjustment                                      | 80 |

|            |        | 4.4.4.2    | Network Reconfiguration Interval                                        | 83 |

|            |        | 4.4.4.3    | Communication Cost Savings in Distributed<br>Training                   | 84 |

|            |        | 4.4.4.4    | Communication Cost Savings in Distributed<br>Training                   | 84 |

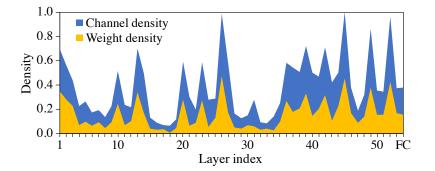

|            |        | 4.4.4.5    | Individual Weight Sparsity                                              | 85 |

| 4.5        | Discu  | ssion .    |                                                                         | 86 |

|            | 4.5.1  | PruneT     | rain with Mini-batch Serialization                                      | 86 |

| 4.6        | Summ   | nary       |                                                                         | 87 |

| Chapter 5. |        |            | le Systolic Array Architecture for Fast and<br>at Pruned Model Training | 89 |

| 5.1        | Challe | enges of   | Training Pruned CNN Models                                              | 90 |

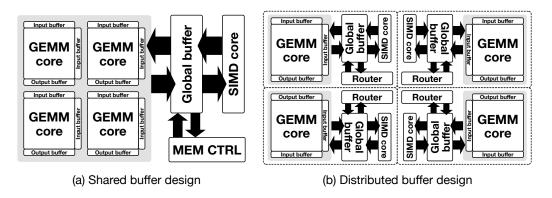

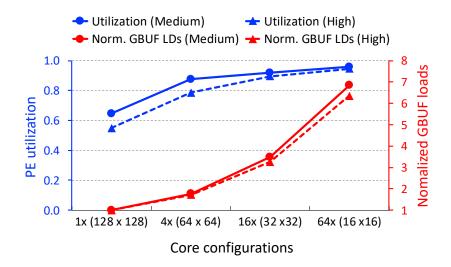

|            | 5.1.1  | Trade-o    | ffs of Different GEMM Core Designs                                      | 90 |

| 5.2        | Naive  | GEMM       | Core Splitting                                                          | 92 |

| 5.3        | FlexS<br>PE U | A: Flexible Systolic Array for High<br>tilization and Input Reuse | 97  |

|------------|---------------|-------------------------------------------------------------------|-----|

|            | 5.3.1         | FlexSA Core Architecture                                          | 98  |

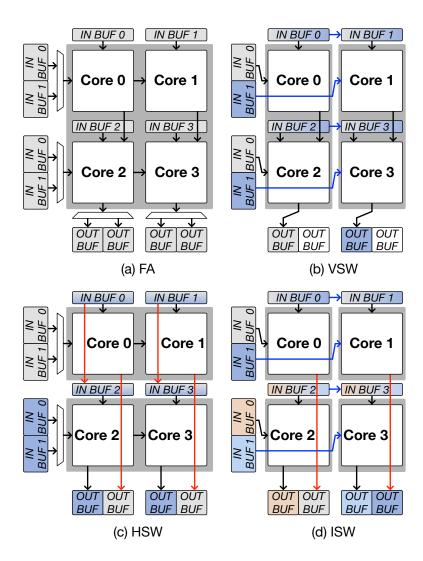

|            | 5.3.2         |                                                                   | 103 |

|            |               |                                                                   | 104 |

|            |               | 5.3.2.2 ISA Support and Compilation for GEMM Pro-                 |     |

|            |               | cessing                                                           | 106 |

| 5.4        | Evalu         | ation                                                             | 109 |

|            | 5.4.1         | Evaluation Methodology                                            | 109 |

|            |               | 5.4.1.1 GEMM Partitioning and Blocking                            | 110 |

|            | 5.4.2         | Evaluation Results                                                | 111 |

|            |               | 5.4.2.1 On-chip Traffic and Energy Efficiency                     | 113 |

|            |               | 5.4.2.2 FlexSA Operating Mode Breakdown                           | 115 |

| 5.5        | Sumn          | nary                                                              | 116 |

| Chapter 6. |               | GPU Memory Traffic and Performance Models for                     |     |

|            |               |                                                                   | 18  |

| 6.1        |               |                                                                   | 118 |

|            |               |                                                                   | 119 |

| 6.2        | -             |                                                                   | 120 |

| 6.3        | Memo          |                                                                   | 122 |

|            | 6.3.1         |                                                                   | 123 |

|            | 6.3.2         | L2 Cache Traffic                                                  | 124 |

|            | 6.3.3         | DRAM Traffic                                                      | 126 |

| 6.4        | GPU           | Performance Modeling                                              | 128 |

|            | 6.4.1         | Multi-CTA Interleaving                                            | 130 |

| 6.5        | Evalu         | ation                                                             | 132 |

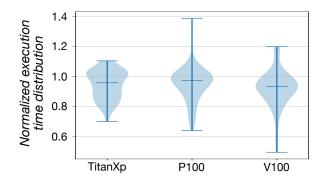

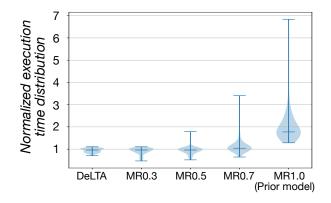

|            | 6.5.1         | Evaluation Environment                                            | 132 |

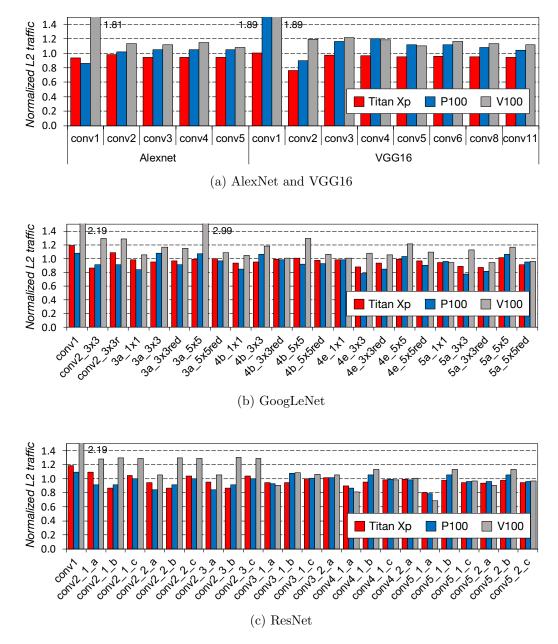

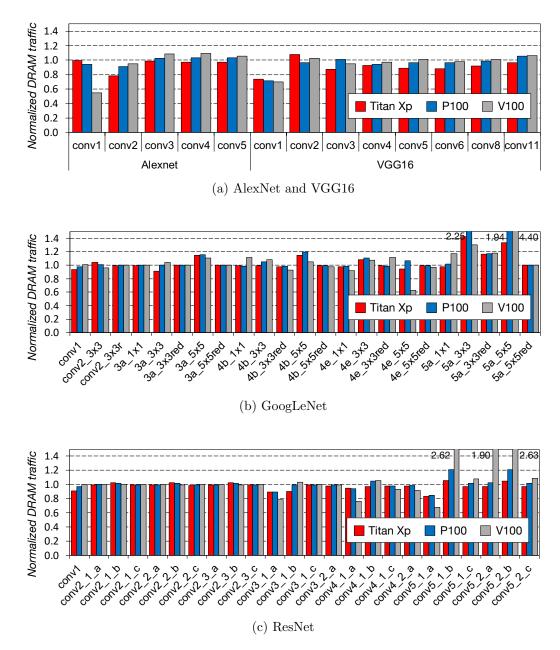

|            | 6.5.2         | Memory Traffic Model                                              | 133 |

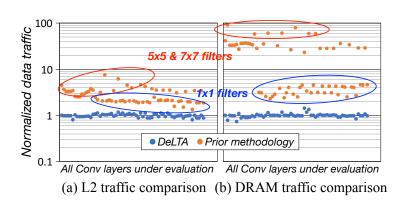

|            | 6.5.3         | Performance Model                                                 | 139 |

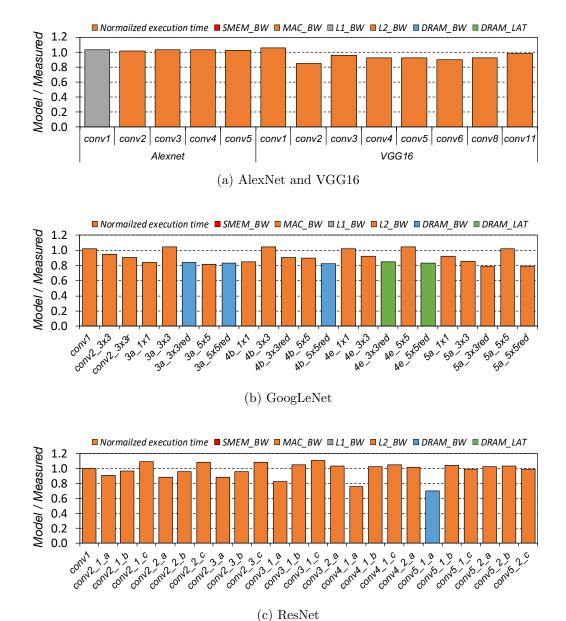

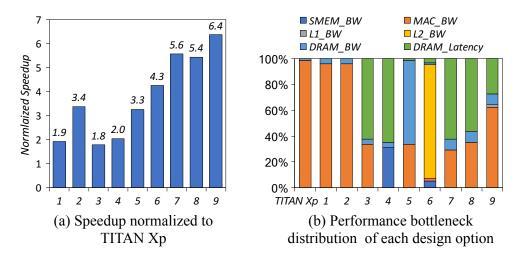

|            | 6.5.4         | Fine-grain GPU Performance Scaling Study                          | 142 |

| 6.6        | Discu         | ssion: Generalization of DeLTA                                    | 144 |

| 6.7        | Sumn          | nary                                                              | 146 |

| Chapter 7. Conclusion | 147 |

|-----------------------|-----|

| Bibliography          | 150 |

| Vita                  | 170 |

# List of Tables

| 3.1 | WaveCore accelerator specification and comparison to other training accelerators.                           | 38  |

|-----|-------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | Evaluation configuration description.                                                                       | 40  |

| 3.3 | Off-chip memory configuration.                                                                              | 40  |

| 4.1 | Training FLOPs and time compared to the dense baseline                                                      | 74  |

| 4.2 | Inference performance comparison                                                                            | 76  |

| 4.3 | Pruning performance comparison to AMC                                                                       | 79  |

| 4.4 | Training time, inference FLOPs, and validation accuracy with and without dynamic mini-batch size adjustment | 83  |

| 5.1 | Evaluation configuration description.                                                                       | 110 |

| 6.1 | GPU device specifications                                                                                   | 133 |

| 6.2 | GPU design options                                                                                          | 143 |

|     |                                                                                                             |     |

# List of Figures

| 2.1  | CNN architecture                                                                     | 12 |

|------|--------------------------------------------------------------------------------------|----|

| 2.2  | Im2col conversion                                                                    | 19 |

| 3.1  | Inter-layer data<br>flows in CNN training                                            | 22 |

| 3.2  | Inter-layer data size of each layer in ResNet50 $\ldots$                             | 23 |

| 3.3  | Block information of ResNet50 for MBS $\ldots \ldots \ldots \ldots$                  | 25 |

| 3.4  | ResNet50 training flow by baseline and MBS. $\ldots$ .                               | 26 |

| 3.5  | ResNet50 validation error trained with $\mathrm{GN}$ + MBS and BN. $% \mathrm{GN}$ . | 29 |

| 3.6  | Pre-activation mean of normalization layers in ResNet50 $$                           | 30 |

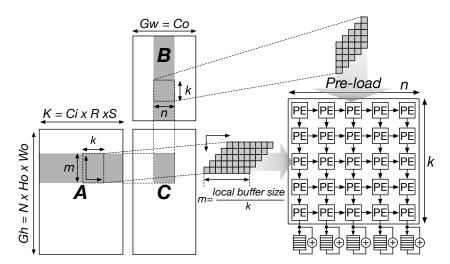

| 3.7  | Tiled GEMM mapping to the systolic array                                             | 32 |

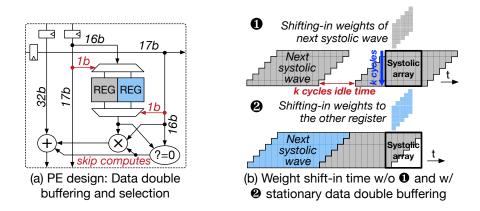

| 3.8  | Removed inter-wave idle time by register double buffering                            | 32 |

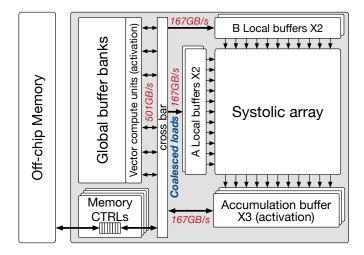

| 3.9  | Per-core architecture of the WaveCore accelerator                                    | 36 |

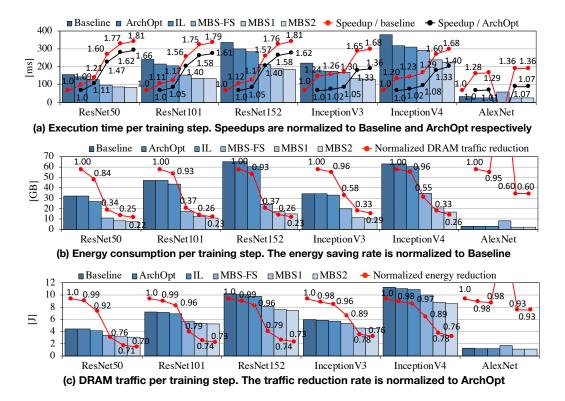

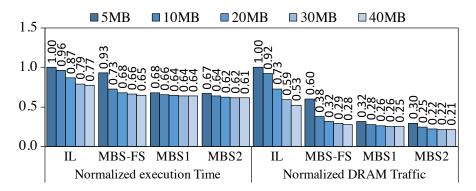

| 3.10 | Performance, DRAM traffic, and energy consumption by con-<br>figurations             | 42 |

| 3.11 | Performance sensitivity to global buffer size                                        | 44 |

| 3.12 | Performance sensitivity to DRAM bandwidth                                            | 45 |

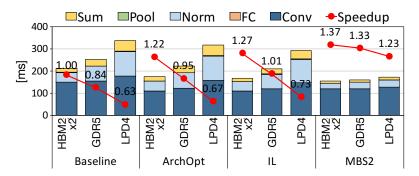

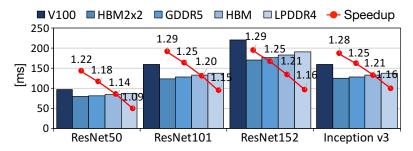

| 3.13 | Performance comparison to GPU                                                        | 46 |

| 3.14 | Systolic Array Utilization                                                           | 47 |

| 3.15 | Validation loss of ResNet32 with SBN trained on CIFAR $\ . \ . \ .$                  | 51 |

| 3.16 | Output stationary systolic dataflow                                                  | 52 |

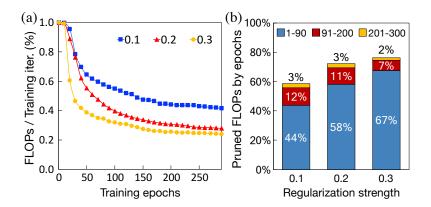

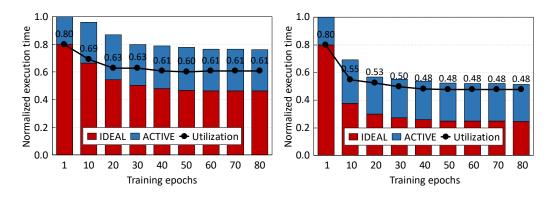

| 4.1  | Normalized pruned FLOPs during training                                              | 60 |

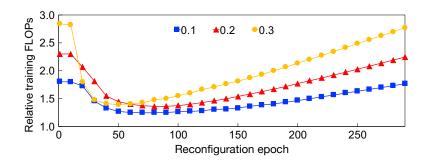

| 4.2  | Training computation saving by continuous reconfiguration                            | 61 |

| 4.3  | Group lasso regularization structure of a convolution layer $\$ .                    | 65 |

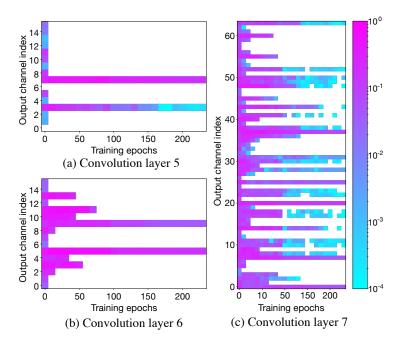

| 4.4  | The maximum absolute weight value of each output channel during training             | 67 |

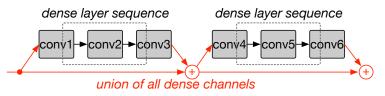

| 4.5  | Channel indexing for CNNs with short-cut paths                                       | 69 |

| 4.6  | Normalized training and inference FLOPs different pruning in-<br>tensity             | 70 |

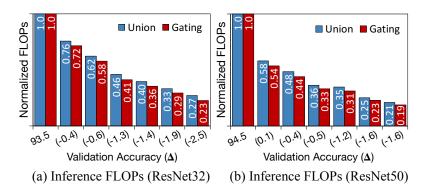

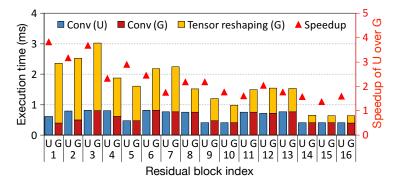

| 4.7  | Per-layer execution time of channel gating and channel union .                                                     | 70  |

|------|--------------------------------------------------------------------------------------------------------------------|-----|

| 4.8  | Inference cost, training cost, and prediction accuracy comparison to SSL                                           | 76  |

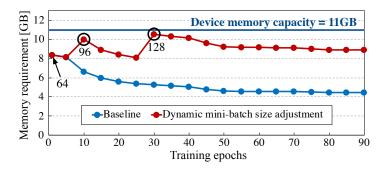

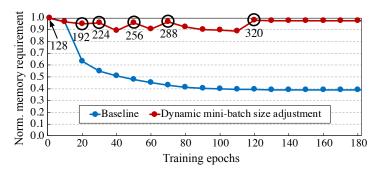

| 4.9  | Memory requirement changes during training                                                                         | 82  |

| 4.10 | Reduced inference FLOPs and validation accuracy by different network reconfiguration intervals                     | 84  |

| 4.11 | Projected communication cost of model updates based on hier-<br>archical ring-allreduce                            | 85  |

| 4.12 | Channel and individual weight density of each layer                                                                | 86  |

| 5.1  | Computing unit utilization of processing a pruned CNN model                                                        | 91  |

| 5.2  | Different GBUF configurations                                                                                      | 94  |

| 5.3  | Impact of core sizing to PE utilization and GBUF loads                                                             | 95  |

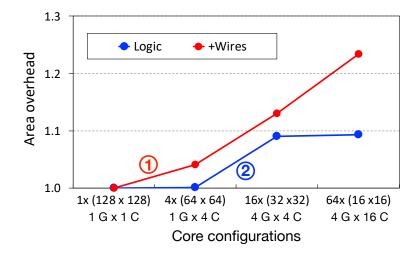

| 5.4  | Area overhead of core division normalized to $1 \times (128 \times 128)$ .                                         | 97  |

| 5.5  | FlexSA architecture.                                                                                               | 99  |

| 5.6  | Four different systolic sub-array operations supported by FlexSA and the micro-architecture settings for each mode | 102 |

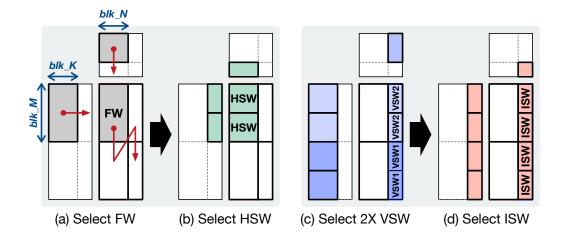

| 5.7  | FlexSA operating mode selection examples                                                                           | 105 |

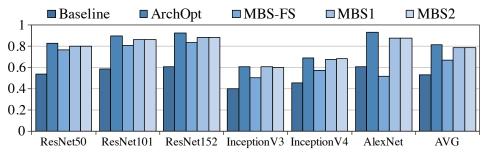

| 5.8  | PE utilization comparison                                                                                          | 112 |

| 5.9  | On-chip traffic comparison                                                                                         | 114 |

| 5.10 | Dynamic energy consumption comparison                                                                              | 115 |

| 5.11 | FlexSA modes selection breakdown                                                                                   | 116 |

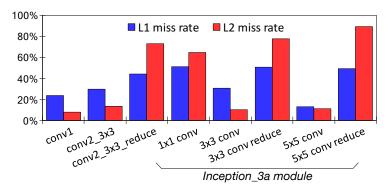

| 6.1  | Cache miss rates of the convolution layers                                                                         | 119 |

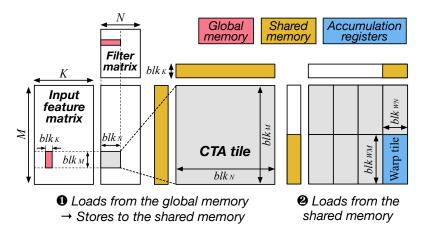

| 6.2  | Im2col GEMM blocking by cuDNN GPU kernel                                                                           | 121 |

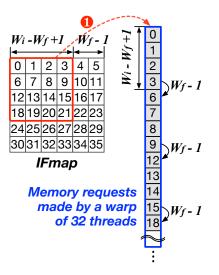

| 6.3  | IF map data requested by a single warp per main loop                                                               | 123 |

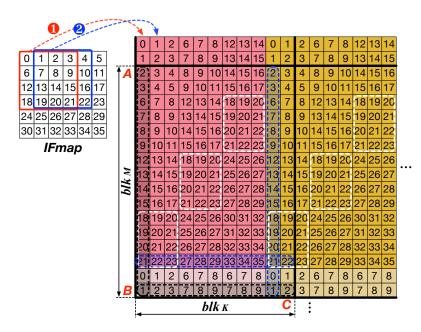

| 6.4  | IFmap matrix layout of im2col GEMM                                                                                 | 125 |

| 6.5  | IFmap and filter data reference at sequences of processing CTA batches                                             | 127 |

| 6.6  | Execution time breakdown of a software pipelined GEMM main loop                                                    | 128 |

| 6.7  | GEMM loop execution model of active CTAs with different GPU resource bottlenecks                                   | 131 |

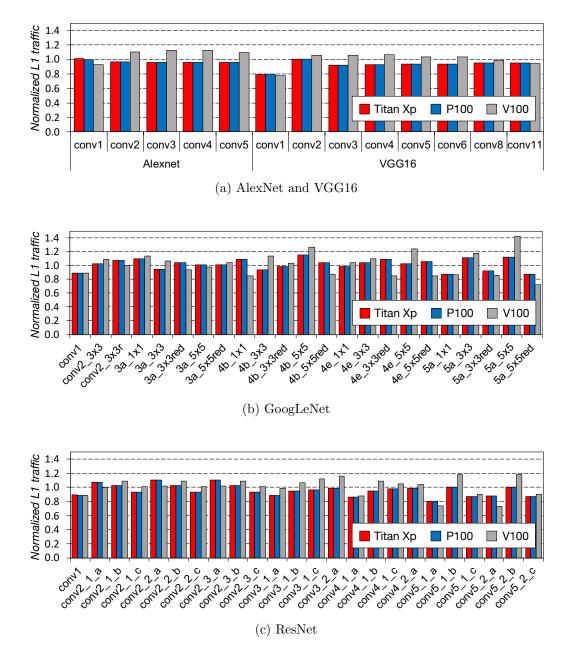

| 6.8  | L1 traffic estimates of different GPUs by DeLTA                                                                    | 134 |

| 6.9  | L2 traffic estimates of different GPUs by DeLTA                                                                    | 135 |

| 6.10 | DRAM traffic estimates of different GPUs by DeLTA               | 136  |

|------|-----------------------------------------------------------------|------|

| 6.11 | Memory traffic estimates comparison to prior methodology        | 138  |

| 6.12 | Conv layer execution time estimates by DeLTA $\ldots$ .         | 140  |

| 6.13 | Estimated GPU performance for different GPUs                    | 141  |

| 6.14 | Comparison to the fixed miss rate models                        | 141  |

| 6.15 | GPU resource scaling and speedup of convolution layers in ResNe | t143 |

## Chapter 1

## Introduction

Training modern DNNs (deep neural networks) requires millions of computation and memory bandwidth intensive workload iterations. In addition, ever-growing network architecture complexity and training dataset size have been continuously increasing the already expensive DNN model training cost [11]. Even using a cluster of training accelerators with large compute throughput, training a state-of-the-art network model on a large dataset such as ImageNet [22] still takes multiple hours to days [29]. Furthermore, unlike inference, training workloads involve many memory bandwidth-bound vector functions such as feature normalization. This increases the need for high memory bandwidth leading to many modern training accelerators adopting expensive high-bandwidth memory system. This dissertation focuses accelerating convolutional neural network training, an important branch of DNN models for computer vision tasks, by identifying and reducing its unnecessary memory accesses and unimportant computations.

#### 1.1 High Memory Bandwidth Needs in CNN Training

Convolutional neural networks (CNNs) are the state of the art for various vision applications [57, 85, 84, 101]. Modern CNN models have millions of learning parameters and they are first trained on a large dataset to be used for inference. CNN architectures consists of different layer components and they need high memory bandwidth to fully utilize the computing elements on high performance accelerators. However, based on my observation, commonly used data-parallel CNN training mechanisms on current systems require 3–4 times more memory bandwidth than necessary, reducing performance and wasting energy.

Conventional CNN training propagates a mini-batch of samples across network layers in lockstep, where a mini-batch typically consists of 32–512 samples [96, 95, 36]. Therefore, the mini-batch output of one layer is reused in its following layer as an input. However, large mini-batches have per-layer memory footprints that exceed typical on-chip buffer capacity. This leads not capturing the inter-layer data locality, resulting in high memory traffic. Many inter-layer locality techniques were proposed in the context of network inference [77, 5]. However, directly applying these techniques to training is ineffective or not feasible because they do not optimize locality across large mini-batches, and their design is not compatible with batch normalization [46], the most commonly used feature normalization algorithm. In this dissertation, I introduce a memory bandwidth-efficient training mechanism that enables inter-layer data reuse and a coupled training accelerator that achieves effective training speedup.

## 1.2 Model Pruning for Cost-efficient CNN Training

CNN architectures contain millions of learning parameters (or weights) for learning complex features. However, not all parameters equally contribute to prediction accuracy. Model pruning is a commonly used technique that removes less critical learning parameters from an initially-dense model [33, 34]. This leads to lower memory and compute cost with minor prediction accuracy loss compared to the original dense model.

Model pruning mechanisms are typically used for high-performance and energy-efficient inference [103, 25, 39, 38]. They typically retrain a pre-trained model, which eventually increases net training time. Some prior work prunes models during training [110, 103, 102, 113, 4]. However, this work maintains the original network architecture without pruning, or prune only a limited number of times during training. In this dissertation, I discuss a CNN training mechanism that constantly prunes unimportant parameters during training to gradually reduce computation cost over training. Furthermore, I develop and evaluate a practical implementation of this algorithm for modern CNN models.

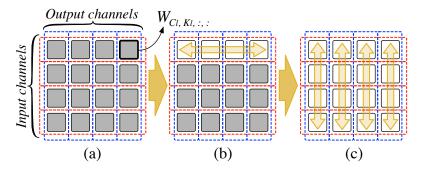

## 1.3 Efficient Pruned Model Training on High-Throughput Accelerators

Not all parameters of a CNN model are equally important. Structured model pruning removes such parameters at the granularity of channels. Therefore, unlike unpruned CNN models that have regular number of channels such as 64, 128, and 256 (powers of two) [57, 85, 84, 101], their channel-pruned versions have an arbitrary number of channels, such as 3 and 71. Such convolution layers are computed as GEMMs (general matrix multiplies) for efficient execution on data-parallel accelerators. However, the GEMMs of the pruned layers have arbitrarily reduced dimensions and these GEMMs execute inefficiently on the large GEMM cores used in modern training accelerators [21, 86]; many GEMM tiles of pruned CNNs tend to have small sizes and executing them on a large core does not fully utilize its PEs.

Splitting a large core into many small cores can improve PE utilization. This is because GEMM is tiled into smaller parts and these small tiles are processed by small cores with high PE occupation (mitigating internal PE utilization fragmentation). However, this core splitting incurs >4% area overhead for data paths and splitting SRAM buffers. Also, such a many-core design increases on-chip input traffic for fetching duplicated inputs to multiple cores, hurting the energy efficiency of training and requiring high on-chip BW. In this dissertation, I introduce a flexible GEMM core architecture that can reconfigure its structures to achieve both high PE utilization and high input reuse. I also discuss GEMM tiling and scheduling techniques for efficient utilization of the reconfigurable hardware resources.

#### **1.4** The Need for an Accurate Performance Model

GPUs are the most widely used training accelerators. The increasing demand for high computation throughput of DNN training is driving GPU arithmetic performance, which has been growing at higher than its historical rate [76]. Based on my analysis, compared to the rapid GPU compute throughput increase of  $32 \times$  over the past 9 years, GPU memory system bandwidth has improved by only  $13 \times$ . This memory wall problem can bottleneck the performance of even the arithmetically-intensive CNNs, making performance scaling challenging.

It is therefore imperative to balance both arithmetic and memory performance in architecting a future GPU or other accelerators for efficient CNN performance scaling. This balanced designing benefits from analytical modeling, which can quickly provide insight and narrow the design space before slower and more resource-consuming modeling is used (e.g., simulators [1, 80]). Analytical models also aide in the optimization of software for efficient hardware resource utilization [114, 61]. Given that DNN models evolve and change quickly, the benefits of a performance model are significant. In this dissertation, I present an accurate GPU performance model that relies on an accurate memory traffic modeling. I also discuss using the performance model for finegrain GPU resource allocation for cost-efficient CNN performance scaling.

#### 1.5 Thesis Statement

Ever increasing neural network model complexity and training dataset size have been constantly raising CNN training cost. Partially serializing a mini-batch CNN training workload enables inter-layer data reuse in training and significantly reduces redundant memory traffic. Also, structurally pruning unimportant model parameters during training effectively reduces total training compute operations and leads to faster model training. At the same time, given the changes in the training workload scheduling and algorithm, co-optimizing the accelerator architecture is critical to maintaining high compute resource utilization and significantly improves the training performance of modern CNNs.

### **1.6** Contributions

In this dissertation, I resolve and mitigate the two key overheads of CNN training; high memory bandwidth requirement and high computation cost. I first resolve the memory bandwidth problem of training by: (1) partially serializing a mini-batched training workload in a way that utilizes interlayer data locality using the available on-chip storage resources, and (2) cooptimizing the training accelerator architecture to cope with the challenges from the changes in the scheduling and algorithm. Next, I reduce the cost of CNN training by gradually pruning less critical parameters from the initial dense model. I introduce three algorithm techniques for efficient model pruning that maintains high training accelerator resource utilization. I also co-design a training accelerator to resolve the reduced PE utilization in processing pruned models on a large systolic array by making the core structure change depending on GEMM dimensions. To evaluate the proposed ideas, I devise a training accelerator performance model that accurately estimates the memory traffic and the performance of CNNs. I also explore the architectural optimization space of a GPU, the most common DNN training accelerator using my model. I summarize the contributions of this dissertation:

1. I propose Mini-Batch Serialization (MBS), a memory bandwidth-efficient network training mechanism. MBS decreases the memory traffic of modern CNN training by exploiting data reuse between layers. MBS breaks a mini-batch into sub-batches, which are then processed serially such that the inter-layer data of an entire sub-batch fits in an accelerator's on-chip buffers and can be reused. Implementing MBS raises two challenges. First, mini-batch wise feature normalization commonly used in modern CNNs is not compatible with (partially) serializing a mini-batch. Second, the data parallelism per sub-batch is smaller than for a whole mini-batch and can decrease the compute array utilization and increase core idle time. I resolve these challenges by (1) adapting an appropriate feature normalization algorithm to the context of MBS, (2) devising a sub-batching mechanism that adjusts the sub-batch size for the network layers to reuse inter-layer data with only a small impact to data parallelism, and (3) using a systolic data flow along with architecture optimizations that maintain high computing array utilization. Compared to the conventional mini-batch wise training for modern CNNs, MBS with the proposed training accelerator optimizations reduces memory traffic by 4X and improves performance by more than 50%.

- 2. I propose PruneTrain, a CNN training acceleration mechanism that continuously prunes the model during training from scratch. For efficient execution on data-parallel training accelerators, I group parameters at channel granularity and prune those channels for which all parameters are below a threshold using group lasso regularization. This periodic reconfiguration maintains a still dense, yet smaller model. This model, which requires less computation, memory, and communication, continues to shrink as pruning continues throughout training. For performanceefficient pruning, I introduce three key optimization techniques. I first propose a systematic method to set the group lasso regularization penalty coefficient that controls group lasso regularization strength and achieves a high model pruning rate with small impact on accuracy with a few training runs. Second, I propose channel union, a memory-access costefficient and index-free channel pruning algorithm for modern CNNs with short-cut connections. Lastly, I propose dynamic mini-batch adjustment that dynamically increases the size of the mini-batch to fully utilize the available off-chip memory space for training iteration. PruneTrain speeds up the training of the commonly used state-of-the-art image classifier by 39%.

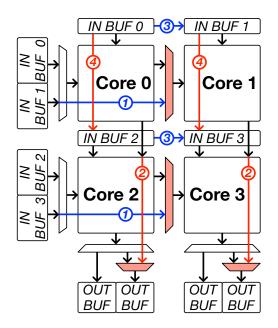

- 3. I propose FlexSA, a flexible systolic array architecture that improves PE

utilization while keeping input reuse high when processing pruned models. FlexSA is comprised of four systolic array cores. However, unlike a naive four-core design, where each core operates independently, FlexSA supports three additional inter-core operating modes, which achieves low on-chip traffic via inter-core data reuse. To efficiently utilize the underlying resources of FlexSA, I propose compile-time GEMM tiling heuristics that use large GEMM tiles with inter-core operations in 96% of cases, improving on-chip input reuse by  $1.8 \times$  compared to a baseline four-core design. Overall, compared to the baseline four-core design, FlexSA adds only 1% additional area but improves energy efficiency by 18%. Also, compared to a single large systolic array, FlexSA improves average PE utilization by  $1.4 \times$ .

4. To explore the design space of a GPU, the most common accelerator for DNN model training, I propose DeLTA, a GPU performance model based on accurate data traffic estimation at all levels of GPU memory system hierarchy. DeLTA separately models the traffic at each memory level using the access patterns of the data-parallel convolution algorithm. DeLTA also accounts for how the computation is blocked for locality and parallelism and how the hardware handles memory accesses in the caches and the software-managed shared memory. The estimated memory traffic is used to predict convolution layer execution time under different system configurations and identify the GPU performance bottlenecks. Overall, DeLTA predicts all L1, L2, and DRAM traffics by GMAE less than 5% (geometric mean absolute error) and execution time by 6.0% GMAE for NVIDIA TITAN Xp GPU. I also show that DeLTA helps fine-grain GPU compute and memory resource balancing for cost-efficient CNN performance scaling.

## 1.7 Dissertation Organization

The remainder of this dissertation is organized as follows: Chapter 2 reviews the background for understanding CNN architecture, its model training mechanisms, a data-parallel convolution kernel, and training accelerator architectures. Chapter 3 proposes a memory bandwidth-efficient CNN training mechanism with the combination of workload scheduling, learning algorithm, and architecture optimizations. Chapter 4 discusses computation-efficient CNN training using an efficient model parameter pruning mechanism during training. Chapter 6 introduces the models to estimate memory traffic and performance of GPU for CNNs. Finally, Chapter 7 concludes the dissertation.

# Chapter 2

## Background

This chapter provides background on CNN applications and training accelerator architecture. I first explain different layer functions of CNNs and CNN training algorithms in Section 2.1. Then, I briefly explain the neural network model pruning mechanisms in Section 2.2. Lastly, I describe the architectures of commonly used CNN training accelerators and the data-parallel convolution layer kernel design for GPUs in Section 2.3 and Section 2.4, respectively.

## 2.1 CNN Architecture and Training

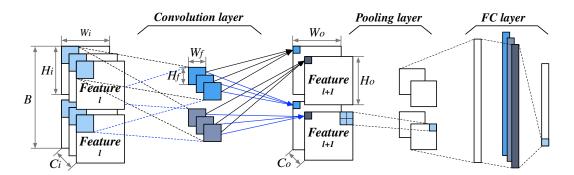

**CNN Architecture.** CNNs consist of various types of layers (Figure 2.1): convolution layers extract feature maps (or features or activation) from input images, down-sampling (e.g., pooling) layers reduce the size of each feature map, and fully-connected (FC) layers generate prediction scores for classes. Also, a convolution layer typically includes feature normalization and activation. Feature normalization maintains stable feature distributions across layers and different mini-batches (a set of samples used per training iteration) [46] and activation layers, e.g., ReLU [73] add non-linearity to the learning func-

tion.

Each convolution layer takes IF maps (input feature maps) and produces OF maps (output feature maps). As shown in Figure 2.1, each set of IF maps and OF maps has four dimensions: the number of samples in a mini-batch (B), the number of channels (C), and the height (H) and width (W) of each feature map. I use *i* and *o* to denote IF map and OF map, respectively.

Convolution and FC layers are implemented primarily with matrix multiplication and accumulation. As illustrated in Figure 2.1, a convolution layer convolves its IFmaps with small filter matrices (each  $H_f \times W_f$ ), possibly with a non-unit stride. Filters hold weights and there are  $C_i \times C_o$  filter matrices that map input to output channels. After each convolution, the results from all input channels are accumulated to a single output data point. As the same filter is reused for convolving IFmaps and the same input feature data is reused to compute different OFmaps, a convolution layer typically exhibits large data reuse and its performance is bottlenecked by compute through-

Figure 2.1: Layers of a CNN, and the feature and filter data structure of a convolution layer.

put [15]. Other layers, including pooling, activation, and feature normalization have low arithmetic intensity as their major function is element-wise vector computations [57, 46]. Therefore, their performance is constrained by data access bandwidth.

**CNN Training.** A modern CNN model contains millions of weights W (or learning parameters) that are trained using a collection of samples called the training dataset. The baseline training approach starts by randomly taking a sample from the training set and propagating it through the CNN layers to predict an output using the current weights. Next, the predicted output are compared to the ground truth, and loss l (or prediction error) is computed. Finally, the loss is back-propagated through the network layers, calculating the gradient of loss w.r.t. the current weights in each layer and then updating the current weights using the gradients.

Mini-batch SGD (stochastic gradient descent) is the most commonly used CNN training algorithm, which uses a set of training samples per training iteration for network propagation, loss computation, and model update. Using a large mini-batch exhibits many benefits: (1) it provides abundant data parallelism to each layer operation, which helps achieve high HW resource utilization, (2) it reduces the frequency of weight updates, and (3) it decreases the variance in weight updates between training iterations [63, 29, 20]. Typically, a mini-batch is 32–512 samples (possibly distributed across multiple processors) [94] but even a huge mini-batch bigger than 8K is often used with algorithmic support to enable extreme-scale distributed training [108, 2, 48]. Equation 4.1 describes the mini-batch SGD algorithm. Here f is the network's prediction on the input  $x_i$ , W are the weights, l is the classification loss function between the prediction and its ground truth  $y_i$ , and N is the mini-batch size.

$$\min_{\boldsymbol{W}} \left( \frac{1}{N} \sum_{i=1}^{N} l(y_i, f(x_i, \boldsymbol{W})) \right)$$

(2.1)

Feature Normalization for Fast Model Convergence. Feature normalization is critical to scaling the depth of a network architecture and enabling faster convergence of the SGD training algorithm. It maintains a constant feature distribution for the input to each convolution layer and avoids the parameter variance caused by random sampling. BN (batch normalization) is the default technique for most modern deep CNNs. BN normalizes features each mini-batch [46]. BN typically uses 32 or 64 samples (partial mini-batch assigned to a processor) for normalization. The performance of BN is highly memory bound because each of the mean, variance, and normalization steps requires reading of the entire mini-batch [52].

**Distributed Training.** A cluster of GPUs is typically used to train a complex CNN model on a large dataset. Data parallelism is the most commonly used multi-processor training mechanism [57]. First, each GPU in the system holds the same copy of the weights. Then, a mini-batch of input samples is distributed to each GPU and all GPUs process the inputs in parallel. Data parallelism is network-traffic efficient as the inter-GPU communication is required only for model updates; the partial weight gradients of all GPUs are first reduced then used to update the current weights. Although using more GPUs increases the peak computation throughput, it also increases this communication overhead, preventing linear end-to-end training performance scaling. For efficient weight gradient reduction, a ring-allreduce based communication is for weight gradients reduction, which efficiently pipelines data transfer latencies among nodes [104]. In particular, recently proposed hierarchical allreduce communication [64] reduces the communication complexity by hierarchically dividing the reduction granularity and achieves more linear training performance scaling with increasing number of GPUs.

**Training Memory Context.** Processing a training iteration requires a large off-chip memory space. This is mainly because the input activations of each layer at forward propagation should be kept in memory and reused to compute the local gradients in back-propagation. In particular, the total size of all layer inputs linearly increases with mini-batch size [69]. Therefore, small off-chip memory capacity or a large feature size of a CNN can constrain the mini-batch size per accelerator, and hence also the data parallelism of each layer. This eventually decreases HW resource utilization. In addition, insufficient memory increases the total number of training iterations per epoch because of smaller mini-batches, which increases the communication cost for model updates.

Chen et.al propose a memory-storage efficient training technique that stores the activations of only a fraction of layers [13]. Their approach keeps only the layer output activations that are expensive to compute and recompute the outputs of other layers during back-propagation. Although this method reduces the memory cost from O(n) to  $O(\sqrt{n})$ , it increases computation during back-propagation.

### 2.2 Neural Network Model Pruning for Fast Inference

Model pruning has been studied primarily for CNNs, to make their models more compact and their inference fast and energy-efficient. Most pruning methods compress a CNN model by removing small-valued weights with a fine-tuning process to minimize prediction loss [33, 34]. Pruning algorithms can be unstructured or structured. Unstructured pruning can maximize model-size reduction but requires fine-grained indexing with irregular data access patterns. Such accesses and extra index operations lead to poor performance on deep learning accelerators with vector or matrix compute units despite reducing the number of weights and FLOPs (floating point operations) [31, 109, 8]. Structured-pruning algorithms remove or reduce fine-grained indexing and better match the needs of hardware and thus effectively realize performance gains.

#### 2.2.1 Trial-and-Error Based Structured Model Pruning

One approach to structured pruning is to start with a pre-trained dense model and then attempt to remove weights in a structured manner, generally removing channels rather than individual weights [39, 43, 72, 38]. Unimportant channels are removed based on the value of their weights or hints derived from regression [97]. The removed channels are rolled back if accuracy is severely affected. Although effective, the search space of such a trial-anderror based model pruning substantially increases with the complexity of the network model, which can increase pruning time significantly. Also, as pruning is applied to a pre-trained model, these mechanisms do not speed up training.

### 2.2.2 Model Pruning with Parameter Regularization

An alternative mechanism to trial-and-error pruning uses parameter regularization. This optimizes training loss while simultaneously forcing the absolute values of weights or groups of weights toward zero. I call this process of forcing weights toward zero sparsificiation. Group lasso regularization is typically used to structurally sparsify weights by assigning a regularization penalty to  $l_2$ -norms of groups of weights [103, 102, 25, 4, 113]. This regularization-based pruning mechanism adds regularization loss terms to the baseline classification loss function as shown in Equation 4.1, then backpropagate the loss to update the weights to both improve accuracy and reduce their absolute values. Eventually, the sparsified weights can be effectively zeroed-out and pruned from the model.

# 2.3 Training Accelerator Architecture

### 2.3.1 GPU Architecture

GPUs are designed to accelerate compute-intensive highly-parallel workloads thus they require applications to express parallelism with many threads for efficient utilization. GPUs contain a large number of very wide SIMD (single instruction multiple data) cores, called streaming multiprocessors (SMs). In NVIDIA GPUs, each SM processes a warp of 32 threads in lockstep, such that ideally all 32 threads execute the same instruction. In addition to the processing elements, each SM contains load store units (LSU), register files (RF), a shared RAM (SMEM), and an L1 cache. The SMs share access to the L2 cache and DRAM through a crossbar interconnection network.

GPU workloads are tiled into thread groups called cooperative thread arrays (CTAs). The CTA scheduling mechanism is assumed to assign SMs to CTAs in a round-robin manner [62]. Each CTA typically consists of multiple thread warps that execute concurrently to hide memory access latencies. Given sufficient resources (RF and SMEM), multiple CTAs can be simultaneously executed within one SM (active CTAs). Interleaving multiple CTAs improves the ability of the SM to overlap computation with memory access.

#### 2.3.2 Systolic-Arrays

A systolic array used for DNN training acceleration is (typically) a twodimensional mesh of many simple and efficient processing elements (PEs). At each cycle of a kernel, each PE applies the same computation to its inputs and then passes the computed result or its unmodified inputs to one or more of its neighbors. All PEs communicate only with adjacent PEs such that there is minimal data movement and high computational concurrency [58]. Computation consists of pipelining inputs from the top and left (for example) edges of the array and obtaining results at each PE or at the bottom depending on the systolic dataflow. The large compute throughput required for convolutional and fully-connected layers, along with the repetitive computation and large data reuse are a good match for a systolic array, as found in Google's TPU ML accelerators [51, 21]. I describe the detailed systolic array operation in Section 3.3.1 along with the accelerator architecture that this dissertation proposes.

# 2.4 Data-parallel Convolution GEMM

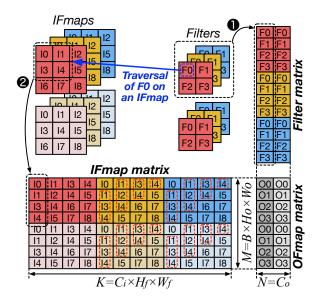

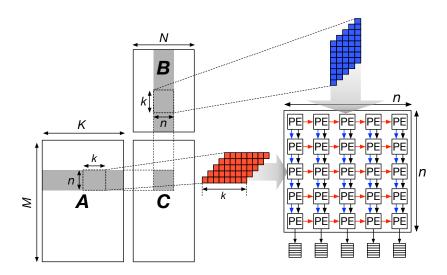

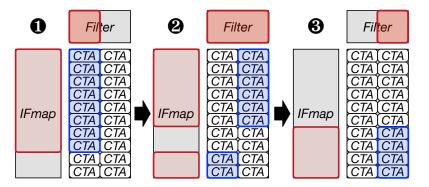

Im2col (image-to-column) is one of the most commonly used algorithms for convolution kernels for data-parallel accelerators [19, 78, 42]. Im2col transforms the direct convolution described in Figure 2.1 into a single general matrix-matrix multiplication (GEMM) with three-dimensions  $(M \times N \times K)$ by merging the IFmaps and small filter matrices (Figure 2.2). In this example,

Figure 2.2: Im2col conversion: direction convolution converted to GEMM.

first, the  $2\times 2$  filters for each OFmap channel are converted into columns and stacked **①**. Next, the data elements in the IFmaps are laid out in a way such that the elements to be multiplied by one filter (F0) are placed as a column **②**. The IFmap matrix data layout changes depending on the filter size and stride. Im2col duplicates many data elements (data in red doted boxes) which represents input feature data reuse. Therefore, compared to the typical GEMM, convolution GEMM has greater data reuse and benefits more from caches or programmable buffers.

# Chapter 3

# **CNN** Training with Inter-layer Data Reuse

This chapter covers my memory bandwidth-efficient CNN training approach that reuses inter-layer data. I first discuss the inter-layer data reuse opportunity in CNN training and the difficulty of capturing such locality when using conventional training mechanism. Then, I introduce a CNN training approach that reuses inter-layer data with a small on-chip storage budget. The proposed training method changes the scheduling of CNN training along with adopting a coupled feature normalization algorithm. This chapter also introduces a systolic array-based training accelerator that supports high PE utilization given the proposed approaches. <sup>1</sup>

# 3.1 Data Reuse in CNN Training

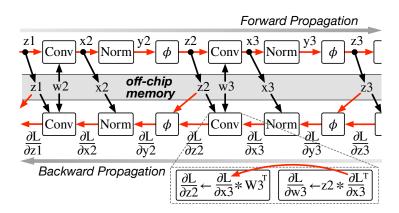

CNN training consists of forward and back-propagation phases as described in Section 2.1. Figure 3.1 illustrates the major data elements needed for training and their reuse patterns with red arrows indicating opportunities for on-chip buffers to reduce memory bandwidth requirements and black arrows

<sup>&</sup>lt;sup>1</sup>This chapter was published in the proceedings of The Conference on Systems and Machine Learning (SysML) in April 2019. Sangkug Lym contributed to this work as the main author.

indicating accesses to main memory. In both phases there is direct producerconsumer locality between layers—*inter-layer data* that can be buffered if it is not too large. The outputs of convolution, normalization, and activation layers in forward propagation (x, y, and z in the figure) are immediately used by their following layers. Normalization layers exhibit additional reuse because they iterate over inputs to first compute the mean and variance before normalizing the data [46]. The convolution outputs and the activations are stored in off-chip memory for reuse in back-propagation because their large storage requirements and long data reuse distance prevent on-chip buffering.

Back propagation exhibits even greater potential for inter-layer reuse. The loss gradients (w.r.t. x) are reused twice by a convolution layer to compute the gradients of weights and loss (w.r.t. z). Also, the convolution output stored in memory is reused multiple times to compute the gradients of the normalization layer parameters and the loss gradients (w.r.t. x). Activations

Figure 3.1: Dataflow in forward and backward propagations. Red arrows show the reusable data between layers.

read from memory are also used twice: z is used for convolution gradients and the derivative of z for activation gradients.

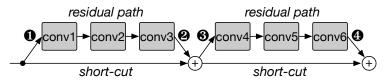

Multi-branch Network Modules. Recent CNNs typically consist of multibranch modules that enable a deeper network architecture and more accurate prediction [96, 95, 36]. The residual [37] and inception [96] modules are the most representative multi-branch modules. A residual module has two branches whose outputs are accumulated when they merge while an inception module has numerous branches whose outputs are concatenated at a common node. As the input at the branch divergence is used by all branches and the outputs at the join can be referred to other branches for reduction, the multi-branch modules exhibit data locality between branches.

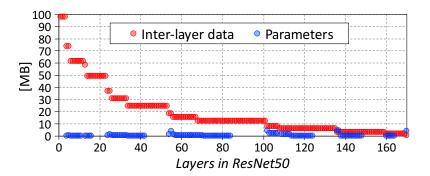

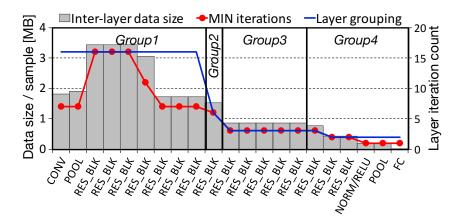

The Problem with CNN Training Memory Footprint. Mini-batch SGD increases each layer's memory footprint, and this limits the opportunity to reuse data on chip. Figure 3.2 shows the per-layer footprint of ResNet50 [36], the most common modern CNN, with a mini-batch size of 32 and a word size

Figure 3.2: The size of inter-layer data and parameters of each layer in ResNet50 (sorted by inter-layer data size).

of 16b in the forward phase. Only 9.3% of inter-layer data can be reused even with 10MiB on-chip storage, leading to significant memory bandwidth waste for storing and refetching data. This problem is even more severe for larger mini-batch sizes, which are desirable as per-processor arithmetic performance and main memory capacity improve.

# 3.2 Memory BW-Efficient CNN Training with Mini-Batch Serialization

# 3.2.1 Serialization Principle

The primary goal of MBS (mini-batch serialization) is to improve reuse by exploiting inter-layer data locality. The key to MBS is partially serializing a mini-batch (propagating a small sub-set of a mini-batch at a time) to control per-layer memory footprint without impacting training accuracy. MBS is based on my insight that if the data synchronization points for functional correctness are maintained and an appropriate normalization algorithm is adapted, even processing a single sample at a time through all network layers does not alter the training result. The trivial serialization of one sample at a time, however, has two crucial drawbacks.

First, while baseline training reads weights and writes weight gradients just once per layer, full serialization re-reads weights and their partial gradient sums for each sample and updates the partial sums once per sample as well. Second, data parallelism within a single sample can be limited in some layers, degrading resource utilization and performance (especially when mapping to a highly-efficient systolic architecture). It is possible to process multiple samples at a time (a *sub-batch*) to to provide some intra-layer weight reuse and extra parallelism. However, the footprints of early layers are large and only a small sub-batch can be formed (1–2 samples), limiting the benefits of this approach.

MBS goes much further and balances locality of intra-layer weight reuse and parallelism with inter-layer locality. I do this by varying the number of samples per sub-batch across layers such that layers that can support more samples require fewer iterations and can benefit from the greater parallelism and locality. This is possible because down-sampling layers decrease feature map size and volume for deeper layers.

### 3.2.2 Layer Grouping Optimizes Reuse

Optimizing layer groups balances intra- and inter-layer locality tradeoffs. The MBS algorithm forms initial layer groups by grouping adjacent layers

Figure 3.3: Per-block inter-layer data size, required layer iterations, and MBS layer grouping for ResNet50 with 32 samples.

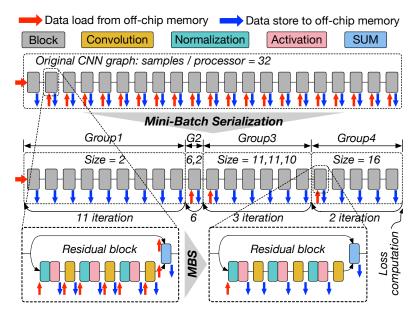

Figure 3.4: ResNet50 training flow by baseline and MBS.

that require the same number of sub-batch iterations. This is shown in Figure 3.3 where grey vertical bars represent the data volume required for the inter-layer data per layer (or one multi-branch module *block*) of ResNet50, and the red line represents the resulting minimal sub-batch iteration count for each layer. Then, layer groups are merged to improve overall locality: groups are merged by reducing the sub-batch size of one group to that of an adjacent group. The first group then requires more iterations (with more weight and gradient accesses), but inter-layer reuse increases across the two layers where the groups meet. The resulting grouping for this optimization for ResNet50 is shown with the blue line in Figure  $3.3.^2$  The mini-batch is then processed

$<sup>^{2}</sup>$ I also experimented with an optimal grouping of layers using exhaustive search, which improved traffic and performance by roughly 1% compared to my greedy optimization.

in several sub-batch iterations  $\left(\left\lceil \frac{mini-batch \ size}{sub-batch \ size} \right\rceil\right)$  within each group as shown in Figure 3.4, which emphasizes how locality is increased and memory traffic reduced across features and weights.

**Back Propagation.** In back propagation, MBS optimizes locality for both newly computed results and for data reloaded from the forward path. For example, as shown in Figure 3.1, MBS reuses the reloaded gradients more than once. Furthermore, both convolution and ReLU layers use activations from the forward path. However, only the gradient of ReLU is needed, which is always 0 (for negative activations) and 1 (for positive); thus, MBS uses a single bit per ReLU gradient instead of a 16b. I also allocate buffer space for normalization layers to reuse their inputs to compute their gradient and loss. As in the forward pass, reuse in back propagation is made possible by MBS processing one sub-batch at a time.

**Data Synchronization.** MBS maintains the original synchronization points across the entire mini-batch. Therefore, MBS accumulates the partial gradients of all learning parameters across all sub-batches. This requires storing partial results to memory, which is not needed in the conventional flow. However, this overhead is dwarfed by the improved reuse of layer outputs, especially considering that deeper layers with large weights are iterated over only a few times.

#### 3.2.3 Data Reuse Within a Multi-Branch Module

Figure 3.4 also shows how MBS applies the same sub-batch approach to a multi-branch residual module of ResNet50. Such multi-branch modules are common in CNN architectures and offer additional reuse opportunities. Both the main path and shortcut branch share an input, and when they merge, their outputs are summed. Therefore, the module inputs should stay on chip until both paths have consumed them, and the output of the shortcut branch should stay on-chip while the main path output is computed. MBS does this by provisioning buffer space based on the needs of multi-branch *blocks*, where a block includes all the branches that share split and merge points—MBS essentially treats such a block as a layer for optimizing locality.

Maintaining locality for such shared nodes leads to additional storage requirements. The per-sample size is calculated by Equation 3.1 where:  $D_{in}$ and  $D_{out}$  indicate the sizes of the main-branch input and output;  $D_{shortcut}$  is the size of the shortcut path output; L is the number of layers in the main branch; and b and l represent a specific branch and layer.

$$\frac{Space}{Sample} = \max_{1 \le b \le 2, \ 1 \le l \le L} D_{in}(b,l) + D_{out}(b,l) + D_{cond}(b,l)$$

$$D_{cond}(b,l) = (b=1 \ \& \ l \ne 1) D_{block\_in} + (b \ne 1) D_{block\_out}$$

(3.1)

Similarly, for inception modules [96, 95], the block input is reused between branches, and the concatenated block output is eventually reused in the following layer. Therefore, MBS keeps both the block input and output on chip while executing the branches. The space required is shown in Equation 3.2, where B indicates the number of branches in a module and other notation is

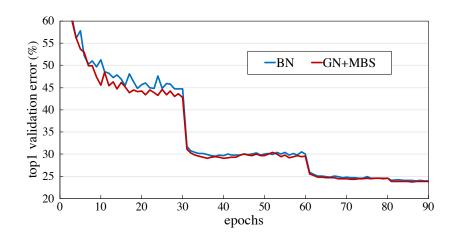

Figure 3.5: ResNet50 validation error trained with GN + MBS and BN.

as above.

$$\frac{Space}{Sample} = \max_{1 \le b \le B, \ 1 \le l \le L} D_{in}(b, l) + D_{out}(b, l) + D_{cond}(l)$$

$$D_{cond}(l) = (l \ne 1) D_{block\_in} + (l \ne L) D_{block\_out}$$

(3.2)

# 3.2.4 Feature Normalization in MBS

While batch normalization (BN) is widely used in many modern CNNs, it is incompatible with MBS because BN requires many samples to work well and improve accuracy [46]—MBS cannot serialize computation if data across an entire mini-batch (per processor) is needed for normalization. Instead of using BN, I adapt group normalization (GN) [106] to MBS. GN normalizes across feature maps within a subset of channels in a single sample, as opposed to across an entire per-processor mini-batch. Thus, GN can be made compatible with MBS.

To use GN with MBS, the per-channel GN scale and shift parame-

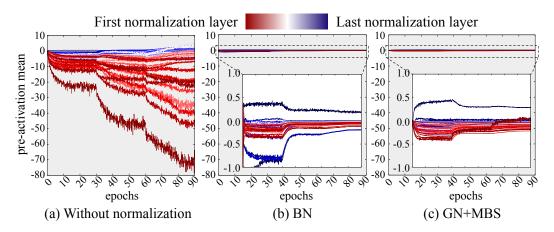

Figure 3.6: Pre-activation mean of each normalization layer. (a) Without normalization, (b) BN ,(c) GN. b and c are zoomed in.

ters must be re-fetched at every sub-batch iteration within a layer group. Additionally in backpropagation, the gradients of these parameters must be accumulated across all sub-batches just like the weights of convolution layers. However, since the size of these parameters is only two times the number of channels per layer, they can easily be stored in the on-chip buffer and incur no overhead.

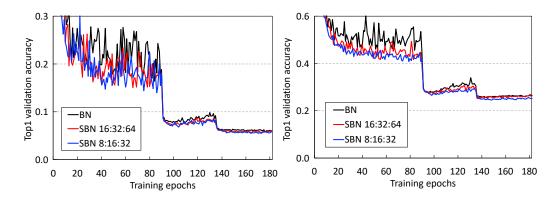

I confirm previous results and demonstrate that both GN and BN provide comparable training effectiveness. Figure 3.5 compares the validation error curves with BN and MBS-GN when training ResNet50 on ImageNet [22]. Figure 3.6 shows that both MBS-GN and BN provide similar normalization, in that both have similar pre-activation (output of normalization) distributions across layers (unlike training without normalization). In this experiment, minibatch samples of 128 are distributed across 4 GPUs and an initial learning rate 0.05 used considering the linear learning rate scale rule [10, 81].

# 3.3 Efficient MBS Training on the WaveCore Accelerator

In this section, I introduce WaveCore, a CNN training accelerator for efficient execution of partially serialized training workloads. The design of WaveCore is based on prior training accelerators with large systolic arrays [51, 21]. To help understand its operation, I first describe the overall operation mechanism of a systolic array then introduce the detailed improvements I develop for WaveCore.

# 3.3.1 MBS Training on a Systolic Array

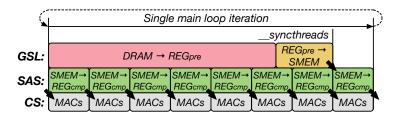

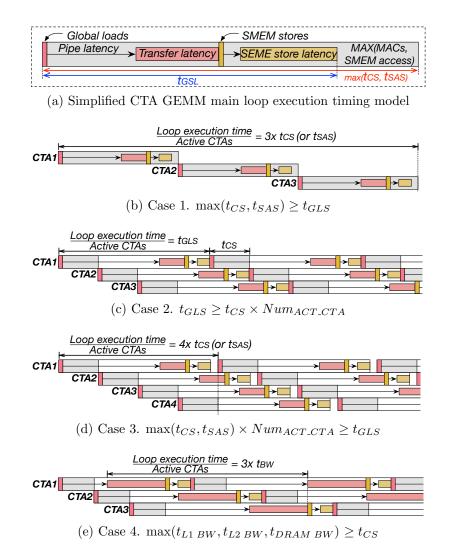

Like prior work, each PE in my proposed systolic array has mixed precision units: 16b inputs are multiplied with accumulation performed in 32 bits to reduce both computation and data traffic overheads [71]. Also like prior work [21], I use a  $128 \times 128$  systolic array for high performance and to circumvent power delivery challenges.

A systolic computation is often divided into multiple *waves*, where each wave proceeds with inputs flowing toward outputs without any stalls or changes to the computational pattern. Between waves, it is sometimes necessary to let the pipeline through the array drain and then refill. This introduces idle time which reduces utilization and hence hurts performance and efficiency. Convolution and matrix operations have efficient systolic implementations that have little idle time if an entire mini-batch is processed together. However, MBS processes an often small sub-batch, which significantly reduces

Figure 3.7: Tiled GEMM mapping to the systolic array of a convolution layer in forward propagation.

Figure 3.8: Removing inter-wave idle time by weight double buffering and control signal shift.

the utilization and performance of a conventional systolic array design. I address this challenge and maintain high systolic array utilization for MBS using a combination of two techniques.

Maintaining High Compute Unit Utilization with im2col. First, in-

stead of directly mapping a convolution computation to a systolic array, I use the *im2col* algorithm described in Section ??. I do this because efficient direct convolution on a systolic array requires tuning for every possible sub-batch size, which is difficult to do with the MBS approach that optimizes groupings to arbitrary size.

The major concern of processing GEMM on a large systolic array is that if the size of M, N, or K (the GEMM dimensions after im2col conversion) is smaller than the systolic array size, the compute units are significantly underutilized. However, based on my observation, the GEMM of each subbatch constructed by im2col is large in all dimensions, and this maintains high systolic array utilization: early layers with small sub-batches have large feature maps and while the feature map sizes of later convolution layers are small, their large sub-batch size compensates.

Systolic Dataflow for Convolution GEMM. I block the convolution GEMM into multiple  $m \times n$  tiles, which are processed in sequence through the array. Each tile corresponds to a portion of the output matrix (C). The width of each tile is equal to the width of the systolic array (n). The height (m) is chosen to maximize the size of a tile, thus minimizing the number of tiles per layer and improving utilization:  $m = \frac{Local \ buffer \ size}{k=systolic \ array \ height}$ . This is illustrated in Figure 3.7.

Each tile is processed using multiple waves through the systolic array, where each wave multiplies a block of input matrix A by a block of input matrix B. A block from B is first read one row at a time. Each row is shifted down until the array has one element of B per PE (this takes 5 cycles in the toy example of Figure 3.7). Then, a block of A is pipelined into the array with results for each element of C eventually accumulated at the bottom of the array as shown in the right side of Figure 3.7. Notice that in the figure, cycle 6 corresponds to the first row of the block of A having been multiplied and then accumulated by the first column of the block of B. In the following cycle, the second row of the A block completes its pipeline through the first column, while the first row of A now completes its dot product with the second column of the B block (and its output is at the bottom of the second column of the systolic array). Once a wave as described above completes, the next blocks of A and B are processed. As additional blocks are processed, their outputs are added to the current values of the C tile (a reduction across waves), eventually completing a tile of C in [K/k] waves.

### 3.3.2 Gapless Waves with Per-Register Weight Double Buffering

The flow described above has one significant problem. Before every multiplication of blocks of A and B, the B block is read and distributed to the PEs, which requires k (PE array height) cycles (for reading and inter-PE shifting). No arithmetic occurs during these k cycles, which decreases performance (upper half of Figure 3.8b).

To remove this inter-wave idle time, I modify the basic PE design to double buffer weights (Figure 3.8a)—the next wave's weights are fetched and distributed into a second register within each PE while the current wave is still being processed. As the current wave starts draining from the PE array, the following wave starts immediately by feeding in a new block of A and multiplying by the second register that stores the next set of weights from B. Thus, there are no gaps between waves and an entire tile of C is computed without any idle time beyond the initial fill and final drain of the pipeline. In addition to the extra register in each PE, a minor further change is that a select signal for choosing which weight register to use is propagated along with the inputs of A and B. This optimization significantly boosts performance at very low cost: the simple 1b local signal between every two PEs and a 16b register and multiplexer between the two registers per PE. As in prior work, I also check for zero inputs and skip arithmetic in such cases to reduce energy consumption [77].

# 3.3.3 WaveCore Processor Architecture

In addition to the systolic cores, the WaveCore CNN training accelerator contains several more structures and units. Figure 3.9 illustrates the overall architecture of one core of the processor. There are two such cores in my proposed design that are connected by an on-chip network, similar to TPU v2 [21]. I describe these structures and estimate the area and power requirements of WaveCore below.

**Local Buffers.** Both A and B local input buffers are double-buffered. Double buffering enables the overlap of computation within the PEs with accesses to

Figure 3.9: Per-core architecture of the WaveCore accelerator.

the global buffer and to memory and allows for very simple coarse-grain control of data transfers between buffers and memory. I choose the minimal size for each buffer, such that PEs never directly access the global buffer or memory, as this avoids access-related stalls. A half-buffer of B stores a 16b word for each PE and is thus 32KiB ( $128 \times 128 \times 16b$ ). Each half-buffer for A is 64KiB because A blocks need to be twice as large as B blocks to avoid inter-wave idle time. The output accumulation buffer is triple-buffered because it holds the current output tile while the previous tile is being written to memory and the partial gradient sums for the next tile are read. Each part of this buffer holds an entire tile of C and is 128KiB. Note that while outputs are summed in 32b precision, the final write to the output buffer quantizes to 16b precision.

**Global Buffers.** The baseline global buffer is 10MiB and has 32 banks. This is sufficient for using MBS with modern CNNs and avoiding bank access conflicts. The global buffer is connected to all local buffers via a crossbar. To avoid duplicated data loads from the global buffer, I have memory load coalescing units that maintain high effective bus bandwidth utilization. My processor is designed to operate at a 0.7GHz clock frequency, and the data bandwidth of local and global buffers are set to fully support the systolic wave pipelining.

Main Memory. The off-chip memory is connected to memory controllers, which communicate with the on-chip buffers via the crossbar switches. The baseline WaveCore uses a single HBM2 stack with 4 dice [50], which provides 8GiB off-chip DRAM with 300GiB/s data bandwidth over 8 channels (4 channels per core). I choose HBM2 because it is used by other modern training accelerators [21, 76]. I later show that cheaper GDDR or even LPDDR memory can be sufficient for WaveCore.