Copyright

by

**Eric Charles Quinnell**

2007

# The Dissertation Committee for Eric Charles Quinnell certifies that this is the approved version of the following dissertation:

# **Floating-Point Fused Multiply-Add Architectures**

| Committee:                            |   |

|---------------------------------------|---|

| Earl E. Swartzlander, Jr., Supervisor | _ |

| Jacob Abraham                         | _ |

| Tony Ambler                           | _ |

| Jason Arbaugh                         | _ |

| Adnan Aziz                            |   |

# **Floating-Point Fused Multiply-Add Architectures**

by

Eric Charles Quinnell, B.S.E.E.; M.S.E.E.

### Dissertation

Presented to the Faculty of the Graduate School of

the University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

**Doctor of Philosophy**

The University of Texas at Austin

May 2007

# For my wife Eres mi vida, mi alma, y mi corazón.

### Acknowledgements

This work on the design and implementation of the new floating-point fused multiply-add architectures would not be possible without the knowledge, expertise, and support of the following people:

#### First and foremost

Leslie K. Quinnell, my wife – for her unwavering patience, understanding, and support throughout the lifetime of this project.

### **Supervisors**

Dr. Earl E. Swartzlander, Jr., The University of Texas at Austin – for his wisdom and unparalleled knowledge in the field of computer arithmetic, as well as for single-handedly convincing a student to pursue a wild new idea.

Carl Lemonds, Advanced Micro Devices – for his vast experience and expertise in the field of x86 floating-point design, as well as his uncanny ability to plainly identify the benefits and flaws of any idea, without which these new architectures would never have been conceived.

#### The Committee

Dr. Earl E. Swartzlander, Jr.

Dr. Jacob Abraham

Dr. Tony Ambler

Dr. Adnan Aziz

Dr. Jason Arbaugh

#### **Advanced Micro Devices**

Carl Lemonds Dimitri Tan Albert Danysh Derek Urbaniak

#### Legal

Rick Friedman, The University of Texas at Austin Brian Spross, Advanced Micro Devices Antony Ng, Dillon & Yudell

#### **Family and Friends**

Leslie K. Quinnell

Don and Patricia MacIver

Charlie and Denise Quinnell

Chris and Janet King

Brig General & Mrs. Philip J. Erdle USAF (Ret)

Mrs. Marianne Quinnell

and countless others...

## Floating-Point Fused Multiply-Add Architectures

| Publication No. |  |

|-----------------|--|

| i uoncanon ivo. |  |

Eric Charles Quinnell, Ph.D. The University of Texas at Austin, 2007

Supervisor: Earl E. Swartzlander, Jr.

This dissertation presents the results of the research, design, and implementations of several new architectures for floating-point fused multiplier-adders used in the x87 units of microprocessors. These new architectures have been designed to provide solutions to the implementation problems found in modern-day fused multiply-add units.

The new three-path fused multiply-add architecture shows a 12% reduction in latency and a 15% reduction in power as compared to a classic fused multiplier-adder. The new bridge fused multiply-add architecture presents a design capable of full performance floating-point addition and floating-point multiplication instructions while still providing the functionality and performance gain of a classic fused multiplier-adder.

Each new architecture presented as well as a collection of modern floating-point arithmetic units that are used for comparison have been designed and implemented using the Advanced Micro Devices (AMD) 65 nanometer silicon on insulator transistor technology and circuit design toolset. All designs use the AMD 'Barcelona' native quadcore standard-cell library as an architectural building block to create and contrast the new architectures in a cutting-edge and realistic industrial technology.

# **Table of Contents**

| Acknowl   | edgements                                                    | V  |

|-----------|--------------------------------------------------------------|----|

| Floating- | Point Fused Multiply-Add Architectures                       | vi |

|           | Contents                                                     |    |

|           | gures                                                        |    |

|           | ables                                                        |    |

|           | 1                                                            |    |

|           | duction to the Floating-Point Fused Multiply-Add Unit        |    |

| 1.1       | Introduction                                                 |    |

| 1.2       | The Floating-Point Fused Multiply-Add Unit                   |    |

| 1.3       | Overview of the Dissertation                                 |    |

| Chapter 2 | 2                                                            |    |

|           | Work on the Floating-Point Fused Multiply-Add Architecture   |    |

| 2.1       | Introduction                                                 | 6  |

| 2.2       | The IEEE-754 Floating-Point Standard                         |    |

| 2.3       | The IBM RISC System/6000 Fused Multiplier-Adder              | 10 |

| 2.4       | The PowerPC 603e and Dual-Pass Fused Multiplier-Adder        |    |

| 2.5       | The Pseudo-Fused Multiplier-Adder                            | 19 |

| 2.6       | Reduced Power Fused Multiplier-Adders                        | 20 |

| 2.7       | A Fused Multiplier-Adder with Reduced Latency                |    |

| 2.8       | Multiple Path Fused Multiplier-Adder                         | 24 |

| 2.9       | 3-Input LZA for Fused Multiplier-Adders                      | 28 |

| 2.10      | A Fused Multiplier-Adder with Floating-Point Adder Bypass    | 29 |

| 2.11      | A Comparison of Literature                                   |    |

| Chapter 3 | 3                                                            | 34 |

|           | and Components using AMD 65nm SOI                            | 34 |

| 3.1       | Introduction                                                 |    |

| 3.2.1     | Design and Implementation Method Overview                    |    |

| 3.2.2     | High-Level Design – Verilog RTL                              |    |

| 3.2       | 2.1 Verilog 2K HDL and the VCS Compiler                      |    |

| 3.2.      | 2.2 Novas Debussy Debugger                                   |    |

| 3.2.3     | Front-End Implementation – The AMD AXE Flow                  |    |

| 3.2       | <i>5</i>                                                     |    |

| 3.2       | J                                                            |    |

| 3.2       | $\mathcal{G}_{\mathcal{J}}$                                  |    |

| 3.2       | J                                                            |    |

| 3.2       |                                                              |    |

| 3.2       | $\sigma$                                                     |    |

| 3.2       | 3.7 Power Estimation – HSim with axe-extracted SPICE netlist | 64 |

| 3.3 Fl       | oating-Point Components                                         | 66           |

|--------------|-----------------------------------------------------------------|--------------|

| 3.3.1        | Radix-4 53-bit x 27-bit Multiplier Tree                         | 68           |

| 3.3.2        | Kogge-Stone Adders, Incrementers, and Carry Trees               | 73           |

| 3.3.3        | Leading-Zero Anticipators (LZA)                                 |              |

| 3.3.4        | Miscellaneous Components                                        | 82           |

| Chapter 4    |                                                                 | 83           |

| References j | for Comparison: A Floating-Point Adder, a Floating-Point Multip | olier, and a |

|              | ed Multiplier-Adder                                             |              |

| 4.1 In       | troductiontroduction                                            | 83           |

| 4.2 D        | ouble-Precision Floating-Point Adder                            | 84           |

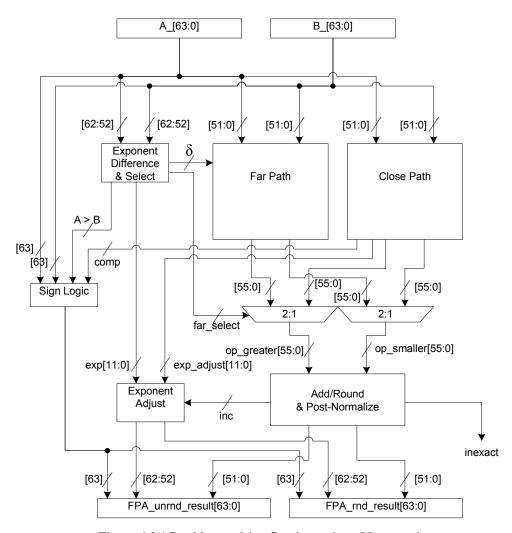

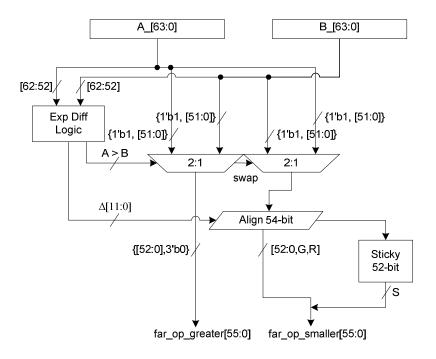

| 4.2.1        | The Far Path                                                    | 85           |

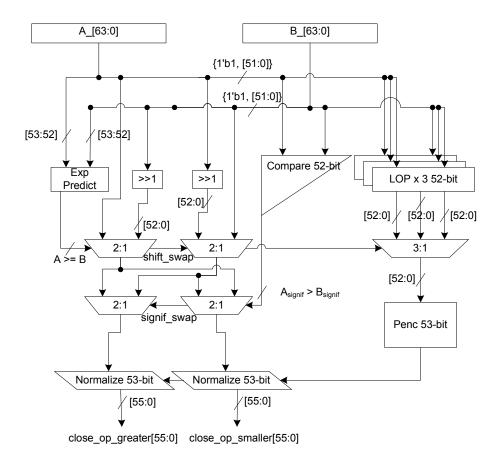

| 4.2.2        | The Close Path                                                  | 87           |

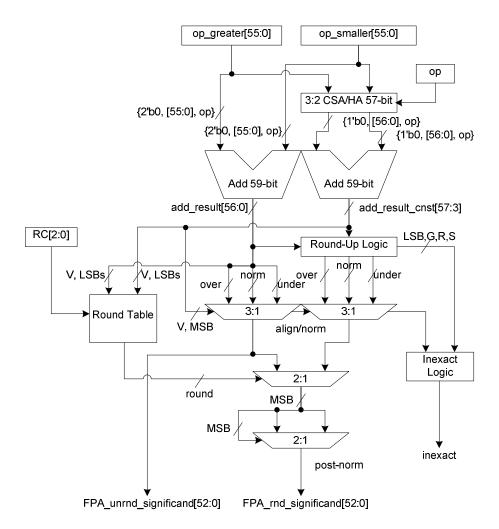

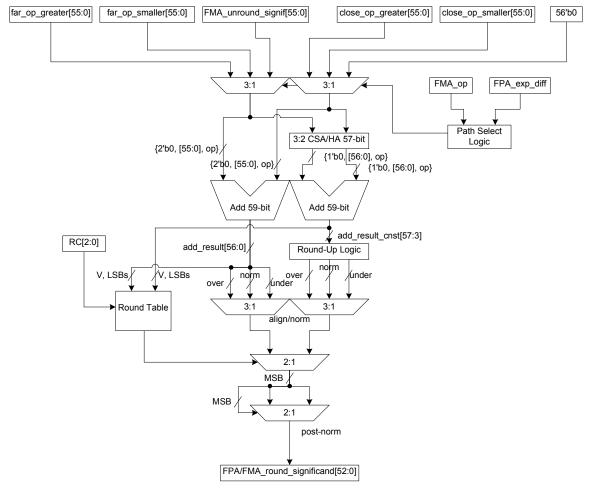

| 4.2.3        | The Add/Round Stage                                             | 89           |

| 4.2.4        | Floating-Point Adder Exponent and Sign Logic                    | 90           |

| 4.2.5        | Floating-Point Adder Results                                    |              |

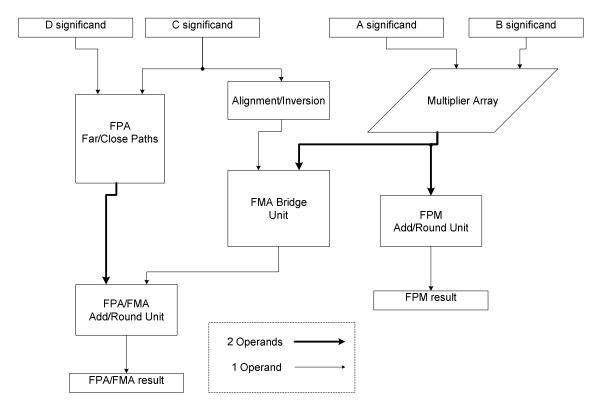

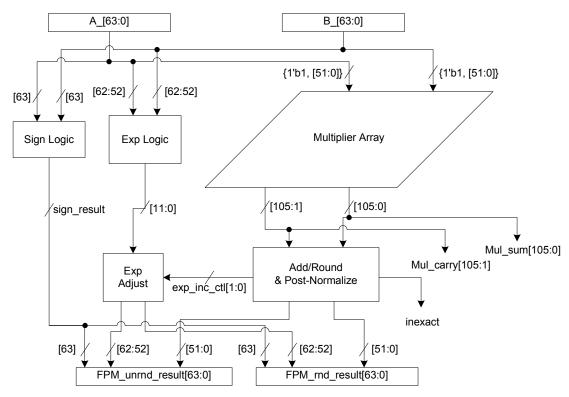

| 4.3 D        | ouble-Precision Floating-Point Multiplier                       |              |

| 4.3.1        | The Add/Round Stage                                             |              |

| 4.3.2        | Exponent and Sign Logic                                         |              |

| 4.3.3        | Floating-Point Multiplier Results                               |              |

| 4.4 D        | ouble-Precision Classic Fused Multiplier-Adder                  |              |

| 4.4.1        | Addition to Rounding Stage Specifics                            |              |

| 4.4.2        | Exponent and Sign Logic                                         |              |

| 4.4.3        | Floating-Point Classic Fused Multiplier-Adder Results           |              |

| Chapter 5    |                                                                 |              |

|              | Path Fused Multiply-Add Architecture                            |              |

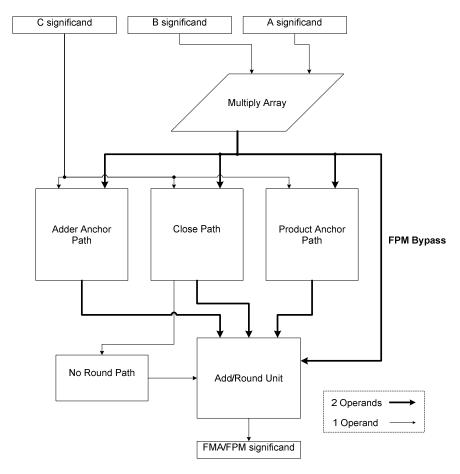

|              | troduction                                                      |              |

|              | hree-Path Fused Multiply-Add Architecture                       |              |

| 5.2.1        | The Anchor Paths                                                |              |

| 5.2.2        | The Close Path                                                  |              |

| 5.2.3        | The Add/Round Stage                                             |              |

| 5.2.4        | Exponent and Sign Logic                                         |              |

|              | hree-Path Fused Multiplier-Adder with Multiplier Bypass         |              |

|              | hree-Path Fused Multiplier-Adder Results                        |              |

|              |                                                                 |              |

|              | Fused Multiply-Add Architecture                                 |              |

| _            | troduction                                                      |              |

|              | he Bridge Fused Multiply-Add Architecture                       |              |

| 6.2.1        | The Multiplier                                                  |              |

| 6.2.2        | The Bridge                                                      |              |

| 6.2.3        | The Adder                                                       |              |

| 6.2.4        | The Add/Round Unit                                              |              |

|              | he Bridge Fused Multiplier-Adder Results                        |              |

|              |                                                                 |              |

| -            | s and Future Work                                               | 142          |

| 7.1       | Conclusions | 142 |

|-----------|-------------|-----|

| 7.2       | Future Work | 145 |

| Bibliogra | aphy        | 146 |

| U         |             |     |

# **List of Figures**

| Figure 1.2.1 Simple block diagram of a floating-point fused multiplier-adder          | 3    |

|---------------------------------------------------------------------------------------|------|

| Figure 2.2.1 The IEEE-754 single and double precision floating-point data types [20]  | 9    |

| Figure 2.3.1 Block diagram showing the combination of add and multiply (right,        |      |

| redrawn) [1]                                                                          | . 11 |

| Figure 2.3.2 Alignment range for the 3rd operand in a multiply-add fused operation    |      |

| (redrawn) [1]                                                                         | . 12 |

| Figure 2.3.3 Original fused multiply-add unit (redrawn) [2]                           | . 13 |

| Figure 2.8.1 The fused multiply-add 5 data range possibilities [29]                   |      |

| Figure 2.8.2 Suggested implementation for a 5-case fused multiply-add (redrawn) [28]  |      |

| Figure 2.10.1 Lang/Bruguera fused multiply-add with floating-point adder capabilities |      |

| (redrawn) [32]                                                                        |      |

| Figure 3.2.2.1 Radix-4 Booth multiplexer                                              | . 38 |

| Figure 3.2.2.2 Verilog code for a radix-4 Booth multiplexer                           |      |

| Figure 3.2.2.3 A Verilog input/output stimulus file                                   |      |

| Figure 3.2.2.4 UNIX output of VCS compile and simulation                              |      |

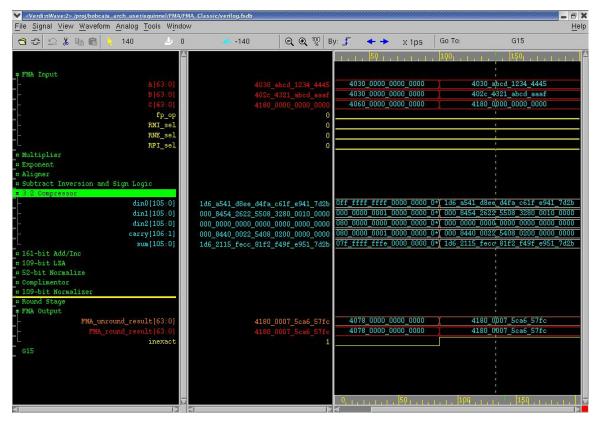

| Figure 3.2.2.5 Novas Debussy debugger                                                 | . 44 |

| Figure 3.2.2.6 Verilog behavioral checkpoint code                                     | . 44 |

| Figure 3.2.2.7 Debussy behavioral checkpoint screenshot                               |      |

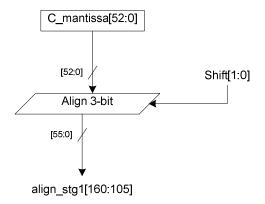

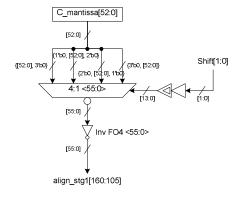

| Figure 3.2.3.1 Gate-level schematic of a 3-bit aligner                                |      |

| Figure 3.2.3.2 Gate-level Verilog of a 3-bit aligner                                  | . 49 |

| Figure 3.2.3.3 UNIX output of axe -flat (part 1)                                      | . 50 |

| Figure 3.2.3.4 UNIX output of axe -flat (part 2)                                      |      |

| Figure 3.2.3.5 UNIX output of axe -u2v                                                |      |

| Figure 3.2.3.6 UNIX output of axe –formal                                             |      |

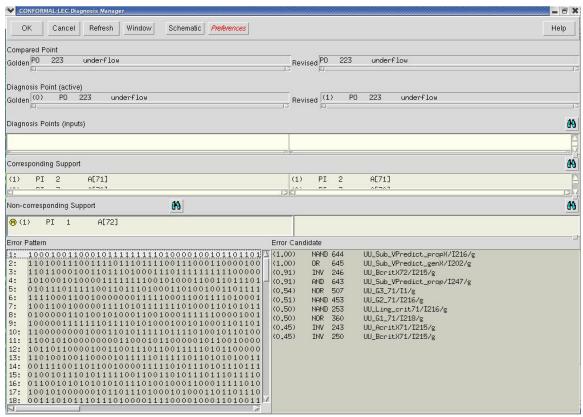

| Figure 3.2.3.7 LEC error vector screen                                                | . 54 |

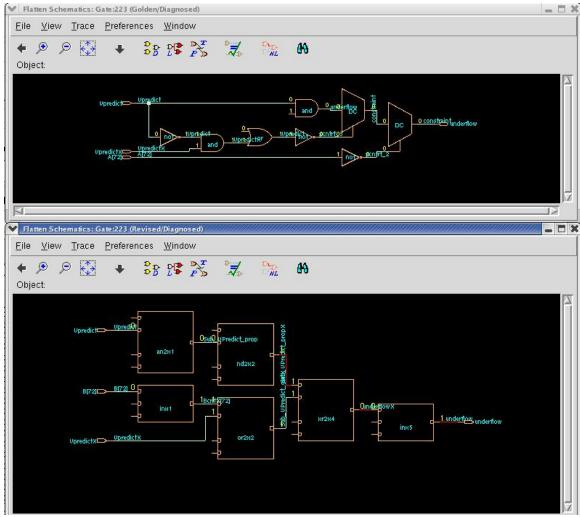

| Figure 3.2.3.8 LEC schematic debugger                                                 | . 55 |

| Figure 3.2.3.9 UNIX output of axe -place (part 1)                                     | . 56 |

| Figure 3.2.3.10 UNIX output of axe -place (part 2)                                    | . 57 |

| Figure 3.2.3.11 PX placement code for an adder sum block                              | . 58 |

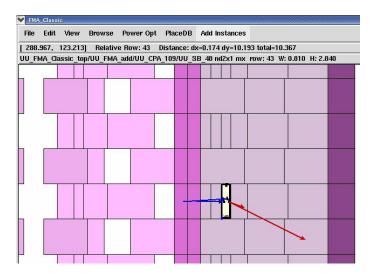

| Figure 3.2.3.12 VP output of a cell with I/O flyline interconnects                    | . 59 |

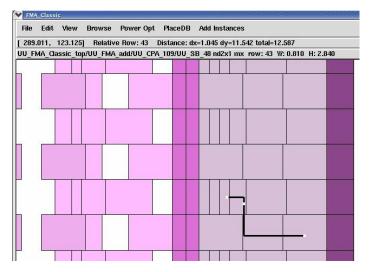

| Figure 3.2.3.13 VP output of a cell with a Steiner output interconnect                | . 60 |

| Figure 3.2.3.16 UNIX output of axe –espftime                                          | . 63 |

| Figure 3.2.3.17 A segment from a parsed Primetime report                              | . 63 |

| Figure 3.2.3.18 A segment from a re-sizing script                                     | . 63 |

| Figure 3.2.3.19 A segment from a edgerate report                                      | . 63 |

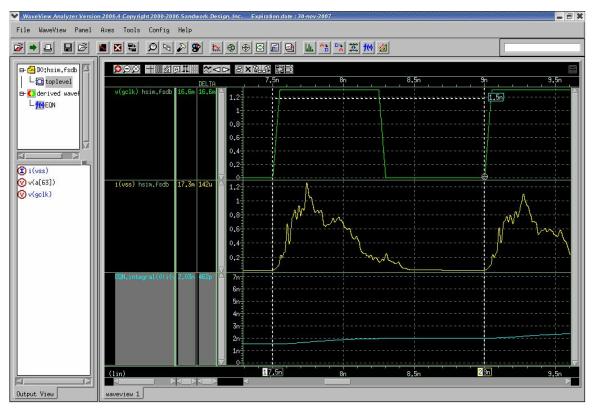

| Figure 3.2.3.20 UNIX output of a HSim power simulation                                |      |

| Figure 3.2.3.21 Spice Explorer power simulation screenshot                            |      |

| Figure 3.3.1 Booth encoded digit passed to a Booth multiplexer                        | . 69 |

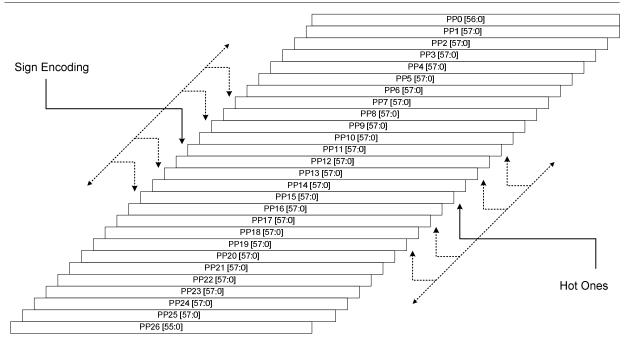

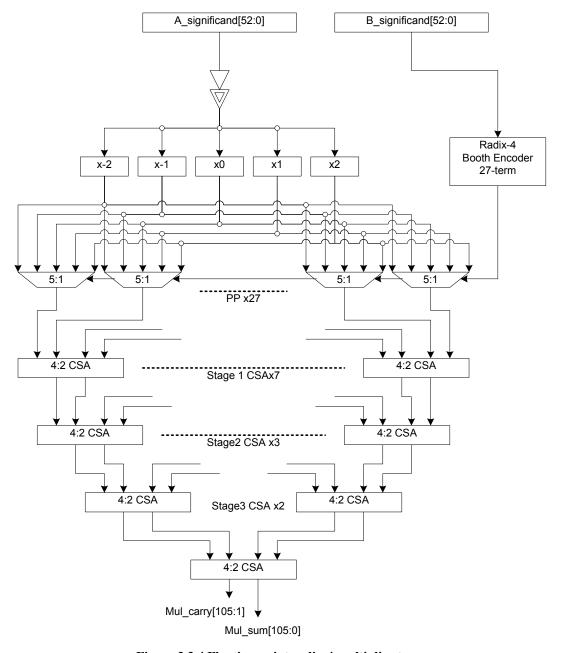

| Figure 3.3.2 Multiplier 27-term partial product array                  | 70  |

|------------------------------------------------------------------------|-----|

| Figure 3.3.3 "Hot one" and "sign encoding" of a partial product        | 71  |

| Figure 3.3.4 Floating-point radix-4 multiplier tree                    |     |

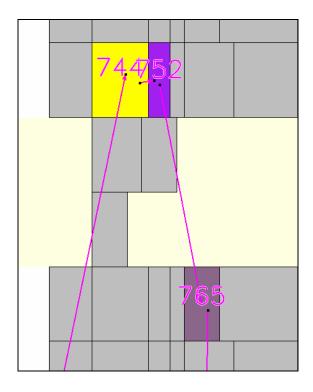

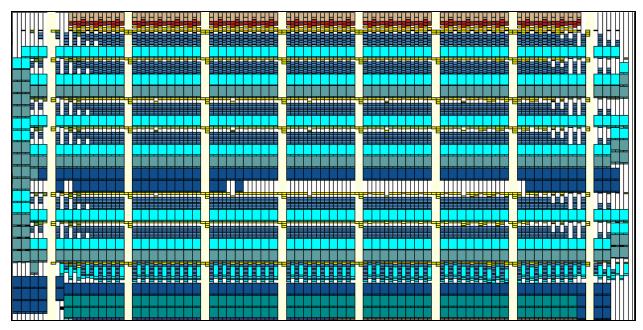

| Figure 3.3.5 Multiplier tree floorplan                                 | 73  |

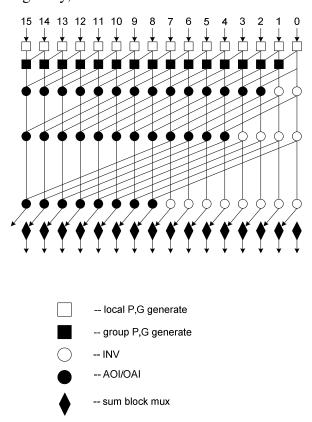

| Figure 3.3.6 Kogge-Stone prefix adder and its components [34]          | 74  |

| Figure 3.3.7 Kogge-Stone 109-bit adder                                 |     |

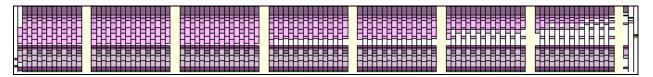

| Figure 3.3.8 Block view of the 109-bit adder                           | 76  |

| Figure 3.3.9 Kogge-Stone 52-bit incrementer                            | 76  |

| Figure 3.3.10 Kogge-Stone 13-bit adder                                 | 76  |

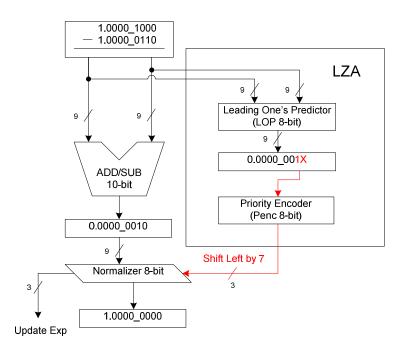

| Figure 3.3.11 LZA 9-bit floating-point example                         | 78  |

| Figure 3.3.12 Leading one's prediction (LOP) equations in Verilog      | 79  |

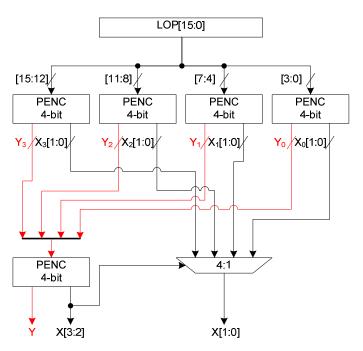

| Figure 3.3.13 Priority encoder 16-bit                                  | 80  |

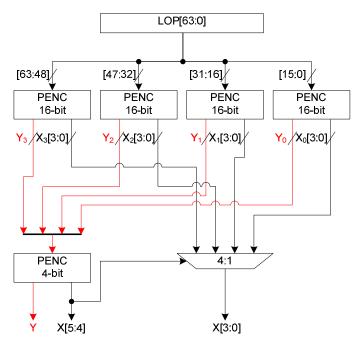

| Figure 3.3.14 Priority encoder 64-bit                                  | 81  |

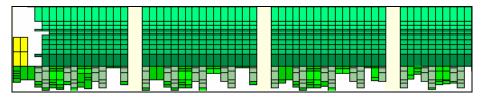

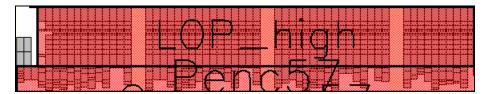

| Figure 3.3.15 LZA 57-bit floorplan                                     | 82  |

| Figure 3.3.16 LZA 57-bit blocks                                        | 82  |

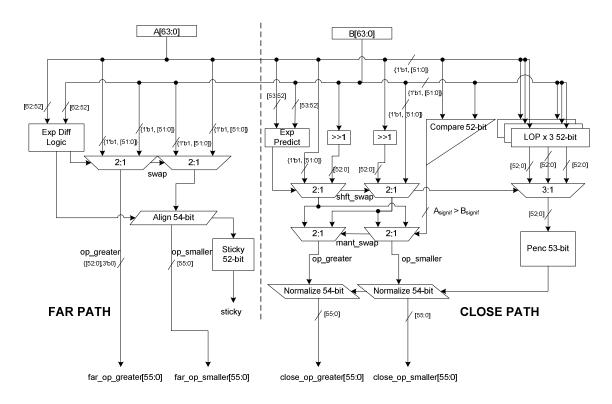

| Figure 4.2.1 Double-precision floating-point adder top view            | 85  |

| Figure 4.2.2 Floating-point adder far path                             | 86  |

| Figure 4.2.3 Floating-point adder close path                           | 88  |

| Figure 4.2.4 Floating-point adder add/round stage                      | 90  |

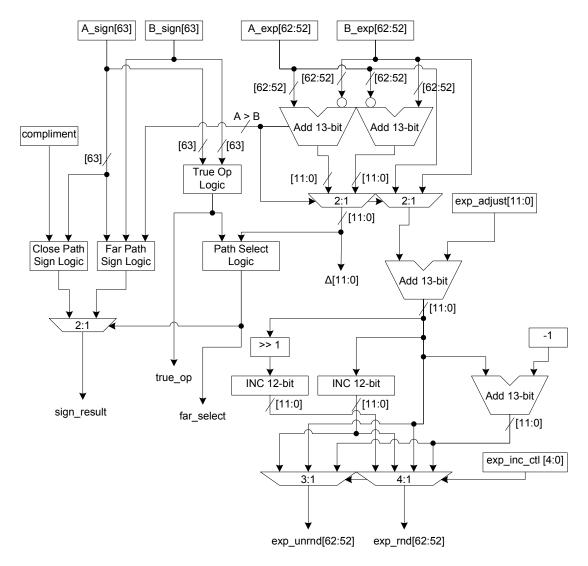

| Figure 4.2.5 Floating-point adder exponent and sign logic              | 92  |

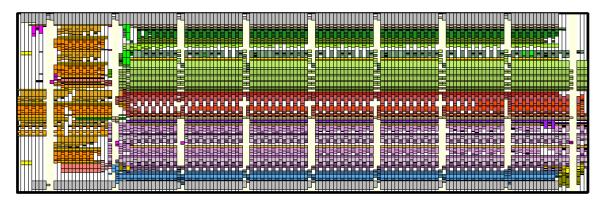

| Figure 4.2.6 Floating-point adder floorplan                            | 93  |

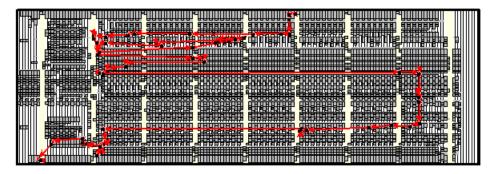

| Figure 4.2.7 Floating-point adder critical path                        | 94  |

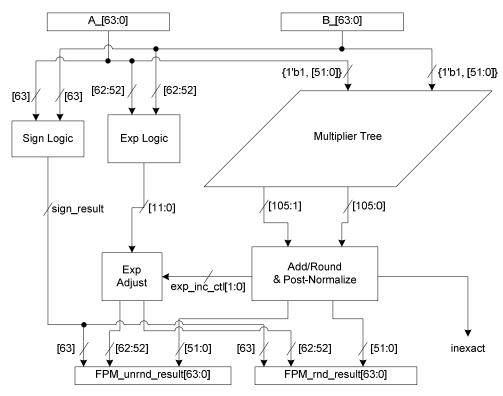

| Figure 4.3.1 Floating-point multiplier top view                        | 96  |

| Figure 4.3.2 Floating-point multiplier add/round stage                 | 97  |

| Figure 4.3.3 Floating-point multiplier exponent and sign logic         | 98  |

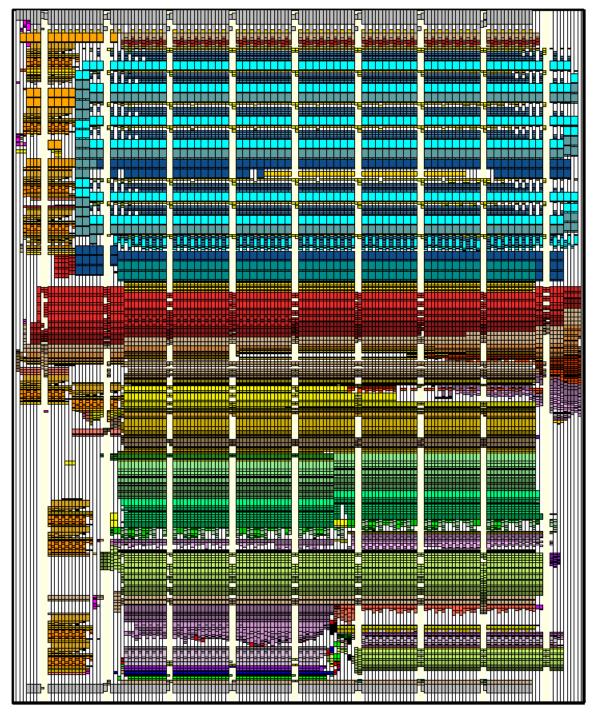

| Figure 4.3.4 Floating-point multiplier floorplan                       | 99  |

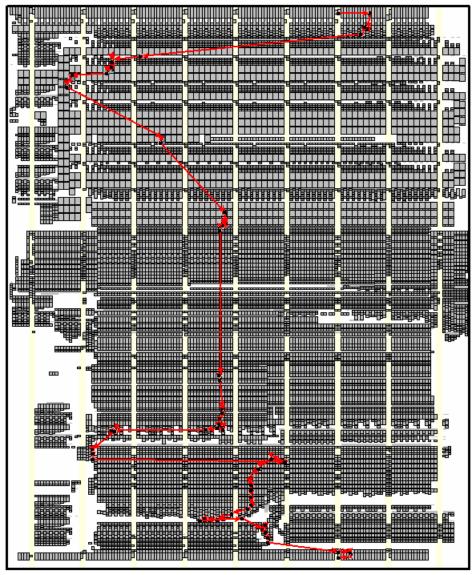

| Figure 4.3.5 Floating-point multiplier critical path                   | 100 |

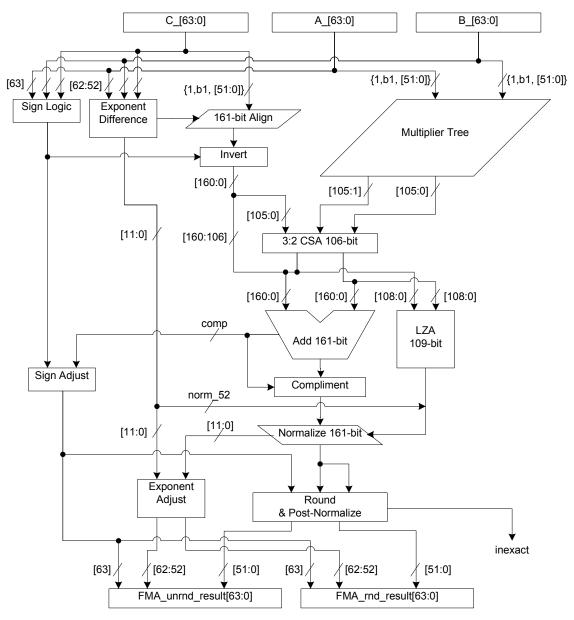

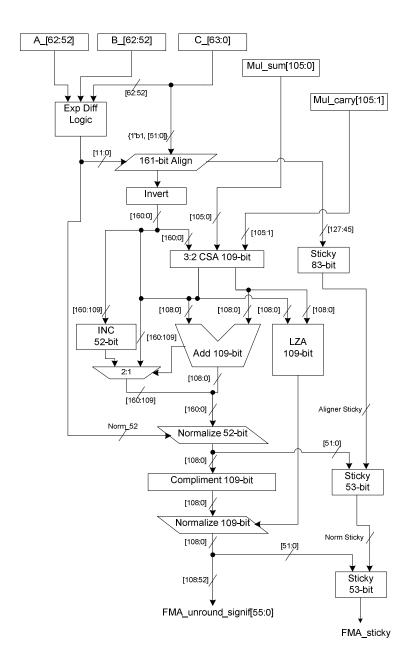

| Figure 4.4.1 Floating-point fused multiply-add top view                | 102 |

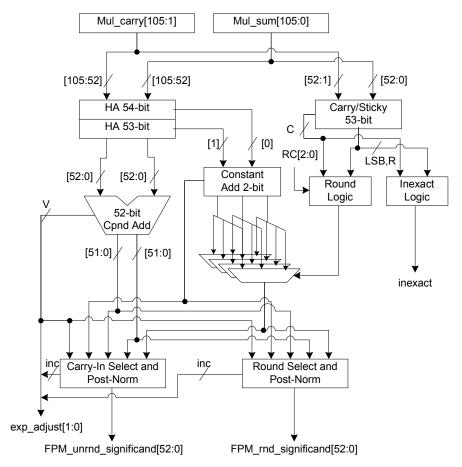

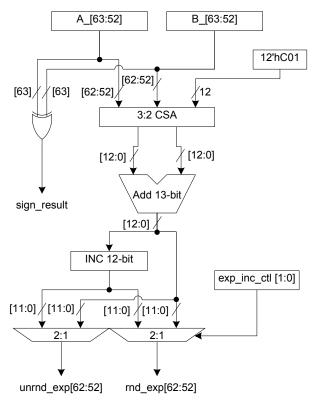

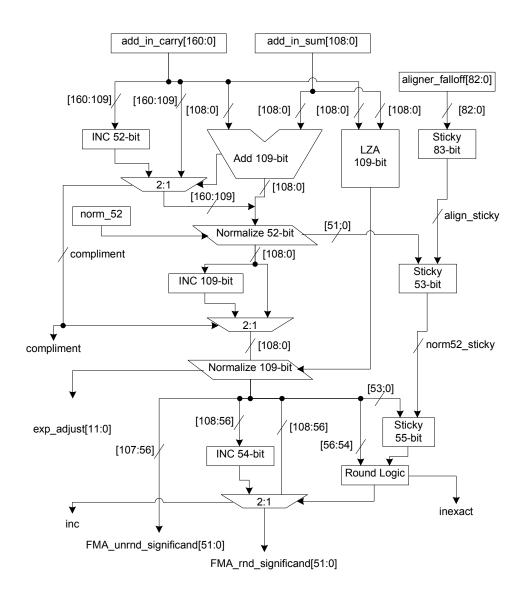

| Figure 4.4.2 Floating-point fused multiply-add addition and rounding   | 104 |

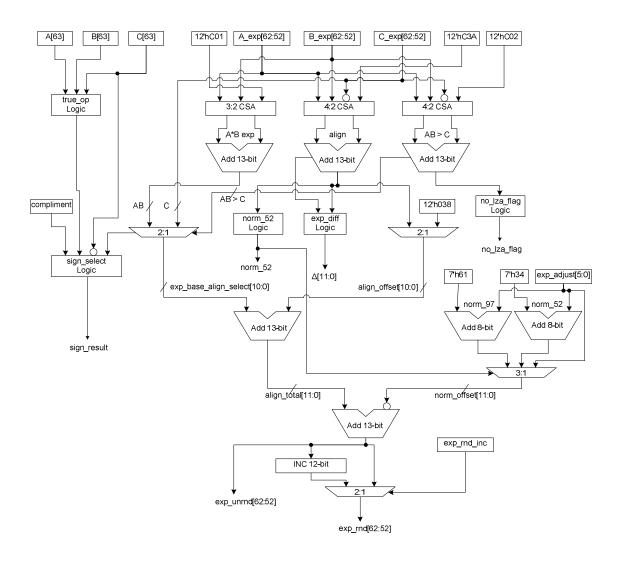

| Figure 4.4.3 Floating-point fused-multiply add exponent and sign logic | 106 |

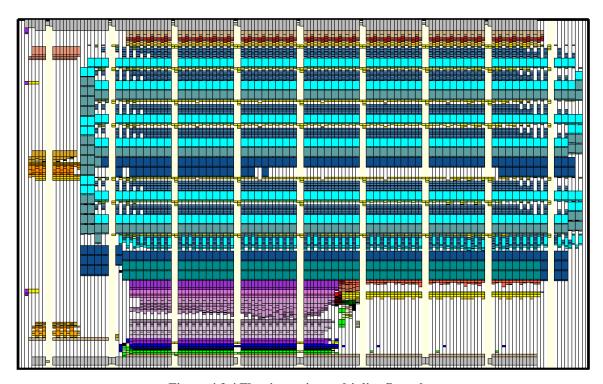

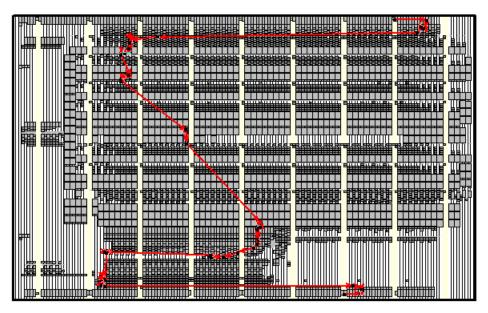

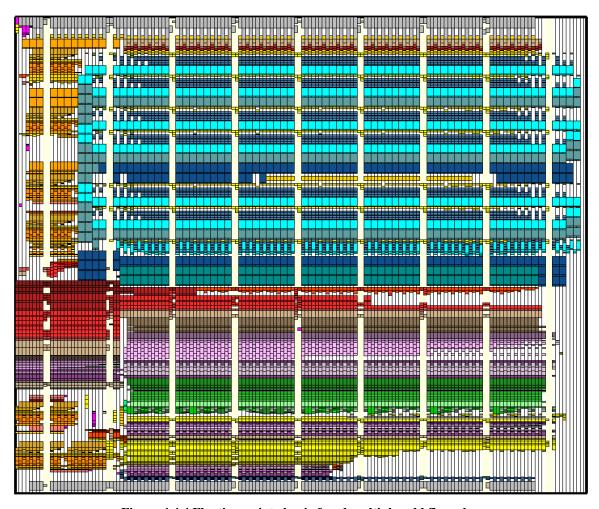

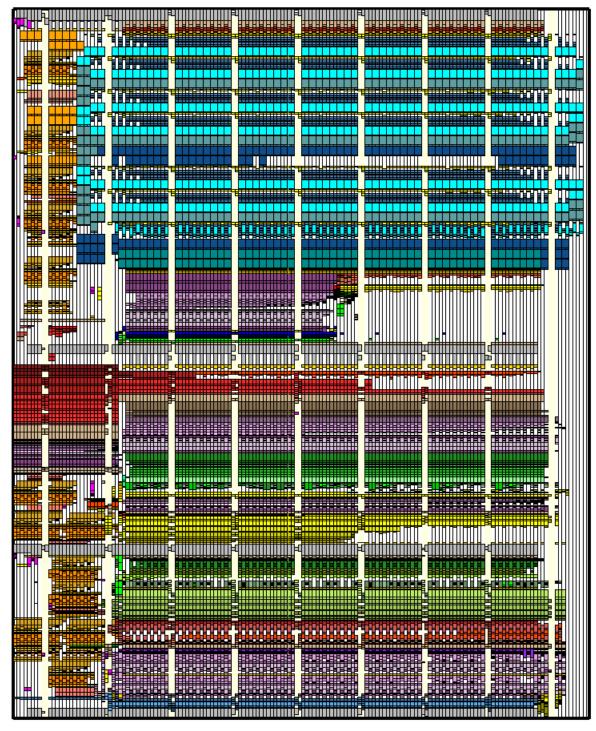

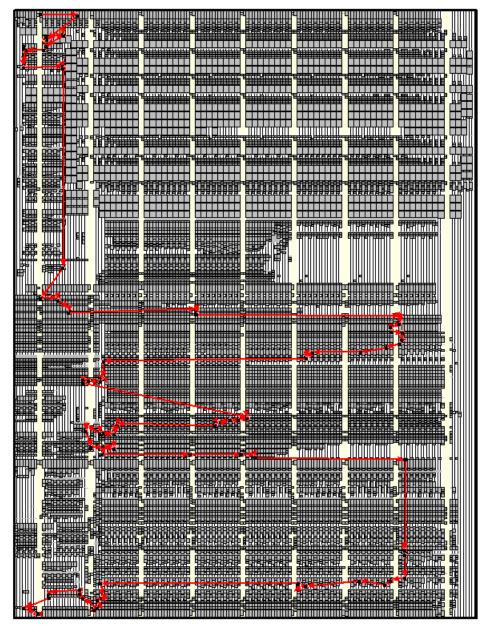

| Figure 4.4.4 Floating-point classic fused multiply-add floorplan       |     |

| Figure 4.4.5 Floating-point classic fused multiply-add critical path   | 108 |

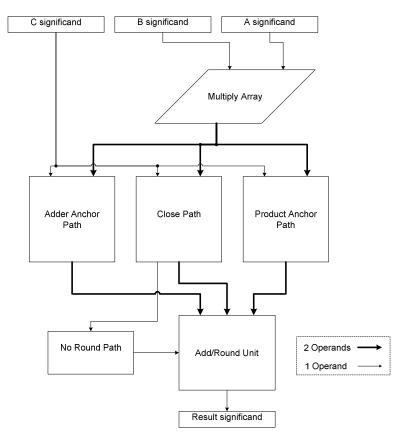

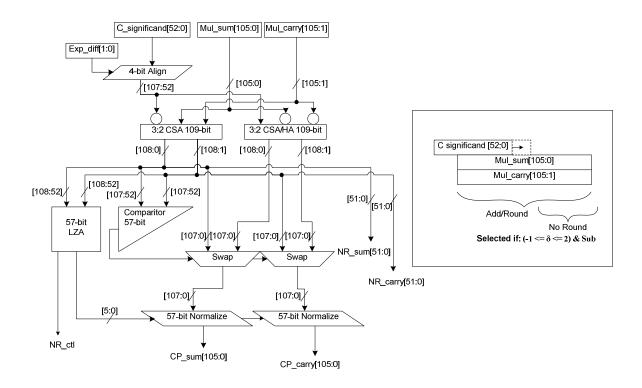

| Figure 5.2.1 Three-path fused multiplier-adder architecture            | 112 |

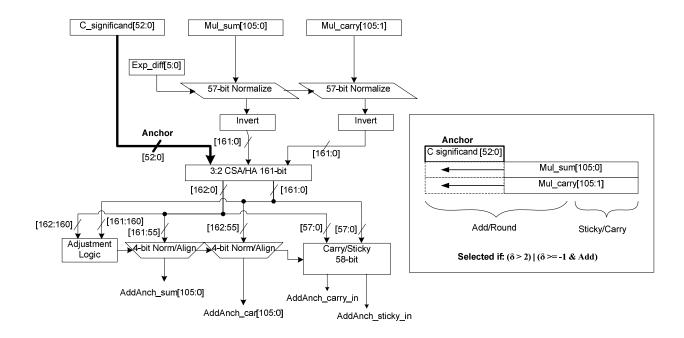

| Figure 5.2.2 The Adder Anchor Path                                     | 114 |

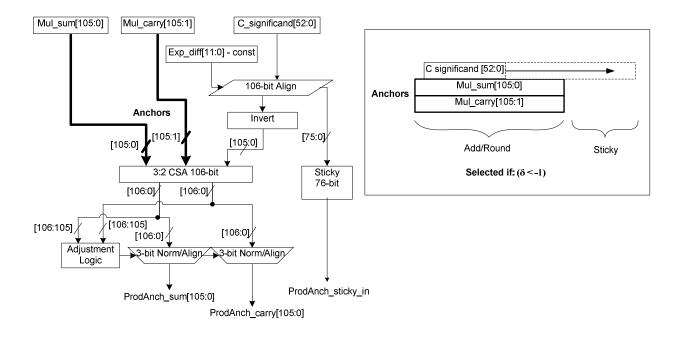

| Figure 5.2.3 The Product Anchor Path                                   | 115 |

| Figure 5.2.4 The Close Path                                            |     |

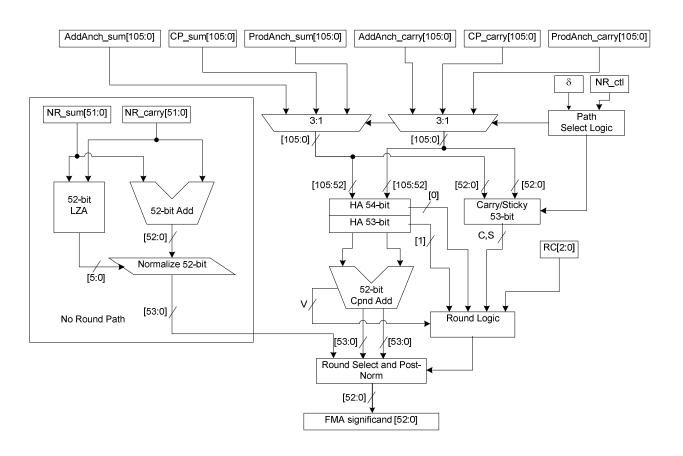

| Figure 5.2.5 The No Round Path (left) and Add/Round Stage (right)      | 118 |

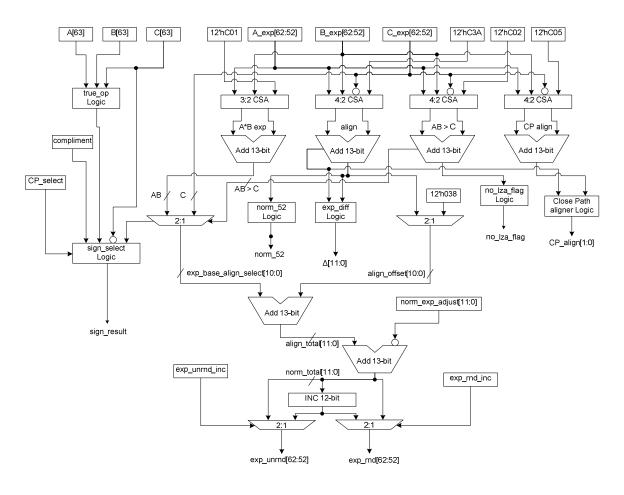

| Figure 5.2.6 Exponent and Sign Logic                                   |     |

| Figure 5.3.1 Three-path fused multiply-add with FPM bypass             | 121 |

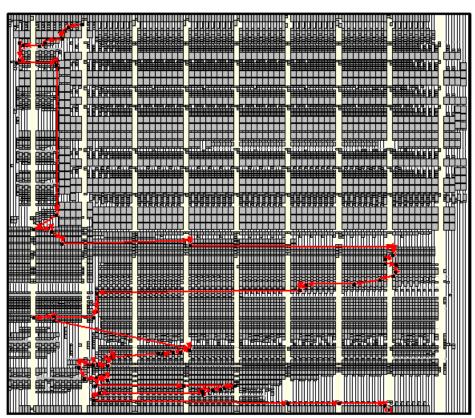

| Figure 5.4.1 Three-path fused multiply-add floorplan                   | 123 |

| Figure 5.4.2 Three-path fused multiply-add critical path               |     |

| Figure 6.2.1 The bridge fused multiply-add block diagram               |     |

| Figure 6.2.2 The Multiplier                                            |     |

| Figure 6.2.3 The Bridge                                                | 132 |

| Figure 6.2.4 The Adder                                   | 134 |

|----------------------------------------------------------|-----|

| Figure 6.2.5 The Add/Round Unit                          | 135 |

| Figure 6.3.1 The bridge fused multiply-add floorplan     | 137 |

| Figure 6.3.2 The bridge fused multiply-add critical path | 139 |

# **List of Tables**

| Table 2.2.1 The IEEE-754 table of formats [20]                        | 8   |

|-----------------------------------------------------------------------|-----|

| Table 2.11.1 Comparison of proposed fused multiply-add architectures  | 33  |

| Table 3.3.1 Radix-4 Booth encoding for a multiplier tree              | 68  |

| Table 3.3.2 Multiplier color legend                                   | 73  |

| Table 4.2.1 Floating-point adder color legend                         | 93  |

| Table 4.2.2 Floating-point adder results                              | 94  |

| Table 4.3.1 Floating-point multiplier color legend                    | 99  |

| Table 4.3.2 Floating-point multiplier results                         | 100 |

| Table 4.4.1 Floating-point classic fused multiply-add color legend    | 108 |

| Table 4.4.2 Floating-point classic fused multiply-add results         | 109 |

| Table 5.4.1 Floating-point fused multiply-add color legend            | 124 |

| Table 5.4.2 Floating-point three-path fused multiplier-adder results  | 126 |

| Table 5.4.3 Floating-point fused multiplier-adder comparative results |     |

| Table 6.3.1 Bridge fused multiply-add color legend                    | 138 |

| Table 6.3.2 Bridge fused multiplier-adder results                     | 141 |

| Table 6.3.3 Raw results from various floating-point units             | 141 |

| Table 6.3.4 Results Normalized to an FPA Stand-Alone Addition         | 141 |

| Table 6.3.5 Results Normalized to an FPM Stand-Alone Multiplication   | 141 |

| Table 6.3.6 Results Normalized to a Classic Fused Multiply-Add        | 141 |

| Table 7.1.1 Comparison of proposed fused multiply-add architectures   |     |

|                                                                       |     |

# **Chapter 1**

An Introduction to the Floating-Point Fused Multiply-Add Unit

This chapter presents a brief introduction to the floating-point fused multiply-add arithmetic unit, its recent spike in interest due to 3D graphics and multimedia demands, and the problems found in its architectural implementation. The chapter finalizes with a short overview of this dissertation's research.

#### 1.1 Introduction

This dissertation presents the results of the research, design, and implementation of several new architectures for floating-point fused multiplier-adders used in the x87 units of microprocessors. These new architectures have been designed to provide solutions to the implementation problems found in modern-day fused multiply-add units, simultaneously increasing their performance and decreasing their power consumption.

Each new architecture, as well as a collection of modern floating-point arithmetic units used as reference designs for comparison, have been designed and implemented using the Advanced Micro Devices (AMD) 65 nanometer silicon on insulator transistor technology and circuit design toolset. All designs use the AMD 'Barcelona' native quad-core standard-cell library as an architectural building block to create and contrast the new architectures in a cutting-edge and realistic industrial technology.

This chapter presents an introduction to the floating-point fused multiply-add architecture, a brief discussion of its implementation benefits and problems, and a

description of the recent spike in its academic and industrial use. The chapter finishes with an overview of the dissertation.

### 1.2 The Floating-Point Fused Multiply-Add Unit

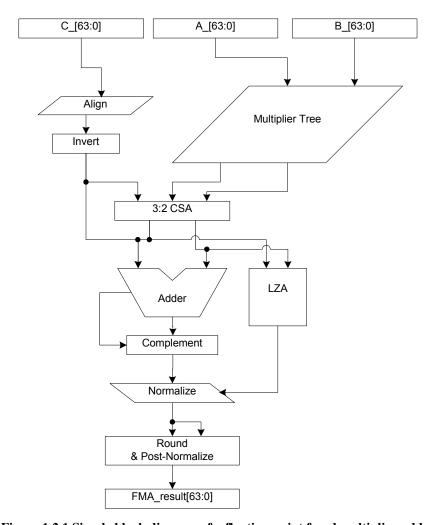

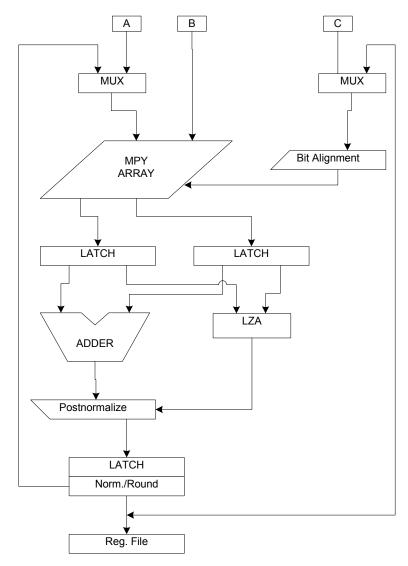

In 1990, IBM unveiled implementation of a floating-point fused multiply-add arithmetic execution unit on the RISC System 6000 (IBM RS/6000) chip [1], [2]. IBM recognized that several advanced applications, specifically those with dot products, routinely performed a floating-point multiplication, A x B, immediately followed by a floating-point addition,  $(A \times B)_{result} + C$ , *ad infinitum*. To increase these applications' performances, IBM design engineers created a new unit that merged a floating-point addition and floating-point multiplication into a single hardware block—the floating-point fused multiplier-adder. This floating-point arithmetic unit, seen in Figure 1.2.1, executes the equation  $(A \times B) + C$  in a single instruction.

The floating-point fused multiply-add unit has several advantages in a floating-point unit design. Not only can a fused multiplier-adder improve the performance of an application that recursively executes a multiplication followed by an addition, but the unit may entirely replace an x87 co-processor's floating-point adder and floating-point multiplier.

A fused multiplier-adder may emulate a floating-point adder and floating-point multiplier by inserting fixed constants into its data path. A floating-point addition is executed by replacing the equation operand B with 1.0, forming the equation  $(A \times 1.0) + C$ . Likewise, a floating-point multiplication is executed by replacing operand C with 0.0, forming the equation  $(A \times B) + 0.0$ . This simple injection of constants allows a floating-point fused multiplier-adder to be built as the stand-alone, all-purpose execution unit inside a floating-point co-processor.

However, such advantages do not come without a cost. Although an application may experience increased performance when a program requires multiplications followed by additions, others that require single-instruction additions or single-instruction

multiplications without the cross-over experience a significant decrease in performance. A fused multiply-add unit may be able to emulate a floating-point adder or floating-point multiplier, but the block's additional hardware imposes extra latency on the stand-alone instructions as compared to their original units.

Figure 1.2.1 Simple block diagram of a floating-point fused multiplier-adder

Single instruction latencies are not the only disadvantage to a floating-point fused multiplier-adder. The unit's internal components require bit-widths and interconnectivities commonly more than double that of components found in floating-point adders and floating-point multipliers. With the increasing presence of the parasitic constraints found in designs with massive interconnectivity [3] - [5], the fused multiply-

add architecture is quickly becoming not only a design with difficult timing goals, but also one with heavy power consumption.

The pros and cons of the fused multiplier-adder are well known, and the list of disadvantages has historically driven industry to avoid the unit's use in x87 designs. However, modern-day applications have grown in complexity, requiring a noticeably increased use of the fused multiply-add equation  $(A \times B) + C$ .

For instance, the fused multiply-add is now used in applications for DSP and graphics processing [6], [7], FFTs [8], FIR filters [6], division [9], and argument reductions [10]. To accommodate this increased use of the fused multiply-add instruction, several commercial processors have implemented embedded fused multiply-add units in their silicon designs. These chips include designs by IBM [1], [11]-[13], HP [14], [15], MIPS [16], ARM [6], and Intel [17], [18].

With the continued demand for 3D graphics, multimedia applications, and new advanced processing algorithms, not to mention the IEEE's consideration of including the fused multiply-add into the 754p standard [19], the performance benefits of the fused multiply-add unit is beginning to out-weigh its drawbacks. Even though the fused multiply-add architecture has troublesome latencies, high power consumption, and a performance degradation with single-instruction execution, it may be fully expected that more and more x87 designs will find floating-point fused multiply-add units in their silicon.

# 1.3 Overview of the Dissertation

Chapter 2 presents the complete history, advancement, and academic design suggestions of the floating-point fused multiply-add architecture presented by published literature. The chapter begins with the IEEE-754 standard [20] followed by an original description of the IBM RS/6000 unit and finishes with the most recent fused multiply-add publication.

Chapter 3 provides the details of how a circuit is designed and implemented in the AMD 65nm silicon on insulator technology and toolset environment. Following the toolset description, the chapter also presents the results of a custom-implemented floating-point component library which was used by each design in this dissertation.

Chapter 4 presents the design and implementation results of three standard floating-point units created as a reference for comparison. The designs include a floating-point adder, floating-point multiplier, and a modern implementation of a floating-point classic fused multiplier-adder.

Chapter 5 presents the design and implementation of a new floating-point three-path fused multiply-add architecture created to simultaneously increase the performance and reduce the power consumption of a fused multiply-add instruction. The results of the implementation are directly compared to the results from the floating-point classic fused multiply-add unit from Chapter 4.

Chapter 6 presents the design and implementation of a new floating-point bridge fused multiply-add architecture created to allow full-performance executions of single floating-point instructions while still providing the performance benefits of a fused multiply-add architecture. The results of this implementation are directly compared to the results of the floating-point adder, floating-point multiplier, and floating-point classic fused multiplier-adder from Chapter 4.

Chapter 7 summarizes the design results and highlights the benefits and disadvantages of the two new floating-point fused multiply-add architectures. This chapter concludes the dissertation.

# Chapter 2

Previous Work on the Floating-Point Fused Multiply-Add Architecture

This chapter provides a description of previous significant works on the floating-point fused multiply-add architecture, including an overview of the original IBM RS/6000.

#### 2.1 Introduction

Several works for the reduction of latency or power consumption in floating-point fused multiply-adders have been published since IBM's original papers on the RS/6000 [1], [2]. This chapter presents the invention and proposed advancements or implementations of the fused multiply-add unit in chronological order. These publications come from both industry circuit implementations and academic architecture proposals.

While not all suggestions for improved fused multiplier-adders have actually been implemented, much of the already completed research provides insight to the variety of complications found in the original architecture. Each paper listed in this section after the original provides a different approach to the design of floating-point fused multiply-add units in an attempt to deviate from the industry-wide acceptance of IBM RS/6000 style architectures. The research presented is fully comprehensive and presents all major advancements to the fused multiply-add architecture to date.

The chapter begins with a brief summary of the IEEE-754 standard [20], followed by the research papers on floating-point fused multiply-add units. Papers that do not present changes to the original fused multiply-add architecture or those that are only industry implementation reports are not described in this chapter.

### 2.2 The IEEE-754 Floating-Point Standard

The field of floating-point computer arithmetic is a sub-section of computer engineering that concentrates on the development and execution of complex mathematics in modern-day microprocessors. The family of floating-point chips and co-processors are the units in a microprocessor that execute advanced applications such as 3D graphics, multimedia, signal processing, Fourier transforms, and just about every variety of scientific, engineering, and entertainment solutions that require complex mathematics.

The floating-point notation is the electronic world's binary equivalent form of scientific notation for decimal values. A binary floating-point number may represent a vast range of real numbers, including values approaching the infinitely large to those approaching the infinitely small—all in a compact and finite bit-width. In a floating-point number, a selection of binary bits representing an integer fraction hold a numerical position in the real number plane based on another selection of binary bits representing an exponent. The rules that define and govern this floating-point format are enumerated in the Institute of Electrical and Electronics Engineers (IEEE) specification document reference number 754, known as the IEEE-754 floating-point standard [20].

The IEEE-754 standard sets down specific rules and formats for any electronic processing system that uses floating-point arithmetic. The 754 begins by defining precision and exponent parameters for its description of floating-point formats as follows:

```

p = the number of significant bits (precision)

E_{max} = the maximum exponent

E_{min} = the minimum exponent

```

It then specifies all binary numeric floating-point numbers to be represented by bits in the following three fields:

```

1) 1-bit sign s

```

<sup>2)</sup> Biased exponent e = E+bias

<sup>3)</sup> Fraction  $f = b_1 b_2 \dots b_{p-1}$

where

s = 0 or 1 E = any integer between Emin and Emax, inclusive  $b_i = 0$  or 1

These bits represent an actual number by listing them in the following form:

Number =

$$(-1)^s \times 2^e \times (1.b_1b_2...b_{p-1})$$

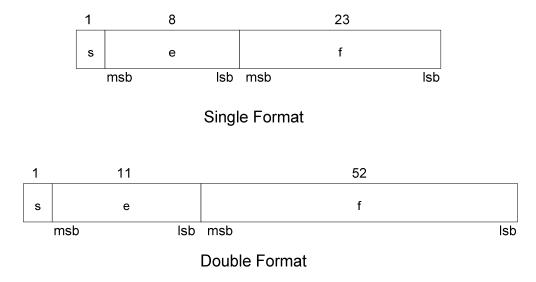

The standard goes on to list the parameter values and their respective names, all listed in Table 2.2.1. For example, a "single precision" floating point format uses 24 bits to represent an implicit one and 23 fraction bits (i.e., 1.*fraction*), 8 bits to represent exponents from the range  $2^{+127}$  to  $2^{-126}$  (approximately 1.7 x  $10^{38}$  and 1.18 x  $10^{-38}$  respectively) and one bit for the sign (i.e., 0 for positive or 1 for negative). The standard lists single, double, and extended precisions as floating-point data type options, each respectively increasing in numerical range and precision.

Table 2.2.1 The IEEE-754 table of formats [20]

| Format                 |        |      |                 |        |                 |

|------------------------|--------|------|-----------------|--------|-----------------|

| Parameter              | Single |      | Single Extended | Double | Double Extended |

| р                      |        | 24   | ≥ 32            | 53     | ≥ 64            |

| E <sub>max</sub>       |        | 127  | ≥ +1023         | 1023   | ≥ +16383        |

| E <sub>min</sub>       |        | -126 | ≤ -1022         | -1022  | ≤ -16382        |

| Exponent bias          |        | 127  | unspecified     | 1023   | unspecified     |

| Exponent width in bits |        | 8    | ≥ 11            | 11     | ≥ 15            |

| Format width in bits   |        | 32   | ≥ 43            | 64     | ≥ 79            |

In the standard's data type definition of "single precision," the 23 fraction, 8 exponent, and 1 sign bit may be stored in a single 32-bit register or memory location. The implicit '1' from the fraction is just that, and does not need to be included in the register. "Double precision" is stored in a 64-bit register or memory location. Figure 2.2.1 shows the bit partitioning of the stored binary words.

Figure 2.2.1 The IEEE-754 single and double precision floating-point data types [20]

After the enumeration of formats and precisions, the IEEE 754 standard lists a set of requirements for rounding methods. In a floating-point arithmetic calculation, (i.e., a floating-point addition) the result, since it is a fractional representation, may have bits that are too small to include in the format specified. However, leaving them out will alter the correct answer, creating error.

To consider calculation errors, the 754 standard requires any compliant application to support four rounding methods: round to nearest even, round toward plus infinity, round toward minus infinity, and round toward zero. These methods give application programmers the power to determine what kind of rounding error correction is best for their design. In hardware designs conforming to this requirement, generally the rounding stage is at the end of an execution block.

Following the section on rounding, the 754 standard enumerates the required mathematical functions that must be supported in a floating-point machine. The list requires the implementation of the following operations: add; subtract; multiply; divide; square root; remainder; round to integer in floating-point format; convert between

floating-point formats; convert between floating-point and integer; convert binary to decimal; and compare. In the recent meetings of the IEEE-754 committee, currently known as the IEEE 754r, the inclusion of the fused multiply-add function,  $z = a + b \times c$ , is being considered as an addition to the floating-point operation standard [19].

The formats, rounding, and operation requirements of the IEEE-754 standard listed here are important for the complete understanding of the project described in this and following chapters. All designs, simulations, implementations, as well as most previous publications are in IEEE-754 double precision, 64-bit format and conform to the rounding methods described.

### 2.3 The IBM RISC System/6000 Fused Multiplier-Adder

In January of 1990, a paper by Robert K. Montoye, Erdem Hokenek, and S. L. Runyon was published in the *IBM Journal of Research and Development* on the design of the RISC System/6000 floating-point execution unit [1]. The journal publication was followed by an *IEEE Journal of Solid-State Circuits* paper published in October 1990 [2]. These papers included details on the invention of the multiply-add fused unit, or what later became more commonly known as the same name rearranged: the fused multiply-add unit, or the multiply-accumulate chained (MAC) unit.

The original paper [1] states that "the most common use of floating-point multiplication is for 'dot-product' operations" and that "a single unit which forms the multiply-accumulation operation  $D = (A \times B) + C$  would produce a significant reduction in internal busing requirements."

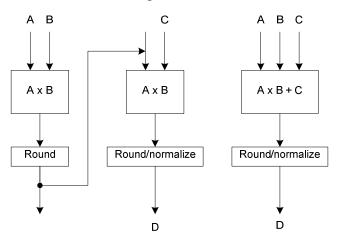

What the paper states is that the equation  $D = (A \times B) + C$  was at the time a highly-used group of operations in the floating-point unit. The problem with the operation is that a floating-point multiplication and round must first take place before the floating-point addition and round is performed. If a single unit were produced that performs the whole

operation in one block, several benefits could be realized. The original block diagram describing the combination is shown in Figure 2.3.1.

Figure 2.3.1 Block diagram showing the combination of add and multiply (right, redrawn) [1]

The papers go on to describe additional benefits of combining the floating-point adder and floating-point multiplier into a single functional unit. First, the latency for a multiply-add fused mathematical operation is reduced significantly by having an addition combined with a multiplication in hardware. Second, the precision of the final result is increased, since the operands only go through a single rounding stage. Third, there is a decrease in the number of required input/output ports to the register file and their controlling sub-units. Finally, a reduced area of both the floating-point adder and floating-point multiplier may be realized since the adder is only wired to the output connections of the multiplier.

Reference [1] follows these enumerated points with a basic description of the architecture required for a fused multiply-add unit. Since three operands are used in the fused multiply-add operation, the floating-point data must be handled in a range of normalization different than that found in the standard floating-point adder or floating-point multiplier.

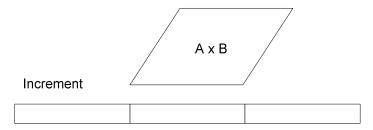

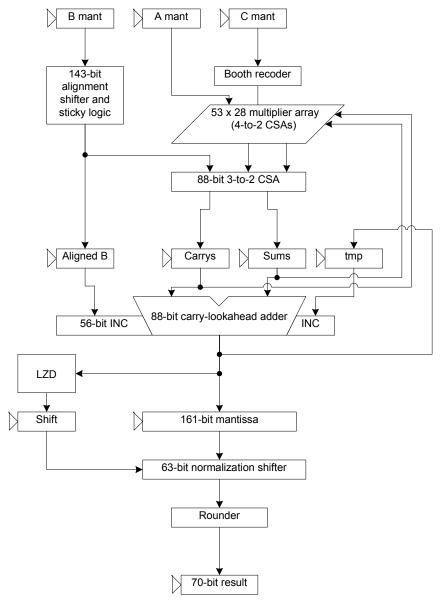

In multiplication, the product word size is double the bit-width of the operands. In a floating-point addition, the addition operand (i.e., the addend) is shifted to align the implicit binary point so that the operands are properly aligned when they are added. In an extreme case of addition, the addend's binary point may line up at any position with respect to the product. To cover all of the addition and multiplication cases without losing precision, a fused multiply-add operation must be a full three times the size of the original operator bit widths to correctly normalize the data. Figure 2.3.2 shows the required alignment data-range.

Figure 2.3.2 Alignment range for the 3rd operand in a multiply-add fused operation (redrawn) [1]

Reference [2] describes this normalization problem as one of the tradeoffs required in a fused multiply-add unit. The large bit range requires a very large shifter which can add a significant latency to the operation. The solution presented is the pre-alignment of the addend in parallel with the multiplication.

The second challenge in combining a floating-point multiplication with a floating-point addition comes again from the large precision range. To perform an addition in double precision format, a fused multiply-add unit requires a 161-bit adder. This creates a very difficult timing arc in implementation.

For the adder's case of massive cancellation, which is a case when lots of leading '0's result from a subtraction of nearly identical operands, the leading '1' must be found and the data normalized. To do this, a leading-zero detector (LZD) is included in the fused multiply-add unit and runs in parallel with the massive adder. The LZD is built to find the

first '1' position in the result before the addition is completed, allowing a pre-calculated normalization control to immediately shift the output data from the adder.

Paper [2] presents the original fused multiply-add architecture as built on the IBM RS/6000 shown in Figure 2.3.3. The IBM RS/6000 was implemented in  $1\mu m$  CMOS silicon technology at IBM.

Figure 2.3.3 Original fused multiply-add unit (redrawn) [2]

### 2.4 The PowerPC 603e and Dual-Pass Fused Multiplier-Adder

The first papers of note after the RS/6000 on fused multiply-add units are [12] and [13]. Both are on the same subject and contribute the same ideas, just in different detail.

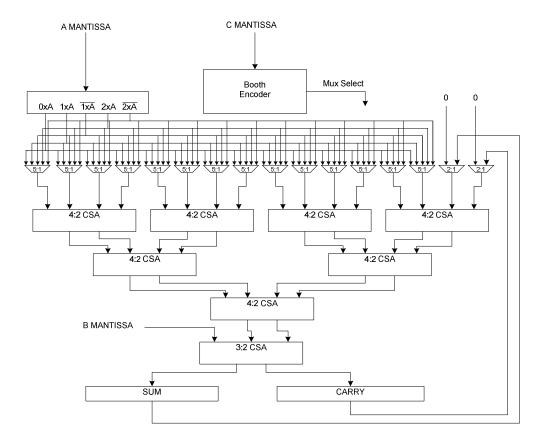

Paper [12] is on the implementation of the PowerPC 603e microprocessor. This paper provides three main contributions for the fused multiply-add architecture: first, the paper provides far better detail and descriptions of the original IBM RS/6000 architecture with slight improvements; second, it uses a dual-pass iterative technique in the multiplier to reduce the area and power consumption of the overall fused multiply-add unit; third, the adder/complement stage uses an iterative dual-pass end around carry (EAC) adder that reduces the overall adder size by replacing bit ranges with incrementors. The PowerPC 603 fused multiply-add architecture is shown in Figure 2.4.1.

Figure 2.4.1 Block diagram of the PowerPC 603e fused multiply-add unit (redrawn) [12]

The fused multiply-add architecture presented is in essence the same as the IBM RS/6000. First, a large addend aligner that runs in parallel to the multiplier array meets up with the product data in a 3:2 carry-save adder (CSA). The operands are added together in a 161-bit adder while an LZD calculates the shift amount for the normalization shifter. The result is then rounded and passed out of the block.

Although the general architecture is the same as that of the IBM RS/6000, the PowerPC 603e uses far less area and power in exchange for additional cycles. Specifically, each double-precision fused multiply-add instruction must pass through the multiplier block twice before a correct carry save product is calculated.

The details of the iterative components are described thoroughly in [13]. These components are specifically designed to accelerate the performance of single-precision data types. The iterative multiplier scheme reduces the logic in the CSA critical path by a full half. While this makes the tree too small for double-precision numbers, a single-precision instruction is able to produce a product in one multiplier cycle.

To implement this scheme, both the adder and multiplier have the ability to hold for a second cycle during a double-precision fused multiply-add instruction. The iterative multiplier, shown in Figure 2.4.2, adds together partial products like any standard CSA tree for the first cycle. For the second cycle, the partial product result from the first iteration is fed back into the tree and combined with the new partial products.

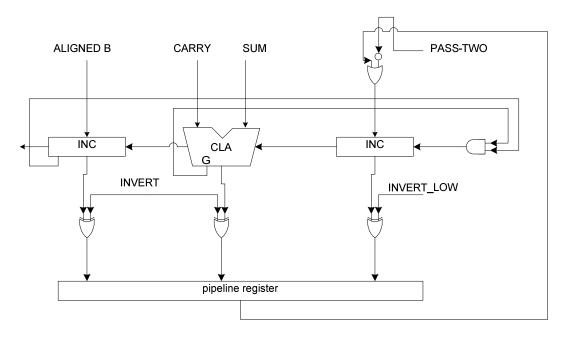

The dual-pass EAC adder, shown in Figure 2.4.3, performs an addition in every cycle regardless of the data type. In the first pass of a double-precision calculation, a selection of the lower product bits are added together and fed-back to the addition stage. Since many of the low-end partial products are complete in the first iteration, they do not need to be re-combined with the higher-order product from the multiplier second pass. Instead, the bits are passed to an incrementer for the case of EAC 2's complementation.

Figure 2.4.2 Iterative Booth radix-4 multiplier CSA tree [13]

Figure 2.4.3 Dual-pass, iterative EAC adder [13]

In any fused multiply-add case, the high 55-bits of the 161-bit adder input range may only come from the addend and never the multiplier product. Since the product result has a fixed internal bit position, the addend must align with respect to the product. If the addend is much greater than the product, only the top 55-bits of the 161-bit adder result are required. In this case, the product is only used in carry propagation and rounding, so the top 55-bits only come from the addend. If the product is much larger than the addend, the top 55-bits of the 161-bit internal range are all '0's due to the fixed position of the product, so the 161-bit addition result discards the top 55-bits and normalizes the product instead.

Since the design only requires carry propagation in the high 55-bits of the 161-bit adder range, an incrementer is used instead of an adder. The carry-out from this high-end incrementer is passed back to the carry-in of the low-end incrementer, completing the EAC scheme. In total, the 161-bit CPA from the RS/6000 fused multiply-add architecture is reduced in the 603e to an 88-bit EAC CPA with incrementers on each side.

To finalize, the iterative, dual-pass fused multiply-add architecture provides lower single-precision latency, as well as a large reduction in area and power by its creative implementation of the adder and multiplier array. The cost of these gains comes from the taxation of double-precision operations with an extra cycle. These data types can therefore only get half the throughput of single-precision instruction vectors.

The floating-point fused multiply-add architecture described in [12] and [13] has been physically implemented on the IBM PowerPC 603e floating-point unit in 0.5µm CMOS silicon technology.

### 2.5 The Pseudo-Fused Multiplier-Adder

Naini, Dhablania, James, and Das Sarma presented a paper in 2001 on the implementation of the HAL SPARC64 [21]. The paper is not specifically about a fused multiply-add unit, but does provide a very interesting idea on an architectural arrangement named the "pseudo-fused multiply-add."

In the implementation of the HAL SPARC64, the FPU architecture provides support for a fused multiply-add instruction via two pseudo-fused multiply-add instructions:

- unfused-floating-point multiply-add (uFMADD)

- unfused-floating-point multiply-subtract (uFMSUB)

The SPARC chip itself has two floating-point execution pipelines that can calculate up to two independent fused multiply-add instructions. The pipelines each include a standard floating-point adder (floating-point adder) and floating-point multiplier (floating-point multiplier) with pseudo-fused multiply-add bus handling. This pseudo-fused multiply-add handler is simply a forwarding bus that takes the result from a pipeline's floating-point multiplier and sends it directly to the pipeline's floating-point adder, bypassing the register file. Although bypass buses are now common place in modern FPUs, the bus presented is specifically for pseudo-fused multiply-add instructions.

The pseudo-fused multiply-add does not combine the hardware of the floating-point multiplier and adder. Instead, each floating-point multiplication performs rounding on the data before forwarding the result to the adder on the reserved fused multiply-add bus. The floating-point adder unit uses a third operand from the register file and adds it to the forwarded result. The final pseudo-fused multiply-add is rounded and sent back to the FPU register file. The dual pipe SPARC FPU architecture is shown in Figure 2.5.1 in its original form.

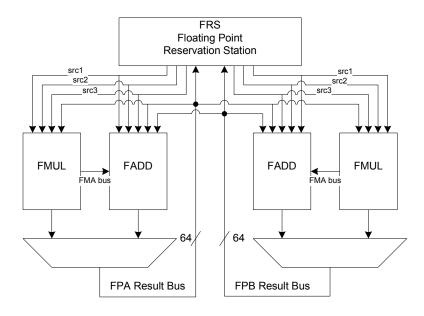

Figure 2.5.1 Dual unit floating-point unit with pseudo-fused multiply-add forwarding buses [21]

The results presented for the SPARC FPU show a latency of 3 cycles for a floating-point addition or floating-point multiplication, and a latency of 4 cycles for a pseudo-fused multiply-add instruction. The HAL SPARC64 has been implemented on  $0.15\mu m$  CMOS silicon technology.

### 2.6 Reduced Power Fused Multiplier-Adders

Later in 2001, Pillai, Shah, A. J. Al-Khalili, and D. Al-Khalili presented a paper that compares the IBM RS/6000 architecture with a proposed architecture specifically designed for power reduction [22]. The general philosophy of the architecture is to provide two parallel computation paths (as well as a bypass for floating-point multipliers) that process under different data range assumptions. Early in the pipeline, as soon as the correct path is known via the exponent difference, the other path pipeline is gated and the inputs hold the previous state, saving power.

Figure 2.6.1 (redrawn for clarity) shows the paper's proposed architecture—the Concordia fused multiplier-adder. The Concordia architecture uses alignment blocks before the multiplier array in a move to pre-shift the operands into alignment. This allows

the resulting product terms to be immediately forwarded to two separate paths, each of which may be turned off via pre-calculation. The chosen path which matches the aligned data range of the operands goes on to complete the fused multiply-add instruction. As an added feature, a third partial bypass path is allowed for floating-point multiplier single instructions to have reduced latency.

Figure 2.6.1 Concordia fused multiplier-adder (redrawn) [22]

A complication of the Concordia architecture comes from the alignment before the multiplier array. An operand aligned before the multiplier widens the multiplier tree input range, requiring either a larger variable multiplier tree or a loss of precision by parsing lower bits for power savings and latency reduction. The paper's description and arguments for the acceptance of small ulp errors in digital signal processing applications suggest that the Concordia fused multiplier-adder uses the in-accurate multiplier implementation option in pursuit of lower power consumption and latencies.

The paper finalizes by presenting a 44% reduction in power consumption and a 9% latency reduction in the Concordia architecture as compared to the IBM RS/6000 design (re-built on the same technology for comparison). The architecture was synthesized on both 0.35  $\mu$ m CMOS silicon technology as well as a FPGA and simulated with digital signal processing application data to produce the results.

### 2.7 A Fused Multiplier-Adder with Reduced Latency

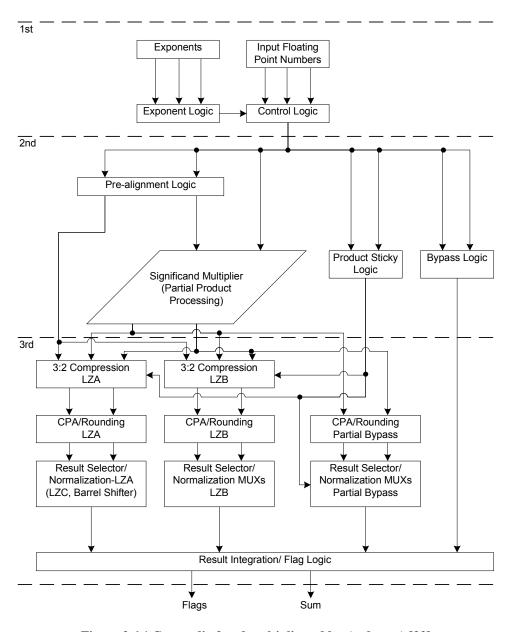

The greatest deviation from the original IBM RS/6000 architecture comes from a paper by T. Lang and J.D. Bruguera on a reduced latency fused multiplier-adder [23]. This proposal claims to achieve a significant increase in fused multiply-add unit performance by the combination of the addition and rounding stage into one block. Although the add/round stage is a widely used component in modern floating-point adder and floating-point multiplier architectures as seen in [24] – [27], its use in a fused multiplier-adder proves to be more difficult.

Lang and Bruguera describe that in order to combine the addition and rounding stages in a fused multiply-add unit, the add/round block must follow the leading-zero anticipator (LZA) normalization stage. Much like a floating-point adder in cases of massive cancellation, the location of the floating-point itself must be determined before any rounding is performed. If the addition and rounding occur simultaneously, then the required compound adder must logically follow the normalization.

The reduced latency fused multiply-add architecture is shown in Figure 2.7.1. In this design, the aligned addend combines with the multiplier product much in the same way as in the IBM RS/6000. However, immediately after the CSA, the data enter two complementary half adder (HA) paths. Sign detection logic determines the correct inversion, selects the correct HA result, and passes the data to the normalization stage.

The correctly inverted data stall at the normalization stage and waits for LZA shift control. In this architecture, the LZA itself is on the critical path. To reduce the time between the multiplier output and the first normalization shift, the authors design a special LZA encoder that produces the control signals on an accelerated path. These signals exit the LZA one bit at a time as they are calculated, as opposed to a standard encoder which selects all the outputs from a parallel multiplexer simultaneously. As each control exits the block, it drives its respective multiplexer normalization.

When the data exit the normalization stage, it is split between a 51-bit compound adder and a 108-bit carry/sticky block. The carry/sticky block creates and passes the rounding information bits to rounding control, which then selects the correct augmented adder output. The data are post-normalized, and the fused multiply-add is complete.

The paper claims an estimated 15-20% reduction in latency as compared to a standard fused multiply-add [23]. This result is calculated theoretically, and the actual architecture has yet to be implemented in either a synthesized or a custom CMOS silicon design.

Figure 2.7.1 Lang/Bruguera combined addition/rounding stage fused multiply-add (redrawn) [23]

# 2.8 Multiple Path Fused Multiplier-Adder

Peter-Michael Seidel wrote a paper in 2003 that proposes a multiple path fused multiply-add architecture to selectively execute on different data ranges for increased performance [28]. Much like the architecture of a common dual-path floating-point adder, the

proposed architecture uses pre-determined data range assumptions that perform different operations on parallel hardware.

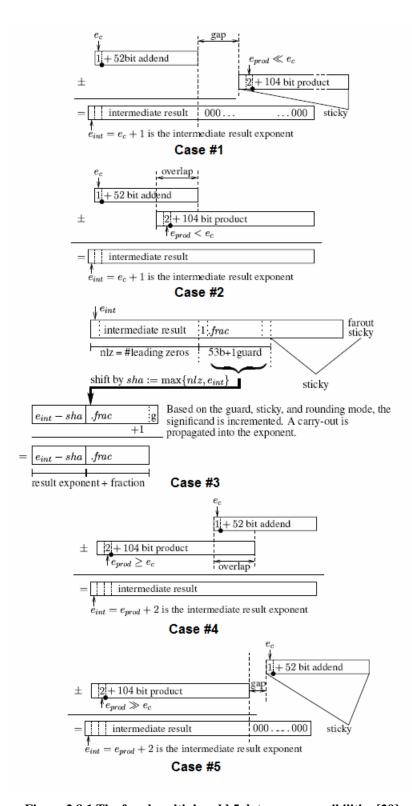

Seidel specifically suggests that a fused multiply-add may be split up into 5 distinct cases, all based on the difference in the exponents ( $\delta = [A_{exp} + B_{exp}] - C_{exp} + BIAS$ ):

- 1.  $\delta \leq -54$ , where the addend is far greater than the multiplication product. The product only affects the post-normalization, depending on rounding mode.

- 2.  $-54 < \delta \le -3$ , where the addend is greater than the product. The product operands are aligned and added.

- 3.  $-2 \le \delta \le 1$ , where the product and addend may cause massive cancellation during a subtraction. This case is handled like the close path in a dual-path adder.

- 4.  $2 \le \delta < 53$ , where the product dominates the upper digits of the result. The addend is aligned and added.

- 5.  $53 \le \delta$ , where the product term is much greater than the addend. The addend only affects rounding.

Each fused multiply-add range case listed is seen in Figure 2.8.1. The bit descriptions are all for IEEE double-precision operands.

Figure 2.8.1 The fused multiply-add 5 data range possibilities [29]

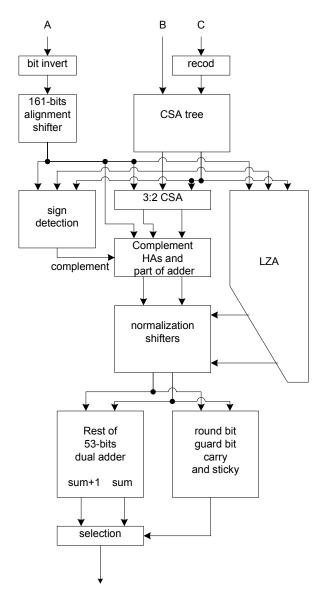

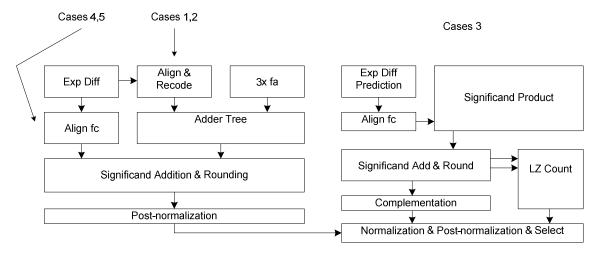

The paper goes on to suggest an implementation for a fused multiply-add unit that considers the ranges of the five cases as shown in Figure 2.8.2. The implementation uses two parallel hardware paths—one for the far exponent differences and one for the close exponent difference. Much like [22], the far path uses two aligner blocks to selectively shift operands based on the specific data range. For range case 1 and 2, one of the multiplier operands is shifted before entering the multiplier tree. For case 4 and 5, the addend is aligned to the position of the multiplier product.

The hardware suggestion for the implementation of the close exponent difference case performs an alignment on the addend to match the significand product. The data are passed to a combined add and round stage that processes in parallel to a LZA block. The add/round result is complemented if necessary, and normalized by the LZA.

The multiple path fused multiply-add paper claims around a 30% gain in performance as compared to a IBM RS/6000 architecture [28]. These performance gains are estimated based on theoretical calculations.

Figure 2.8.2 Suggested implementation for a 5-case fused multiply-add (redrawn) [28]

# 2.9 3-Input LZA for Fused Multiplier-Adders

In 2005, Xiao-Lu presented a paper [30] for the specific improvement of the critical path found in the Lang and Bruguera fused multiply-add architecture [23]. Specifically, the paper presents a new algorithm for accelerating the LZA stage in the fused multiply-add, since the LZA block is the critical path in Lang and Bruguera's scheme.

Modern architectures design LZA blocks to predict the leading '1' in a massive cancellation subtraction based on the derivation of a set of equations [31]. These leading one's prediction (LOP) equations, as seen in Figure 2.9.1, pass to an encoder which generates normalizing signals correct to within one digit. These equations  $(f_i)$  are generated on the assumption that the predicted result consists of two operands.

$$t_{i} = a_{i} \otimes b_{i}$$

$$g_{i} = a_{i} \cdot b_{i}$$

$$z_{i} = \overline{a_{i}} \cdot \overline{b_{i}}$$

$$f_{i} = t_{i-1} \cdot (g_{i} \cdot \overline{z_{i+1}} + z_{i} \cdot \overline{g_{i+1}}) + \overline{t_{i-1}} \cdot (z_{i} \cdot \overline{z_{i+1}} + g_{i} \cdot \overline{g_{i+1}})$$

**Figure 2.9.1** A two-input LZA algorithm [30]

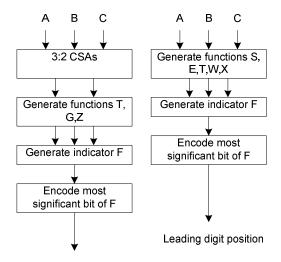

The Lang/Bruguera fused multiply-add architecture is unique, as it provides three inputs to the LZA block. In the original Lang/Bruguera paper, the three inputs are combined with a 3:2 CSA before entering the LOP unit. The Xiao-Lu paper presents new equations, shown in Figure 2.9.2, that allow this three input string to predict the leading '1'. A three-input LOP removes the requirement for a 3:2 CSA and therefore decreases the number of logic stages in a LZA. A comparison of two- and three-input LZAs is shown in Figure 2.9.3.

$$\begin{aligned} s_i &= \overline{a_i} \cdot \overline{b_i} \cdot c_i \\ e_i &= \overline{a_i} \cdot \overline{b_i} \cdot \overline{c_i} + (a_i \oplus b_i) \cdot c_i \\ t_i &= a_i \cdot b_i \cdot \overline{c_i} \\ w_i &= a_i \oplus b_i \oplus c_i \\ x_i &= a_i \cdot b_i + (a_i + b_i) \cdot \overline{c_i} \end{aligned}$$

$$f_i(pos) = e_i \cdot t_{i+1} + w_i \cdot e_{i+1} + w_{i+1} \cdot x_{i+2}$$

$$f_i(neg) = s_i \cdot \overline{x_{i+1}} + \overline{w_i} \cdot t_{i+1}$$

Figure 2.9.2 A three-input LZA algorithm [30]

Figure 2.9.3 A comparison of two- and three-input LZA algorithms [30]

Paper [30] claims the three-input LZA scheme shows a 17% reduction in latency and 20% reduction in required area as compared to a two-input scheme. The results come from a Synopsis 0.13 μm synthesis. The reduction in the LZA latency directly improves the critical path delay for a Lang/Bruguera fused multiply-add architecture.

# 2.10 A Fused Multiplier-Adder with Floating-Point Adder Bypass

The final paper included in this section is a second paper by Lang and Bruguera [32]. The paper describes a fused multiply-add architecture that enhances the functionality of their original proposal for a reduced-latency fused multiply-add unit. While in their original

paper [23] the reduced-latency fused multiplier-adder is designed to accelerate the performance of a fused multiply-add unit, the architecture shares the same disadvantage as the IBM RS/6000 design—the fused multiply-add architecture increases the latency of stand-alone floating-point additions.

The new Lang/Bruguera architecture is designed to allow a floating-point addition instruction to bypass the blocks in the fused multiply-add unit that add to its single-instruction latency. In the first Lang/Bruguera fused multiply-add unit, a floating-point adder instruction has to use the constant '1.0' (A x '1.0' + C) to propagate a multiplier input through the CSA tree, producing an addition operation. Meanwhile, the addend is sent through an aligner unit too large for a floating-point adder range, adding unnecessary latency to the data.

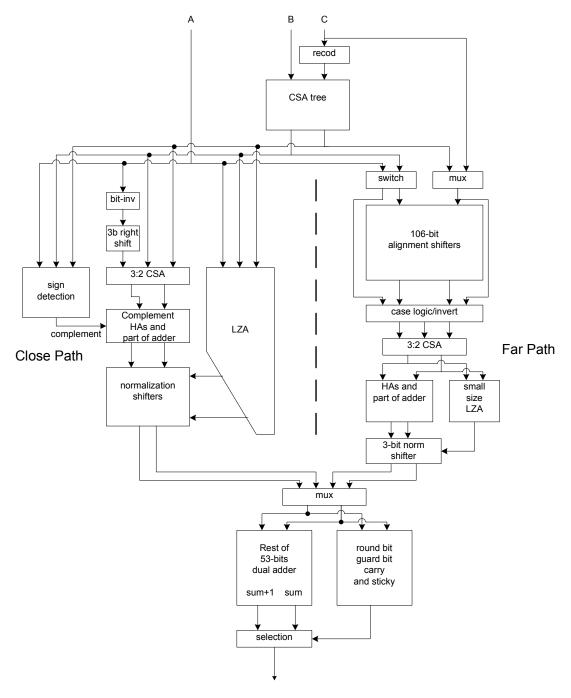

As shown in Figure 2.10.1, the new architecture uses selection multiplexers after the multiplier stage to choose different operands based on the instruction input. Mimicking common floating-point adder designs, an additional "far" path is added to the Lang/Bruguera fused multiply-add scheme for cases where the floating-point addend must still be aligned by a significant amount. This path is processed in parallel to the "close" path, which is a slight deviation from the first Lang/Bruguera fused multiply-add scheme. For floating-point adder data with close exponents, the large LZA and normalization hardware already found in the fused multiply-add path handles the operations correctly. Both paths are merged after normalization and passed to the add/round stage.

Figure 2.10.1 Lang/Bruguera fused multiply-add with floating-point adder capabilities (redrawn) [32]

However, the new architecture makes changes to how a fused multiply-add instruction is processed. In the design, the multiplier and aligner data from the head of the unit pass to both the far and close paths. The fused multiply-add data in the far path are assumed to

have a large exponent difference, so the use of a dual path parallel inversion is not required. Instead, only a single operand is needed for inversion during a subtraction, and the data may pass to a smaller size LZA. For the fused multiply-add close path, the fused multiply-add scheme follows the algorithm originally provided by Lang and Bruguera with the addition of a 3-bit aligner used in floating-point adder cases. Like the floating-point adder operation, both paths are merged after each normalization. The fused multiply-add data are added, rounded, and post-normalized, completing the instruction.

Much like the original Lang and Bruguera paper, this paper concludes by claiming a 40% acceleration of floating-point adder instructions as compared to an IBM RS/6000 fused multiply-add unit handling the same [32]. Additionally, the fused multiplier-adder provides a 10% reduction in latency compared to the IBM RS/6000. This result is calculated theoretically, and the actual architecture has yet to be implemented in either a synthesized or a custom CMOS silicon design.

The fused multiply-add unit latency reduction is lower than the original Lang and Bruguera improvements due to additional logic stages supporting a single-instruction floating-point addition. The results were calculated by theoretical delay analysis.

# 2.11 A Comparison of Literature

Table 2.11.1 shows a comparison of the various floating-point fused multiply-add architectures presented in this chapter against the original IBM RS/6000. Each design is compared against the IBM RS/6000 in the categories of latency reduction, power reduction, implementation, numerical accuracy, and whether the unit is capable of a maximum-performance single-instruction execution of a floating-point adder or floating-point multiplier.

Table 2.11.1 Comparison of proposed fused multiply-add architectures

| Design                                                    | Latency<br>vs<br>RS/6000           | Power<br>vs<br>RS/6000 | Implemented or Theoretical                | Numerically Correct? | Max-<br>performance<br>FPM? | Max-<br>performance<br>FPA? |

|-----------------------------------------------------------|------------------------------------|------------------------|-------------------------------------------|----------------------|-----------------------------|-----------------------------|

| IBM RS/6000<br>[1],[2]                                    | N/A                                | N/A                    | Implemented                               | Yes                  | No                          | No                          |

| IBM PowerPC 604e [12],[13]                                | Faster<br>SP,<br>Slower<br>DP      | ½ size<br>Mul tree     | Implemented                               | Yes                  | No                          | No                          |

| HAL SPARC64<br>(pseudo FMA)<br>[21]                       | Slower                             | N/A                    | Implemented                               | Rounded<br>Twice     | Yes                         | Yes                         |

| Concordia FMA [22]                                        | -9%                                | -44%                   | Implemented                               | No                   | Yes                         | No                          |

| Lang/Bruguera [23]                                        | -(15-<br>20%)                      | N/A                    | Theoretical                               | Yes                  | No                          | No                          |

| Seidel Multi-<br>Path [28]                                | -30%                               | N/A                    | Theoretical                               | unclear              | No                          | No                          |

| Xiao-Lu LZA<br>improvement<br>of<br>Lang/Bruguera<br>[30] | -(15-<br>20%) -<br>(0.17 x<br>LZA) | N/A                    | LZA<br>Implemented,<br>FMA<br>Theoretical | Yes                  | No                          | No                          |

| Lang/Bruguera<br>w/ FPA<br>bypass [32]                    | -10%                               | N/A                    | Theoretical                               | Yes                  | No                          | No <sup>†</sup>             |

\_

$<sup>^\</sup>dagger$  40% faster floating-point add performance as compared to a classic FMA execution of the same

# **Chapter 3**

#### Methods and Components using AMD 65nm SOI

This chapter begins by detailing the implementation methods and tools used to create a circuit in the AMD 65nm silicon on insulator design flow. Following that, the chapter lists the architectures and implementations of shared floating-point arithmetic components used in several of the final designs.

#### 3.1 Introduction

This chapter provides a detailed description of the methods and components used to design, implement, and test the floating-point fused multiply-add circuits presented in this dissertation. The designs have been implemented using the AMD 65nm silicon on insulator (SOI) transistor models and implementation design flow.

The AMD 65nm SOI circuit design flow used is also known as the AMD "axe" flow. The axe flow is a collection of industry tools and software linked together with AMD transistor libraries and databases organized in such a fashion that the progression of a circuit from RTL to GDSII "flows" through the necessary CAD tools in a logical order. This implementation flow, as well as the RTL tools and compilers that were used for designing the behavioral models, are described in detail in the first half of this chapter.

The second half of this chapter includes detailed descriptions of the floating-point components and libraries built specifically for this dissertation's floating-point fused multiply-add designs. The components, ranging from multiplier arrays and adders to barrel shifters and sticky trees, are shared in a common floating-point library that has been created to keep the components used by the designs consistent in their

implementation. These macro components are all original designs and have not been downloaded from any AMD IP database.

At AMD, the CAD tools, manufacturing models, and standard cell libraries are in a volatile consistently evolving developmental state. All of the models and tools are subjected to frequent, rapid and drastic fundamental changes to meet the demands of whatever AMD project is currently under development. Since this dissertation is intended to compare high-level architectural changes alone, a specific "snapshot" of the standard cells and tools for 65nm SOI development was taken on July 30<sup>th</sup> of 2006. This flow snapshot uses the most up to date models and libraries as of that specific date, and has ignored any further changes since then to keep the implementations consistent from origin to completion. It should be noted that the axe flow used for this dissertation is now an outdated and retired CAD system at AMD.

#### 3.2.1 Design and Implementation Method Overview

A wide variety of CAD tools are used at AMD to bring a design from concept on paper to GDSII mask data. These tools include both in-house CAD developments as well as externally written design software. Depending on the technology and goals of the design, this arrangement of tools varies in functionality and what models it considers. For the specific fused multiply-add designs considered here, this section describes in detail each step used to take the fused multiply-add architectural concepts to "front-end" design completion.

When considering the design flow at a high-level, the toolsets may be split into three major categories. The first category of CAD systems is the register transfer level (RTL) Verilog code used to describe the architecture at a purely digital level. At this highest-level behavioral model, the circuit is designed and tested for digitally functional correctness, using virtual logic analyzers to debug and adjust the inputs and outputs of the block. The RTL models are also passed into a set of verification procedures during

development that use custom test benches and already proven legacy vectors to ensure the formal verification of the digital model.

The second level of design, commonly called the "front-end" design, is the translation of the digital RTL into a transistor-level description. The transistor-level model is coupled with the manufacturing models to create and simulate the circuit in an analog environment, producing accurate simulation estimates of timing, power, and area. The front-end is considered complete when the model has acceptable results based on a true floor plan and pessimistic Steiner routing parasitic calculations.

The final level of design, called the "back-end" design, is the fine-tuning and physical routing of the circuit. This level uses pre-routing, auto-routers, and routing editors to physically add and adjust the interconnection of the circuit in a model that may "tape-out" to the GDSII manufacturing mask standard. The circuit's final transistor model is coupled with the routing model and the circuit undergoes a series of fine-grain electrical tests, including electromagnetic simulations, IR calculations, local heating, noise, and a full chip-level analog timing simulation. A model that passes all of the back-end checks, as well as provides acceptable electrical power, timing, and area results, is ready for GDSII tape-out. Any errors or unacceptable results require design iterations at either the back-end, front-end, or RTL levels, depending on the errors and their severity.

This section includes descriptions of the RTL and front-end design methods used in this dissertation's fused multiplier-adders. The back-end design was not included in the implementations, as the intended results are only for architectural comparisons and not for immediate industrial tape-outs. A design in the back-end of the flow requires an enormous amount of resources, effort, and time to fine-tune the circuit and prepare it for manufacturing.

The decision to keep all designs in the front-end of the flow was made early in the project, concluding that the results produced by the back-end design, such as electromagnetic reports, local heating, timing results that are equal to or slightly better than the Steiner front-end estimations, and mask layers of the metal interconnects would provide little additional useful information for an academic architectural comparison. Additionally, the back-end design has more focus on connecting up various front-end blocks and fixing bad route netlists than evaluating architecture, so a line was drawn and the fused multiplier-adder designs concluded at a transistor-level with a floor plan and Steiner routing parasitics.

# 3.2.2 High-Level Design - Verilog RTL

The first step in the design of the fused multiply-add units was the translation of the block diagram to an RTL description via the Verilog2K high-level design language (HDL). Each design has been coded in Verilog2K RTL, compiled by Synposys Chronologic VCS compiler tools, and debugged using the Novas Debussy logic analysis software. Verification has been performed by a collection of test vectors and test benches which include comprehensive corner cases, as well as built-in Verilog behavioral checks within the RTL models themselves to ensure a more formal level of functional verification. A description, screenshots, and examples of each RTL toolset are described in the following sub-sections.

# 3.2.2.1 Verilog 2K HDL and the VCS Compiler

The Verilog 2K RTL HDL language is a syntax coding standard most recently updated in 2005 [33]. This language is written so that every line of code is executed simultaneously, simulating electrical components with multiple inputs and outputs that execute on multiple signals at the same time. The code may be written in any text-based editor compliant with the user's operating system, and must be compiled with a tool conforming to the Verilog 2K standard.

An example of the Verilog HDL syntax used for the fused multiply-add designs is provided in the RTL design of a Booth multiplexer. In this example, Verilog code is written using the UNIX-based XEMACS program to create the Booth multiplexer in a format that is accepted by the debugging and simulation software.

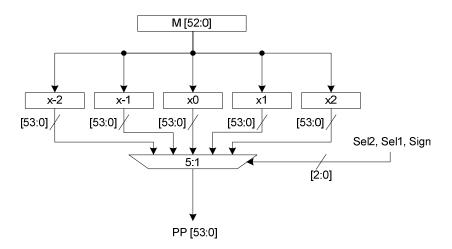

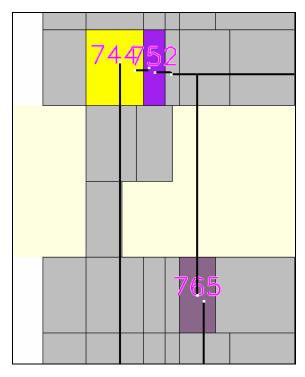

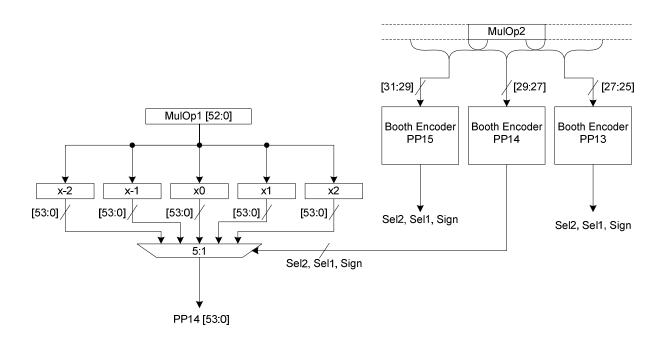

The Booth multiplexer seen in Figure 3.2.2.1 is a block used in a radix-4 multiplier tree that accepts inputs from both a Booth encoder block and an un-processed multiplier operand. The Booth encoder block outputs signals from the radix-4 Booth encoding of the other multiplier operand input that determine if the partial product bits created for a specific position in the multiplier tree require an inversion or shifting, i.e., if the operand is multiplied by {-2,-1,0,1,2}. The behavioral code of this architectural block is realized in the Verilog code seen in Figure 3.2.2.2.

Figure 3.2.2.1 Radix-4 Booth multiplexer

```

// (#1) Booth Mux

module fma_lib_boothmux

M,

Sel2.

Sel1,

Sign,

PP,

);

// Inputs

input Sel1;

input Sel2;

input Sign;

input [52:0] M;

// =====

// Outputs

// =====

output reg [53:0] PP;

// =======

// Booth Mux

// =======

reg [53:0]

PP_Shift;

always @* begin

PP\_Shift[53:0] = (\{54\{Sel1\}\} \& \{1'b0, M[52:0]\}) \mid (\{54\{Sel2\}\} \& \{M[52:0], 1'b0\});

PP[53:0] = PP_Shift[53:0] ^ {54{Sign}};

end

endmodule

```

Figure 3.2.2.2 Verilog code for a radix-4 Booth multiplexer

After a Verilog block like the Booth multiplexer is combined with all the blocks required for a design, the total model is not yet ready for compilation and simulation in a debug tool. A functional block or collection of blocks may be syntactically correct according to the Verilog standard, but without an input/output file that produces vectors as stimuli, a debugger will provide no useful information on the design.

Figure 3.2.2.3 shows the syntax of an input/output file that creates two test vectors for the FMA\_Classic collection of Verilog modules. The vectors are latched to virtual registers in an initialization statement, and time increments are described by numerical statements following a '#' sign (in this case, a 100ps increment from the initial state to the following state). After the test vectors are described, the file makes a call to the top level of the fused multiply-add model that connects vectors to the various inputs.

When a Verilog collection has been coded along with an input/output file for stimulus, the code needs to be compiled and ported to a format that can be read by a debugging tool. For the fused multiply-add designs, the Synposys Chronologic VCS compiler is used to collect all the Verilog files and combine them into a single object file database. If the code compiles without errors, the object code may be simulated and prepared for debugging.

To follow with the same example of the input/output file, a UNIX terminal output of the VCS compilation and simulation tools for the fused multiply-add Classic test is shown in Figure 3.2.2.4. The first command is the call to the VCS compiler, and the second './simv' command is the tool that passes the vectors through the Verilog models and dumps the outputs to a database for the debugger. If both tools complete successfully, the models may be viewed in the virtual logic analyzer.

```

initial begin

// Initial Design Tests

A = 64'h4030\_0000\_0000\_0000;

B = 64'h4030\_0000\_0000\_0000;

C = 64'h4060_0000_0000_0000;

fp_op = 1'b0;