Copyright

by

Woo Young Jang

2011

# The Dissertation Committee for Woo Young Jang Certifies that this is the approved version of the following dissertation:

# Architecture and Physical Design for Advanced Networks-on-Chip

| Committee:               |

|--------------------------|

| David Z. Pan, Supervisor |

|                          |

| Jacob A. Abraham         |

| Adnan Aziz               |

| Andreas Gerstlauer       |

| Yin Zhang                |

# Architecture and Physical Design for Advanced Networks-on-Chip

by

Woo Young Jang, B.E.; M.S.

## **Dissertation**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

## **DOCTOR OF PHILOSOPHY**

The University of Texas at Austin

May 2011

### Acknowledgements

First of all, I would like to express my deepest gratitude and appreciation to my advisor Prof. David Z. Pan for his invaluable advice, great generosity, and continuous encouragement throughout my research. I am extremely fortunate to study under his supervision. He has guided my research with remarkable insight and profound knowledge. Without his guidance and support, this dissertation would not have been completed.

I am also grateful to the members of my dissertation committee, Prof. Jacob A. Abraham, Prof. Adnan Aziz, Prof. Andreas Gerstlauer, and Prof. Yin Zhang. Their helpful advices on my research and their knowledge have guided me in my quest to do quality work.

I am indebted to many people in Samsung for their support and concern for me. In particular, I would like to thank Dr. Sun-Jae Cho, Mr. Byung-Hoan Chon, Dr. Seh-Woong Jeong, Dr. Jinhyun Kim, Dr. Donghoon Lee, and Mr. Youngbum Lee. Without their support and help, I could not have the great chance to study for a Ph.D. degree with the complete support of Samsung.

I would like to thank the colleagues at UTDA for their help and cheering up: James Ban, Ashutosh Chakraborty, Minsik Cho, Duo Ding, Jerrica Gao, Ou He, Kiwoon Kim, Anurag Kumar, Yen-Hung Lin, Katrina Lu, Joydeep Mitra, Jiwoo Pak, Sean Shi, Jae-Seok Yang, Bei Yu, Kun Yuan, Rein Zhang, and Yilin Zhang.

I sincerely appreciate the support and love from my father and mother who always encourage me to pursue my goal. I also thank my parents-in-law who always cheer me up and my daughter, Hannah who always makes me smile. Finally, I would like to express my sincerest and deepest gratitude and love to my wife, Minkyung, who

always supports and encourages me with great love. I will pay my debt back to her throughout my life.

Woo Young Jang

The University of Texas at Austin May 2011 Architecture and Physical Design for Advanced Networks-on-Chip

Publication No.\_\_\_\_

Woo Young Jang, Ph.D.

The University of Texas at Austin, 2011

Supervisor: David Z. Pan

The aggressive scaling of the semiconductor technology following the Moore's Law has delivered true system-on-chip (SoC) integration. Network-on-chip (NoC) has been recently introduced as an effective solution for scalable on-chip communication since dedicated point-to-point (P2P) interconnection and shared bus architecture become performance and power bottlenecks in the SoCs. This dissertation studies three critical

NoC challenges such as latency, power, and compatibility with emerging technologies in

aspect of an architecture and physical design level.

Latency is a key issue in NoC since the performance of applications considerably depends on resource sharing policies employed in an on-chip network. NoCs have been

mainly developed to improve network-level performance that captures the inherent

performance characteristics of a network itself, but the network-level optimizations are

not directly related to application- or system-level performance. In addition, memory

latency on NoC critically affects the performance of applications or systems. We propose

a synchronous dynamic random access memory (SDRAM) aware NoC design to

vii

optimize memory throughput, latency, and design complexity. Furthermore, it is extended to an application-aware NoC design to provide the quality-of-service (QoS) of memory for various applications.

NoC provides great on-chip communication. However, it brings no true relief to power budget when the on-chip network scales in terms of complexity/size and signal bandwidth. The combination of NoC and other techniques has the potential to reduce power. We study two power saving research topics for NoC: (a) we propose a voltage-frequency island (VFI) aware NoC optimization framework with a better tradeoff between power efficiency and design complexity to minimize both computation and on-chip communication power. (b) We formulate an application mapping problem to mixed integer quadratic programming (MIQP) with the purpose of reducing power consumption in various hard networks and develop highly efficient algorithms for the MIQP.

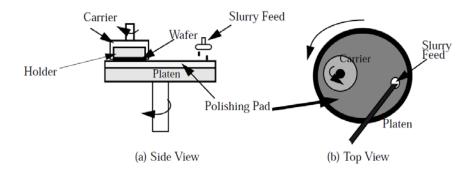

Regarding NoC compatible with new technologies, we focus on three dimensional (3D) die integration based on through-silicon vias (TSVs). Since an on-chip network design has been subject to not only application constraints but also design/manufacturing constraints, a 3D NoC design is required for innovation in interconnection networks. We propose a chemical-mechanical polishing (CMP) aware application-specific 3D NoC design that minimizes TSV height variation, thus reduces bonding failure, and meanwhile optimizes conventional NoC design objectives such as hop count, wirelength, power, and area.

# **Table of Contents**

| List of Ta  | ıbles           |                                                                          | xiii |

|-------------|-----------------|--------------------------------------------------------------------------|------|

| List of Fig | gures           |                                                                          | xv   |

| Chapter 1   | : Introduction. |                                                                          | 1    |

| 1.1         | Network-on-     | Chip Challenges in Ultra-Deep Submicron Era                              | 1    |

| 1.2         | Overview and    | d Contributions of This Dissertation                                     | 5    |

| -           | •               | are NoC Design for Improving Application-Level                           | 8    |

| 2.1         | SDRAM-Aw        | are NoC Design                                                           | 9    |

|             | 2.1.1 Basic S   | DRAM Operation                                                           | 12   |

|             | 2.1.2 SDRAN     | A Scheduling                                                             | 14   |

|             | 2.1.2.1         | Bank Conflict                                                            | 14   |

|             | 2.1.2.2         | Data Contention                                                          | 15   |

|             | 2.1.2.3         | Short Turn-Around Bank Interleaving                                      | 20   |

|             | 2.1.3 NoC De    | esign with SDRAM                                                         | 23   |

|             | 2.1.3.1         | Problem Description                                                      | 23   |

|             | 2.1.3.2         | Basic Idea of Our Approach                                               | 24   |

|             | 2.1.4 SDRAN     | /I-Aware Router                                                          | 26   |

|             | 2.1.4.1         | Router Description                                                       | 27   |

|             |                 | SDRAM-Aware Flow Control for Avoiding Bank onflict and Data Contention   | 30   |

|             | 2.1.4.3<br>Tu   | SDRAM-Aware Flow Control for Avoiding Short arn-Around Bank Interleaving | 36   |

|             | 2.1.4.4         | Hardware Complexity                                                      | 39   |

|             | 2.1.5 Experin   | nental Results                                                           | 40   |

|             | 2.1.5.1         | Digital Television Application                                           | 41   |

|             | 2.1.5.2         | Synthetic Benchmarks                                                     | 44   |

|             | 2.1.5.3         | Comparison of SP and SP+AP                                               | 46   |

|             | 2.1.6 Summa     | ry                                                                       | 46   |

| 2.2        | Application-A | Aware NoC Design                        | 48  |

|------------|---------------|-----------------------------------------|-----|

|            | 2.2.1 Problem | Description and Our Basic Idea          | 51  |

|            | 2.2.1.1       | Priority SDRAM Service in NoC           | 51  |

|            | 2.2.1.2       | SDRAM Access Granularity Mismatch       | 54  |

|            | 2.2.2 Applica | tion-Aware NoC Design                   | 56  |

|            | 2.2.2.1       | Architecture of GSS Router              | 56  |

|            | 2.2.2.2       | GSS Flow Control Algorithm              | 59  |

|            | 2.2.2.3 1     | NoC Design for SAGM                     | 63  |

|            | 2.2.3 Experim | nental Results                          | 68  |

|            | 2.2.3.1       | No Priority Memory Request              | 68  |

|            | 2.2.3.2       | Priority Memory Request                 | 72  |

|            | 2.2.4 Summar  | ry                                      | 79  |

| Chapter 3: | Power Optimi  | zation for Advanced NoC                 | 80  |

| 3.1        | VFI-Aware E   | nergy Optimization Framework for NoC    | 81  |

|            | 3.1.1 Motivat | ion and Contributions                   | 84  |

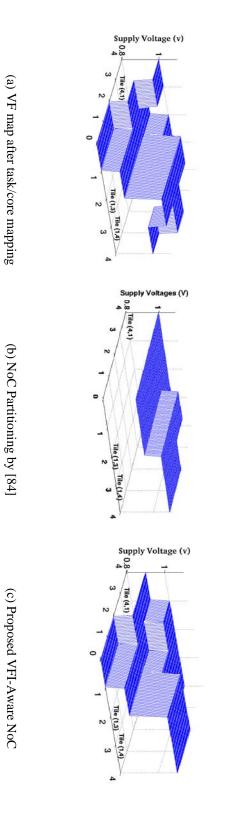

|            | 3.1.1.1       | Motivational Example                    | 84  |

|            | 3.1.1.2       | Major Novelty                           | 86  |

|            | 3.1.2 Problem | n Formulations                          | 87  |

|            | 3.1.2.1       | Partitioning with VF Assignment Problem | 87  |

|            | 3.1.2.2       | VFI-Aware Mapping Problem               | 88  |

|            | 3.1.2.3       | VFI-Aware Routing Problem               | 89  |

|            | 3.1.3 VFI Opt | timization Framework                    | 90  |

|            | 3.1.3.1       | Core Partitioning with VF Assignment    | 91  |

|            | 3.1.3.2       | VFI-Aware Mapping Algorithm             | 93  |

|            | 3.1.3.3       | VFI-Aware Routing Path Allocation       | 96  |

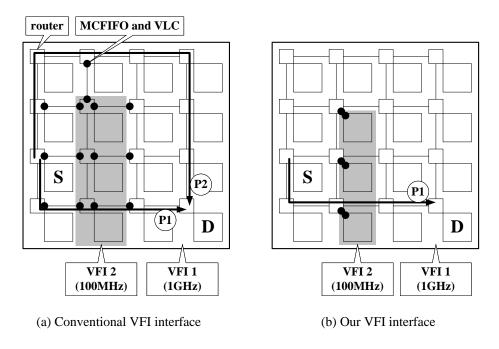

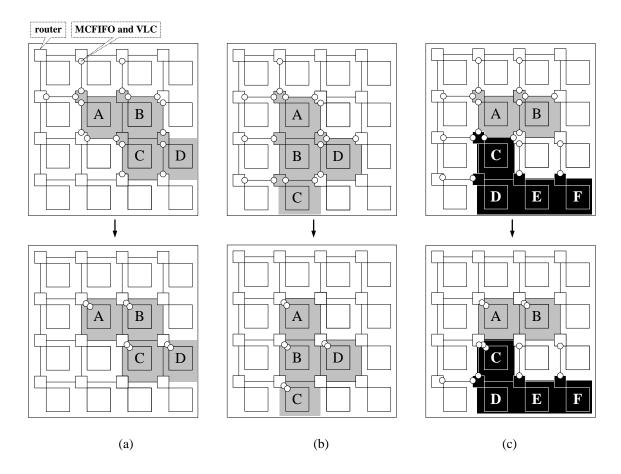

|            | 3.1.3.4       | VFI-Aware Interface Planning            | 102 |

|            | 3.1.4 Experim | nental Results                          | 108 |

|            | 3.1.5 Summar  | ry                                      | 113 |

| 3.2        | Architecture- | Aware Analytic Application Mapping      | 114 |

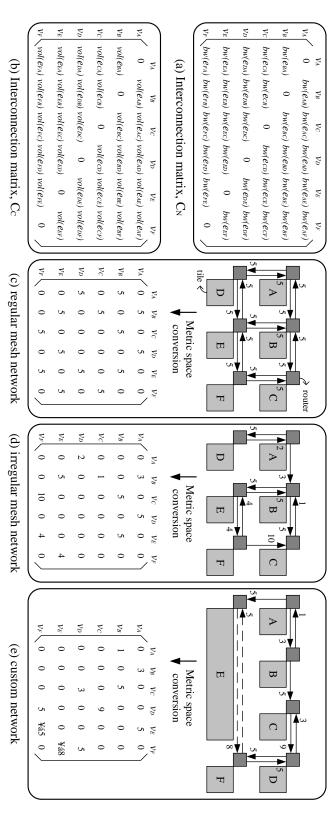

|            | 3.2.1 Problem | n Formulation                           | 117 |

|            | 3.2.2 | A3MAF    | P Algorithms                                                           | 123     |

|------------|-------|----------|------------------------------------------------------------------------|---------|

|            |       | 3.2.2.1  | A3MAP-SR                                                               | 123     |

|            |       | 3.2.2.2  | A3MAP-GA                                                               | 126     |

|            | 3.2.3 | A3MAF    | of for Large-Scale NoC                                                 | 129     |

|            | 3.2.4 | Experim  | nental Results                                                         | 132     |

|            |       | 3.2.4.1  | Regular Mesh Network                                                   | 132     |

|            |       | 3.2.4.2  | Irregular Mesh Network                                                 | 135     |

|            |       | 3.2.4.3  | Custom Network                                                         | 137     |

|            |       | 3.2.4.4  | Large-Scale NoC                                                        | 139     |

|            | 3.2.5 | Summar   | ry                                                                     | 144     |

| Chapter 4: | NoC   | Architec | ture and Physical Design for Emerging Technologi                       | les.146 |

| 4.1        | CMF   | P-Aware  | Application-Specific 3D NoC Design                                     | 146     |

|            | 4.1.1 | Prelimir | naries                                                                 | 149     |

|            |       |          | Chemical-Mechanical Polishing and Cu-Cu Thernompression Direct Bonding |         |

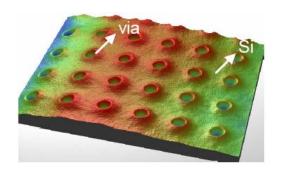

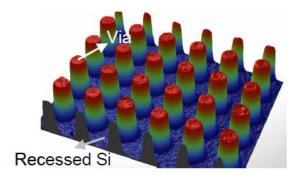

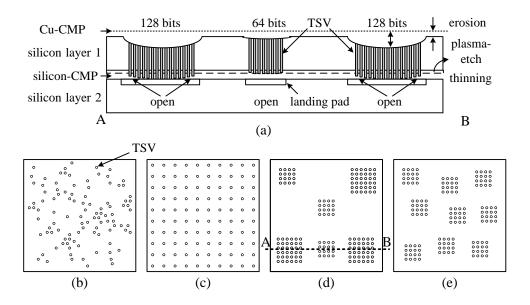

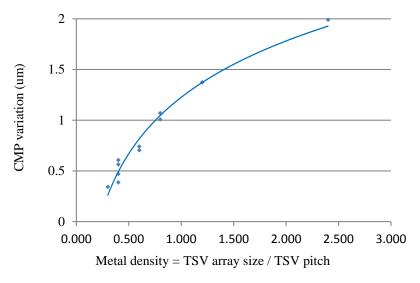

|            |       | 4.1.1.2  | TSV Layouts and CMP Variation                                          | 151     |

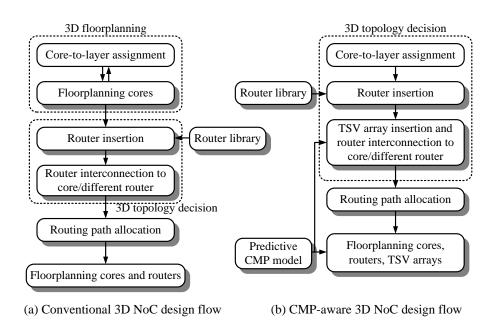

|            | 4.1.2 | CMP-A    | ware NoC Design Flow and Problem Formulation.                          | 155     |

|            |       | 4.1.2.1  | Core-to-Layer Assignment                                               | 157     |

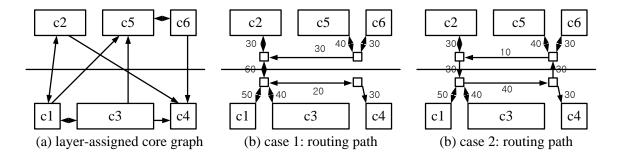

|            |       |          | 3D NoC Topology Decision and Routing Path location                     | 158     |

|            |       | 4.1.2.3  | Floorplanning                                                          | 159     |

|            | 4.1.3 | CMP-A    | ware 3D NoC Design                                                     | 160     |

|            |       | 4.1.3.1  | CMP-Aware Core-to-Layer Assignment                                     | 160     |

|            |       | 4.1.3.2  | CMP-Aware 3D NoC Topology Decision                                     | 162     |

|            |       | 4.1.3.3  | CMP-Aware Floorplanning                                                | 166     |

|            | 4.1.4 | Experim  | nental Results                                                         | 167     |

|            |       | 4.1.4.1  | TSV Density and Predictive CMP Model                                   | 167     |

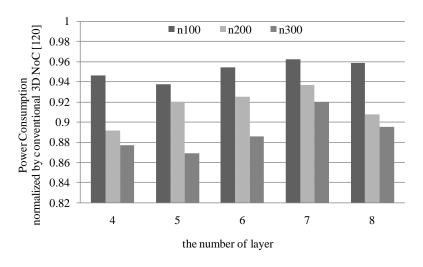

|            |       | 4.1.4.2  | CMP-Aware Application-Specific 3D NoC                                  | 168     |

|            | 4.1.5 | Summar   | ry                                                                     | 172     |

|            |       |          |                                                                        |         |

| Chapter 5: Conclusions | 175 |

|------------------------|-----|

| Bibliography           | 178 |

| Vita                   | 187 |

# **List of Tables**

| Table 2.1:  | Timing parameter of DDR I, II, and III SDRAM                 | .16 |

|-------------|--------------------------------------------------------------|-----|

| Table 2.2:  | SDRAM data input/output delay between $h(n)$ and $h_i(n+1)$  | .32 |

| Table 2.3:  | Memory utilization and latency comparison in DTV application |     |

|             | according to various DDR SDRAMs                              | .45 |

| Table 2.4:  | Memory utilization and latency comparison in synthetic       |     |

|             | benchmarks according to network size.                        | .45 |

| Table 2.5:  | Memory utilization and latency comparison of SP and SP+AP in |     |

|             | DDR I/II/III SDRAM                                           | .47 |

| Table 2.6:  | Memory performance comparison on industrial benchmarks       |     |

|             | without priority memory requests.                            | .71 |

| Table 2.7:  | Memory performance comparison on industrial benchmarks with  |     |

|             | priority memory requests.                                    | .73 |

| Table 2.8:  | The memory performance comparison of GSS+SAGM+STI and        |     |

|             | GSS+SAGM on industrial benchmarks.                           | .77 |

| Table 2.9:  | The comparison of gate count synthesized at 400MHz clock     |     |

|             | speed.                                                       | .77 |

| Table 2.10: | The comparison of power consumption ruing at 400MHz clock    |     |

|             | speed.                                                       | .78 |

| Table 3.1:  | The comparison of VFI overhead, hop count, and communication |     |

|             | congestion on VOPD benchmark                                 | 109 |

| Table 3.2:  | The comparison of VFI overhead and hop count on E3S          |     |

|             | benchmark                                                    | 111 |

| Table 3.3: | The comparison of energy consumption according to the number   |     |

|------------|----------------------------------------------------------------|-----|

|            | of VFI on E3S benchmarks                                       | 113 |

| Table 3.4: | The hop count increase and runtime improvement of NMAP,        |     |

|            | A3MAP-GA, and A3MAP-SR normalized by A3MAP-FS                  | 133 |

| Table 3.5: | The comparison of hop count for industrial benchmarks in regul | ar  |

|            | mesh networks.                                                 | 134 |

| Table 3.6: | The comparison of hop count for VOPD benchmark in various      |     |

|            | irregular mesh networks                                        | 137 |

| Table 3.7: | The comparison of hop count and wirelength for VOPD            |     |

|            | benchmark in custom networks.                                  | 139 |

| Table 4.1: | TSV height variation comparison (μm).                          | 169 |

| Table 4.2: | Hop count comparison.                                          | 170 |

| Table 4.3: | Total wirelength comparison (mm).                              | 170 |

# **List of Figures**

| Figure 1.1: | NoC architecture                                                   |

|-------------|--------------------------------------------------------------------|

| Figure 2.1: | SDRAM architecture and activation, read/write, and deactivation    |

|             | operations                                                         |

| Figure 2.2: | Examples showing bank conflict and interleaving in DDR II          |

|             | SDRAM @333MHz17                                                    |

| Figure 2.3: | Examples showing data contention in DDR II SDRAM                   |

|             | @266MHz19                                                          |

| Figure 2.4: | Examples showing short turn-around bank interleaving in DDR III    |

|             | SDRAM @800MHz21                                                    |

| Figure 2.5: | Bank conflict in 2×3 NoC with conventional round-robin flows       |

|             | controller although an effective memory subsystem23                |

| Figure 2.6: | No bank conflict in 2×3 NoC with SDRAM-aware flow controller       |

|             | although a simple memory subsystem                                 |

| Figure 2.7: | The architecture of an SDRAM-aware router consisting of input      |

|             | buffers, routing logics, flow controllers, and output schedulers   |

|             | for a mesh network                                                 |

| Figure 2.8: | The architecture of an SDRAM-aware flow controller combined        |

|             | with a conventional flow controller for a mesh network29           |

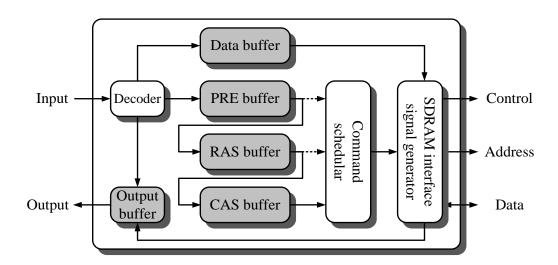

| Figure 2.9: | The architecture of an SDRAM interface signal generator with a     |

|             | deactivation buffer, an activation buffer, and a read/write buffer |

|             | which packets pass through                                         |

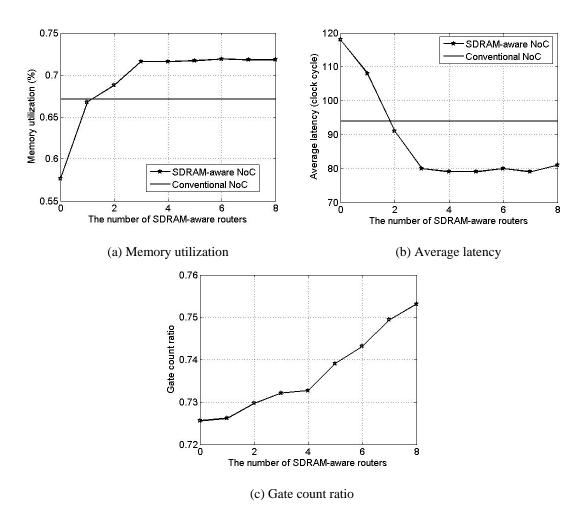

| Figure 2.10: | The comparisons of memory utilization, latency, and design           |   |

|--------------|----------------------------------------------------------------------|---|

|              | complexity in DTV application according to the number of             |   |

|              | SDRAM-aware routers, where our NoC design achieves the best          |   |

|              | tradeoff between performance and cost when three conventional        |   |

|              | routers are replaced to SDRAM-aware routers4                         | 2 |

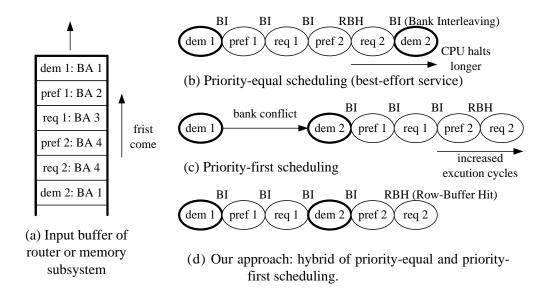

| Figure 2.11: | Examples of scheduling memory requests, where priority-equal         |   |

|              | and priority-first schedulers show long latency for priority packets |   |

|              | and low memory utilization, respectively5                            | 3 |

| Figure 2.12: | Example of memory access granularity mismatch in DDR II              |   |

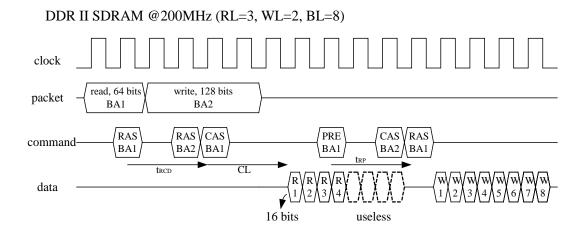

|              | SDRAM @200, where four bursts read are thrown away5                  | 5 |

| Figure 2.13: | The architecture of an NoC router and a GSS flow controller          |   |

|              | for a 2D mesh network5                                               | 7 |

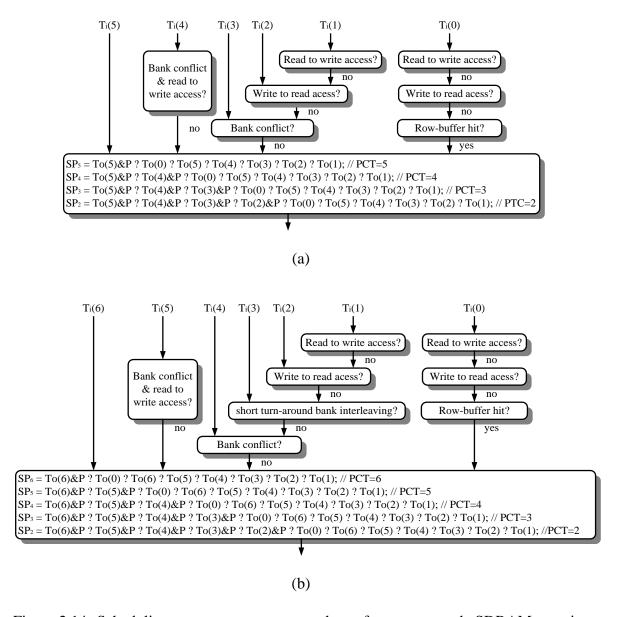

| Figure 2.14: | Scheduling memory request packets for guaranteed SDRAM               |   |

|              | service considering (a) bank conflict and data contention, and       |   |

|              | (b) bank conflict, data contention and short turn-around bank        |   |

|              | interleaving6                                                        | 2 |

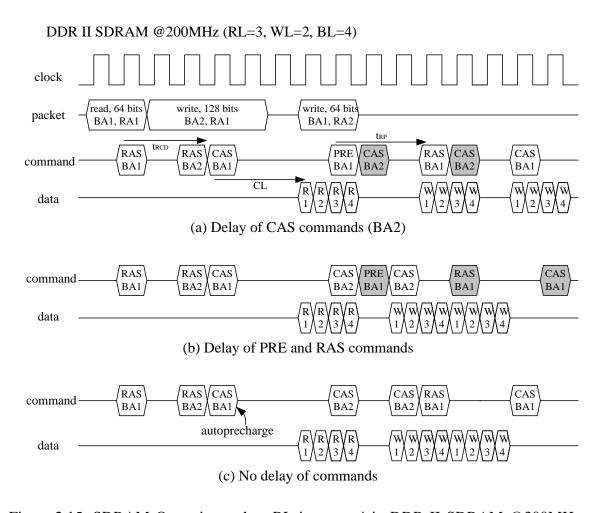

| Figure 2.15: | SDRAM Operations when BL is set to 4 in DDR II SDRAM                 |   |

|              | @300MHz, where the read command with authorrecharge does             |   |

|              | not need any precharge command6                                      | 5 |

| Figure 2.16: | The architecture of our memory controller where small PRE and        |   |

|              | RAS buffers are required thanks to authorrecharge operations6        | 7 |

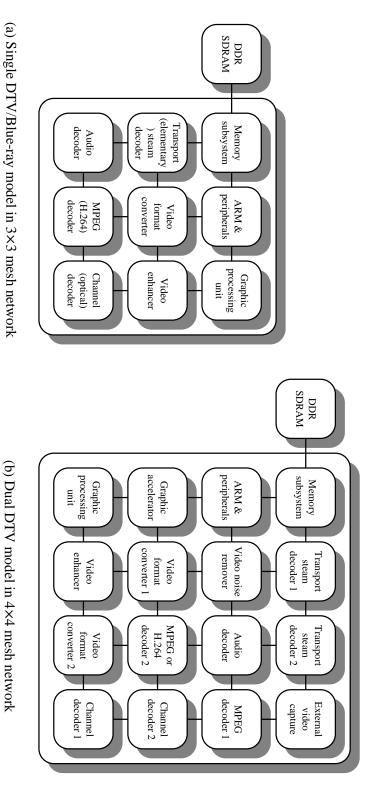

| Figure 2.17: | Single DTV/blue-ray and dual DTV application mapping results         |   |

|              | by A3MAP in 3x3 and 4x4 mesh networks7                               | 0 |

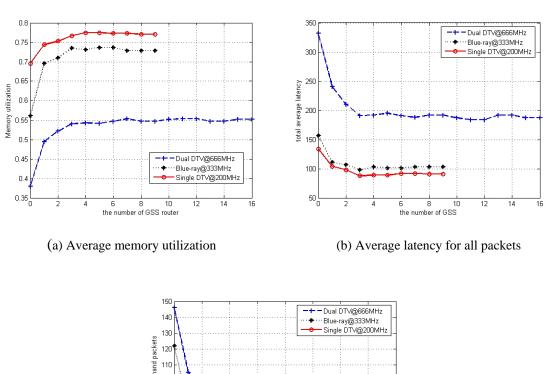

| Figure 2.18: | The memory performance of our application-aware NoC design         |

|--------------|--------------------------------------------------------------------|

|              | according to the number of GSS routers, where our NoC design       |

|              | achieves the best tradeoff between performance and cost when       |

|              | three conventional routers are replaced to GSS routers74           |

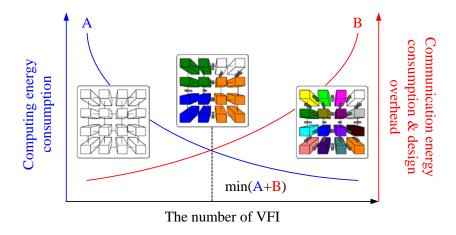

| Figure 3.1:  | Computing and communication energy consumption and design          |

|              | overhead according to the number of VFIs. The goal of VFI based    |

|              | NoC designs is to minimize the sum of the computing and            |

|              | communication energy and the design overhead84                     |

| Figure 3.2:  | Motivational VFI based NoC designs86                               |

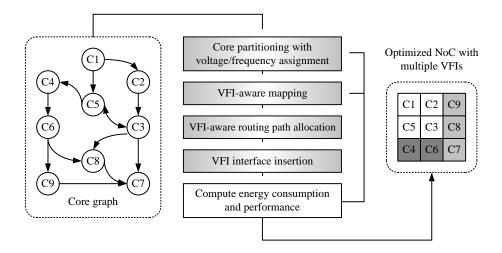

| Figure 3.3:  | The proposed VFI-aware NoC methodology where VFI                   |

|              | partitioning is first performed91                                  |

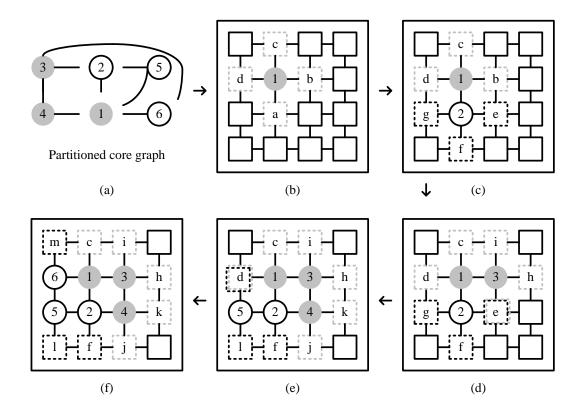

| Figure 3.4:  | Incremental core mapping on NoC96                                  |

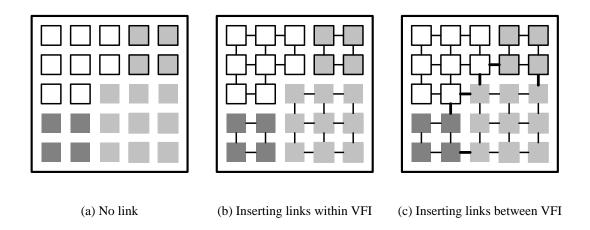

| Figure 3.5:  | Link insertion within VFI and between VFIs, where all links        |

|              | between VFIs are not inserted                                      |

| Figure 3.6:  | Finding the best interconnection between VFIs100                   |

| Figure 3.7:  | The proposed rules for allocating routing path in VFI-based        |

|              | NoC                                                                |

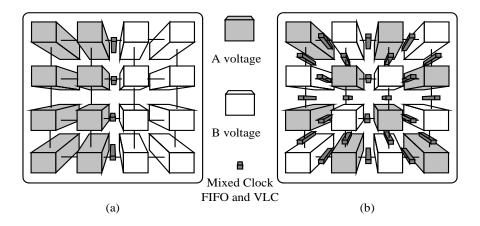

| Figure 3.8:  | NoC tiles with MCFIFO or VLC placed (a) between routers and        |

|              | (b) a core and a router. 103                                       |

| Figure 3.9:  | NoC designs with (a) the conventional VFI interface and (b) the    |

|              | proposed VFI interface                                             |

| Figure 3.10: | Examples of the proposed VFI interface insertion                   |

| Figure 3.11: | Visual comparison of VFI based NoC designs on 4x4 NoC111           |

| Figure 3.12: | Various graphs and their interconnection matrices119               |

| Figure 3.13: | Guiding continuous $P(i,j)$ to binary $P(i,j)$ after solving QP125 |

| Figure 3.14: | Cycle crossover                                                            | 128 |

|--------------|----------------------------------------------------------------------------|-----|

| Figure 3.15: | Partition-based A3MAP flow for large networks and complex                  |     |

|              | applications.                                                              | 130 |

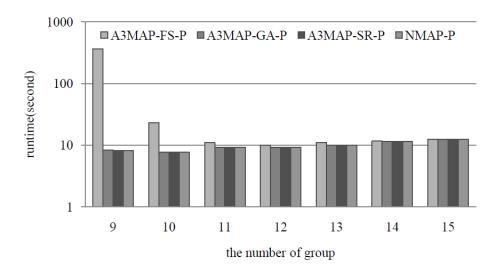

| Figure 3.16: | The comparison of runtime for industrial benchmarks in $3\times3-5\times5$ | i   |

|              | regular mesh networks.                                                     | 134 |

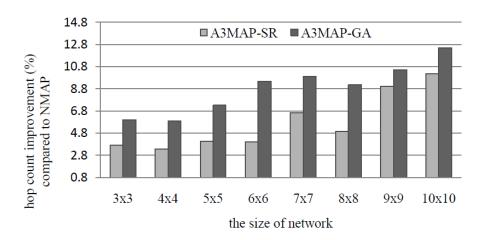

| Figure 3.17: | The hop count improvement of A3MAP algorithms compared to                  |     |

|              | NMAP for synthetic benchmarks in 3×3-10×10 regular mesh                    |     |

|              | networks                                                                   | 135 |

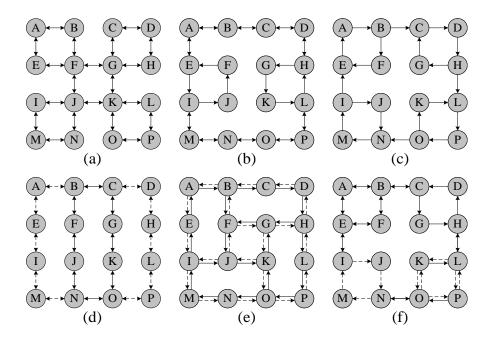

| Figure 3.18: | Irregular mesh networks used in our experiments.                           | 136 |

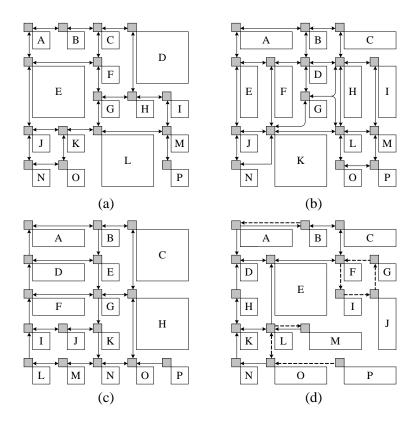

| Figure 3.19: | Custom NoC networks used in our experiments                                | 138 |

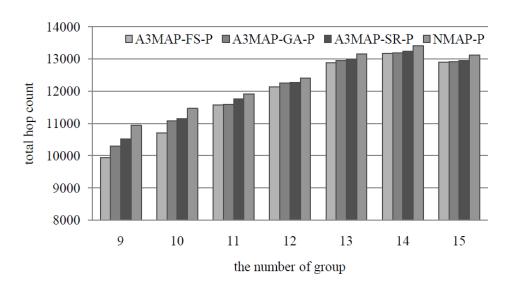

| Figure 3.20: | The hop count comparison of application mapping algorithms in              |     |

|              | large networks partitioned to 9-15 subnetworks                             | 140 |

| Figure 3.21: | The runtime comparison of application mapping algorithms in                |     |

|              | large networks partitioned to 9-15 subnetworks                             | 141 |

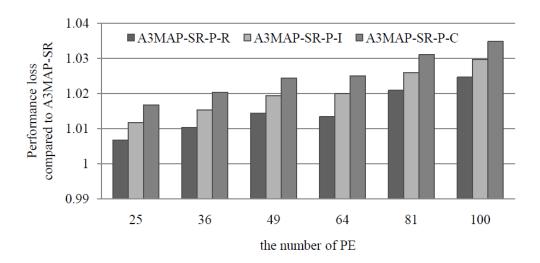

| Figure 3.22: | The hop count of A3MAP-SR-P normalized by A3MAP-SR on                      |     |

|              | regular mesh, irregular mesh, and custom networks with 25-100              |     |

|              | PEs.                                                                       | 142 |

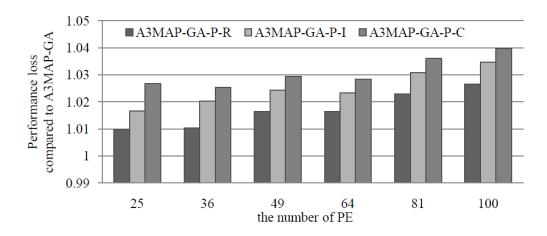

| Figure 3.23: | The hop count of A3MAP-GA-P normalized by A3MAP-GA on                      |     |

|              | regular mesh, irregular mesh, and custom networks with 25-100              |     |

|              | PEs.                                                                       | 143 |

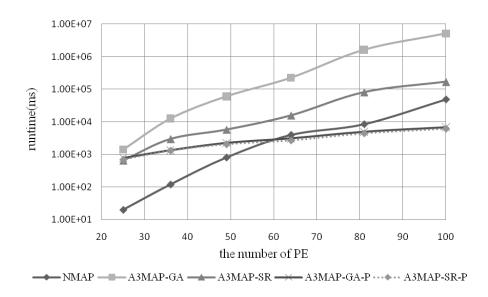

| Figure 3.24: | The runtime comparison of NMAP, A3MAP-GA, A3MAP-SR,                        |     |

|              | A3MAP-GA-P, and A3MAP-SR-P.                                                | 144 |

| Figure 4.1:  | Typical rotary CMP tool                                                    | 150 |

| Figure 4.2:  | Local topography on backside of wafer                                      | 151 |

| Figure 4.2:  | Local topography on backside of water                                      | 151 |

| Figure 4.3:  | TSV layouts and their TSV height variation induced by CMP      |      |

|--------------|----------------------------------------------------------------|------|

|              | process                                                        | .152 |

| Figure 4.4:  | The conventional and proposed 3D NoC design flows              | .156 |

| Figure 4.5:  | Examples of assigning eight cores to four layers               | .160 |

| Figure 4.6:  | CMP-aware router-to-router interconnections in adjacent layers | .166 |

| Figure 4.7:  | TSV height variation by TSV density                            | .168 |

| Figure 4.8:  | Network topologies and layouts performed by CMP-aware 3D       |      |

|              | NoC                                                            | .171 |

| Figure 4.9:  | Typical application-specific 3D NoC with 2 layers              | .173 |

| Figure 4.10: | CMP-aware application-specific 3D NoC with 2 layers            | .173 |

| Figure 4.11: | Improvement according to the area of routers                   | .174 |

### Chapter 1

#### Introduction

#### 1.1 NETWORK-ON-CHIP CHALLENGES IN ULTRA-DEEP SUBMICRON ERA

The aggressive scaling of the semiconductor technology has enabled billions of transistors to be integrated to a single chip, following Moore's Law that the minimum feature size is scaled down at the rate of a factor 0.7 reduction every three years. The technology scaling trend has continued for more than half a century and it is expected to last until 2015 or later, according to the International Technology Roadmap for Semiconductors [48]. The effective reduction in size and cost provides higher chip performance in a smaller silicon area and thus enables the realization of scenarios deemed to belong to the domain of science fictions.

The continued feature size scaling has delivered the potential of true and complete system-on-chip (SoC) integration. However, as most SoC designs target the high-performance system level integration of existing heterogeneous cores with low power consumption, previous dedicated point-to-point (P2P) interconnections and shared bus architectures become performance bottlenecks due to the increasing communication between the cores. Furthermore, with the rapid technology scaling, the global interconnection causes critical delays and high energy consumption. To mitigate such issues, network-on-chip (NoC) has been recently introduced as an effective solution for the scalable on-chip communication [4][18]. As the better SoC platform for system integration, NoC makes interconnect structure and wiring complexity manageable easily such that the issues in a physical design such as floorplanning, placement, and routing can be well optimized. It leads to faster time-to-market by reduction in the number of

design re-spins. Therefore, the NoC has attracted great attentions for the current and future SoC designs.

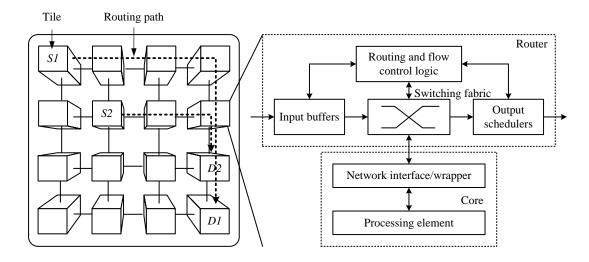

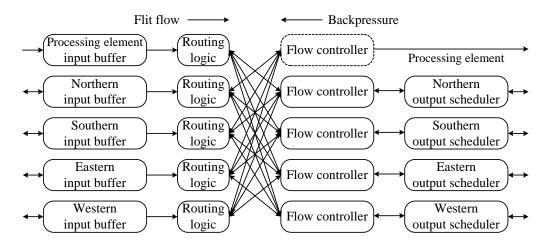

Figure 1.1 illustrates general NoC architecture. Each processing element (PE) is attached to its own router via a network interface logic or a wrapper and the router is interconnected to different routers. When any PE receivers or transfers data to different PE, the requests and data are encoded or wrapped to a packet in the network interface logic or the wrapper and then the packet is delivered to its own router. The packet is stored at an input buffer and a routing logic in the router selects the path of the packet on a given network topology. If more than two packets arriving on different input buffers at the same time desire the same output channel, a flow-control mechanism resolves this contention. An output scheduler either detects if the input buffer of the next router is available or expects when the input buffer is available. After performing such operations, the packets are delivered to the next router on its path. This process is repeated until the packet arrives at its final destination.

Figure 1.1: NoC architecture.

For the last decade, there have been many NoC researches to achieve greater design productivity and higher performance by handling increasing parallelism, manufacturing complexity, wiring problems, and reliability, where critical challenges for NoC include latency, power, and compatibility with new technologies [88]. Unfortunately, a number of researches gave an impression that NoC greatly improved SoC designs where it was utilized, but failed to show that NoC reduces latency and power consumption, compared to shared bus interconnects. In addition, as emerging technologies have become feasible, new constraints and design flows are required for innovation in NoC.

Latency is crucial to the success of NoC since an on-chip network with long latency can considerably deteriorate the overall application performance although its high throughput. NoCs have been mainly developed to improve network-level performance such as throughput or average network latency [5][21][31][59][63][76][83][89][94]. It captures the inherent performance characteristics of a network itself, but is not directly related to application-level or system-level performance. This is because each application demands different network performance and much of the system performance depends on not only on-chip networks but also shared memories, in particular, synchronous dynamic random access memories (SDRAMs). The application- and SDRAM-oblivious NoCs lead to reduced overall system performance. Therefore, latency in NoC is required to approach the characteristics of shared bus interconnects with the consideration of various applications and memories.

Power should be budgeted and traded off among different NoC optimization factors since it has also become a major issue. NoC itself is not efficient for power and even may consume higher power than shard bus interconnects due to additional power consumers such as router and network interface logics. However, the combination of

NoC and other techniques efficient for power has the potential to easily reduce power to allowable levels. A voltage-frequency island (VFI) paradigm is one of the desirable solutions for reducing power consumption in NoC since it is inefficient for all cores and links on NoC to operate at a single voltage level and clock speed [10][41][62][66][84] [118][119]. VFI enables fine-grained core-level power optimization by utilizing a unique voltage and clock for each island. The use of multiple voltages and clocks in NoC provides better performance-power tradeoffs than that of a single voltage and clock. In addition, application mapping which decides how to topologically place the selected set of cores onto the tiles of a network can greatly reduce both application latency and power consumption. NoC designers or programmers favor regular mesh architecture consisting of regular rectangle tiles on which homogeneous processors are placed since the regular mesh architecture makes the application mapping manageable [13][15][39][79][103]. On the contrary, most industrial SoC platforms consist of heterogeneous cores with different design areas, and thus they can be structured with an irregular mesh network or even a custom network. Therefore, since previous works have mainly optimized their application mapping on the regular mesh architecture, the application mapping algorithm is required to reduce application latency and power consumption in various networks.

The architecture and physical design for an on-chip network design should be compatible with emerging technologies since it has been always subject to technology constraints. With shrinking transistor and wire dimensions, variability and reliability have become important for NoC designs. In addition, as three dimensional (3D) die integration using through-silicon vias (TSVs) becomes viable, 3D NoC becomes new opportunities and challenges [80][102][120]. Since 3D NoC must satisfy not only application constraints such as latency, throughput, and power, but also manufacturing/design constraints imposed by 3D technologies such as the number of TSVs, chemical-

mechanical polishing (CMP), TSV stress, and temperature, 3D NoC design shall consider such constraints for interconnection networks.

Therefore, it is indispensable to propose novel architecture and physical designs for advanced NoCs in ultra-deep submicron era, which can address all these challenges in an effective and efficient manner. First, we need to improve system-level or application-level performance with consideration of various application demands and memories. Next, we propose a VFI based NoC design and an application mapping algorithm to reduce power consumption. Finally, we propose a 3D NoC design with consideration of both application constraints and manufacture/design constraints imposed by the 3D technology.

#### 1.2 OVERVIEW AND CONTRIBUTIONS OF THIS DISSERTATION

The architectures and physical design techniques for advanced NoC, presented in this dissertation target the above mentioned challenges and are described in the next three chapters. The overall flow of the dissertation is as follows.

Chapter 2 presents SDRAM- and application-aware NoC designs to improve not only network-level performance but also application-level or system-level performance. The performance of various applications considerably depends on the resource sharing policies employed in an on-chip network. In particular, memory service for the applications becomes one of the most important issues since its performance becomes the bottleneck of the overall system. Unfortunately, its improvement aided by a memory subsystem is severely limited since diverse applications generate their specific memory requests with different latency constraints and data sizes. With consideration of different

demands of applications, our on-chip network shares the responsibility for the memory performance with the memory subsystem.

In Chapter 3, we propose a VFI based design flow and application mapping algorithms for a low power NoC design. The NoC design style fits nicely with the concept of VFI. There have been several design efforts to combine VFI based design style with the NoC interconnect mechanism. However, previous works are limited since VFI-awareness is partially applied in a NoC design. In Section 3.1, a systematic VFI-aware energy optimization framework that considers partitioning, mapping, and routing together is presented to improve the power efficiency of VFI-based NoC designs. In Section 3.2, we propose architecture-aware analytic application mapping (A3MAP) algorithms that are analogous to analytical communication minimization in a given NoC. The proposed A3MAP algorithms adaptively map cores to any different sized tiles on regular/irregular meshes and custom networks for the minimum power consumption under performance constraints.

In Chapter 4, we propose a CMP process-aware application-specific 3D NoC design that minimizes TSV height variation, thus reduces bonding failure, and meanwhile optimizes conventional NoC design objectives, such as hop count, wirelength, power, and area. Previous NoC design flows are not effective in 3D integration since they do not consider manufacturing/design constraints by TSVs. The key idea behind our 3D NoC design flow is to determine the CMP-aware network topology where different layers are interconnected by one-way links with the minimum hops and thus TSV height variation is minimized. This is the first work that addresses the 3D NoC design which considers architecture, physical design and manufacturing issues together.

Chapter 5 concludes this dissertation with summaries based on the results of the previous chapters as well as presents promising future research directions to further investigate architecture and physical design for advanced NoC.

### Chapter 2

## Memory-Aware NoC Design for Improving Application-Level Latency

Memory bandwidth and latency to feed a number of cores have become a key issue in the modern and future SoC design. SDRAM is commonly used as a shared memory since it provides high memory capacity and infinite endurance for modern computing systems. However, since the SoCs mainly interface with a single or dual SDRAM, there would be insufficient memory bandwidth to keep up with a number of high speed cores. For example, Intel Teraflop which is the state-of-the-art NoC and composed of 80 cores is supported by a dual shared memory [112]. If cores will have access to the single or dual memory at the same time, memory latency will be too long to provide real-time computing. As an effective solution of memory bandwidth and latency, 3D NoC based on TSV technology [78] is gaining momentum and industry adoption. 3D NoC can be embedded with a lot of SDRAMs on top of processing elements at different layers [67]. It achieves higher system performance and more reliable electrical features. Furthermore, it provides low power consumption, low electromagnetic interference (EMI), small die and printed circuit board (PCB) area and low pin density.

Most NoCs with a number of cores require a dedicated memory subsystem to control SDRAMs. The memory subsystem that schedules SDRAM requests and generates SDRAM interface signals is one of the most important components in SoCs since the performance of the entire system depends on its performance. However, the conventional memory subsystem still underperforms due to special operation flows of SDRAM [24]. For example, double data rate (DDR) II SDRAM utilization gets deteriorated up to 55% in a digital television (DTV) application [113], where memory utilization is defined as the number of clock cycles used for data transfer divided by the

number of total clock cycles. In addition, since on-chip networks are oblivious of applications and SDRAMs, their performances are not directly related to the performance observable at the application level or system level. Moreover, since the corresponding number of a memory subsystem must also be equipped to control a number of SDRAMs, the cost of an NoC design will rapidly increase. Therefore, considerable attention has been shifted toward memory-aware NoC exploration to improve memory utilization and latency with the economical design cost of NoC platform [27].

#### 2.1 SDRAM-AWARE NOC DESIGN

A memory subsystem usually consists of three parts, i.e., a buffer, a SDRAM scheduler and a SDRAM interface signal generator (or memory controller), where a depth of buffer and an SDRAM scheduler for reordering dynamic SDRAM requests are key components for higher memory utilization and shorter memory latency. Panda et al. presented synthesis models for various off-chip memory access modes, as well as a technique for analyzing a behavior to determine memory accesses that can be optimized by exploiting the available memory features [90]. A memory scheduler proposed in [96] supports preemption and reordering to optimize offered net bandwidth and average latency. Schedulers discussed in [36] and [114] support preemption for high-priority requests to decouple latency and rate. In [1], PREDATOR is proposed with two step approaches: grouping memory requests and predictable arbitration for the group. A memory scheduler proposed in [44] adopts an adaptive history-based (AHB) scheduler that uses a history of recently scheduled operations to improve memory efficiency. However, the improvement just aided by such memory subsystems is severely limited

since diverse applications generate their specific memory requests with different latency constraints and the different data sizes.

Recently, microprocessors and shared buses considering SDRAM operations have been developed to support a guaranteed memory service. In [59], a memory bus was implemented to source-synchronous code division multiple access. A low-cost memory controller was present in [64] to maximize the benefit of useful prefetches and to minimize harms caused by useless prefetches. Cost-effective on-chip memory request issue mechanisms were proposed in [65] using SDRAM bank-level parallelism (BLP)-aware prefetch issue and BLP-preserving multi-core request issue. In [20], network interface architecture was proposed to cope with in-order delivery, resource utilization, and latency. A memory controller was integrated into this network interface to improve memory utilization and reduced both memory latency and network latency. However, they all do not provide an efficient priority memory service or an access granularity matching solution when using multiple SDRAMs.

Flow control in NoC is on how network resources, e.g. channel bandwidth, buffer capacity, and control state, are allocated to packets traversing a network. In previous works, congestion control is well studied for macro-networks. For example, decentralized control and predictive explicit-rate control are developed in [89], where sources adjust their traffic generation rates based on feedbacks received from bottleneck links. In [94], a predictive flow controller managing a packet injection rate to regulate the number of packet is proposed, based on traffic sources and router models. To minimize overall execution time and link utilization of applications, optimal link scheduling and shared buffer router architecture are proposed in [83]. An open-loop flow control scheme is proposed in [60] to reduce conflicts of data transfers from multiple memory modules to

the same masters. In addition to such congestion control mechanisms, flow controllers may be useful for scheduling packets for memories.

This section presents an SDRAM-aware NoC design to improve memory utilization and latency with a low design cost [50][54]. Our key ideas are twofold. First, if each NoC router schedules memory request packets, the packets arrive at a memory subsystem in the order that is friendly to SDRAM operations. Since our SDRAM-aware router uses existing resources to schedule the packets, e.g. input buffers for storing blocked packets and other flow-control mechanisms, additional circuitry is tiny. On the other hand, a heavy reordering buffer and a complex scheduler can be removed in a memory subsystem. Second, a scheduling scheme performed by multiple SDRAM-aware routers outperforms a scheduling scheme performed by a single memory subsystem. The reason is that the performance of single-stage scheduling mainly depends on the number of port/buffer in the single memory subsystem. However, the multi-stage scheduling uses all the buffers in multiple routers to schedule the memory request packets. Based on these ideas, the major novelty and contribution of this section include:

- We propose a novel NoC router architecture with explicit SDRAM-aware flow control to schedule SDRAM access requests instead of using the conventional memory subsystem.

- We propose SDRAM-aware flow control algorithms to resolve problems of bank conflict, data contention and short turn-around bank interleaving, which employs priority-based arbitration and multi-stage scheduling.

- We show that an NoC design embedding our SDRAM-aware router achieves higher memory utilization, shorter memory latency and cheaper design cost than the conventional NoC design with an SDRAM-unaware router.

• We show that performance of our SDRAM-aware router gets better for complex NoC architectures and high- performance SDRAM.

To the best of our knowledge, this is the first work that addresses a router scheduling memory requests instead of a memory subsystem. The rest of this section is organized as follows. In the next section, we survey related works. In Section 2.1.2, we review basic SDRAM operation principles and SDRAM request scheduling. In Section 2.1.3, the problem of the conventional SDRAM-unaware NoC router is presented and our basic solution is proposed. Section 2.1.4 presents detailed description of our SDRAM-aware router. Experimental results are shown in Section 2.1.5. Finally, Section 2.1.6 summarizes Section 2.1.

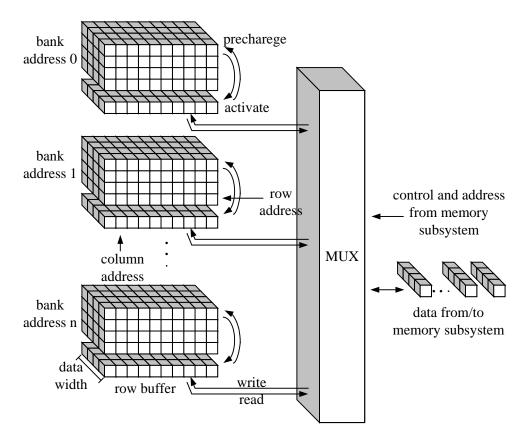

#### 2.1.1 Basic SDRAM Operation

SDRAM has a three dimensional structure, i.e., a bank, a row, and a column as shown in Figure 2.1. Basic commands to access SDRAM are activation (ACT), read/write (R/W), and precharge (PRE), where the ACT command is executed with a bank address (BA) and a row address (RA), the R/W command is executed with BA and a column address (CA), and the PRE command is executed only with BA. A bank becomes active by an ACT command and idle by a PRE command. An R/W command can be executed only after a bank is activated. In Figure 2.1, when a bank is activated, one row data of the bank move to a row buffer of the bank. It takes  $t_{RCD}$  to complete an ACT command. Timing parameters of DDR I, II, and III SDRAM used in this work is shown in Table 2.1 [24]. As shown in Table 2.1, the faster clock rate is used in DDR SDRAM, the more clock cycles are required to complete SDRAM operations. For

example, DDR I SDRAM working at 133MHz clock frequency spends only two clock cycles activating a bank while DDR III SDRAM working at 800MHz clock frequency spends 11 clock cycles activating a bank. Then, an R/W command is executed on the active row buffer. After either read latency called column access strobe (CAS) latency (CL) or write latency (WL), successive data go from or to SDRAM. Finally, a PRE command is executed to deactivate the active row buffer in the bank, i.e., data in the row buffer move to the bank of the row buffer. It takes the bank state  $t_{RP}$  to become an idle state.

Figure 2.1: SDRAM architecture and activation, read/write, and deactivation operations.

#### 2.1.2 SDRAM Scheduling

SDRAM consists of independent multiple banks whereas address and data pin/wire resources serialize accesses to different banks, as shown in Figure 2.1. The benefit of this architecture is that pin/wire resources between SDRAM and SoC can be saved and commands to different banks can be pipelined, i.e., while data are transferred to or from any bank, the rest of bank becomes idle and active for the latter request. Based on this principle, memory subsystems schedule SDRAM access requests. However, the improvement of memory performance is still limited due to special operation flows of SDRAMs and clock cycles wasted by timing constraints in Table 2.1. Moreover, it is much worse in high performance SDRAMs. Main factors which deteriorate memory performance are bank conflict, data contention, and short turn-around bank interleaving explained in the next three subsections.

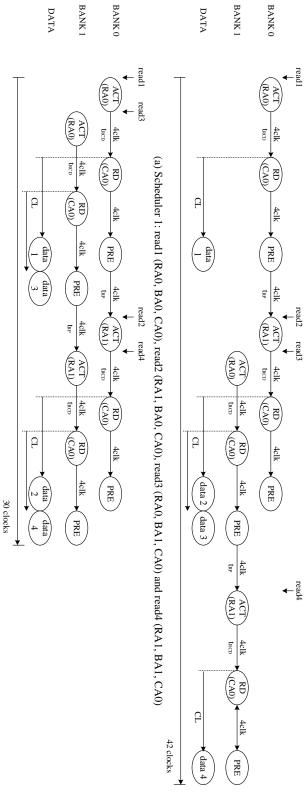

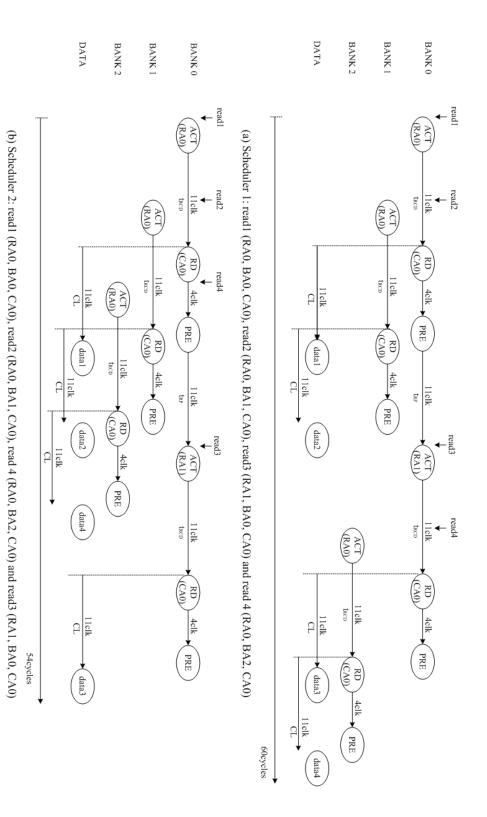

#### 2.1.2.1 Bank Conflict

Continuously accessing one bank with different RAs is called *bank conflict* which is the most critical to SDRAM performance. Since a bank activated by the former request should get idle and then active for the latter request again, a lot of clock cycles are required to complete these operations. For example, in Figure 2.2, there are two SDRAM schedulers reordering four read requests, i.e., read 1 (RA 0, BA 0, CA 0), read 2 (RA 1, BA 0, CA 0), read 3 (RA 0, BA 1, CA 0), and read 4 (RA 1, BA 1, CA 0). We assume that all schedulers work for DDR II SDRAM at 333MHz clock frequency. In Figure 2.2 (a), let them scheduled in the order, read 1, read 2, read 3, and read 4 by scheduler 1. After performing read 1, read 2 cannot be immediately executed since a row buffer of bank 0 is already occupied by data of RA 0. Hence, a PRE command should release the open row buffer of bank 0 and then an ACT command should be executed to fill the row

buffer of bank 0 with data of RA 1. On the contrary, read 3 can be pipelined, called *bank interleaving*, since it has different BA with read 2. As shown in Figure 2.2(a), while the bank 0 is activated and accessed for read 2, bank 1 gets activated for read 3. As a result, data 3 accessed by read 3 are generated with no loss of clock cycle. The last read 4 conflicts with read 3 since they have the same BAs, but different RAs.

On the contrary, scheduler 2 changes the execution order of four read requests, read 1, read 3, read 2, and read 4 as shown in Figure 2.2(b). Since this order does not cause any bank conflict, all read requests are pipelined. That means the second SDRAM scheduler lets all requests completed faster and latency of data 3 and 4 be shorter than the first SDRAM scheduler. In this example, the first scheduler achieves 9.5% (= 4 data/42 clock cycles) memory utilization and the second scheduler achieves 13.3% (= 4 data/30 clock cycles) memory utilization. Therefore, the second one is more desirable.

#### 2.1.2.2 Data Contention

A case of a write request followed by a read request or a read request followed by a write request is called *data contention*. Data pins/wires are bidirectional in most SDRAMs while control and address pins/wires are unidirectional. As a result, input data may be collided with output data. To transfer data to SDRAM after receiving data from SDRAM, there should be at least one clock cycle interval between writing data and reading data in DDR I/II SDRAM. Since internal read-to-write command delay time ( $t_{RTW}$ ) is required in DDR III SDRAM in Table 2.1, an interval between read data and write data happens up to two clock cycles.  $t_{RTW}$  is  $CL+t_{CCD}+2-WL$  if burst length (BL) is 8 or  $t_{RTW}$  is  $CL+t_{CCD}/2+2-WL$  if BL is 4. Hence, data contention is naturally hidden behind this delay time in DDR III SDRAM.

|               |                                 |                                |                       | $\overline{}$ | -             |        | $\overline{}$       |                    |               |

|---------------|---------------------------------|--------------------------------|-----------------------|---------------|---------------|--------|---------------------|--------------------|---------------|

| $t_{RTW}^{i}$ | $t_{\mathrm{WTR}}^{\mathrm{h}}$ | $t_{\mathrm{WR}}^{\mathrm{g}}$ | $t_{\mathtt{RP}}^{}}$ | tccpe         | $t_{RCD}^{d}$ | $WL^c$ | $CL^{\mathfrak{b}}$ | parameter          | Timing        |

| -             | 1                               | 2                              | 2                     | 1             | 2             | 1      | 2                   | 133MHz             | DDR I SDRAM   |

|               | 1                               | 3                              | 3                     | 1             | 3             | 1      | 2.5                 | 167MHz             |               |

|               | 2                               | 3                              | 3                     | 1             | 3             | 1      | 3                   | 200MHz             |               |

|               | 2                               | 3                              | 3                     | 2             | 3             | 2      | 3                   | $200 \mathrm{MHz}$ | DDR II SDRAM  |

| -             | 2                               | 4                              | 4                     | 2             | 4             | 3      | 4                   | 267MHz             |               |

| -             | 3                               | 5                              | 4                     | 2             | 4             | 3      | 4                   | 333MHz             |               |

| -             | 3                               | 6                              | 6                     | 2             | 6             | 5      | 6                   | 400MHz             |               |

| 7             | 4                               | 6                              | 6                     | 4             | 6             | 5      | 6                   | 400 MHz            | DDR III SDRAM |

| 8             | 4                               | 8                              | 8                     | 4             | 8             | 6      | 8                   | 533MHz             |               |

| 9             | 5                               | 10                             | 9                     | 4             | 10            | 7      | 10                  | 667MHz             |               |

| 9             | 6                               | 12                             | 11                    | 4             | 11            | 8      | 11                  | 800MHz             |               |

<sup>&</sup>lt;sup>a</sup> We assume that posted CAS (Column Access Strobe) additive latency (AL) is 0 in DDR II/III SDRAM.

<sup>b</sup>CAS latency or read latency.

Table 2.1: Timing parameter of DDR I, IIa, and IIIa SDRAM.

<sup>&</sup>lt;sup>c</sup> Write latency.

<sup>&</sup>lt;sup>d</sup>RAS (Row Access Strobe) to CAS delay time. <sup>e</sup>CAS-to-CAS command delay

fRow precharge time.

§ Write recovery time.

§ Write recovery time.

h Internal write-to-read command delay time.

i Internal read-to-write command delay time for DDR III SDRAM. If Burst Length (BL) is 8, it is  $CL + t_{CCD} + 2 - WL$  and if BL is 4, it is  $4 - CCL + t_{CCD} + 2 - WL$ . In this table, BL is 8.

Figure 2.2: Examples showing bank conflict and interleaving in DDR II SDRAM @333MHz.

(b) Scheduler 2: read1 (RA0, BA0, CA0), read3 (RA0, BA1, CA0), read2 (RA1, BA0, CA0) and read4 (RA1, BA1, CA0)

On the other hand, a read command following a write command needs internal write-to-read command delay time ( $t_{WTR}$ ) to be executed. Then, after read latency or CL, reading data can be received from SDRAM. Write-to-read data contention is naturally hidden behind  $t_{WTR}$  and CL, but they cause memory utilization and memory latency degraded critically. Therefore, continuous read or write requests are preferred to access SDRAM efficiently.

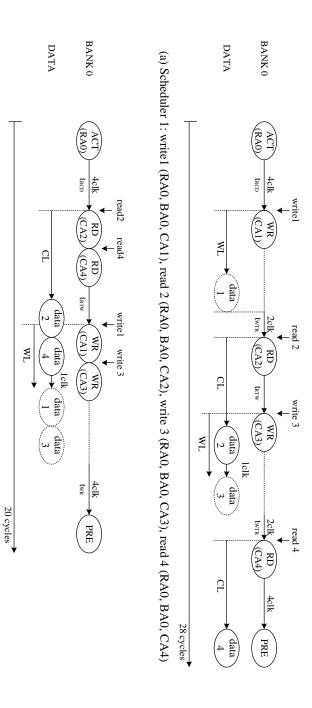

For example, in Figure 2.3, there are two SDRAM schedulers reordering two write requests and two read requests, i.e., write 1 (RA 0, BA 0, CA 1), read 2 (RA 0, BA 0, CA 2), write 3 (RA 0, BA 0, CA 3), and read 4 (RA 0, BA 0, CA 4). All schedulers interface with DDR II SDRAM working at 266MHz clock frequency. As shown in Figure 2.3(a), let them scheduled in the order, write 1, read 2, write 3, and read 4 by scheduler 1. In this figure, read 2 cannot be immediately performed after writing all data 1 since  $t_{WTR}$ is required to accept the next read command. Furthermore, since data 2 are received from SDRAM after read latency or CL, a read request following a write request wastes total  $t_{WTR}$  and CL cycles even if bank conflict does not happen between two requests. If both bank conflict and data contention happen simultaneously, bank conflict is commonly prioritized. Since bank conflict wastes more clock cycles than data contention, data contention is hidden behind bank conflict. On the contrary, a write request following a read request has no internal command delays in DDR I/II SDRAM. Instead, a write command performing write 3 should be given to DDR SDRAM when it does not cause any collision with data 2. Most DDR I/II SDRAM schedulers get at least one clock cycle interval between read data and write data. If DDR III SDRAM is used, data contention is hidden naturally behind  $t_{RTW}$ . The last read 4 requires both  $t_{WTR}$  and CL before transferring data 4.

Figure 2.3: Examples showing data contention in DDR II SDRAM @266MHz.

(b) Scheduler 2: read 2 (RA0, BA0, CA2), read 4 (RA0, BA0, CA4), write 1 (RA0, BA0, CA1), write 3 (RA0, BA0, CA3)

On the contrary, scheduler 2 changes the order of two write requests and two read requests, i.e., read 2, read 4, write 1 and write 3 as shown in Figure 2.3(b). Since this order causes one data contention wasting just one clock cycle, all read/write requests are performed faster than scheduler 1. In common SDRAM operations, after writing data 3, write recovery time ( $t_{WR}$ ) is required to accept a PRE command. Scheduler 1 and scheduler 2 take 28 and 20 clock cycles, respectively, until bank 0 becomes idle after performing all requests. As a result, scheduler 1 achieves 14.3% (= 4 data/28 clock cycles) memory utilization and scheduler 2 achieves 20% (= 4 data/20 clock cycles) memory utilization. Therefore, continuous read or write requests are encouraged to access SDRAM efficiently.

## 2.1.2.3 Short Turn-Around Bank Interleaving

A bank interleaving approach as a solution of bank conflict is the efficient technique. Hence, high memory utilization and short memory latency can be achieved as explained in Section 2.1.2.1. However, bank interleaving may achieve little improvement, in particular, in high performance SDRAM even if bank interleaving is performed completely. In Table 2.1, as an operating clock of SDRAM is faster and faster, activation delay time ( $t_{RCD}$ ), deactivation delay time ( $t_{RP}$ ) and read/write latency (CL/WL) are also longer and longer. The long delay times let the benefit of bank interleaving critically degraded since a bank interleaved may not get sufficient time to be deactivated or reactivated after the bank is accessed by the previous request with different RA.

For example, in Figure 2.4, there are two SDRAM schedulers reordering four read requests, i.e., read 1 (RA 0, BA 0, CA 0), read 2 (RA 0, BA 1, CA 0), read 3 (RA 1, BA 0, CA 0), and read 4 (RA 0, BA 2, CA 0). We assume that all schedulers work for DDR

Figure 2.4: Examples showing short turn-around bank interleaving in DDR III SDRAM @800MHz.

III SDRAM at 800MHz clock frequency. In Figure 2.4(a), let them be scheduled in the order, read 1, read 2, read 3, and read 4 by scheduler 1 such that all read requests are performed without bank conflict. After performing read 1, bank 0 is deactivated and read 2 starts to receive data 2. Then, read 3 waits until all data 2 are received. However, read 3 accessing bank 0 cannot be performed even if read 2 is done and the relation between read 2 and read 3 is bank interleaving. The reason is that bank 0 accessed by read 1 is not deactivated due to too long  $t_{RP}$ , i.e., operations for read 3 such as deactivation, reactivation, and read/write cannot be hidden behind the process of read 2. Hence, while bank 0 is deactivated, reactivated with data of RA 1, and ready to transfer data 3, any data cannot be transferred or received from other banks, which makes memory utilization and latency degraded.

On the contrary, scheduler 2 changes the execution order of read 3 and read 4 as shown in Figure 2.4(b). As a result, read 4 accessing bank 2 can be hidden behind the process of executing read 2 and even read 3 accessing bank 0 can be hidden behind the process of executing read 4. If there is another read 5 accessing bank 3 and it is performed between read 4 and read 3, data may be transferred more continuously with no loss of clock cycle. Consequently, memory utilizations by scheduler 1 and scheduler 2 are 6.7% (= 4 data/60 clock cycles) and 7.4% (= 4 data/54 clock cycles), respectively. Since this problem is more serious in high performance DDR SDRAM, a memory subsystem should check when banks get active again even if bank interleaving is performed completely.

# 2.1.3 NoC Design with SDRAM

#### 2.1.3.1 Problem Description

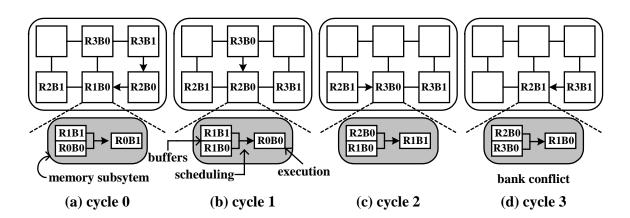

Bank conflict and data contention frequently happen in the conventional NoC design due to limited resources such as an input buffer in a memory subsystem. Moreover, short turn-around bank interleaving also happens in high performance DDR SDRAM. Figure 2.5 shows a simple example of bank conflict in a 2×3 NoC design under the limited resources. This NoC includes a single memory subsystem that consists of an input buffer, a memory scheduler and an SDRAM interface signal generator. The memory scheduler reorders packets stored in the input buffer to avoid bank conflict, data contention and short turn-around bank interleaving. In this figure, *RxBy* means that a row address (RA) and a bank address (BA) of packet are *x* and *y*, respectively. An arrow indicates that a packet will move to the direction at the next clock cycle. We assume that a length of all packets is 1, the memory subsystem includes a two-depth input buffer to store two packets and the scheduler makes one of two stored packets executed every cycle (although execution time is actually longer than one cycle).

Figure 2.5: Bank conflict in  $2 \times 3$  NoC with conventional round-robin flows controller although an effective memory subsystem.

In Figure 2.5, round-robin arbitration [19] is adopted as a flow control mechanism of NoC routers to assign a channel and an input buffer of the next node to one packet among several competing packets. At cycle 0, three packets, R2B0, R2B1 and R3B0 get a competition for an advance to the router interconnected to the memory subsystem and we assume that R2B0 wins. R0B1 is executed in the memory subsystem. At cycle 1, R2B0 advances to the router interconnected to the memory subsystem and then R3B1 also advances to the empty router by the advance of R2B0. Then three packets, R2B1, R3B0 and R3B1 also get the competition such that R3B0 wins by round-robin arbitration. In the memory subsystem, R0B0 but not R1B1 is executed for avoiding bank conflict since R0B1 accessing bank 0 is performed at cycle 0. At cycle 2, R3B0 advances in the router interconnected to the memory subsystem and R1B1 is executed in the memory subsystem. Then, two packets, R3B1 and R2B1 get the competition such that R2B1 wins by round-robin arbitration. At cycle 3, bank conflict happens in the memory subsystem since current execution is a bank 0 request and two buffers are also stored with bank 0 requests, where all row addresses are different. Although the efficient memory subsystem is included in the NoC design, it is difficult to avoid bank conflict completely under the limited depth of a buffer and the dynamic SDRAM accesses of processing elements. Data contention and short turn-around bank interleaving can happen in the conventional NoC design by similar mechanism to this example.

# 2.1.3.2 Basic Idea of Our Approach

In our NoC design, scheduling SDRAM request packets is performed by multiple SDRAM-aware routers. This architecture makes the possibility of bank conflict lower since packets arrive at a memory subsystem in the order that is friendly to SDRAM

operations. Figure 2.6 shows how NoC with our SDRAM-aware router works well without bank conflict. At the first competition (cycle 0) for an advance to the router interconnected to the memory subsystem, the winner is R2B1 accessing bank 1 since the former packet (R1B0) passed in this router accesses bank 0. The rest of packet causes bank conflict since they read/write data in the same bank but different row addresses from the former packet. At cycle 1, R2B1 advances to the router interconnected to the memory subsystem and then R2B0 and R3B0 get the competition. Both can be a winner for the next advance since they access bank 0. In this example, R2B0 is chosen by our SDRAM-aware router. At cycle 2, R2B0 advances to the router interconnected to the memory subsystem and R3B1 avoiding bank conflict wins against R3B0 for the next advance. Finally, R3B1 advances to the router interconnected to the memory subsystem and R3B0 follows R3B1 at cycle 3. As a result, an NoC design with our SDRAM-aware router avoids bank conflict better than an NoC design with the conventional memory subsystem and router.

Figure 2.6: No bank conflict in  $2 \times 3$  NoC with SDRAM-aware flow controller although a simple memory subsystem.

A single memory subsystem usually controls one channel of SDRAM in the conventional NoC, which means the same number of memory subsystem as the number of SDRAM channel is required. Whereas it is allowable to use multiple SDRAMs for high performance, it is not desirable to use a corresponding number of memory subsystems. The reason is that the memory subsystem as shown in Figure 2.5 is too high in terms of hardware cost due to the heavy input buffer and the complex scheduler. Furthermore, a depth of input buffer rapidly increases as a length of packet is longer and longer in a high definition graphics/video system. On the other hand, the proposed architecture saves the NoC design cost since any input buffer and any scheduler are not required in the memory subsystem as shown in Figure 2.6. Instead, a simple flow controller is included in multiple routers, which has a very low hardware cost compared to an input buffer and a scheduler in a memory subsystem. In the next section, we present a novel SDRAM-aware NoC router in detail.

### 2.1.4 SDRAM-Aware Router

For a wide range of applications, the proposed NoC router is about a novel paradigm for SDRAM-aware-NoC exploration, which has a flow-control mechanism improve memory utilization and memory latency with a cost-effective NoC platform. Indeed, based on our idea present in Section 2.1.3.2, any deterministic and adaptive routing scheme can be combined to implement our SDRAM-aware router. Another flow-control mechanism can be also combined to avoid deadlock and livelock [19], to make traffic load balanced on a network [83][89][94] and to manage buffers and channel bandwidth [58].

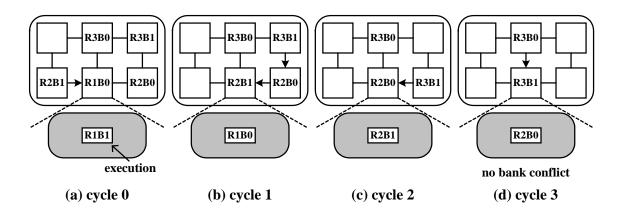

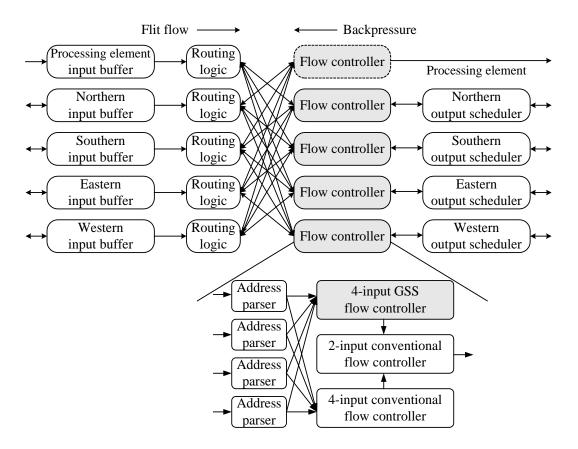

#### 2.1.4.1 Router Description

Our NoC router consists of an input buffer, a routing logic, a flow controller and an output scheduler as shown in Figure 2.7. A packet is split into so-called flits (flow control digits) which are then routed and stored in a pipelined fashion. The input buffers are managed by a wormhole flow control mechanism or a virtual-channel flow control mechanism and backpressure is used to inform upstream nodes when they must stop transmitting flits because all of the downstream input buffers are full. For our experiment, the wormhole flow control mechanism is implemented due to its simplicity and wide popularity [19] and an on/off flow control mechanism for the backpressure is employed to avoid a loss of flits.

Figure 2.7: The architecture of an SDRAM-aware router consisting of input buffers, routing logics, flow controllers, and output schedulers for a mesh network.

Our SDRAM-aware router can be implemented to either deterministic or adaptive routers according to a routing logic that guarantees deadlock and livelock freeness. Virtual channels and deterministic dimension-ordered routings (e.g. XY routing, odd-even routing) are commonly used to prevent deadlock [19]. We implement XY routing that is a deterministic and minimal path routing algorithm such that it guarantees

deadlock- and livelock-free routing. In addition, we consider an ordering issue when a master core sends a read request to another slave core before the master core receives a read data from one slave core or when a master core requests another read data to a slave core in NoC employing an adaptive router before the master core receives one read data from the slave core. This ordering issue can be solved by [61] or under the following constraint: a master core can send a read request to a slave core only after the master core receives all data requested. The latter solution is employed in our implementation. In addition, since our SDRAM-aware flow control algorithm is performed with in-order buffers, the ordering problem does not happen in each SDRAM-flow control.

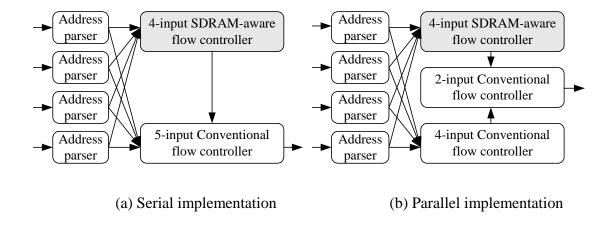

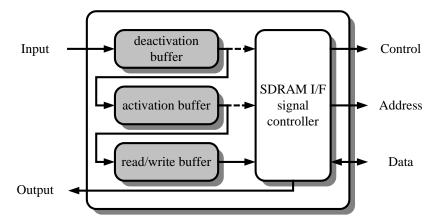

In this router, more than two flits arriving on different input buffers at the same time may both desire the same channel toward a memory subsystem. In this situation, our flow-control mechanism resolves this contention, allocating the channel to one packet and dealing with the others, blocked packets. Figure 2.8 shows our SDRAM-aware flow controller combined with the conventional flow controller. In Figure 2.8, an address parser sends an incoming memory request packet to our SDRAM-aware flow controller and an incoming normal packet to the conventional flow controller. Our SDRAM-aware flow controller schedules the memory packets in order to prevent bank conflict, data contention and short turn-around bank interleaving. In the next section, the SDRAM-aware flow-control algorithm using a priority-based arbitration is described minutely. Then, the resulting memory request packet competes with normal packets by the conventional flow control mechanism. Hence, normal packets can reach their destination with no additional communication delay.

Figure 2.8(a) shows its serial implementation. This architecture causes a timing path to be much longer since a 5-input conventional flow control algorithm is performed

Figure 2.8: The architecture of an SDRAM-aware flow controller combined with a conventional flow controller for a mesh network.

after performing our 4-input SDRAM-aware flow control algorithm. On the other hand, in Figure 2.8(b), our 4-input SDRAM-aware flow controller for memory packets and a 4-input conventional flow control algorithm for normal packets are parallelly performed. Finally, two resulting packets are scheduled by a 2-input conventional flow controller. This parallel implementation can minimize an increase of timing path whereas its design cost is more expensive than the design cost of the serial implementation. We adopt this parallel implementation in our experiment. In addition, our flow controllers adopt winner-take-all bandwidth allocation that allocates all of the bandwidth to just one packet until it is finished or blocked before serving the other packets [19].

An output scheduler either detects if an input buffer of the next router is available or expects when the input buffer is available. When an input buffer of the next router is full and a deterministic routing logic is implemented, an output scheduler lets the corresponding SDRAM-aware flow controller stop scheduling packets. On the other hand, packets given multiple routing paths performed by an adaptive routing logic can be scheduled to other flow controller less busy.

# 2.1.4.2 SDRAM-Aware Flow Control for Avoiding Bank Conflict and Data Contention

Our flow control acts to allocate a channel to one of competing flits which destination is a memory subsystem interfacing with SDRAM. Therefore, our flow-control mechanism performs arbitration to determine which flit gets the channel it has requested. After the arbitration, a winning flit advances over this channel. Our arbitration algorithm also decides how to dispose of any flits that do not get their requested channel.

In Algorithm 1 called SP, our arbitration is a priority-based algorithm, where a priority is determined by SDRAM awareness. The priority is assigned to all head flits which destination is a memory subsystem. Let h(n) be a head flit of a packet, which is already allocated a channel by the SDRAM-aware flow control at the nth arbitration. Body and tail flits are assigned the same channel as their head flit. Let  $h_i(n+1)$  be one of all competing head flits (I)—which should be allocated to the same channel as h(n) by the SDRAM-aware flow control at the (n+1)th arbitration, where  $i \in I$ . The head flits, h(n) and  $h_i(n+1)$  contain address and command information to access SDRAM, denoted by  $(RA_n, BA_n, R/W_n)$  and  $(RA_{n+1,i}, BA_{n+1,i}, R/W_{n+1,i})$ , respectively, where the notations are (row address, bank address, read/write command). At the (n+1)th arbitration, all  $h_i(n+1)$

## Algorithm 1 Scheduling Packet to Avoid Bank Conflict and Data Contention

```

Input: h(n), h_i(n+1) and Table 2.2

1:

for each h_i(n+1), i \in I do

2:

if h_i(n+1) is a new packet entering to the router then

w_i = 0:

3:

4:

else

5:

w_i = w_i + \text{waiting cycles from previous arbitration(n)};

6:

7:

d_i = delay cycle between h(n) and h_i(n+1) from Table 2.2;

8:

p_i = w_i - d_i;

9:

end for

h_i(n+1) with maximum(p_i) is allocated to a channel;

10:

Output: h(n+1)

```

are compared to h(n) and then are given a delay penalty from Table II (line 7) that is composed from DDR I, II and III SDRAM working at 133MHz to at 800MHz clock frequency (with 266MHz to 1.6GHz data rate) [24].

Table 2.2 shows how many clock cycles waste by bank conflict and data contention or a combination thereof when  $h_i(n+1)$  accesses SDRAM after h(n). If bank conflict and data contention happen simultaneously, bank conflict is commonly prioritized since bank conflict wastes more clock cycles than data contention. According to a read/write command, a bank address and a row address, there are twelve cases as shown in Table 2.2. Twelve cases are also classified into eight delay types that are described as follows:

Delay a: Case 1 and case 10 have no clock cycle loss since  $h_i(n+1)$  is the same read/write command, bank address and row address as h(n). These cases indicate that the same row data of the same bank are again accessed by the same command. Thus, the bank does not need to be deactivated and reactivated, which causes the clock cycle loss. In addition, read/write latency of  $h_i(n+1)$  can be hidden while h(n) is accessed. In Figure 2.3(b), the relation between read 2 and read 4 is case 1 and the relation between write 1 and write 3 is case 10.

Delay b: Case 2 is the read-to-read bank conflict explained in Section 2.1.2.1. Before executing the latter read accessing the same bank but a different row, the bank must be deactivated, i.e. data in the row buffer move to the corresponding row of the bank. Then, the bank must be activated again, which indicates that the row buffer should be again filled with new data for the latter read. Thus, it takes  $t_{RP}+t_{RCD}+CL$  to receive data of the latter read after receiving data of the former

| Relation                                                                                       |                                    | RW <sub>z</sub> =R |                                                   |              |                   |                        |                                    | RW <sub>n</sub> =W |                                      |                                    |                   |                                      |                        |

|------------------------------------------------------------------------------------------------|------------------------------------|--------------------|---------------------------------------------------|--------------|-------------------|------------------------|------------------------------------|--------------------|--------------------------------------|------------------------------------|-------------------|--------------------------------------|------------------------|

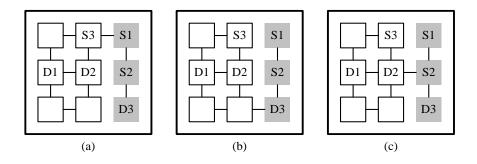

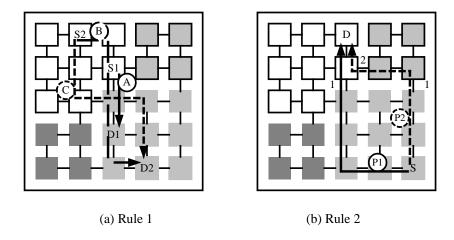

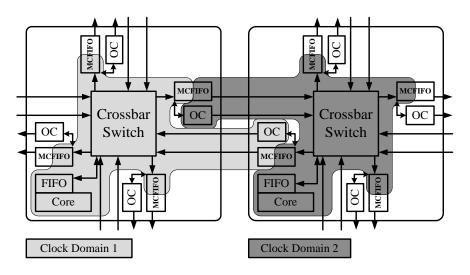

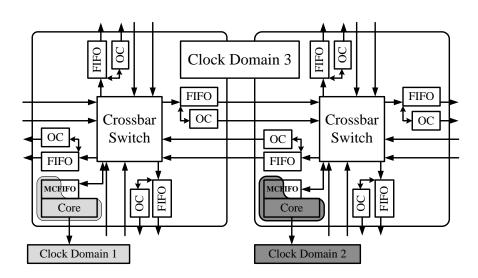

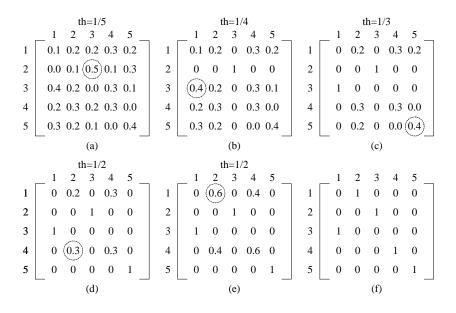

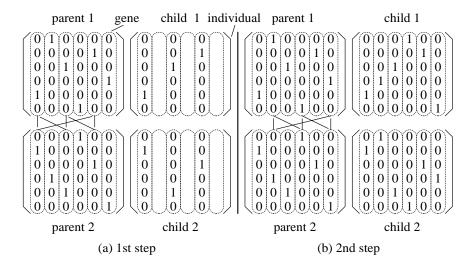

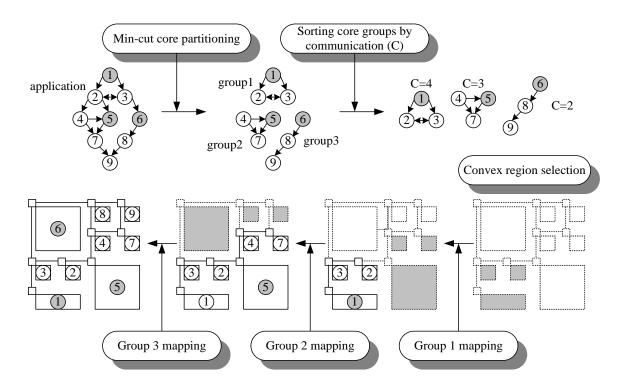

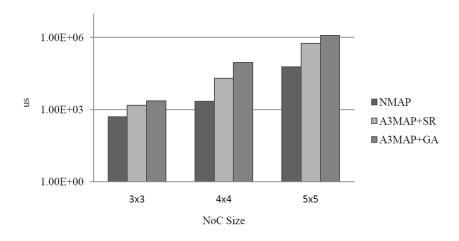

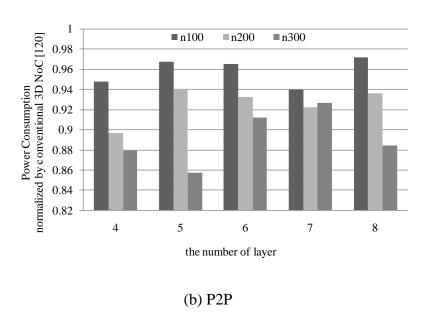

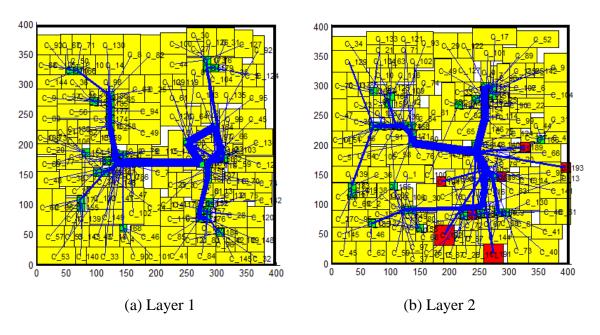

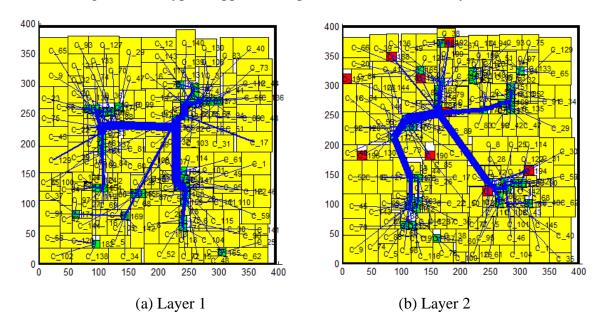

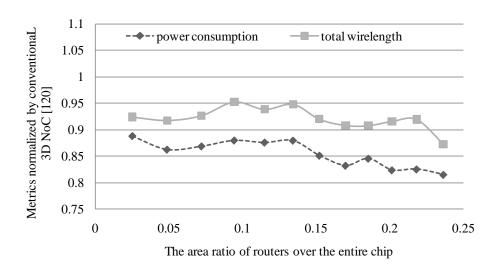

| of $h(n)$ with RV                                                                              | with RWn+l,i,                      |                    | $RW_{n+1,i}=R$                                    |              |                   | $RW_{n+1,i}=W$         |                                    |                    | $RW_{n+1,i}=R$                       |                                    |                   | $RW_{n+1,i}=W$                       |                        |