Copyright

by

Wing-Chi Poon

2010

# The Dissertation Committee for Wing-Chi Poon certifies that this is the approved version of the following dissertation:

# **Real-Time Hierarchical Hypervisor**

| Committee:                  |

|-----------------------------|

| Aloysius K. Mok, Supervisor |

| James Browne                |

| Mike Dahlin                 |

| Greg Plaxton                |

| Deji Chen                   |

# **Real-Time Hierarchical Hypervisor**

by

Wing-Chi Poon, BEng, MSc

#### **DISSERTATION**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

#### **DOCTOR OF PHILOSOPHY**

THE UNIVERSITY OF TEXAS AT AUSTIN

August 2010

# Acknowledgments

Glory to God in the highest, and thank God for His loving kindness. I ventured into the journey for a PhD before I was saved by His grace, but ultimately it is God who helped me to finish this race. His love endureth forever!

The road to a PhD has been a long one for me. Countless number of people have helped me in the process. Without their support and encouragement, I would not have completed the program. Just as the holy Bible puts it: "I returned, and saw under the sun, that the race is not to the swift, nor the battle to the strong, neither yet bread to the wise, nor yet riches to men of understanding, nor yet favor to men of skill; but time and chance happeneth to them all" (Ecclesiastes 9:11, KJV) and "I know that, whatsoever God doeth, it shall be forever: nothing can be put to it, nor anything taken from it: and God doeth it, that men should fear before Him." (Ecclesiastes 3:14, KJV).

I would like to thank my parents for their up-bringing. They cared for my academic success from a very early age, and set a good example of continuous learning. They supported my quest to continue my higher education in United States.

My advisor Prof. Aloysius K. Mok provided excellent guidance throughout the process. He allowed great freedom to his students in our pursuit of intellectual excellence. I would like to thank my committee members Prof. James Browne, Prof. Mike Dahlin, Prof. Greg Plaxton and Dr. Deji Chen for their time and valuable input. I would like to thank my graduate advisors and graduate coordinators for their help with the graduation process. I would like to thank people from my research group Pak-Ho Chung, Xiang Feng, Yi Feng, Song Han, Zhenting He, Ruiqi Hu, Raymond Lau, Chan-Gun Lee, Huiya Liu, Yanbin Liu, Jianping Song, Peiyu Wang, Weirong Wang, Hung-Uk Woo, Jianliang Yi, Weijiang Yu and Xiuming Zhu for their fruitful discussions. The former works of Xiang Feng and Zhenting He were especially important towards building up this dissertation. I also had good discussion with other people in my department who are not in the same research group, including but not limited to Huiling Gong, Yan Li, Yi Li, Jia Liu, Yu Sun, Yuk-Wah Wong, Hua Xiang, Xincheng Zhang, Jiandan Zhen. I would also like to thank my roommates Junwei Huang and Rongfeng Shen during these years.

Part of the idea of the dissertation originated from my summer co-op at AMD, when I had access to expertise in the x86 architecture. Kevin J. McGrath, Ben Serebrin and Erich Boleyn had been especially helpful to me in my learning. The dissertation could not be completed without the full support of my acting manager and principal engineer Ole Agesen, my current manager Jerri-Ann Meyer, all my colleagues in the monitor group and monitor verification group especially for technical help from Ole Agesen, Jim Mattson and Ben Serebrin from the monitor group, and Haoqiang Zheng and Carl Waldspurger from the vmkernel group. Alex Gathwaite, Jeffrey Sheldon, Ross Knippel, Wei Xu and my officemate Michael Ho, all from the monitor group, have also greatly encouraged me and/or shared some of my workload while I worked on the dissertation. Some people from other teams

also encouraged me in the process, including but not limited to Limin Wang, Tony Huang and Lisa Liu.

These years, I have enjoyed wonderful times with friends from church. They gave me much support, encouragement and inspiration from time to time. I would like to thank the guidance, patience and good example of the counsellors of Austin Chinese Campus Christian Fellowship (ACCCF) Pastor Philip Hsu, Sylvia Hay, Phil and Ruth Chang, Morgan and Yuning Lin, Shin-Tower and Lie-Ching Wang, Hsing-Pang and Mei-Fang Wang, Charles and Esther Tang; the counsellors of Silicon Valley Christian Assembly (SVCA) Rainbow Fellowship James and Julie Chen, Pastors Hung-Chieh and Nancy Yu; and the counsellors of Stanford Campus Evengelical Fellowship (CEF) Sister Gan, Dr. Juan. Various people have also influenced me in non-trivial ways.

The final months of my PhD began with Urbana 2009 mission conference in St. Louis MO. People who are not listed above and greatly influenced me during these months include Tin-Ying Hsu (ACCCF), Yi-Ju Hsiao (ACCCF), Kevin Tung (ACCCF), Hsin-Yao Chen (ACCCF), Pastor and Mrs. James Liu (SVCA), Pastor John Shou and Mrs. Esther Shou (SVCA), Han Hu (SVCA), Auntie Christine Yu (SVCA) and Wenwei Zheng (CEF). I would like to thank Yang Li and Dandan Wang, Lan Tang and Lina Zhang for their hospitality. Last but not least, I would also like to thank Daniel and Karen Evans for proof-reading my dissertation for grammatical correctness.

**Real-Time Hierarchical Hypervisor**

Publication No. \_

Wing-Chi Poon, Ph.D.

The University of Texas at Austin, 2010

Supervisor: Aloysius K. Mok

Both real-time virtualization and recursive virtualization are desirable prop-

erties of a virtual machine monitor (or hypervisor). Although the prospect for vir-

tualization and even recursive virtualization has become better as the PC hardware

becomes faster, the real-time systems community so far has not been able to reap

much benefits. This is because no existing virtualization mechanism can properly

support the stringent timing requirements needed by real-time systems. It is hard

to do real-time virtualization, and it is even harder to do it recursively. In this dis-

sertation, we propose a framework whereby the hypervisor is capable of running

real-time guests and participating in recursive virtualization. Such a hypervisor is

called a real-time hierarchical hypervisor.

We first look at virtualization of abstract resource types from the real-time

systems perspective. Unlike the previous work on recursive real-time partition-

ing that assumes fully-preemptable resources, we concentrate on other and often

more practical types of scheduling constraints, especially the non-preemptive and

viii

limited-preemptive ones. Then we consider the current x86 architecture and explore the problems that need to be addressed for real-time recursive virtualization. We drill down on the problem that affects timing properties the most, namely, the recursive forwarding and delivery of interrupts, exceptions and intercepts. We choose the x86 architecture because it is popular and readily available, but it is by no means the only architecture of choice for real-time recursive virtualization. We conclude the research with an architecture-independent discussion on future possibilities in real-time recursive virtualization.

# **Table of Contents**

| Acknov  | vledgm | nents                                                        | V      |

|---------|--------|--------------------------------------------------------------|--------|

| Abstra  | ct     |                                                              | viii   |

| List of | Tables |                                                              | xv     |

| List of | Figure | s                                                            | xvi    |

| Chapte  | r 1. I | ntroduction                                                  | 1      |

| 1.1     | Abstra | act Resource Virtualization                                  | . 2    |

| 1.2     | Time   | Sharing Fully Preemptable Resource                           | . 3    |

|         | 1.2.1  | The Bounded-Delay Resource Partition (BDRP) Model            | 3      |

|         |        | 1.2.1.1 Task Level Scheduling                                | . 5    |

|         |        | 1.2.1.2 Recursive Resource Level Scheduling                  | 6      |

| 1.3     | The x  | 86 Recursive Virtualization                                  | . 7    |

| Chapte  | r 2. I | Non-Preemptive Robustness - Definition and Characteriza tion | -<br>9 |

| 2.1     | Introd | luction                                                      | 9      |

|         | 2.1.1  | Requirements Space - Periodic Task Set                       | . 11   |

|         | 2.1.2  | Design - Priority Assignment                                 | 12     |

|         | 2.1.3  | Requirement Change - Reduction in System Load                | 13     |

|         | 2.1.4  | Robustness                                                   | 14     |

|         | 2.1.5  | Preemptiveness vs Non-preemptiveness                         | 15     |

|         | 2.1.6  | Some Definitions and Notations                               | 15     |

|         | 2.1.7  | Related Works                                                | 16     |

| 2.2     | Robus  | stness of Preemptive Schedulers                              | 17     |

|         | 2.2.1  | Preemptive Earliest-Deadline-First (PEDF)                    | 18     |

|         | 2.2.2  | Preemptive Fixed-Priority (PFP)                              | 19     |

| 2.3    | Loss   | of Robustness in Non-preemptive Schedulers                                                                   | 22 |

|--------|--------|--------------------------------------------------------------------------------------------------------------|----|

| 2.4    | How l  | Bad is the Non-Preemptive Robustness Problem                                                                 | 23 |

| 2.5    | Prope  | rties of Non-preemptive Anomaly                                                                              | 29 |

| 2.6    | Miss 1 | Ratio                                                                                                        | 35 |

| 2.7    | Concl  | usion                                                                                                        | 40 |

|        | •      |                                                                                                              |    |

| Chapte |        | Solutions to the Non-Preemptive Robustness Problem                                                           | 41 |

| 3.1    |        | uction                                                                                                       | 41 |

|        | 3.1.1  | Task Model                                                                                                   | 43 |

|        | 3.1.2  | Reduction in System Load Revisited                                                                           | 45 |

|        | 3.1.3  | Robustness Revisited                                                                                         | 47 |

| 3.2    | Relate | ed Work                                                                                                      | 47 |

| 3.3    | Prope  | rties of Non-Preemptive Robustness                                                                           | 48 |

|        | 3.3.1  | Concrete Robustness and Non-Concrete Schedulability                                                          | 49 |

|        | 3.3.2  | Increase in Period / Minimum Separation ( $\uparrow P$ ) vs. Decrease in Computation Time ( $\downarrow C$ ) | 52 |

| 3.4    | Comn   | non Non-Preemptive Schedulers                                                                                | 55 |

|        | 3.4.1  | Discrete-Time, NPEDF Scheduler                                                                               | 55 |

|        | 3.4.2  | Dense Time, NPEDF Scheduler                                                                                  | 57 |

|        | 3.4.3  | Discrete or Dense Time, NPFP Scheduler                                                                       | 59 |

| 3.5    | Specia | al Cases for Non-preemptive Robustness                                                                       | 62 |

|        | 3.5.1  | Geometric Envelope Task Set                                                                                  | 62 |

|        | 3.5.2  | No-Blocking Test                                                                                             | 63 |

|        | 3.5.3  | Necessary and Sufficient Condition of Robustness for Task<br>Set of Successively Divisible Period            | 65 |

| 3.6    | Concl  | usion                                                                                                        | 67 |

|        |        |                                                                                                              |    |

| Chapte | r 4.   | <b>Fime Sharing Limited-Preemptable Resources and Mixed- Type Resources</b>                                  | 69 |

| 4.1    | Introd | uction                                                                                                       | 69 |

| 4.2    | Robus  | stness for Limited Preemption                                                                                | 70 |

| 4.3    | Robus  | stness on a Bounded Delay Resource Partition (BDRP)                                                          | 71 |

|        | 4.3.1  | Preemptive Robustness on a Bounded Delay Resource Partition (BDRP)                                           | 72 |

|        |       | 4.3.1.1           | Preemptive Earliest-Deadline-First (PEDF)                         | 72 |

|--------|-------|-------------------|-------------------------------------------------------------------|----|

|        |       | 4.3.1.2           | Preemptive Fixed Priority (PFP)                                   | 74 |

|        | 4.3.2 |                   | emptive Robustness on a Bounded Delay Resource (BDRP)             | 76 |

| 4.4    | Resou | ırce Level        | Scheduling with Aperiodic Tasks under Discrete Time               | 77 |

|        | 4.4.1 | The Pro           | blem                                                              | 78 |

|        | 4.4.2 | VMware            | e ESX Server Case Study                                           | 79 |

|        | 4.4.3 | A Paran           | netric Delay Bound $\Delta$ Solution                              | 80 |

|        | 4.4.4 | Why Isn           | 't Parametric Granularity a Good Idea?                            | 81 |

| 4.5    | Time  | Sharing N         | Mixed Set of Resources                                            | 82 |

| 4.6    | Concl | lusion            |                                                                   | 82 |

| Chapte | r 5.  | Г <b>he x86</b> Н | lierarchical Hypervisor                                           | 84 |

| 5.1    |       |                   |                                                                   | 84 |

|        | 5.1.1 |                   | on                                                                | 84 |

|        | 5.1.2 | Related           | Works                                                             | 85 |

| 5.2    | Why 1 | Recursive         | Virtualization?                                                   | 86 |

|        | 5.2.1 |                   | ing and Upgrading to New Hypervisor                               | 86 |

|        | 5.2.2 | Testing 1         | Hypervisor Management Software                                    | 87 |

|        | 5.2.3 | Hardwa            | re Feature Prototyping                                            | 87 |

|        | 5.2.4 | GENI N            | et                                                                | 88 |

|        | 5.2.5 | Real-Tir          | ne Resource Partitioning                                          | 88 |

| 5.3    | Desig | n Issues o        | on the x86 Architecture                                           | 88 |

|        | 5.3.1 | Trap-and          | d-Emulate vs. Paravirtualization                                  | 89 |

|        | 5.3.2 | Processo          | or Virtualization                                                 | 90 |

|        |       | 5.3.2.1           | Time Multiplexing                                                 | 90 |

|        |       | 5.3.2.2           | Binary Translation                                                | 91 |

|        | 5.3.3 | Memory            | Management                                                        | 92 |

|        |       | 5.3.3.1           | Shadow GDT/LDT (for implementation without hardware support)      | 92 |

|        |       | 5.3.3.2           | Shadow Page Tables (for implementation without nested paging)     | 93 |

|        |       | 5.3.3.3           | Shadow Nested Page Tables (for implementation with nested paging) | 95 |

|        |         | 5.3.3.4 ASID Remapping (for implementation with hardware support)  | . 9      |

|--------|---------|--------------------------------------------------------------------|----------|

|        | 5.3.4   | I/O Subsystem Virtualization                                       |          |

| 5.4    |         | lusion                                                             |          |

| Chapte | er 6. I | Interrupt and Exception Forwarding in x86 Recursive Virtualization | ı-<br>10 |

| 6.1    | Introd  | luction                                                            | . 10     |

|        | 6.1.1   | Motivation                                                         | . 10     |

|        | 6.1.2   | The Problem                                                        | . 10     |

|        | 6.1.3   | Our Contribution                                                   | . 10     |

| 6.2    | Desig   | n Issues                                                           | . 10     |

|        | 6.2.1   | Statically Determined Interrupt and Exception Handling Sequence    | . 10     |

|        | 6.2.2   | Forward Propagation                                                | . 10     |

|        | 6.2.3   | Reverse Propagation                                                | . 10     |

|        | 6.2.4   | Performance Measurement Methodology                                | . 10     |

| 6.3    | Imple   | ementation without Hardware Support                                | . 10     |

|        | 6.3.1   | Processor Operating Modes                                          | . 10     |

|        | 6.3.2   | Hypervisor IDTs and Shadow IDTs                                    | . 10     |

|        | 6.3.3   | Forward Propagation                                                | . 10     |

|        | 6.3.4   | Reverse Propagation                                                | . 11     |

|        | 6.3.5   | Interrupt-Enable Flag RFLAGS.IF Shadowing                          | . 11     |

|        | 6.3.6   | Running time Analysis                                              | . 11     |

| 6.4    | Imple   | ementation with Hardware Support for Single-Level Hypervisor       | 11       |

|        | 6.4.1   | Processor Operating Modes                                          | . 11     |

|        | 6.4.2   | Intercept Handling                                                 | . 11     |

|        | 6.4.3   | Running Time Analysis                                              | . 11     |

| 6.5    | Possil  | ble Hardware Extensions to Support Recursive Intercept Deliver     | y12      |

|        | 6.5.1   | Hardware Intercept Delivery                                        | . 12     |

|        |         | 6.5.1.1 Ancestor and Descendant Linked Lists                       | . 12     |

|        |         | 6.5.1.2 Intercept Redirect Bit                                     | . 12     |

|        |         | 6.5.1.3 The Hardware Algorithm                                     | . 12     |

|         |        | 6.5.1.4          | Running Time Analysis                                                      | 124 |

|---------|--------|------------------|----------------------------------------------------------------------------|-----|

|         | 6.5.2  | Avoid A          | valanche of Intercepts Cascading down the Hierarchy                        | 125 |

| 6.6     | Concl  | usion            |                                                                            | 126 |

| Chapte  | r 7. ( | Conclusio        | on                                                                         | 128 |

| 7.1     | Future | Work .           |                                                                            | 128 |

|         | 7.1.1  |                  | ctural Constraints to Real-Time Recursive Virtualiza-                      | 128 |

|         | 7.1.2  | Principl cursive | es for Adapting Any Architecture for Real-Time Re-<br>Virtualization       | 129 |

|         |        | 7.1.2.1          | Make the architecture virtualizable                                        | 130 |

|         |        | 7.1.2.2          | Make the architecture real-time capable                                    | 133 |

|         |        | 7.1.2.3          | Make the architecture recursively virtualizable in a real-time perspective | 134 |

| 7.2     | Concl  | usion            |                                                                            | 134 |

| Append  | lix    |                  |                                                                            | 137 |

| Append  | lix 1. | Acronyr          | ms                                                                         | 138 |

| Bibliog | raphy  |                  |                                                                            | 145 |

| Index   |        |                  |                                                                            | 153 |

| Vita    |        |                  |                                                                            | 166 |

# **List of Tables**

| 1.1 | Abstract resources and their real-life examples                                                                                                                                                                                                                                                                                     | 2   |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.1 | Combining nested page tables $(i=1,j>1,k=j+1 \text{ for paravirtual hierarchy}; i\geq 1, j=i+1, k>j \text{ for trap-and-emulate hierarchy})$                                                                                                                                                                                        | 95  |

| 5.2 | Mapping of combined nested page tables $(i=1,j>1,k=j+1)$ for paravirtual hierarchy; $i\geq 1, j=i+1,k>j$ for trap-and-emulate hierarchy; finally, $g_1P$ is the system physical address $sP$ ).                                                                                                                                     | 97  |

| 6.1 | Characterization for AMD Istanbul (family 10h) † ALU instructions include ADD, AND, CMP, OR, SUB, XOR, etc. ‡ <i>Round-trip world switch time</i> is measured as the combined time for a VMRUN instruction followed immediately by a #VMEXIT event that is triggered by an intercepted #GP exception in the first guest instruction | 106 |

| 6.2 | Shadow IDT and Hypervisor IDT Access Control Bits                                                                                                                                                                                                                                                                                   | 108 |

# **List of Figures**

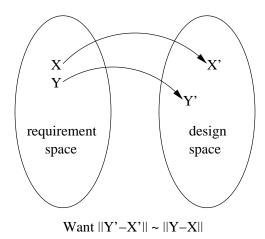

| 2.1  | Tracking Relation                                                                                                        | 10         |

|------|--------------------------------------------------------------------------------------------------------------------------|------------|

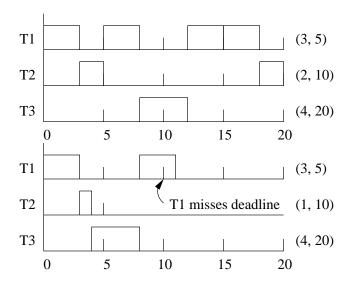

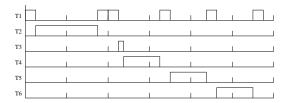

| 2.2  | Loss of Non-Preemptive Robustness under Decrease in Computation Time (Top=Before; Bottom=After)                          | 23         |

| 2.3  | Loss of Non-Preemptive Robustness under Increase in Period (Top=Bet Bottom=After)                                        | fore<br>24 |

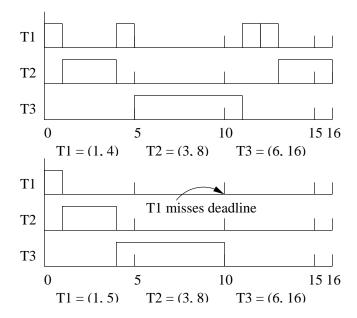

| 2.4  | Loss of Non-Preemptive Robustness under CPU Upgrade or CPU Overclock (Top=Before; Bottom=After)                          | 25         |

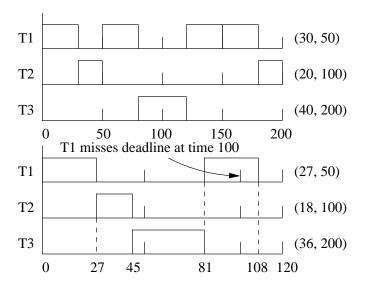

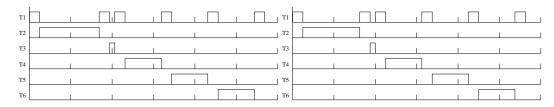

| 2.5  | NPFP/RMA and NPEDF are not robust against decrease in a computation time of $T_1$                                        | 26         |

| 2.6  | NPFP/RMA and NPEDF are not robust against decrease in a computation time of $T_2$                                        | 26         |

| 2.7  | NPFP/RMA and NPEDF are not robust against an increase in period of $T_1$                                                 | 27         |

| 2.8  | NPFP/RMA and NPEDF are not robust against CPU upgrade, $\alpha < 1.0$                                                    | 27         |

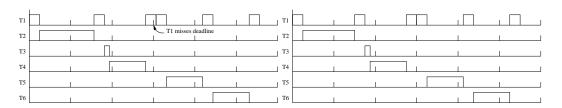

| 2.9  | Original task set is schedulable                                                                                         | 28         |

| 2.10 | $C_2' = \text{left: } C_2 - \frac{1}{2}\delta, \text{ right: } C_2 - \delta \ldots \ldots \ldots \ldots \ldots \ldots$   | 28         |

| 2.11 | $C_2' = \text{left: } C_2 - 1\frac{1}{2}\delta, \text{ right: } C_2 - 2\delta \ldots \ldots \ldots \ldots \ldots \ldots$ | 28         |

|      | $C_2' = \text{left: } C_2 - 2\frac{1}{2}\delta, \text{ right: } C_2 - 3\delta \ldots \ldots \ldots \ldots \ldots \ldots$ | 29         |

| 2.13 | $C_2' = \text{left: } C_2 - 3\frac{1}{2}\delta, \text{ right: } C_2 - 4\delta \ldots \ldots \ldots \ldots \ldots \ldots$ | 29         |

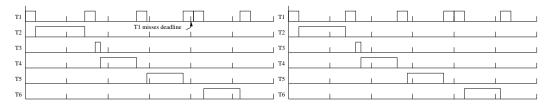

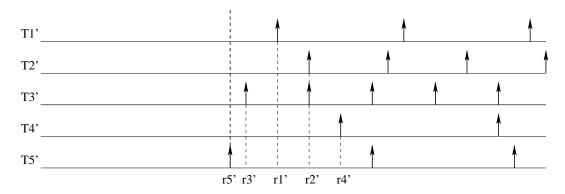

| 2.14 | First seven periods of $T_1$ in the example task set                                                                     | 35         |

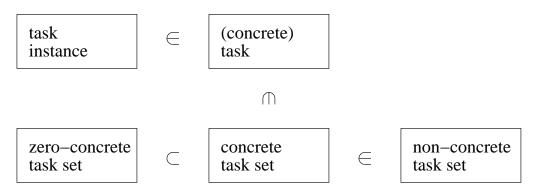

| 3.1  | Set relationship in our task model                                                                                       | 44         |

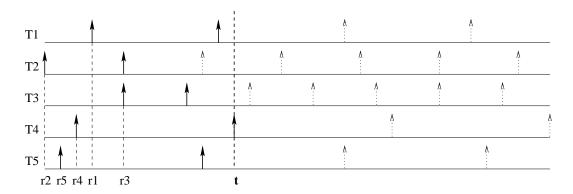

| 3.2  | Determination of $t$ from task set $T$                                                                                   | 50         |

| 3.3  | Construction of task set $T'$                                                                                            | 50         |

| 3.4  | Back to $\tau$ with arbitrary $r_i'$                                                                                     | 51         |

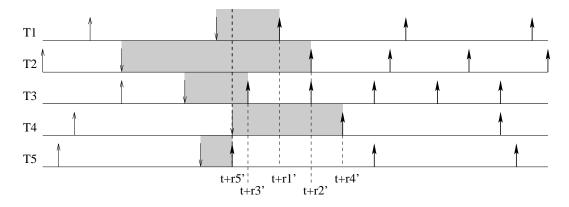

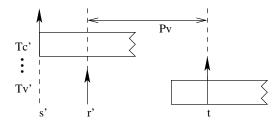

| 3.5  | Identification of time points $s'$ , $r'$ and $t$                                                                        | 53         |

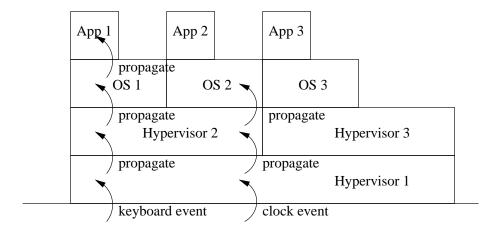

| 6.1  | Forward propagation                                                                                                      | 103        |

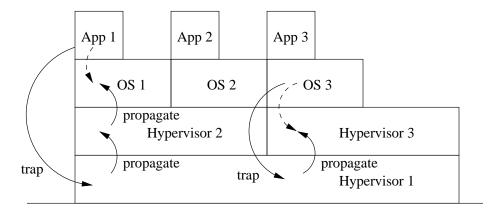

| 6.2  | Reverse propagation                                                                                                      | 04         |

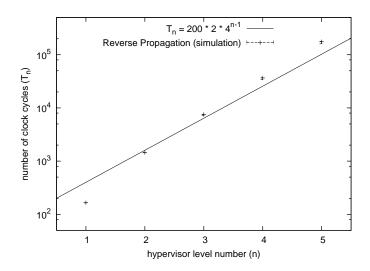

| 6.3 | Reverse propagation without hardware-assisted virtualization takes exponential time   |

|-----|---------------------------------------------------------------------------------------|

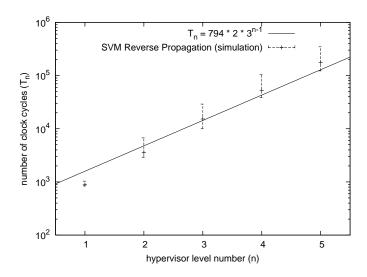

| 6.4 | Reverse propagation with hardware-assisted virtualization also takes exponential time |

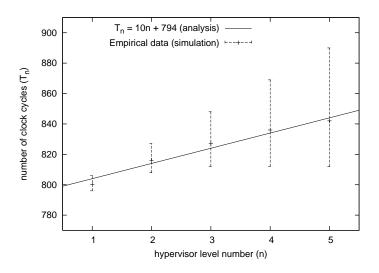

| 6.5 | Propagation with hardware extension takes linear time                                 |

# **Chapter 1**

### Introduction

The performance of computer systems has been growing exponentially according to Moore's Law. Most new servers have seen very low average utilization. Hence it is more economical to consolidate different servers into one physical machine to reap the benefits of its increased performance. However, running multiple servers in one physical system poses new security concerns. Another layer of system software called virtual machine monitor or hypervisor is used between the hardware and OS to provide isolation and fault containment. While the hypervisor solves part of the problem, it does not deliver the full power of the underlying hardware to its virtual machine partitions, hence real-time application may miss the deadline when running inside a hypervisor. We propose a real-time hypervisor that could be stacked up hierarchically to allow for arbitrarily complex security constraints to be implemented.

There are two challenges to this research, one is to make the hypervisor real-time capable, and the other is to make the hypervisor hierarchical capable. Sections 1.1 and 1.2 give an introduction and related known results to the real-time resource sharing problem. Chapters 2, 3 and 4 will cover our development to the real-time resource sharing issue. Section 1.3 gives introduction and related

works on the hierarchical virtualization problem, whereas chapters 5 and chapter 6 will cover our development to the x86 hierarchical virtualization issue. Finally, we conclude in chapter 7 with a summary of new results and a discussion of future possibilities.

#### 1.1 Abstract Resource Virtualization

Computing resources could be exclusively-owned, space-partitioned, timeshared or software-emulated. Examples of each type of resource are shown in table 1.1. We try to lay down a theoretical framework for the real-time aspects of resource virtualization by abstracting all computing resources.

| Exclusively Owned | Space Partitioned         | Time Shared                 | Software Emulated |

|-------------------|---------------------------|-----------------------------|-------------------|

| Floppy Disk Drive | Memory<br>Hard Disk Space | CPU<br>Hard Disk Controller | Virtual Ethernet  |

Table 1.1: Abstract resources and their real-life examples

Exclusively-owned and space-partitioned resources do not pose any realtime problems, because they are always available to their owner OS. Problems arise with time-shared or software-emulated resources because they may lengthen the critical path of execution and potentially induce a deadline miss which does not exist if running on a dedicated resource.

Timing properties of software-emulated resources could be obtained from Worst-Case Execution-Time (WCET) analysis. Puschner and Alan [43] have a detailed review of the available literature in WCET analysis that could be utilized.

Virtualization of time-shared resources could be fully-preemptable (e.g. processor), limited-preemptable (e.g. packet-switched network) or non-preemptable (e.g. printer).

Time sharing fully preemptiable resources has been well studied. We will quote some selected definitions and key results from the Bounded-Delay Resource Partition (BDRP) model in the next section. This related work is highly useful in real-time recursive virtualization for all fully preemptable resources. We will present our development on non-preemptable resources in the chapter 2 and chapter 3, followed by limited-preemptable resources and other variants in chapter 4.

#### 1.2 Time Sharing Fully Preemptable Resource

Mok et. al. [37] [36] have developed a complete framework for partitioning fully-preemptable resources so that each partition is capable of running real-time application. For the sake of easy reference, this section is a reproduction of their key definitions and results.

#### 1.2.1 The Bounded-Delay Resource Partition (BDRP) Model

In summary, each partition has two configurable parameters  $0 < \alpha \le 1$  and  $\Delta > 0$ .  $\alpha$  is the percentage of time we want to assign the resource to the partition, and  $\Delta$  is the maximum additional units of time a partition has to wait before it receives its full allocation  $\alpha(t_2-t_1)$  of the resource for any duration of time  $(t_2-t_1)$ . Based on this model, Feng et. al. has shown that any preemptive scheduling policy that works with a given task set under the reduced resource availability ( $\alpha$  of total),

with  $\Delta$  subtracted from all the deadlines, are guaranteed to continue to work on this partition.

**Definition 1.** A Periodic Resource Partition  $\Pi$  is a tuple  $(\Gamma, P)$ , where  $\Gamma$  is an array of N time pairs  $\{(S_1, E_1), (S_2, E_2), \dots, (S_N, E_N)\}$  that satisfies  $(0 \le S_1 < E_1 < S_2 < E_2 < \dots < S_N < E_N \le P)$  for some  $N \ge 1$ , and P is the partition period. The physical resource is available to a task set executing on this partition only during time intervals  $(S_i + j \times P, E_i + j \times P)$ , where  $1 \le i \le N, j \ge 0$ .

The above definition enumerates every time interval that is assigned to a partition and is a general representation of periodic partitioning schemes, including those that are generated dynamically by an on-line partition scheduler. We will build onto this definition and arrive at a more useful one in terms of real-time scheduling.

**Definition 2.** A Bounded Delay Resource Partition (BDRP)  $\Pi$  is a tuple  $(\alpha, \Delta)$  where  $\alpha$  is the percentage of total time the resource is available to the partition and  $\Delta$  is called the Partition Delay, which is the largest time deviation of a partition during any time interval with regards to a uniform uninterrupted allocate of the resource.

Note that this definition defines a set of partitions because there are many different partitions in the static partition model that may satisfy this requirement. It provides a starting point upon which other approaches of defining partitions will be considered in sections 4.3.2 and 4.4.

Thus the problem of scheduling a number of task sets on a given resource could be split into two steps:

- 1. Scheduling of the given resource into BDRPs

- 2. Scheduling of one task set on each of these BDRPs

We call the first one resource level scheduling, and the second one task level scheduling.

#### 1.2.1.1 Task Level Scheduling

**Theorem 3.** Given a task set  $\tau$  and a BDRP  $\Pi = (\alpha, \lambda_n)$ , let  $S_n$  denote a valid schedule of  $\tau$  on the normalized execution of  $\Pi$ ,  $S_p$  the schedule of  $\tau$  on Partition  $\Pi$  according to the same execution order and amount as  $S_n$ . Also let  $\lambda$  denote the largest amount of time such that any job on  $S_n$  is completed at least  $\lambda$  time before its deadline.  $S_p$  is a valid schedule if and only if  $\lambda \geq \lambda_n$ .

In Theorem 3,  $\lambda$  defines the maximum allowable output jitter [8] for  $S_n$ . Therefore, informally, Theorem 3 could be written as: A task set is schedulable on a partition if the maximum allowable output jitter is no less than the partition delay.

Theorem 3 provides a practical way to schedule a task set on a partition. If we could find a schedule on the normalized execution and the smallest  $\lambda$  is no less than  $\lambda_n$ , we could use this schedule on the partition and be guaranteed that no deadline will be missed on the partition. The schedule on the normalized execution is the same as the traditional task schedule, for which there are many known techniques.

#### 1.2.1.2 Recursive Resource Level Scheduling

In recursive virtualization, a partition group is scheduled within another partition. This is the more general problem of recursive resource level scheduling. When we schedule a partition group on a dedicated resource, we could consider the dedicated resource as a partition with  $\alpha=1$  and  $\Delta=0$ .

**Theorem 4.** A partition group  $\{\Pi_i(\alpha_i, \Delta_i)\}\ (1 < i \le n)$  is schedulable on a partition  $\Pi(\alpha, \Delta)$  if  $\sum_{i=1}^n \alpha_i \le \alpha$  and  $\Delta_i > \Delta$  for all i,  $(1 < i \le n)$ .

Theorem 4 provides a method to determine the schedulability of scheduling partitions (a partition group) on another partition. However, it does not explain how to perform the actual scheduling since the infinite time slice scheme that is used in the proof is impractical. Therefore, the question remains how to schedule partitions using methods with finite context switch overhead.

**Theorem 5.** Given a partition group  $\{\Pi_i(\alpha_i, \Delta_i)\}\ (1 < i \le n)$  to be scheduled on a partition  $\Pi(\alpha, \Delta)$ . Let  $S_n$  denote a scheduler of scheduling  $\Pi'_i(\alpha_i/\alpha, \Delta_i - \Delta)$   $(1 < i \le n)$  on a dedicated resource with capacity of the same as the normalized execution of  $\Pi$ . Also let  $S_p$  denote the virtual time  $S_n$  scheduler of scheduling  $\Pi_i$  on  $\Pi$ . Then  $S_p$  is valid if  $S_n$  is valid.

Theorem 5 justifies the observation that we may use essentially the same algorithms of scheduling partitions on dedicated resources for hierarchical partitioning by applying the virtual time scheduling scheme.

With the ability of scheduling a partition inside another partition, we could build a hierarchy of resource partitions for fully-preemptable resources.

Chapter 2 continues with an anomaly we discovered in non-preemptive scheduling. We call this the robustness problem. It is being rigorously defined and formally analyzed. Then in chapter 3, we propose necessary and sufficient conditions to ensure non-preemptive robustness. Finally, this new result is combined with the BDRP model in chapter 4, together with new lights on limited-preemptive scheduling and other types of scheduling constraints.

#### 1.3 The x86 Recursive Virtualization

The x86 architecture is chosen because it is popular and readily available. The abstract theory in resource virtualization discussed in section 1.2, chapter 2, chapter 3 and chapter 4 finds its application in a real-life scenario.

Before the advent of the Intel VT-x [27] and AMD SVM technology [4], the x86 architecture is not known to be virtualizable [42] [44]. Known problems include, but are not limited to, ring aliasing, ring compression, address space compression, non-faulting access to privileged state, high overhead in interrupt virtualization, and lack of access to processor hidden states.

The advent of hardware-assisted virtualization addressed these issues [50] but some of them would re-appear if we proceed to recursive virtualization. For example, the hardware-assisted virtualization solved the ring aliasing problem by essentially creating an extra set of rings for the hypervisor, known as the root mode operation. When we do recursive virtualization, the guest hypervisor has to be run in non-root mode although it was designed to be run in root mode. Instead of ring aliasing, we may call this mode aliasing problem. Basically, the outer hypervisor

has to trap all root mode operations and emulate them sacrificing performance.

Although the hardware-assisted virtualization is very handy to use, we do not take it for granted as the only possible form of virtualization in our discussion. In each aspect of recursive virtualization, we presented the case when hardware-assisted virtualization is not available, when it is available, and when the hardware could be extended to do better. Chapter 5 integrates the abstract theories of resource virtualization in the context of the x86 architecture. Then chapter 6 deals with one specific problem that affects real-time workloads the most, namely, the recursive forwarding and delivery of interrupts, exceptions and intercepts. These chapters dive into a lot of the x86 technicalities. Readers are referred to appendix 1 for a list of the acronyms used.

Finally, we give an architecture-independent view of how real-time recursive virtualization might be achieved in chapter 7. This is useful in real-time recursively virtualizing non-x86 architecture, or designing new architecture specifically for use with real-time recursive virtualization.

# Chapter 2

# Non-Preemptive Robustness - Definition and Characterization

Unlike preemptive scheduling policies, non-preemptive real-time scheduling policies can exhibit anomalies even for the single-processor case. In particular, a task set that is schedulable by a non-preemptive scheduler may become unschedulable when the utilization of the task set decreases relative to the CPU speed, e.g., when a faster CPU is used to run the same task set. In this chapter, we define the notion of *robustness* to capture the essence of the scheduling anomaly on real-time system performance. We shall show that it is difficult to test for robustness in general but it could still be characterized. In chapter 3, we shall derive necessary and sufficient conditions for guaranteeing non-preemptive robustness.

#### 2.1 Introduction

One problem in engineering large complex software systems is the sensitivity of a design to changes in the requirements. If we view each step of the design process as a mapping from a requirement space to an (abstract) design space, the sensitivity problem may be viewed as a relation. Let us call it the *tracking relation* between a *difference metric* in the requirements space and a corresponding differ-

ence metric induced in the design space. These difference metrics are appropriately defined to measure the magnitude of change within their respective space.

Some properties of the tracking relation are obviously desirable. For example, it should preserve *locality*: differences confined to a locality in the requirements space should induce differences confined to a locality in the design space, and *scalability*: a small difference in the requirements space should induce a small difference in the design space.

Of course, how a difference metric is defined should reflect the aspect of requirements captured under consideration. For example, the difference metric meant to capture locality in the requirements space may reflect the number of functionalities / components that are affected by a change in the requirement, and the difference metric meant to capture the scalability in the requirements space may reflect the increase in system load in a requirements change. The idea of tracking relation is illustrated in figure 2.1.

Figure 2.1: Tracking Relation

In the following, we shall illustrate the tracking relation concept by considering a specific aspect of real-time systems design, specifically, the relation between a change in the real-time performance requirements and the schedulability of the design solution. Intuitively, if we make the real-time performance requirement of an application less stringent, we should expect the design solution to require at most the same amount of computing resources. A mapping from requirement to design is *robust* if a less demanding requirement will not cause a performance failure in the design.

We believe that the notion of robustness will be important as long as CPU speed keeps on improving at a faster rate than memory I/O bandwidth (including L1, L2 and L3 caches). This is because the *worst-case* cost of preempting a task includes flushing caches, instruction pipelines and page tables all of which may incur I/O operations. Therefore unless all real-time tasks can be kept in fast memory all the time, the cost of preemption will be significant compared with task execution time.

#### 2.1.1 Requirements Space - Periodic Task Set

The requirements space is the set of periodic tasks. A periodic task is characterized by a pair:  $T_i = (C_i, P_i)$ , where each service request of  $T_i$  requires  $C_i$  units of CPU time to satisfy and two successive requests must be separated by  $P_i$  time units. Suppose M is a set of n periodic tasks  $\{(C_1, P_1), \ldots, (C_n, P_n)\}$  where  $C_i$ ,  $P_i$  are respectively the computation time and the period for periodic task  $T_i$ . The first instance of all tasks in M arrive together at time 0.

#### 2.1.2 Design - Priority Assignment

A design is a (fixed or dynamic) priority assignment to the tasks in the periodic task set. A Fixed-Priority (FP) scheduler or an Earliest-Deadline-First (EDF) scheduler is used to schedule tasks in M. An FP scheduler always selects for execution the task that has the highest priority. With Rate Monotonic Assignment (RMA) of priority, task  $T_i$  having a higher priority than task  $T_j$  implies  $P_i \leq P_j$ . We shall adopt the convention for FP scheduler that task  $T_i$  is assigned a higher priority than task  $T_j$  iff i < j. An EDF scheduler always selects for execution the task whose deadline is the nearest, hence the task priorities for EDF scheduler are dynamic, and change over time.

In this chapter, we talk about schedules for task set M that are produced by a Preemptive FP (PFP) scheduler, Non-Preemptive FP with RMA priority (NPFP/RMA) scheduler, Preemptive EDF (PEDF) scheduler and Non-Preemptive EDF (NPEDF) scheduler. We call these schedules the PFP schedules, NPFP/RMA schedules, PEDF schedules and NPEDF schedules respectively.

|        | Preemptive | Non-Preemptive |

|--------|------------|----------------|

| EDF    | PEDF       | NPEDF          |

| FP     | PFP        | NPFP           |

| /w RMA | PFP/RMA    | NPFP/RMA       |

In general, FP/RMA and EDF produce different schedules (e.g. consider the task set  $\{(2,3),(1,5),(1,8)\}$ ), but in order to save space, throughout the chapter, counter-examples are carefully chosen so that both EDF and FP/RMA have the same schedule.

A scheduler first computes an initial schedule or priority assignment based on the requirements specification of each task either statically (computed offline) or as part of the admission control process (computed online). Then a run-time dispatcher selects task instances for execution based completely or partially on the priority assignment information provided by the scheduler.

#### 2.1.3 Requirement Change - Reduction in System Load

A (favorable) change in the requirements space is characterized by a reduction in system load, which is defined to be one or more of the following:

- Decrease in computation time of some task(s)

- Increase in period of some task(s)

- CPU upgrade, i.e. the use of a faster processor or CPU overclock

In particular, (3) is a special case of (1), where the computation time of all tasks are decreased by the same ratio. Also, deletion of a task is also a special case of (1) and (2), where the computation time becomes 0 and period becomes  $\infty$ . Note that we do not talk about scaling up resource nor increased workload in this dissertation (this is because in most of our target applications, e.g., mission critical embedded systems, an upgrade is often forced by the need for additional system functionality, and at best, you end up with the same if not greater system load).

We denote the task set after reduction in system load by M', and its constituent tasks  $T'_i = (C'_i, P'_i)$ , obeying the relations  $C'_i \leq C_i$  and  $P'_i \geq P_i$ , with at least one inequality over all tasks being strictly less than (<).

There are two possibilities for reduction in system load, advertised and unadvertised. An advertised reduction in system load for a task means the actual values of  $(C'_i, P'_i)$  are made known to the run-time dispatcher prior to the arrival of the first instance of the task. Unadvertised reduction means the run-time dispatcher is never informed of any such changes. If the system load reduction is advertised, the scheduler could spend some time computing the optimal schedule; but the unadvertised ones are more common and do more harm. The unadvertised increase in period also represents a transitional model from periodic task to sporadic task.

#### 2.1.4 Robustness

When there is a reduction in system load, we would normally expect the same design to work. In other words, a priority assignment that results in a task set being schedulable should preserve schedulability under reduction in system load. We say that a priority assignment is robust if schedulability is preserved in any reduction of system load. Robustness depends on the scheduling policy and type of timing constraints imposed on the system.

One of the hard problems in maintaining real-time systems requirements in mobile computing is to keep track of the impact of resource usage on the applications. Due to power consideration, CPU in mobile computing is often clocked at a range of frequencies, and adjusted at run time according to need. Often times, it is not sufficient to keep track of only the upper bounds on resource usage, since some requirements such as jitter are also sensitive to the lower bounds and the resource scheduling algorithm employed.

#### 2.1.5 Preemptiveness vs Non-preemptiveness

Because of the NP-completeness of non-preemptive deadline scheduling [28], most extant work is about preemptive scheduling. However, non-preemptive scheduling is worth studying for a number of reasons, especially for resources that are inherently non-preemptable or when preemption cost is high.

Nowadays, processors are much faster, so jobs are much shorter. As processors are more pipelined, context switch overheads become relatively high. We want to resort to non-preemptive policies in an attempt to cut down this context switch overhead.

Also, in communication networks, synchronization and packet header processing overhead is relatively large. In order to deliver most of the available bandwidth to the end-user, batch processing of packets and messages is favored, thus limiting preemption.

Moreover, in open systems environment like mobile computing, we want non-interference among partitions, and jobs should not be preempted by other partitions. So it also necessitates the use of non-preemptive schedules.

#### 2.1.6 Some Definitions and Notations

The  $p^{th}$  instance of a task  $T_i$  is denoted by  $T_i^p$ . Suppose r is the request for  $T_i^p$  that occurs at time t in a schedule s. Then the response time of r is defined to be t'-t where t' is the time at which r is satisfied by the completion of  $T_i^p$  in s. Given a priority assignment, a task is schedulable if and only if all of its requests have

response time no bigger than its period in the schedule. A task set is schedulable if every task in the set is schedulable.

A task  $T_i$  has no outstanding computation at time t if all the requests for  $T_i$  that arrived before t were satisfied by time t. A task set M does not have outstanding computation at time t if all the tasks inside M have no outstanding computation at time t. Time t is the time of the first request arrival, so by definition, it is a time of no outstanding computation.

#### 2.1.7 Related Works

Scheduling anomalies have been known since [24]. Previous results pertain mostly to multiprocessor and list scheduling anomalies. The results reported in this dissertation pertain to real-time uniprocessor scheduling. The multiprocessor anomaly reported in previous work depends on processor assignment anomaly and do not apply to the uniprocessor case.

As far as we know, the definition of robustness in the sense of freedom from anomalies was first proposed by Mok in an invited lecture at both the NSF/ARO/CNR-Italy Workshop on Modelling Software System Structures and the 7th International Conference on Real-Time Computing Systems and Applications in 2000 (http://www.informatik.uni-trier.de/~ley/db/conf/rtcsa/rtcsa2000.html). This and the next chapters contains results that answer some open problems proposed by Mok.

In [12], Buttazzo used Cyclical Asynchronous Buffers to avoid blocking on shared resources to avoid anomalies. However, the use of their approach is mainly limited to control applications, e.g. sensory acquisition task, because in their model, messages could be lost or read more than once. Their Rate Adaptation scheme works for processor overload, not reduced system load. In [10], Brandt et al showed that PEDF scheduling is anomaly-free. In [46], Sha eta al showed that RMA scheduling is anomaly-free under load reduction. Introduction to the general area includes [32], [47], [29] and [33]. Other related works include [28] and [52].

## 2.2 Robustness of Preemptive Schedulers

The schedulability problem for preemptive schedulers was first discussed in Liu & Layland [32]. We shall assume that time is discrete and all timing parameters are integers. Only slight modification is needed for the discussion below to apply to continuous time.

In each of the following sections, we are going to consider decrease in computation time and increase in period separately. In particular, we also highlight reduction in system load due to CPU upgrade, which is just a special case of decrease in computation time.

For the sake of clarity in proofs, we define an intermediate task set M'', whose constituent tasks  $T_i'' = (C_i', P_i)$  have the same period  $P_i$  as the original task set  $T_i$  (hence the same priorities no matter if we use FP/RMA or EDF), yet with the decreased computation time  $C_i'$  as in T'.

A scheduling policy which is robust separately under both decrease in computation time and increase in period is also robust under any reduction in system load, because any reduction in system load could be represented as a combination of these two factors. Given that a task set M is schedulable under the policy concerned, the intermediate task set M'' is also schedulable because the policy is robust under decrease in computation time. Given M'' is schedulable, our target task set M' is also schedulable because the policy is robust under increase in period. Hence by transitivity, schedulability is preserved by this scheduling policy when system load is reduced from M to M'.

#### 2.2.1 Preemptive Earliest-Deadline-First (PEDF)

By the Liu & Layland Model [32], a task set is schedulable by PEDF scheduling policy iff  $\sum_{j=1}^{n} \frac{C_j}{P_j} \le 1$

For decrease in computation time of some task  $C_k$  by  $\delta$   $(1 \le k \le n, \delta > 0)$ ,

$$\sum_{j=1}^{n} \frac{C'_{j}}{P'_{j}} = \left(\sum_{j=1}^{n} \frac{C_{j}}{P_{j}}\right) - \frac{\delta}{P_{k}} < \sum_{j=1}^{n} \frac{C_{j}}{P_{j}} \le 1$$

For increase in period of some task  $P_k$  by  $\delta$   $(1 \le k \le n, \delta > 0)$ ,

$$\sum_{j=1}^{n} \frac{C'_{j}}{P'_{j}} = \left(\sum_{j=1}^{n} \frac{C_{j}}{P_{j}}\right) - \left(\frac{C_{k}}{P_{k}} - \frac{C_{k}}{P_{k} + \delta}\right) < \sum_{j=1}^{n} \frac{C_{j}}{P_{j}} \le 1$$

(Note that this proof assumes that job priorities may change after period increase when the deadlines cross).

For CPU upgrade, where we reduce the computation time of all tasks by the same proportion  $\alpha$  (0 <  $\alpha$  < 1),

$$\sum_{j=1}^{n} \frac{C_j'}{P_j'} = \sum_{j=1}^{n} \frac{(1-\alpha) \cdot C_j}{P_j} < \sum_{j=1}^{n} \frac{C_j}{P_j} \le 1$$

Under any reduction in system load, the utilization factor

$$\sum_{j=1}^{n} \frac{C'_{j}}{P'_{j}} < \sum_{j=1}^{n} \frac{C_{j}}{P_{j}} \le 1$$

remains smaller than 1. Hence the task set remains schedulable under PEDF scheduling policy. In order words, the PEDF scheduling policy is robust. (Note that this proof assumes that job priorities may change after period increase when the deadlines cross).

#### 2.2.2 Preemptive Fixed-Priority (PFP)

By the Liu & Layland Model [32], a task set is schedulable by the PFP scheduling policy iff

$$\forall i (1 \le i \le n), \exists t_i \in (0, P_i], \sum_{j=1}^i C_j \cdot \left\lceil \frac{t_i}{P_j} \right\rceil \le t_i$$

Since the task set M is schedulable at first, we have a set of values  $t_1, t_2, \ldots, t_n$  satisfying the above inequality. After reduction in system load, we want to find  $t'_1, t'_2, \ldots, t'_n$  satisfying:

$$\forall i (1 \le i \le n), t_i' \in (0, P_i'] \land \sum_{j=1}^i C_j' \cdot \left\lceil \frac{t_i'}{P_j'} \right\rceil \le t_i'$$

For decrease in computation time of some task  $C_k$  by  $\delta$   $(1 \le k \le n, \delta > 0)$ , then  $\forall i \ (k \le i \le n, \delta)$  otherwise task  $T_k$  has no effect on the summation, which is

only to i), we take  $t'_i = t_i \in (0, P_i] = (0, P'_i]$

$$\sum_{j=1}^{i} C'_{j} \cdot \left\lceil \frac{t'_{i}}{P'_{j}} \right\rceil = \left( \sum_{j=1}^{i} C_{j} \cdot \left\lceil \frac{t_{i}}{P_{j}} \right\rceil \right) - \delta \cdot \left\lceil \frac{t_{i}}{P_{k}} \right\rceil$$

$$< \sum_{j=1}^{i} C_{j} \cdot \left\lceil \frac{t_{i}}{P_{j}} \right\rceil$$

$$\leq t_{i}$$

$$= t'_{i}$$

For increase in period of some task  $P_k$  by  $\delta$   $(1 \le k \le n, \delta > 0)$ , we first consider when job priorities do not change:  $\forall i \ (k \le i \le n, \text{ otherwise task } T_k \text{ has no effect on the summation, which is only to } i)$ , take  $t_i' = t_i \in (0, P_i] \subset (0, P_i']$ , then

$$\sum_{j=1}^{i} C'_{j} \cdot \left\lceil \frac{t'_{i}}{P'_{j}} \right\rceil = \left( \sum_{j=1}^{i} C_{j} \cdot \left\lceil \frac{t_{i}}{P_{j}} \right\rceil \right) - C_{k} \cdot \left( \left\lceil \frac{t_{i}}{P_{k}} \right\rceil - \left\lceil \frac{t_{i}}{P_{k} + \delta} \right\rceil \right)$$

$$< \sum_{j=1}^{i} C_{j} \cdot \left\lceil \frac{t_{i}}{P_{j}} \right\rceil$$

$$\leq t_{i}$$

$$= t'_{i}$$

Hence in both cases, the inequality still holds.

If the period increase is advertised, we may change the RMA priorities accordingly. If it is unadvertised (which makes the periodic task begins to look like a sporadic task), the RMA priorities remain unchanged. We have shown that PFP is robust in general when priorities do not change, hence unadvertised PFP/RMA is robust with respect to increase in period.

Consider next advertised PFP/RMA. If the deadlines do cross when the periods increase, we introduce a series of intermediate reduced task sets  $M^{(0)}, M^{(1)}, \ldots, M^{(m+1)}$ , where  $M^{(0)} = M$ ,  $M^{(m+1)} = M'$ , and m is the number of swappings needed for bubble sort to sort the task sets from their original priority arrangement to the new one.

The intermediate reduced task sets are constructed as follows. Start with  $M^{(i)},\,M^{(i+1)}$  is obtained by picking the task  $T^{(i)}_{\tau}$  with the lowest final priority (in M') whose period  $P^{(i)}_{\tau} \neq P'_{\tau}$  and stretch it until either (1)  $P^{(i+1)}_{\tau} = P'_{\tau}$  or (2) it hits the period of another task  $T^{(i)}_{\mu}$  so that  $P^{(i)}_{\tau} < P^{(i+1)}_{\tau} = P^{(i)}_{\mu} < P'_{\tau}$ , whichever is earlier. Repeatedly pick a task this way and stretch its period until there are no more such tasks to pick, then the resulting task set is  $M^{(i+1)}$ .

It is easy to show that  $M^{(m+1)}=M'$  based on an analogy with bubble sort. When system load is reduced from  $M^{(i)}$  to  $M^{(i+1)}$ , task priorities are not changed, so our previous proof holds. Within  $M^{(i+1)}$ , swapping the priority of tasks  $T^{(i+1)}_{\tau}$  and  $T^{(i+1)}_{\mu}$  does not affect the schedulability of the task set because the periods of these two tasks are the same, i.e.  $P^{(i+1)}_{\tau}=P^{(i+1)}_{\mu}$ . Continuing this way, we see that M' remains schedulable for PFP/RMA even when the RMA priority changes after reduction in system load.

CPU upgrade or overclock is a special case of decrease in computation time. We provide the proof here for completeness. Here, the computation times of all tasks are reduced by the same ratio  $\alpha < 1$ . Take  $t_i' = t_i$ , then  $\forall i (1 \le i \le n)$ ,

$$t'_i = t_i \in (0, P_i] = (0, P'_i]$$

and

$$\sum_{j=1}^{i} C'_{j} \cdot \left\lceil \frac{t'_{i}}{P'_{j}} \right\rceil = \sum_{j=1}^{i} (1 - \alpha) \cdot C_{j} \cdot \left\lceil \frac{t_{i}}{P_{j}} \right\rceil$$

$$< \sum_{j=1}^{i} C_{j} \cdot \left\lceil \frac{t_{i}}{P_{j}} \right\rceil$$

$$\leq t_{i}$$

$$= t'_{i}$$

In any case, there exists  $t_i'$  satisfying the inequality after reduction in system load. Hence the task set remains schedulable under PFP scheduling policy. In other words, the PFP scheduling policy is robust.

## 2.3 Loss of Robustness in Non-preemptive Schedulers

Neither NPEDF nor NPFP/RMA scheduling policy is robust. In general, an anomaly may occur for any non-preemptive, eager scheduler which does not idle the CPU as long as there is a ready task.

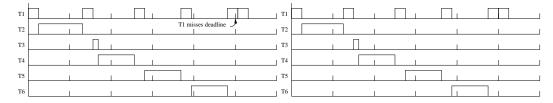

- Decrease in Computation Time: Task set  $\{T_1 = (3,5), T_2 = (2,10), T_3 = (4,20)\}$  is schedulable by an NPFP/RMA or an NPEDF scheduler. But it becomes unschedulable if we reduce the execution time of  $T_2$  from 2 to 1. (figure 2.2)

- Increase in Period: Task set  $\{T_1 = (1,4), T_2 = (3,8), T_3 = (6,16)\}$  is schedulable by an NPFP/RMA or an NPEDF scheduler. But it becomes unschedulable if we increase the period of  $T_1$  from 4 to 5. (figure 2.3)

Figure 2.2: Loss of Non-Preemptive Robustness under Decrease in Computation Time (Top=Before; Bottom=After)

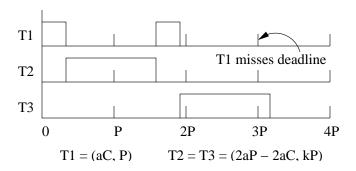

• CPU Upgrade or Overclock: Task set  $\{T_1 = (30, 50), T_2 = (20, 100), T_3 = (40, 200)\}$  is schedulable by an NPFP/RMA or an NPEDF scheduler. But it becomes unschedulable if we reduce the execution times of all tasks by 10%. (figure 2.4)

Hence, the above counter-examples establish:

**Theorem 6.** Neither the NPFP/RMA scheduler nor the NPEDF scheduler is robust with respect to any reduction in system load.

# 2.4 How Bad is the Non-Preemptive Robustness Problem

The robustness problem occurs regardless of the CPU utilization factor, regardless of the number of different job sizes (length of job periods), and the problem

Figure 2.3: Loss of Non-Preemptive Robustness under Increase in Period (Top=Before; Bottom=After)

could not be solved by testing a finite number of workload reduction cases.

**Theorem 7.** The loss of robustness for NPFP/RMA and NPEDF schedule exists even when the utilization factor of the task set tends to zero.

*Proof:* A scenario suffices to demonstrate the fact here. For any given positive number  $\epsilon$ , we construct a task set whose utilization factor  $U < \epsilon$ , yet neither NPFP/RMA nor NPEDF schedule is robust on it.

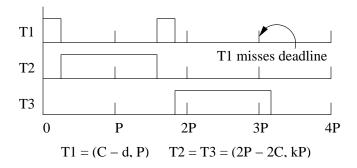

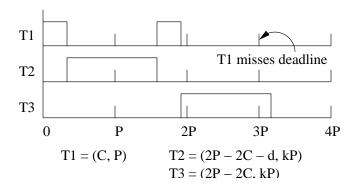

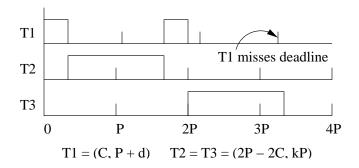

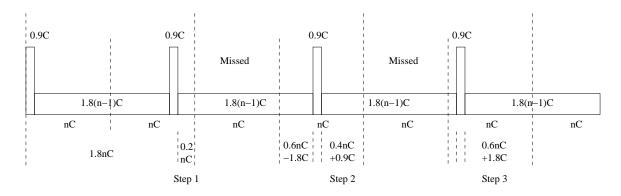

Consider the task set  $\{T_1=(C,P),\,T_2=T_3=(2P-2C,kP)\}$ , where  $k\geq 4$  is an integer. The NPFP/RMA and NPEDF schedules are not robust for this task set under any reduction in system laod. In figures 2.5 2.6 2.7 2.8, it causes  $T_1$  to miss the deadline in the third period.

Figure 2.4: Loss of Non-Preemptive Robustness under CPU Upgrade or CPU Overclock (Top=Before; Bottom=After)

For this parameterized task set, take  $k>\max(4,\frac{4}{\epsilon})$  and  $P>\frac{(k-4)C}{\epsilon k-4}$ , then we have utilization factor  $U<\epsilon$ . Hence when  $\epsilon\to 0$ , we have  $k\to\infty$  and  $P\to\infty$ , utilization factor  $U\to 0$ , but task  $T_1$  misses its deadline on the third period, so the anomaly still exists even when the utilization factor  $U\to 0$ .

**Corollary 8.** Restricting job sizes (length of job periods) to a selected set won't avoid anomalies as long as there are more than one job size.

*Proof:* The same example from theorem 7 shows that anomaly can occur when there are as few as only two job sizes. Restricting job sizes to harmonics won't help either, as illustrated in the scenario above.

Moreover, testing cannot solve the anomaly problem because no testing can detect all problems.

Figure 2.5: NPFP/RMA and NPEDF are not robust against decrease in a computation time of  $T_1$

Figure 2.6: NPFP/RMA and NPEDF are not robust against decrease in a computation time of  $\mathcal{T}_2$

We will illustrate this with decrease in computation time. A good testing approach may go like this: For each task, try to decrease its computation time by a fixed factor  $\delta$  each time and see if the anomaly occurs. If no anomaly occurs at all such testing points, we assume that the task set does not exhibit anomaly behavior for the scheduling policy concerned.

However, for any real-valued  $\delta$  chosen, we can construct a task set such that it remains schedulable at all the testing points but shows anomalies in-between testing points:

Figure 2.7: NPFP/RMA and NPEDF are not robust against an increase in period of  $T_1$

Figure 2.8: NPFP/RMA and NPEDF are not robust against CPU upgrade,  $\alpha < 1.0$

$$\begin{vmatrix} T_1 & (2\delta, P) \\ T_2 & (2P - 4\delta, kP) \\ T_3 & (\delta, kP) \\ T_4 & (P - \delta, kP) \\ \vdots & \vdots \\ T_n & (P - \delta, kP) \end{vmatrix}$$

where  $P \ge n\delta$  and is an even multiple of  $\delta$ , integers  $k \ge n$  and  $n \ge 4$ . This task set is schedulable by both NPFP/RMA and NPEDF scheduler (figure 2.9).

As shown in figures 2.10 to 2.13, whenever the computation time of  $T_2$  is decreased by integral multiples of  $\delta$ , the task set remains schedulable, but it may not be so when the computation time of  $T_2$  is decreased by a non-integral multiple of

Figure 2.9: Original task set is schedulable

Figure 2.10:  $C_2' = \text{left: } C_2 - \frac{1}{2}\delta$ , right:  $C_2 - \delta$

$\delta$ . In particular, the task set is not schedulable when the computation time of  $T_2$  is decreased by  $(m+\frac{1}{2})\delta$  and  $(\frac{P}{\delta}-2+m+\frac{1}{2})\delta$ ,  $\forall m:1\leq m\leq n-3$ . Notice that even though an anomaly may not occur when the change in requirements specification tends to zero, it may still occur later.

**Theorem 9.** There can be an infinite number of regions where an anomaly occurs.

*Proof:* Consider the same parameterized task set we just constructed; for any positive integer m, we can choose n=m+3 to achieve 2m number of anomalous regions. As  $m\to\infty$ ,  $n\to\infty$ .

Figure 2.11:  $C_2' = \text{left: } C_2 - 1\frac{1}{2}\delta$ , right:  $C_2 - 2\delta$

Figure 2.12:  $C_2' = \text{left: } C_2 - 2\frac{1}{2}\delta$ , right:  $C_2 - 3\delta$

Figure 2.13:  $C_2' = \text{left: } C_2 - 3\frac{1}{2}\delta$ , right:  $C_2 - 4\delta$

# 2.5 Properties of Non-preemptive Anomaly

In order to tackle the problem of non-preemptive scheduling robustness, we first gather a set of useful properties of non-preemptive scheduling.

**Lemma 10.** For both NPFP/RMA and NPEDF, if the only kind of reduction in system load allowed is decrease in computation time, then the lowest priority task  $T_n$  will not miss its deadline.

*Proof:* We will show that all instances of the task  $T_n$  would start no later than their respective start time in the original schedule.

Consider an arbitrary instance  $T_n^p$  of the task  $T_n$ . Let r be its request time, t be its start time and let t' be the latest time before t with no outstanding computation. Notice that t' remains a time of no outstanding computation under any decrease in computation time, because no task execution could cross t' under decrease in

computation time. Tasks before t' could not cross because their computation time can only shrink but not expand to cross t'; tasks executed after t' cannot start earlier than their request time so they cannot cross t' too.

The number of requests for each task within the interval [t',t) remains unchanged under reduction in system load, because the period is not changed. After reduction in system load, the total computation in the interval [t',t) (excluding the task instance  $T_n^p$ ) is decreased, hence the CPU must be idle during some time in this interval. Let the end of the last idle interval thus generated be t''. If  $r \leq t'' < t$ , then  $T_n^p$  starts earlier; otherwise, the total computation within the interval [t'',t) is not greater than before, so  $T_n^p$  starts no later than before. Hence  $T_n^p$  will not miss its deadline.

For NPFP/RMA, observe that the start times of all instances of the lowest priority task  $T_n$  in a task set is the same no matter if we use preemptive or non-preemptive scheduling, it is natural to think that the critical instant of the lowest priority task  $T_n$  also occurs when the request for all tasks align at the same time. We will prove it formally in the following lemma. Note that this lemma is a study of the non-preemptive scheduling in general, and has nothing to do with reduction in system load.

**Lemma 11.** For NPFP/RMA, the lowest priority task  $T_n$  has the longest response time when the request for all tasks align at the same time.

*Proof:* Suppose the contrary is true that the lowest priority task  $T_n$  has the longest response time when the request for a certain task instance  $T_i^p$  is not aligned

with that of  $T_n^q$ . Let  $r_p$  be the request time of  $T_i^p$  and  $r_q$  be that of  $T_n^q$ . Without loss of generality, let  $r_p < r_q$  (in the case that the start time of  $T_i^1$  is later than  $r_q$ , we let p = 0, and  $T_i^0$  be a dummy instance which has no outstanding computation during its whole period). We consider the following cases:

If  $T_i^p$  still has outstanding computation at time  $r_q$ , or the CPU is busy between the completion time of  $T_i^p$  and  $r_q$ , then we move the request time of  $T_n^q$  to align with  $r_p$ . Doing so would not change the start time nor completion time of any task, yet the response time for  $T_n^q$  is increased, which is a contradiction.

Otherwise we consider the next instance  $T_i^{p+1}$ , and move its request time to align with  $r_q$  (and move all subsequent request times of  $T_i$  by the same amount too). This way, the number of requests of  $T_i$  during the period of  $T_n^q$  is not less than before, so the response time for  $T_n^q$  is at least as much as before.

So, the lowest priority task  $T_n$  has the longest response time when the request for all tasks align at the same time.

If a task meets its deadline when it has the longest response time, then it meets all deadlines. This is traditionally called the critical instant test.

**Corollary 12.** For NPFP/RMA, when the first request for all tasks arrive together, if the only kind of reduction in system load allowed is increase in period, then the lowest priority task  $T_n$  will not miss its deadline.

*Proof:* Special case 1:  $T_n$  is the only task whose period is increased, the completion time for the first instance of  $T_n$  remains unchanged but its deadline is extended, so  $T_n$  would still pass its critical instant test. Special case 2: The period of

$T_n$  remains unchanged, then during the first period of  $T_n$ , the number of requests for higher priority tasks decreases (because some or all of their periods have increased), so the response time for  $T_n^1$  is less than or equal to before, hence  $T_n$  still meets the critical instant test.

General case: The period of  $T_n$  and one or more other tasks are increased, we consider an intermediate task set in which only the period of  $T_n$  is increased. By transitivity of the above two cases,  $T_n$  still passes its critical instant test. Hence in any case,  $T_n$  will not miss its deadline.

Notice that the proof is true for  $T_n$  even if the period of some other task  $T_x$  increases to beyond that of  $T_n$ , i.e.  $P'_x > P'_n$ . Hence corollary 12 is valid for both advertised and unadvertised period increase, or in other words, valid no matter if the RMA priorities are re-adjusted accordingly or not after period increase.

**Theorem 13.** For NPFP/RMA, when the first request for all tasks arrive together, after reduction in system load, the lowest priority task  $T_n$  in M never misses the deadline.

*Proof:* After reduction in system load, the new task set  $M' = \{(C'_1, P'_1), (C'_2, P'_2), \dots, (C'_n, P'_n)\}$ . We consider an intermediate task set  $M'' = \{(C'_1, P_1), (C'_2, P_2), \dots, (C'_n, P_n)\}$ . The lowest priority task  $T_n$  in M remains to be the lowest priority task as  $T''_n$  in M'' because the periods are not changed. By lemma 10, the lowest priority task  $T''_n$  in M'' does not miss its deadlines. By corollary 12, task  $T''_n$  does not miss its deadlines in M' too even though it may or may not remain to be

the lowest priority task in M'. Hence by transitivity, the lowest priority task  $T_n$  in M never misses its deadline under reduction in system load.

Notice that the lowest priority task is not completely detached from the rest of the task set. Removing it may leave the task set unscehdulable, e.g. deleting  $T_3$  from the task set:  $\{T_1=(2,8),\,T_2=(9,14),\,T_3=(3,28)\}$  under NPFP/RMA or NPEDF. Similarly, decreasing the load (or even removal) of the highest priority task may also leave the task set unschedulable, e.g. removing  $T_1$  or reducing it to (1,20) from the task set:  $\{T_1=(2,20),T_2=(6,20),T_3=(24,80),T_4=(21,80)\}$  under NPFP/RMA or NPEDF.

**Theorem 14.** For NPFP/RMA, when the first request for all tasks arrive together, then after any reduction in system load, let the request time of task  $T'_i$  be r' and its time of start of execution be s': if all the tasks that get executed between r' and s' have priorities higher than i, then task  $T'p_i$  does not miss its deadline.

*Proof:* Since all the tasks that get executed between r' and s' have priorities higher than i, then we may consider task  $T'_i$  as the task of lowest priority during this interval of time (by deleting all lower priority tasks, and for the remaining tasks, counting only requests whose deadlines are after r'). By lemma 11, task  $T'_i$  has the longest response time when the request of all higher priority tasks arrive together at r', so we only need to consider the first request of task  $T'_i$ . By theorem 13, task  $T'_i$  would not miss its deadline under any reduction in system load.

**Theorem 15.** For NPEDF, after any reduction in system load, let the request time of task  $T'_i$  be r' and its time of start of execution be s': if all the tasks that get

executed between r' and s' have deadlines earlier than that of  $T'_i$  (i.e. with higher dynamic priority), then task  $T'_i$  does not miss its deadline.

Proof: It is known that any task set that is schedulable by NPEDF is also schedulable by PEDF. We have also proved that PEDF is robust against reduction in system load. A property of PEDF is that between r' and s', only tasks whose deadlines are earlier than that of  $T'_i$  get executed. By rearranging the PEDF execution order of task instances between r' and s' after reduction in system load, we get the corresponding schedule for NPEDF (which may or may not cause deadline miss for those higher priority tasks, but we are only concerned with task  $T'_i$ ). This task instance swapping keeps the start time s' of task  $T'_i$ . Hence  $T'_i$  would not miss its deadline.

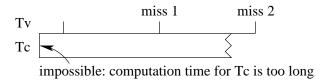

**Theorem 16.** For both NPFP/RMA and NPEDF, assume the first request of all tasks arrive together. If a certain instance of victim task  $T_v^{'p}$  whose request time is r' misses its deadline after reduction in system load, then there exists an instance of a culprit task  $T_c^{'q}$  satisfying these properties:

- The culprit task  $T_c$  is of lower priority than the victim task  $T_v$  (For NPFP/RMA, static priority means v < c; for NPEDF, dynamic priority means the deadline of  $T_c$  is later than that of  $T_v$ ).

- ullet The culprit task  $T_c^{\prime q}$  is executing at time  $r^\prime$ .

*Proof:* Suppose the contrary is true that all the task instances that are executed between r' and the deadline miss are of (static or dynamic) priorities higher than

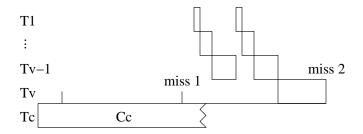

Figure 2.14: First seven periods of  $T_1$  in the example task set

that of the victim task  $T_v$ , then by theorems 14 and 15, the victim task instance  $T_v^{'p}$  would not miss its deadline, which is a contradiction. Hence an instance of the culprit task  $T_c$  of lower (static or dynamic) priority must be executing between r' and the deadline miss. Moreover, the culprit task must have started executing before r', otherwise by the time it starts execution, there is no outstanding computation for all higher priority tasks including the victim task  $T_v$ , and the victim task would not have missed the deadline. Hence the culprit task instance  $T_c^{'q}$  must be executing at time r'.

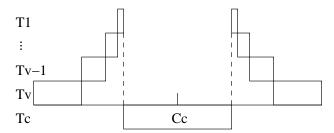

## 2.6 Miss Ratio

We will look at a CPU upgrade scenario where the miss ratio for NPFP/RMA or NPEDF scheduler can be as high as  $\frac{1}{2}$ . Miss ratio is defined for a task as the number of task instances whose deadlines are missed over the total number of task instances initiated in that interval of time.

We assume that if a task instance is not yet started when it misses its dead-

line, it will never be started. If an executing task instance misses its deadline, it does not matter whether it is killed right away or allowed to go to completion. When the run-time dispatcher picks a task instance for execution, the task is started even if the remaining time to its deadline is insufficient for its advertised computation time.

Consider the following set of tasks:

|           | Original        | After CPU upgrade                          |

|-----------|-----------------|--------------------------------------------|

| $T_1$     | (C, nC)         | $((1-\alpha)C, nC)$                        |

| $T_2$     | (2(n-1)C, 2knC) | $\left  ((1-\alpha)2(n-1)C, 2knC) \right $ |

| :         | :               | :                                          |

| $T_{k+1}$ | (2(n-1)C, 2knC) | $\left  ((1-\alpha)2(n-1)C, 2knC) \right $ |