Copyright by  $\label{eq:copyright}$  Tyler Michael Smith 2017

The Dissertation Committee for Tyler Michael Smith certifies that this is the approved version of the following dissertation:

# Theory and Practice of Classical Matrix-Matrix Multiplication for Hierarchical Memory Architectures

| Committee:                           |

|--------------------------------------|

| Robert van de Geijn, Supervisor      |

| 5.5.J., 15.5.P. 11.1.2.1             |

| Enrique Quintana-Ortí, Co-supervisor |

| Keshav Pingali                       |

| Donald Fussell                       |

# Theory and Practice of Classical Matrix-Matrix Multiplication for Hierarchical Memory Architectures

by

# Tyler Michael Smith

#### **DISSERTATION**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

#### DOCTOR OF PHILOSOPHY

# Acknowledgments

First and foremost I want to thank my advisor, Robert van de Geijn. I believe that a successful relationship between advisor and advisee is the greatest predictor of success in a PhD program. Robert's work forms the intellectual foundation for most of the work I've done at UT Austin. I have learned so much from him but although he is the teacher and I the student, he has always respected and trusted me and allowed and encouraged me to find my own problems and solutions. I would also like to thank my co-advisor, Enrique Quintana-Ortí and the rest of my committee Don Fussell and Keshav Pingali.

A big thank you to my friends and colleagues in the SHPC group: Maggie Myers, Field Van Zee, Ardavan Pedram, Tze Meng Low, Richard Veras, Martin Schatz, Devin Matthews, Woody Austin, Chenhan Yu, Jianyu Huang, Devangi Parikh. It takes a team effort to develop the infrastructure and institutional knowledge that are necessary to be able to produce the high quality work that comes out of this group. I owe all of you for your friendship and for just being there to talk shop and to bounce ideas off of.

I want to thank the many others I've been fortunate enough to have worked with during my time as a PhD student: Ted Barragy, Jeff Hammond, Misha Smelyanski, Greg Henry, Alex Heinecke, and Jeff Diamond, from whom I have learned so much about high performance computing.

I want to thank Bob Zigon for opening doors for me in my career when he didn't have to. Bob took it upon himself to teach computer science after school during his free time. He exposed me to all sorts of stuff that 18 year-olds do not typically get exposed to and later hired me as an intern at Beckman Coulter. This was a huge influence on my early career.

Finally I want to thank my family for always being there for me: My mom and dad, my sister Whitney, and Huxley Brown. In particular, I want to thank my wife Anisha for being my best friend, and for keeping me sane while working on my PhD.

# Theory and Practice of Classical Matrix-Matrix Multiplication for Hierarchical Memory Architectures

| Publication No. |

|-----------------|

|-----------------|

Tyler Michael Smith, Ph.D.

The University of Texas at Austin, 2017

Supervisor: Robert van de Geijn Co-Supervisor: Enrique Quintana-Ortí

Matrix-matrix multiplication is perhaps the most important operation used as a basic building block in dense linear algebra. A computer with a hierarchical memory architectures has memory that is organized in layers, with small and fast memories close to the processor, and big and slow memories further away from it. Classical matrix-matrix multiplication is an operation particularly suited for such architectures, as it exhibits a large degree of data reuse, so expensive data movements can be amortized over a lot of computation. This dissertation advances the theory of how to optimally reuse data during matrix-matrix multiplication on hierarchical memory architectures, and it uses this understanding to develop new practical algorithms for matrix-matrix multiplication that exhibit improved properties related to data movement.

# Table of Contents

| Ackno   | wledgments                                               | $\mathbf{V}$ |

|---------|----------------------------------------------------------|--------------|

| Abstra  | act                                                      | vii          |

| List of | Tables                                                   | xii          |

| List of | Figures                                                  | xiii         |

| Chapt   | er 1. Introduction                                       | 1            |

| 1.1     | Motivation                                               | 1            |

| 1.2     | Problem definition                                       | 3            |

| 1.3     | Contributions                                            | 4            |

| 1.4     | Organization                                             | 5            |

| Chapt   | er 2. Related Work                                       | 7            |

| 2.1     | A history of dense linear algebra packages               | 7            |

| 2.2     | Literature on theoretical I/O lower bounds $\dots \dots$ | 9            |

| 2.3     | Literature on practical MMM                              | 10           |

|         | 2.3.1 Strategy and tactics for practical MMM             | 11           |

| 2.4     | State-of-the-art matrix multiplication                   | 14           |

|         | 2.4.1 A brief description of Goto's algorithm            | 16           |

|         | 2.4.2 BLIS                                               | 18           |

| Chapt   | er 3. I/O Lower Bounds                                   | 20           |

| 3.1     | Introduction                                             | 20           |

| 3.2     | Problem Definition                                       | 22           |

|         | 3.2.1 Prior approaches                                   | 22           |

|         | 3.2.2 Our approach                                       | 22           |

| 3.3     | Lower Bound Proof                                        | 23           |

|       | 3.3.1  | High-level strategy                                                | 24 |

|-------|--------|--------------------------------------------------------------------|----|

|       | 3.3.2  | Employing the Loomis-Whitney inequality                            | 25 |

|       | 3.3.3  | A lower bound for $C := AB + C$                                    | 26 |

| 3.4   | Sumn   | nary                                                               | 27 |

| Chapt | er 4.  | Optimal Algorithms or: The Lower Bound is Tight                    | 29 |

| 4.1   | Introd | duction                                                            | 29 |

| 4.2   | Optin  | nal and read-optimal Algorithms                                    | 30 |

|       | 4.2.1  | Algorithms for one level of cache                                  | 30 |

|       | 4.2.2  | Algorithms for different shapes of MMM                             | 35 |

|       | 4.2.3  | A balancing act                                                    | 37 |

| 4.3   | Sumn   | nary                                                               | 39 |

| Chapt | er 5.  | A Family of Algorithms for Multiple Levels of Cache                | 40 |

| 5.1   | Introd | duction                                                            | 40 |

| 5.2   | A Far  | mily of Algorithms                                                 | 41 |

|       | 5.2.1  | The outer loop for the $L_{h-1}$ cache $\ldots \ldots \ldots$      | 42 |

|       | 5.2.2  | The inner loop for the $L_{h-1}$ cache $\ldots \ldots \ldots$      | 46 |

|       | 5.2.3  | Classifying matrix operands                                        | 47 |

|       | 5.2.4  | Special cases for the family of algorithms                         | 50 |

| 5.3   | Multi  | level Cache Tradeoffs                                              | 51 |

|       | 5.3.1  | Impact of optimizing for the $L_h$ cache on the $L_{h-1}$ I/O cost | 52 |

|       | 5.3.2  | Impact of optimizing for $L_{h-1}$ on the $L_h$ I/O cost           | 54 |

|       | 5.3.3  | Skipping caches                                                    | 59 |

| 5.4   | Exper  | riments                                                            | 62 |

|       | 5.4.1  | Experimental setup                                                 | 62 |

|       | 5.4.2  | Optimizing for the L3 cache                                        | 64 |

|       | 5.4.3  | Optimizing for the L4 cache                                        | 72 |

|       | 5.4.4  | Algorithms for different shapes of matrices                        | 77 |

| 5.5   | Sumn   | narv                                                               | 81 |

| Chapter 6.    |        | Cache Aware Multithreaded Parallelization        | 84  |

|---------------|--------|--------------------------------------------------|-----|

| 6.1           | Introd | duction                                          | 84  |

| 6.2           | Parall | lelization of loops within Goto's Algorithm      | 85  |

|               | 6.2.1  | The first loop around the micro-kernel           | 85  |

|               | 6.2.2  | The second loop around the micro-kernel          | 88  |

|               | 6.2.3  | The third loop around the inner-kernel           | 90  |

|               | 6.2.4  | The fourth loop around the inner-kernel          | 91  |

|               | 6.2.5  | The outer-most loop                              | 92  |

|               | 6.2.6  | Parallelism within the micro-kernel              | 93  |

| 6.3           | MMN    | I Parallelization for Intel Xeon Phi KNC         | 94  |

|               | 6.3.1  | Architectural Details                            | 94  |

|               | 6.3.2  | The BLIS implementation on the Intel Xeon Phi    | 95  |

|               | 6.3.3  | Which loops to parallelize                       | 96  |

|               | 6.3.4  | Parallelism within cores                         | 97  |

|               | 6.3.5  | Parallelism between cores                        | 98  |

|               | 6.3.6  | Performance results                              | 98  |

| 6.4           | MMN    | I Parallelization for IBM PowerPC A/2 $\dots$    | 102 |

|               | 6.4.1  | Architectural Details                            | 102 |

|               | 6.4.2  | The BLIS implementation on the IBM PowerPC A2 $$ | 103 |

|               | 6.4.3  | Which loop to parallelize                        | 104 |

|               | 6.4.4  | Performance results                              | 105 |

| 6.5           | Parall | lelizing the family of algorithms                | 106 |

|               | 6.5.1  | Parallelizing outside the $L_{h-1}$ subproblem   | 108 |

|               | 6.5.2  | Parallelizing within the $L_{h-1}$ subproblem    | 109 |

|               | 6.5.3  | Summary                                          | 110 |

| 6.6           | Sumn   | nary                                             | 110 |

| Chapter 7.    |        | Conclusion                                       | 112 |

| 7.1           | Resul  | ts                                               | 112 |

| 7.2           | Futur  | e work                                           | 114 |

| Appendices 11 |        |                                                  | 116 |

| Appendix A.  | Table of Symbols                               | 117 |

|--------------|------------------------------------------------|-----|

| Appendix B.  | Constrained Global Maximum of $\sqrt{xyz}$     | 118 |

| Appendix C.  | Bandwidth requirements for different datatypes | 120 |

| Bibliography |                                                | 122 |

| Vita         |                                                | 136 |

# List of Tables

| 5.1 | Machines used in experiments in this paper                                                               | 63  |

|-----|----------------------------------------------------------------------------------------------------------|-----|

| C.1 | Typical element sizes, computation rate, and bandwidth requirements for MMM relative to single precision | 121 |

# List of Figures

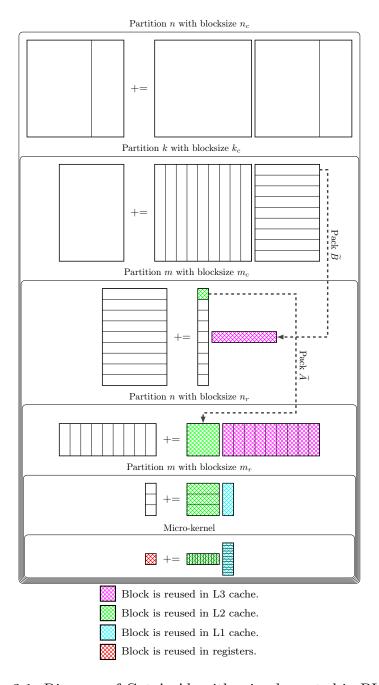

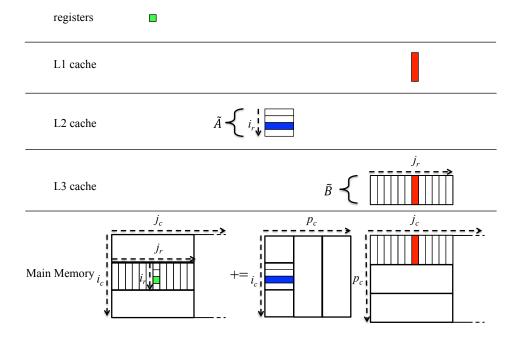

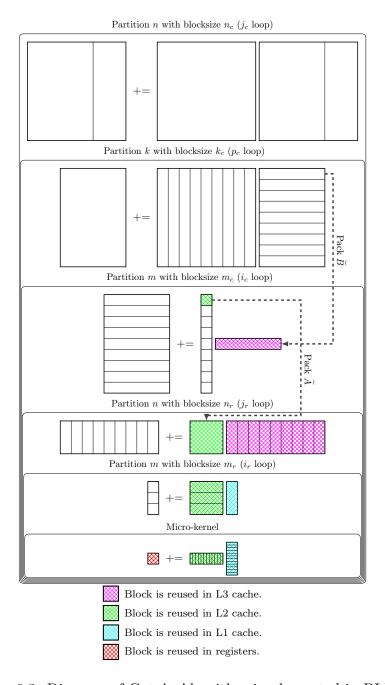

| 2.1 | Diagram of Goto's Algorithm implemented in BLIS                                                                                                                                                                                                                                                                                                                                                                                                             | 15 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

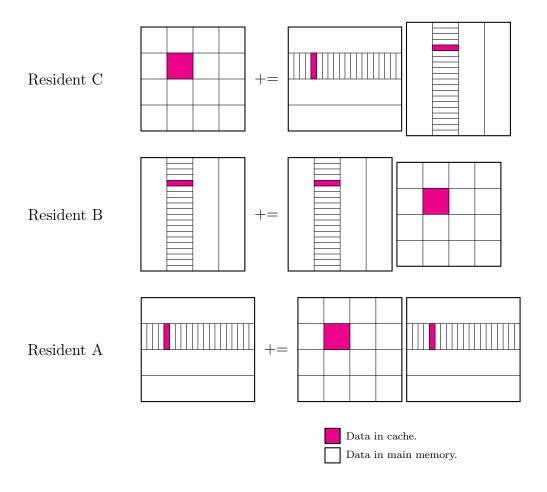

| 4.1 | Three algorithms for matrix multiplication that attain the lower bound for a single level of cache                                                                                                                                                                                                                                                                                                                                                          | 31 |

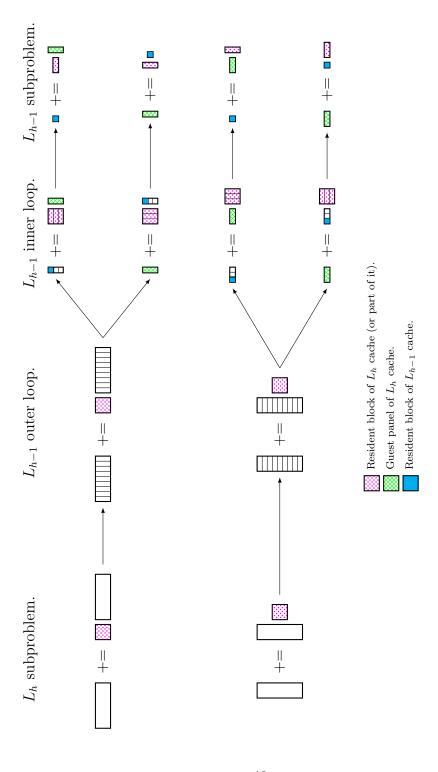

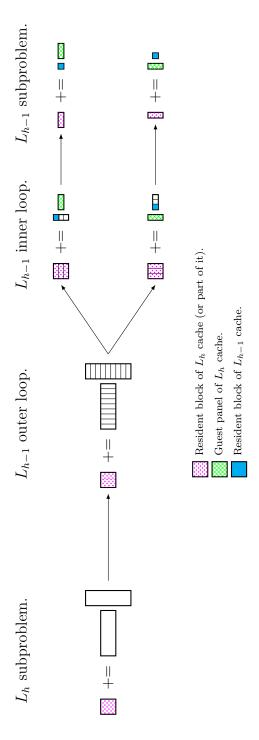

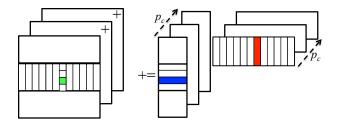

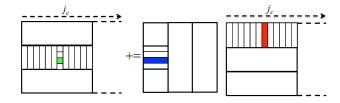

| 5.1 | Illustration showing the possible scenarios when partitioning for the $L_h$ and $L_{h-1}$ caches in the family of MMM algorithms when Resident A (top) or Resident B (bottom) is encountered at the $L_h$ cache.                                                                                                                                                                                                                                            | 43 |

| 5.2 | Illustration showing the possible scenarios when partitioning for the $L_h$ and $L_{h-1}$ caches in the family of MMM algorithms when Resident C is encountered at the $L_h$ cache                                                                                                                                                                                                                                                                          | 44 |

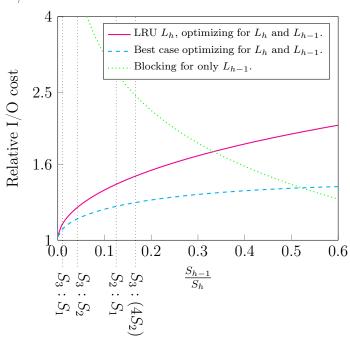

| 5.3 | This plot determines how much worse in terms of number of inputs to the $L_h$ cache an algorithm will be if it optimizes for the $L_{h-1}$ cache as well. If it is too costly, one may choose not to optimize for the $L_{h-1}$ cache. Vertical lines mark cache size ratios for the Intel i7-7700K. For example, $\frac{S_2}{S_1}$ is too large to optimize for both the $L_1$ and $L_2$ caches, but it is reasonable to optimize for both $L_2$ and $L_3$ | 56 |

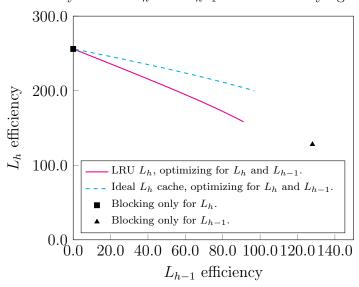

| 5.4 | An algorithm's $L_{h-1}$ versus $L_h$ efficiency in terms of flops per I/O. Moving from left to right, the $L_{h-1}$ blocksizes increase, decreasing the I/O costs associated with the $L_{h-1}$ streamed matrices. This causes the $L_h$ blocksizes to decrease, increasing the I/O costs associated with the $L_h$ streamed matrices and the $L_{h-1}$ resident matrix. In this plot, $S_h$ is $256^2$ , and $S_{h-1}$ is $128^2$ .                       | 58 |

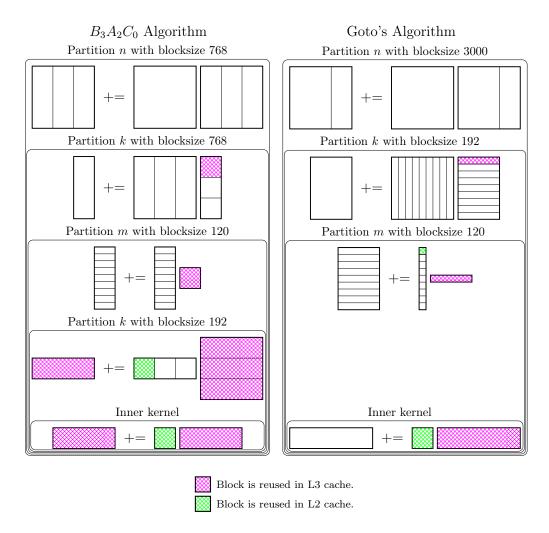

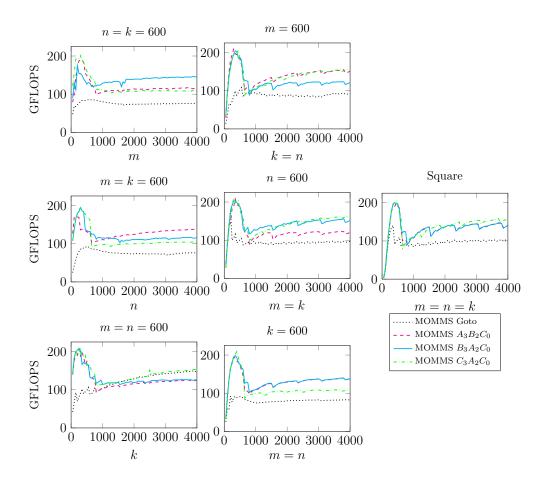

| 5.5 | Two algorithms for MMM. Left: $B_3A_2C_0$ . Right: Goto's Algorithm                                                                                                                                                                                                                                                                                                                                                                                         | 65 |

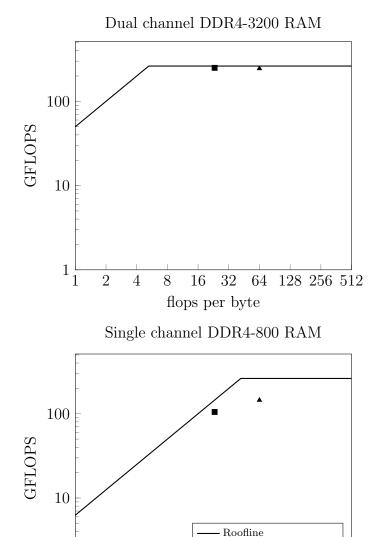

| 5.6 | Roofline models for an Intel i7-7700K at 4.2GHz with 4 cores under two bandwidth conditions. For algorithms displayed on the plots, the y-axis is measured and the x-axis is theoretical. Bottom: Two channels of DDR4 is set to DDR4-3200, for a peak bandwidth of 51200 MB/s. Top: One channel of DDR4 is set to DDR4-800, for a peak bandwidth of 6400 MB/s                                                                                              | 67 |

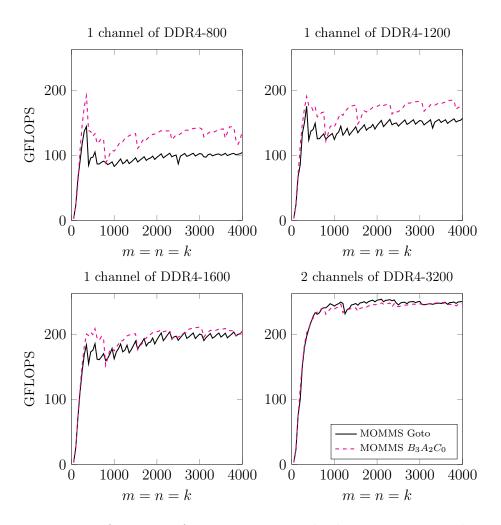

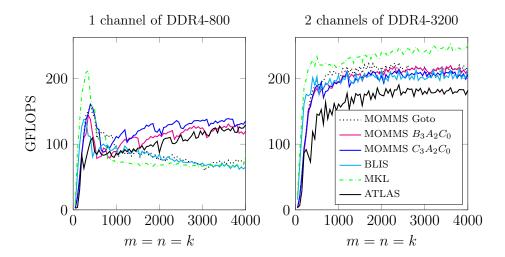

| 5.7 | Performance of matrix-matrix multiplication on an Intel i7-7700K for square matrices, varying problem size and available bandwidth. Matrices are stored prepacked                                                                                                                                                                                                                                                                                           | 70 |

| 5.8  | Practical comparison of performance against state-of-the-art open source and vendor libraries, for both high and low bandwidth scenarios. Matrices are passed in as column-major matrices, so packing is performed                                                                                    | 71 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.9  | An algorithm for MMM optimizing the number of inputs to both the L4 and the L2 caches. It places a square block of $C$ in the L4 cache, and a square block of $A$ in the L2 cache. The L3 cache is "skipped", but the blocksizes are such that the L4 guest matrix, $B$ , is reused from the L3 cache | 73 |

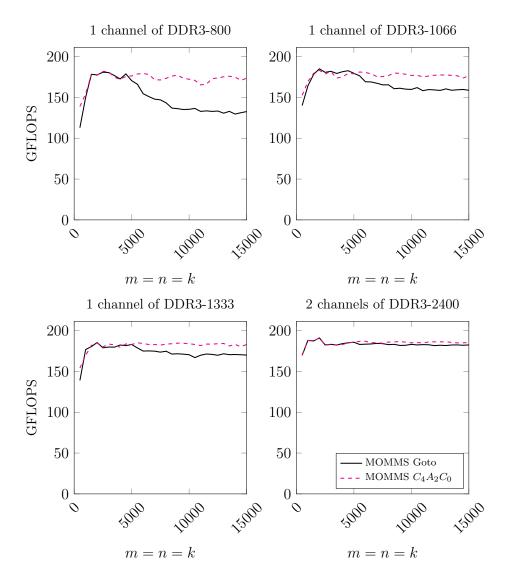

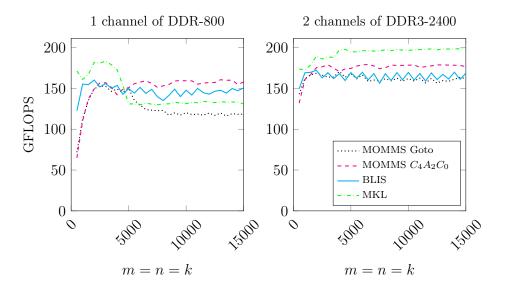

| 5.10 | Performance of matrix-matrix multiplication for square matrices, varying problem size and available bandwidth. Matrices are stored prepacked                                                                                                                                                          | 75 |

| 5.11 | Matrix-matrix multiplication performance on an Intel i7-5775C with an 128MB L4 cache for a low bandwidth scenario (1 channel of DDR3-800) and a high bandwidth scenario (2 channels of DDR3-2400)                                                                                                     | 76 |

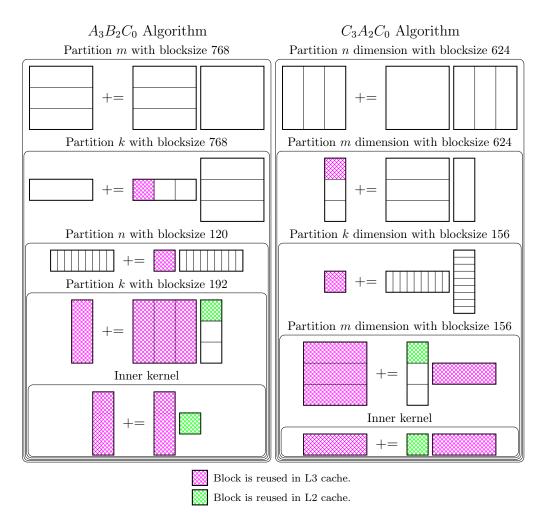

| 5.12 | Two algorithms for MMM for three levels of cache. Left: $A_3B_2C_0$ . Right: $C_3A_2C_0$                                                                                                                                                                                                              | 78 |

| 5.13 | Matrix-matrix multiplication performance for different problem shapes on an Intel i7-7700K under a low-bandwidth scenario (1 channel of DDR4-800)                                                                                                                                                     | 80 |

| 6.1  | Loops implementing Goto's Algorithm in BLIS                                                                                                                                                                                                                                                           | 86 |

| 6.2  | Illustration of which parts of the memory hierarchy each block of $A$ and $B$ reside in during the execution of the micro-kernel with BLIS                                                                                                                                                            | 86 |

| 6.3  | Diagram of Goto's Algorithm implemented in BLIS                                                                                                                                                                                                                                                       | 87 |

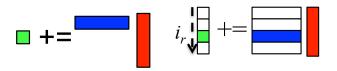

| 6.4  | Left: the micro-kernel. Right: the first loop around the micro-kernel                                                                                                                                                                                                                                 | 88 |

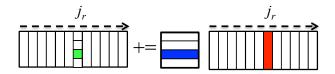

| 6.5  | The second loop around the micro-kernel                                                                                                                                                                                                                                                               | 89 |

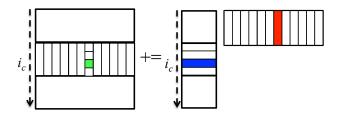

| 6.6  | The third loop around the micro-kernel (first loop around Goto's inner kernel)                                                                                                                                                                                                                        | 90 |

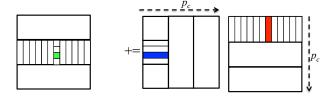

| 6.7  | The fourth loop around the micro-kernel (second loop around Goto's inner kernel)                                                                                                                                                                                                                      | 91 |

| 6.8  | Parallelization of the $p_c$ loop requires local copies of the block of $C$ to be made, which are summed upon completion of the loop.                                                                                                                                                                 | 92 |

| 6.9  | The fifth (outer) loop around the micro-kernel                                                                                                                                                                                                                                                        | 93 |

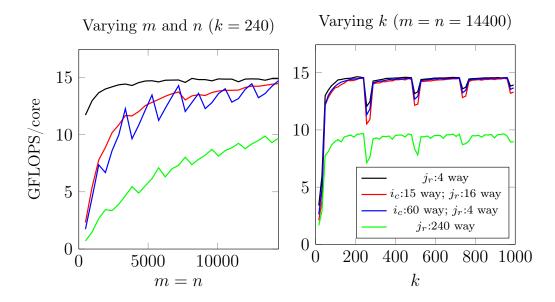

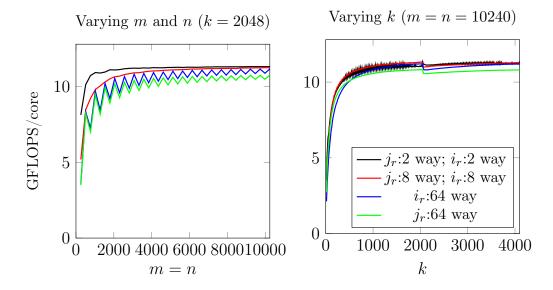

| 6.10 | MMM performance using different parallelization schemes within BLIS on the Intel Xeon Phi. $i_c:n$ way indicates $n$ -way parallelization of the third loop (indexed by $i_c$ ) around the microkernel, and $j_r:n$ way indicates $n$ -way parallelization of the second loop (indexed by $j_r$ ) around the micro-kernel | 99  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

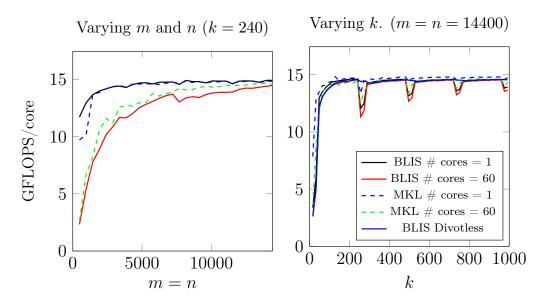

| 6.11 | MMM performance comparison of BLIS and MKL on the Intel Xeon Phi KNC                                                                                                                                                                                                                                                      | 100 |

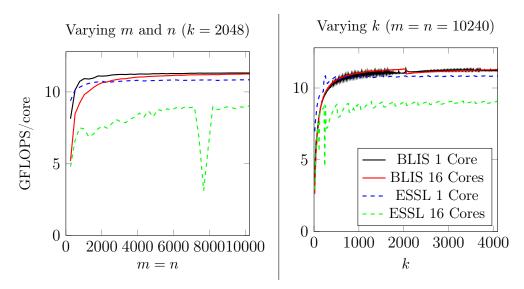

| 6.12 | MMM with different parallelization schemes for the IBM PowerPC A2. ' $j_r$ : $n$ way' indicates $n$ -way parallelization of the second loop (indexed by $j_r$ ) around the micro-kernel, and ' $i_r$ : $n$ way' indicates $n$ -way parallelization of the first loop (indexed by $i_r$ ) around the micro-kernel          | 106 |

| 6.13 | MMM performance comparison of BLIS and ESSL on the PowerPC A2 Blue Gene Q                                                                                                                                                                                                                                                 | 107 |

# Chapter 1

#### Introduction

Hierarchical memory architectures have been used for decades to reduce the cost of data access. One can conceive a memory hierarchy being laid out as a pyramid, with several layers of memory. The layer of memory closes to the processor is the smallest and fastest, and each subsequent layer of memory is bigger, slower, and further from the processor compared to the layer above it. The goal for this dissertation is efficient computation for matrix operations on machines with hierarchical memories. The thesis is that there are three algorithms for matrix-matrix multiplication that, considering one layer of memory, are optimal in terms of the number of reads from slower layers. These three algorithms can be composed in order to encounter one of them at each layer of the memory hierarchy. This dissertation contains both theoretical and practical advances related to this thesis.

#### 1.1 Motivation

High-performance dense linear algebra libraries are of great practical importance, as they are often used as building blocks of applications used in scientific computing and data analysis. Efficient implementations are widely available on almost any platform, and dense linear algebra operations are expected by application programmers to achieve efficiencies close to the peak performance of the machine. In addition to its practical importance, the im-

plementation of high-performance matrix operations are of pedagogical significance, since they are often used to illustrate how to attain high performance on a novel architecture.

Research regarding practical dense linear algebra software has been ongoing for at least the past forty years [34], and research regarding theory of optimal use of hierarchical memory for linear algebra has been ongoing for at least the past three decades [47]. Costs related to data movement are often the most significant overhead when efficient computing is a goal. Caches are small and fast buffers used to facilitate a reduction in data movement costs. When data has good temporal locality, input-output (I/O) costs can be reduced by reusing data while it is in a cache. Modern computers use multiple levels of cache, where higher levels of cache are smaller, faster, and nearer to the processor, and lower levels of cache are bigger, slower, and further away.

Matrix-matrix multiplication (MMM) is an operation that many applications depend upon to attain high performance. Scientists and engineers have come to expect high-performance implementations of the Basic Linear Algebra Subprograms (BLAS) [54, 27, 26] interface, providing functionality for vector-vector, matrix-vector, and matrix-matrix operations. In turn, dense linear algebra (DLA) libraries such as LAPACK [5] and libflame [40, 77, 78] use BLAS operations as building blocks to provide high-performance implementations of more sophisticated operations like matrix factorizations for single-node hierarchical memory systems. Then, distributed-memory DLA libraries such as ScaLAPACK [22], PLAPACK [7], and Elemental [64] rely both on the BLAS and on single-node DLA libraries. As such, MMM is one of the most important operations at the bottom of a rich ecosystem of DLA libraries that are depended upon by scientists in high-performance and scientific computing.

When developing a DLA library, an engineer will typically employ a set of heuristics in order to optimize for performance, energy consumption, or workspace, or to achieve some other goal. Ideally, heuristics should have firm theoretical underpinnings such that they can be shown to be optimal according to a model of computation. Therefore this dissertation has developed realistic but idealized models for computation and then has used these models to develop theoretically optimal algorithms. These results have been used to understand practical algorithms that attain high-performance and are efficient on modern and future hardware in the domain of dense linear algebra.

#### 1.2 Problem definition

In this dissertation, we will focus on the classical MMM operation C += AB. In all cases, C is  $m \times n$ , A is  $m \times k$ , and B is  $k \times n$ . We focus on the case where all matrices are dense and unstructured, however, the algorithms presented in this dissertation should apply to the cases where matrices are dense and structured as well. The operation is classical in the sense that so-called fast algorithms for MMM are not used, and it requires 2mnk floating point operations (flops) for dense unstructured matrices.

The goal of this dissertation is efficient algorithms for matrix operations for hierarchical memory architectures. We will describe memory hierarchies in the following manner: We name the n levels of the memory hierarchy  $L_0, L_1, ..., L_{n-1}$ , for every h, 1 < h < n, the cost of accessing  $L_h$  is more expensive than that of accessing  $L_{h-1}$ . Each level of memory  $L_h$  has a size  $S_h$ , and  $S_h > S_{h-1}$  for every h, 1 < h < n.

#### 1.3 Contributions

This dissertation makes the following contributions:

- It proves a new and improved theoretical I/O lower bound for MMM. For a machine with two layers of memory –one fast layer with capacity S, and one slow layer with unlimited capacity– MMM requires at least  $\frac{2mnk}{\sqrt{S}}$  reads from and writes to slow memory.

- It analyzes the I/O optimality of a family of three algorithms for a single layer of fast memory. One of these three algorithms has an I/O cost of  $\approx \frac{2mnk}{\sqrt{S}} + mn$ . Since it attains the lower bound, the algorithm is I/O optimal and this proves that the I/O lower bound is tight. The other two algorithms attain the lower bound in a weaker sense; that is if one ignores the I/O cost associated with writes to slow memory, which often occurs if the slow memory being written to is a cache.

- It shows that considering different "shapes" of MMM operations, where some of the dimensions m, n, and k are small and other large, some of those three algorithms will be optimal (when ignoring the cost of writes), and others will be suboptimal. It gives the conditions of optimality for each.

- It describes a new family of algorithms for multiple levels of cache. By composing two loops per level of cache, one of the three algorithms for a single level of cache can be encountered at each layer of the memory hierarchy. It then demonstrates the performance of a practical algorithm for MMM that is 45% more efficient than the state-of-the-art Goto's algorithm [36] on a conventional architecture when the matrices are too

large to fit into cache and the ratio between the rate of computation and the rate of data movement from main memory is made artificially high (and representative of possible future architectures). This performance benefit is accomplished by utilizing the  $L_3$  cache more effectively than Goto's algorithm does.

- It shows how the cache hierarchy can be taken into account when parallelizing matrix operations. When caches are shared between threads, it is beneficial to parallelize differently than when threads have independent caches. It then shows how these ideas can be implemented by demonstrating practical performance for the many-core IBM Blue Gene/Q PowerPC A2 and Intel Xeon Phi Knight's Corner architectures.

- It derives algorithms to utilize aggregate fast memories. That is, on a multiprocessor system where each processor has its own proprietary fast memory, the algorithm is optimal both for the number of elements moved into and out of each individual fast memory, and also optimal for the number of elements read into and out of slow memory. This is advantageous if it is less expensive for a processor to access another processor's fast memory than it is to access slow memory.

## 1.4 Organization

This dissertation is organized as follows:

- Chapter 2 outlines the literature related to this present work. The related work is treated with more detail in later chapters.

- Chapter 3 gives a proof of an improved I/O lower bound for MMM.

- Chapter 4 analyzes three algorithms for MMM for machines with a single layer of fast memory. An algorithm is shown to obtain the lower bound from Chapter 3, so the lower bound is said to be tight, and the algorithm is said to be optimal.

- Chapter 5 derives a family of algorithms for MMM for machines with multiple levels of cache. By composing two loops per level of cache, one of the three algorithms from Chapter 4 can be encountered at each level of cache.

- Chapter 6 Discusses how parallelism can be obtained within the family of algorithms presented in Chapter 5. It then describes in detail the properties of parallelizing each of the loops within the BLIS implementation of Goto's algorithm, a member of the family of algorithm from Chapter 5.

In this dissertation, Chapter 3 is very theoretical, and each chapter is more practical than the one before it.

# Chapter 2

#### Related Work

In this chapter, we will look at related work, including a brief history of linear algebra packages, followed by a brief description of the state-of-the-art implementation and algorithms for matrix multiplication.

## 2.1 A history of dense linear algebra packages

First we will describe a history of DLA packages and the building blocks of the DLA software stack. One of the earliest examples of such a package is EISPACK by Garbow [34], which provided routines for obtaining the eigenvalues and eigenvectors of a matrix. Lawson et al. [54] introduced the Basic Linear Algebra Subprograms (BLAS). This was a set of 38 simple FORTRAN routines operating on vectors. Examples include the dot product of two vectors, the scaling of a vector, and the generation and application of Givens rotations. The point of such a library was to standardize an interface for a set of routines such that one could always expect an efficient implementation to exist on any given machine. This standard BLAS interface facilitated portable high performance for the vector computers of the 1970s. Around the same time, Dongarra et al. [25] introduced the LINPACK package that implemented higher level functionality such as matrix factorizations in terms of the BLAS.

In the late 1980s, with the cost of a flop getting cheaper relative to the cost of a memory operation (memop), and with the advent of hierarchical memories, operations solely on vectors could no longer run efficiently, as such operations provide little opportunity for data reuse. Within the BLAS, this was rectified by the introduction of the level-2 BLAS, extending the BLAS with a set of matrix-vector routines (such as a matrix-vector multiplication or a rank-1 update) [27]. This provided more opportunities for data reuse.

Shortly thereafter, Dongarra et al. [26] introduced the level-3 BLAS. This contained matrix-matrix operations (such as MMM) that, when working with data that can fit into fast memory, can amortize the  $\mathcal{O}(n^2)$  memops needed to perform the matrix-matrix operation over  $\mathcal{O}(n^3)$  flops. The BLAS level-1, 2, and 3 interfaces have become so ubiquitous that often DLA operations are referred to as their BLAS function names. For example the MMM operation  $C := \alpha AB + \beta C$  (where  $\alpha$  and  $\beta$  are scalars) is often referred to as GEMM. LINPACK, which casts its computation in terms of the level-1 BLAS, became no longer efficient, leading to the introduction of LAPACK [5].

Gunnels et al. [40, 39] introduced the Formal Linear Algebra Methods Environment or FLAME. It made two important contributions. First, it encodes computation in terms of partitioned matrices and performs operations on these partitions, rather than in terms of indices into arrays. This allowed the associated library, libflame, to be more pedagogical, as the code itself looks like what one might write on a whiteboard when describing an algorithm. Secondly, FLAME provided a method of deriving algorithms for linear algebra operations that are proven to be correct [12, 76, 13].

Libraries such as PLASMA [17] and SuperMatrix [19] build on top of libraries like LAPACK and libflame, respectively, to provide run time paral-

lelization of DLA operations, where matrices are broken into blocks, and operations are implemented as directed acyclic graphs operating on those blocks. The advantage is that this technique avoids tricky load balancing issues that can arise when parallelizing complicated operations.

Finally, there are several libraries targeted towards distributed-memory clusters of computers. Much as LAPACK and FLAME cast computation in terms of the BLAS, distributed dense linear algebra libraries such as ScaLA-PACK [22], PLAPACK [7], and Elemental [64] cast much of their computation in terms of BLAS, LAPACK, and libflame, but this dissertation is not concerned with distributed-memory architectures.

### 2.2 Literature on theoretical I/O lower bounds

The seminal paper by Hong and Kung [47] describes the red-blue pebble game, in which computation is described as a directed acyclic graph (DAG). If a blue pebble is placed on a vertex, the value associated with that vertex is in slow memory, and if the vertex instead has a red pebble, the value is in fast memory. There are a finite number of red pebbles, and a small set of rules for playing the game. The goal of the game is to minimize the number of transitions between red and blue to complete computation. Then, this minimum number of transitions is equivalent to the lower bound on the I/O complexity for a computation. Using this model, the minimum number of memory movements required for MMM is  $\mathcal{O}(\frac{n^3}{\sqrt{S}})$ , where S is the number of red pebbles. Savage [65] extends the Hong-Kung model to memories with multiple layers of fast memory. For MMM, it only proves that the same lower bound from [47] is true at every level of the memory hierarchy.

Irony et al. [50] uses the same strategy as [47] to prove lower bounds

for MMM for both hierarchical and distributed memory architectures. The main concern of Irony, et al. is attaining the lower bound for MMM on distributed memory architectures using 3D algorithms. An innovation of this paper was using the Loomis-Whitney inequality [56] to find an upper bound on the amount of computation that can be performed using a certain number of elements each of A, B and C.

Dongarra et al. [24] improved upon the coefficient of the lower bounds for MMM, showing that MMM must incur an I/O cost of  $\frac{3\sqrt{3}mnk}{2\sqrt{2}}$ . This improvement came from the implicit assumption that computation is performed via fused multiply-add instructions.

Ballard et al. [8] extended the lower bounds results in [50] to operations beyond MMM, like the LU and Cholesky factorizations. Generalizing the lower bounds to these other operations made the coefficient on the leading term less tight. This is because in order to generalize the proof to handle these operations, the matrices A, B, and C could no longer be assumed to be distinct.

# 2.3 Literature on practical MMM

Numerous papers have been written about how to implement the operations in the aforementioned DLA packages. Here, we focus on the papers concerning the practical implementation of MMM. Much of this work has to do with answering the question: How can data be moved across layers of the memory hierarchy optimally?

#### 2.3.1 Strategy and tactics for practical MMM

**Autotuning** Autotuning is a technique where the best values of various parameters like blocksizes are determined by empirically measuring performance when those parameters are adjusted. Autotuning was introduced in DLA by the code generator system PHiPAC [14], which stands for Portable High Performance ANSI C.

The ideas behind PHiPAC were built upon by Whaley and Dongarra [83], in the BLAS library Automatically Tuned Linear Algebra Software (ATLAS). The major contribution of ATLAS was introducing the idea of implementing MMM in terms of a basic unit of computation, often known today as a kernel. In ATLAS it was originally called an on-chip multiply.

The algorithm described in [83] specifies two possible loop orderings used by ATLAS, depending on the problem size. Regardless, of the loop ordering chosen, computation is cast in terms of block dot-products where C is  $n_b \times n_b$ , and the k dimension is much larger. The next step partitions this block-dot product along the k dimension with blocksize  $n_b$ . Then the on-chip multiply occurs, updating the block of C with an  $n_b \times n_b$  block of A times an  $n_b \times n_b$  block of B. During the on-chip multiply, computation is arranged so that either the  $n_b \times n_b$  block of A or the  $n_b \times n_b$  block of B fills most of cache, streaming the other operands.

The loop around ATLAS's on-chip multiply is in the k dimension, and thus each iteration uses a different block of A and B. Therefore each time an on-chip multiply is performed, an  $n_b \times n_b$  block of each matrix A, B, and C must be read from a slower level of memory. There are  $3n_b^2$  reads and  $n_b^2$  writes per on-chip multiply, so there are  $\frac{3}{2n_b}$  reads per flop from slow memory. Since one  $n_b \times n_b$  block must fit into cache,  $n_b \leq \sqrt{S}$ . Thus the algorithm from [83]

has an I/O cost of at least  $\frac{3mnk}{\sqrt{S}}$ . This is 50% larger than the tight lower bound in [69]. This present paper improves upon [83] by introducing algorithms that attain much closer to the I/O lower bound.

Model-based MMM Gunnels et al. [41] describes a family of algorithms for GEMM. It shows that given the shape of matrix-matrix multiplication that is being executed at some level of cache, there are two locally optimal choices for what shape of matrix-matrix multiplication must happen at the next highest level of cache. This forms a tree of locally optimal decisions, and each path from root to leaf is a member of a family of algorithms.

Yotov et al. [88] takes an algorithm similar to that of ATLAS [83], but adopts the opposite stance: Identifying optimal or near-optimal block sizes for GEMM can be done analytically, and thus empirical search is not necessary. More recently, Low et al. [57] took the ideas behind Yotov et al., and applied them to the more modern GotoBLAS approach, to be discussed later [36].

Cache oblivious algorithms. Most of the work presented above is related to algorithms that explicitly partition matrices to fit into cache. These are called *cache-aware* algorithms. An alternate technique is to use a divide-and-conquer algorithm, where each divide step reduces the size of working set of data. At some point, the size of this working set becomes small enough that it naturally fits into cache. Algorithms that attempt to use cache optimally in this manner are called *c*ache oblivious algorithms.

An early cache oblivious algorithm is presented in Aggarwal et al, [3] which proposes a model for hierarchical memory and then shows that a divideand-conquer algorithm for square matrix-multiplication is optimal under this model. Later, Gustavson [42] showed that such recursive divide-and-conquer algorithms could provide cache blocking for more complicated LAPACK routines such as Cholesky factorization as well. Finally, Frigo et al. [29] popularized the idea of cache-oblivious algorithms beyond the domain of linear algebra and named them. Frigo et al. also presents an algorithm that is shown to be optimal for a matrix multiplication of any shape. They show their cache-oblivious algorithms are optimal only for a single level of cache. However they also show that any cache-oblivious algorithm that is optimal for one level of cache is also a locally optimal cache-oblivious at every level of cache on systems that have multiple levels of cache. This local optimality should be compared to Gunnels et al. [41], which presents a family of cache-aware algorithms that are shown to be locally optimal at every level of cache.

Tactics for practical MMM There are some papers that are not so concerned with the theory of how to optimally move matrices through memory, but address more practical considerations that arise when implementing MMM. Henry [46] discusses how to implement high-performance BLAS on the IBM superscalar RISC S/6000. More importantly, it introduces what it calls a Block Data Structured GEMM. Today we know this concept as packing, where matrix partitions are copied into special buffers in order to maximize spatial locality as well as arrange the data in a convenient format for accessing using SIMD instructions.

Kågstöm et al. [51] showed that the level-3 BLAS operations can be implemented mostly in terms of MMM, and in some cases a small amount of computation must be performed in terms of level-2 BLAS operations. This shows that it is only necessary to optimize general MMM, and then the rest

of the level-3 BLAS comes "for free".

Agarwal et al. [2] is not specific on how loops are structured for cache blocking, but rather discusses the low level details of how to exploit the various hardware resources available on the IBM Power2 to effectively use instruction level parallelism, yielding high performance.

This is just a small sample of the papers in this area that influenced our own work.

#### 2.4 State-of-the-art matrix multiplication

Goto and van de Geijn [36] described what is currently accepted to be the most effective approach to implementing MMM in terms of rank-k updates. We call this Goto's algorithm, and it was first implemented in the BLAS implementation GotoBLAS. GotoBLAS is currently maintained as a package called OpenBLAS. The primary innovation was in realizing that there is enough bandwidth from the L2 cache, so that one of the operands can be streamed from the L2 cache, if the other operand resides in the L1 cache, and optimized for the L2 cache by putting a square block in the L2 cache. Previously it was believed that one must optimize for the L1 cache. The effect was that blocksizes could be increased, leading to better amortization of memory movements. <sup>1</sup>

Figure 2.1: Diagram of Goto's Algorithm implemented in BLIS.

#### 2.4.1 A brief description of Goto's algorithm

Let us focus on the simplified case C := AB + C, or C += AB, where A, B, and C are  $m \times k$ ,  $k \times n$ , and  $m \times n$  matrices, respectively. Goto's algorithm, illustrated in Figure 2.1, successively partitions the matrices so that different tiles of A, B, and C are moved across the levels of cache in different ways. A chunk of memory (or matrix partition) may either reside in some layer of memory or it may be streamed through that layer of memory. If the computation is arranged such that some matrix partition is moved into a layer of memory and then reused while it is still in that layer of memory, we say that it resides in that layer. If instead the computation is arranged such that some matrix partition is moved into a layer of memory, used once, and then evicted from that layer of memory before it is used again, we say that it is streamed through that layer of memory.

The partitioning of the matrices and where they reside in memory is shown on the left, and the loops that implement the matrix partitions are shown on the right. Starting from the top, the outer-most loop, indexed by  $j_c$ , partitions C and B into (wide) column panels. Next, the loop indexed by  $p_c$  partitions A and the current column panel of B into column panels and row panels, respectively. Thus the current column panel of C (of size  $m \times n_c$ ) is updated as a sequence of rank-k updates (with  $k = k_c$ ). At this point, Goto's algorithm packs the current row panel of B into a contiguous buffer, B. Assuming there is an L3 cache, B will reside in the L3 cache. The primary reason for the outer-most loop, indexed by  $j_c$ , is to limit the amount

<sup>&</sup>lt;sup>1</sup>At the time, the amount of data addressable by the pages in the level-1 translation lookaside buffer (TLB) limited the size of the block in the L2 cache.

of workspace required for  $\widetilde{B}$  A secondary reason is to allow  $\widetilde{B}$  to remain in the L3 cache.

Next, the current panel of A is partitioned into blocks by a loop indexed by  $i_c$ . The current block of A is then packed into a contiguous buffer,  $\widetilde{A}$ . The block is sized to occupy a substantial part of the L2 cache, leaving enough space to ensure that other data does not evict the block. Goto's algorithm then implements the "block-panel" multiplication of  $\widetilde{A}\widetilde{B}$  as its inner kernel, making this the basic unit of computation.

Now let us describe the workings of this inner kernel. In GotoBLAS, this inner-kernel is a black-box implementation, often coded in assembly language. At this point,  $\widetilde{A}$  resides in the L2 cache and  $\widetilde{B}$  in the L3 cache. The next loop, indexed by  $j_r$ , partitions  $\widetilde{B}$  into column micro-panels of width  $n_r$ . During one iteration of this loop, the current micro-panel of  $\widetilde{B}$  resides in the L1 cache. Finally, the inner-most loop, indexed by  $i_r$ , partitions  $\widetilde{A}$  into row micro-panels of height  $m_r$ .

At each iteration of the inner-most loop, a block dot product computation occurs: the current micro-panel of  $\widetilde{A}$  is multiplied by the current micro-panel of  $\widetilde{B}$  to update the corresponding  $m_r \times n_r$  block of C. This is performed as a sequence of rank-1 updates (outer products) with columns from the micro-panel of  $\widetilde{A}$  and rows from the micro-panel of  $\widetilde{B}$ . During the execution of this block dot product, an  $m_r \times n_r$  block of C resides in registers, a  $k_c \times n_r$  micro-panel of  $\widetilde{B}$  resides in the L1 cache, and the  $m_r \times k_c$  micro-panel of  $\widetilde{A}$  is streamed from the L2 cache.

The key takeaway here is that different tiles of A, B, and C are placed in different layers of memory, and reused from there in an attempt to amortize

or hide the memory movements required to implement MMM. These memory movements can be summarized as follows:

- ullet is moved into the L3 cache from main memory. This memory movement is amortized over many block-panel matrix multiplications.

- ullet  $\widetilde{A}$  is moved into the L2 cache from main memory, amortized over many block-micropanel matrix multiplications.

- $\bullet$  A micro-panel of  $\widetilde{B}$  is moved into the L1 cache from the L3 cache, amortized over many block dot products.

- A micro-tile of C is moved into registers from main memory, amortized over many rank-1 updates.

It is through data reuse that we can amortize the cost of memory movements. With effective amortization, the cost of the MMM is then dependent only on the cost of the computation. The goal is to reuse data optimally to amortize the memory movements the best that we can.

#### 2.4.2 BLIS

Van Zee and van de Geijn [81] introduced the BLAS-like Library Instantiation Software (BLIS). This is a systematic reimplementation of GotoBLAS, focusing on reducing the amount of effort required to port BLIS to a new architecture, as demonstrated in [80]. It shows that the GotoBLAS inner kernel (known in BLIS terminology as the *macro-kernel*) can be implemented as two loops around a much smaller *micro-kernel*. The effect is that only a single micro-kernel must be implemented for each data type on a given architecture,

whereas GotoBLAS requires 12 inner kernels to be implemented for each data type on a given architecture in order to support all level-3 BLAS operations.

# Chapter 3

# I/O Lower Bounds

#### 3.1 Introduction

The goal of this chapter is to find theoretical lower bounds on the I/O cost for MMM. An I/O lower bound gives us the minimum number of reads and writes that must occur during the execution of an MMM operation, and the greater the I/O lower bound, the better. When developing algorithms, we can evaluate them by analyzing their I/O cost and comparing this to the I/O lower bounds. When the costs are equal, we can say that the I/O lower bounds are tight and the algorithm is optimal.

Deriving lower bounds starts with the assumption that a processor has two layers of memory hierarchy, a small *fast* memory and a large *slow* memory. The fast and slow memory could represent the cache(s) and main memory of a processor, respectively, or main memory and disk. Practical implementations attempt to minimize the movement of data between these (and more) layers.

Hong and Kung [47] introduced what they called the red-blue pebble game model for a machine with two layers of memory. A limited number of blue pebbles represented fast memory while an unlimited number of red

Portions of this chapter have been previously published as the techincal report [69]. The lower bounds and analysis of algorithms were obtained by the author of this dissertation, and the majority of the text written by him as well. It is under submission to ACM Transactions on Mathematical Software. Bradley Lowery and Julien Langou are to be added as co-authors as they have independently obtained the same result.

pebbles represented slow memory. By reasoning how at different times blue and red pebbles could be associated with subsets of data, a lower bound of  $\Omega(mnk/\sqrt{S})$  for MMM was obtained, where S is the size of the fast memory (in matrix elements). In 1995, Savage [65] extended the red-blue pebble game to an arbitrary number of layers, and showed that the lower bound from [47] applies at every layer of the memory hierarchy.

In 2004, Irony et al. [50] use a very similar technique to extend the lower bounds to communication between nodes of a distributed memory parallel computer. Importantly, they provide a constant for the leading term of the I/O lower bound,  $mnk/(2\sqrt{2}\sqrt{S})$ . More recently, in 2014, Ballard et al. [8] generalized the techniques in [47] and [50] so that they can be applied to many operations in numerical linear algebra, not only MMM.

This chapter provides a better constant for the leading term of the lower bound for this problem. In Chapter 4, we will show that there are algorithms that attain this lower bound with the same constant, hence the lower bound is tight. While prior papers obtained lower bounds by reasoning about the multiplications that must be performed as part of an MMM operation, this chapter observes that in practice fused multiply add (FMA) operations are employed, and that in practice C := AB + C (matrix-matrix multiplication and accumulation or MMMA) is more representative of how matrix-matrix operations are implemented in high-performance libraries. It shows that by targeting MMMA instead of MMM, a superior lower bound of  $2mnk/\sqrt{S} - 2S$  can be obtained. The constant on the leading term is  $4\sqrt{2}$  times greater than that of the previous lower bound.

## 3.2 Problem Definition

In this section, we give a formal description of MMM for which we will derive I/O lower bounds. The computation that must be performed can be described as follows: Consider C := AB and let  $\gamma_{i,j}$ ,  $\alpha_{i,j}$ , and  $\beta_{i,j}$  equal the (i,j) elements of the respective matrices. Then  $\gamma_{i,j} := \sum_{p=0}^{k-1} \alpha_{i,p} \beta_{p,j}$ . This requires mnk scalar multiplications and mn(k-1) scalar additions.

## 3.2.1 Prior approaches

Previous work, including both Hong and Kung [47], Irony et al. [50], obtained lower bounds for MMM and described computation in terms of a directed acyclic graph (DAG). In those papers, the DAGs have input vertices corresponding to the elements of the matrices A and B, output vertices corresponding to the elements of the result matrix C, and computation vertices corresponding to the mnk elementary multiplications  $\alpha_{i,p}\beta_{p,j}$ . Each computation vertex has as inputs an element of A and an element of B, and as an output a scalar that must be summed with others to form an element of C. These DAGs allow reasoning about dependencies but do not expose the costs associated with reading elements of C from slow memory.

#### 3.2.2 Our approach

In order to achieve tight lower bounds, our problem definition must expose the costs of reading elements of C. To achieve this, we model computation in terms of FMAs. Unfortunately, the MMM operation can not be directly modeled in terms of FMA operations. This is because of the mismatch between the mnk elementary multiplications and the mn(k-1) elementary additions. Because of this, we will instead find lower bounds for a different problem, that

of the operation C += AB, or MMMA. A conventional MMMA has mnk scalar multiplications and mnk scalar additions. We assume that each scalar multiplication  $\alpha_{i,p}\beta_{p,j}$  is paired with a corresponding scalar addition, and they are executed via an FMA instruction that has three inputs (a variable in which contributions to  $\gamma_{i,j}$  are accumulated, and the elements  $\alpha_{i,p}$  and  $\beta_{p,j}$ ) and one output (the variable in which contributions to  $\gamma_{i,j}$  are accumulated).

When describing a DAG for an MMMA that casts computation in terms of FMAs, computing an element of C depends on some vertex that contributes to the same element of C. Thus the definition of such a DAG would impose a partial ordering on the computation. We wish to avoid such an ordering, which leads us to *not* describe computation in terms of a DAG.

Our problem definition is as follows. A conventional MMMA executes mnk FMAs. Each FMA has three inputs: an element of A, B, and C, and all inputs must be in fast memory in order for the FMA to be executed. Our proofs reason only about the input costs, and so our problem definition does not include anything about outputs from instructions. Each FMA must be of the form  $\tau_{i,j} = \delta_{i,j} + \alpha_{i,p}\beta_{p,j}$  where  $\tau_{i,j}$  and  $\delta_{i,j}$  each are partial accumulations of  $\gamma_{i,j}$ . For simplicity, the rest of this chapter uses either  $\gamma_{i,j}$  or the phrase "an element of C" as a shorthand to refer to any partial result to be accumulated into that element of C, except where a distinction between  $\tau_{i,j}$ ,  $\delta_{i,j}$ , and  $\gamma_{i,j}$  needs to be made.

## 3.3 Lower Bound Proof

In this section we prove that an MMMA must have an I/O cost of at least  $2mnk/\sqrt{S} - 2S$ .

#### 3.3.1 High-level strategy

In order to obtain I/O lower bounds, we will think of computation as being divided into phases, where there are exactly M loads and stores during each phase (except for the last phase). That is to say, each phase has an I/O cost of at most M. If one can prove that there must be at least N phases for any algorithm, then it follows that the algorithm must have a total I/O cost of at least (N-1)M. The -1 term comes from the fact that the last phase may have less than M loads and stores.

How many phases must there be? Since it is a conventional MMMA, we know that mnk FMAs must be executed. Let F be an upper bound on the number of distinct FMAs that can occur during a single phase. Then there must be at least (mnk)/F phases. This gives an overall I/O lower bound of ((mnk)/F - 1)M.

How do we find F? We know that the size of fast memory is S, and there are at most M loads during a single phase. This means that there are S + M elements of A, B, and C that can be used as inputs to FMAs during a phase. Thus placing an upper bound on the number of FMAs that can be computed using S + M elements gives an upper bound on F.

This is nearly the same strategy that was used by [47] and [50]. The important difference is that in the previous papers, the number of loads and stores to and from fast memory per phase is always equal to the size of fast memory, S. We will show that one can achieve greater lower bounds by allowing M to be a value other than S.

#### 3.3.2 Employing the Loomis-Whitney inequality

The Loomis-Whitney inequality [56] was used in [50] to determine how many elementary operations involved in an MMM can be executed with some number of elements.

**Theorem 3.3.1** (Loomis-Whitney). Let m be the measure of an open subset  $\mathcal{O}$  of Euclidean n-space, and let  $m_1, ..., m_n$  be the (n-1)-dimensional measures of the projections of  $\mathcal{O}$  on the coordinate hyper planes. Then  $m^{n-1} \leq m_1 m_2 \cdots m_n$ .

To apply this theorem to our situation, let  $\mathcal{O}$  represent a three dimensional set of some FMAs that occur during an MMMA. Each FMA has a coordinate (i, j, p) in the m, n, and k dimensions:  $\gamma_{i,j} + := \alpha_{i,p}\beta_{p,j}$ . The projection of  $\mathcal{O}$  in each of the m, n, and k dimensions respectively corresponds to the elements of B, A, and C that are inputs to the FMAs in  $\mathcal{O}$ . If F is the number of FMAs that occur during an MMMA using x elements of A, y elements of B, and z elements of C then the Loomis-Whitney inequality tells us that  $F^2 \leq xyz$  and hence  $F \leq \sqrt{xyz}$ .

There are at most S+M elements that can be used as inputs to computation during a phase, because there are at most S elements of A, B, and C in fast memory at the start of the phase and at most M elements read from slow memory during the phase. Similarly there can be at most S+M elements that are outputs of computation during a phase, because there are at most S elements in fast memory at the end of the phase and at most M elements written to slow memory during the phase.

The authors of [50] reason separately about x, y, and z, showing that since there can be at most S+M inputs to computation during phase,  $x \le$

S+M and  $y \leq S+M$ . Similarly, since there can be at most S+M elements written during a phase,  $z \leq S+M$ . Working with FMAs, we do better because we know that the x elements of A, the y elements of B, and the z elements of C must all be inputs to the same phase. Therefore, we can reason about x, y, and z all together:  $x+y+z \leq S+M$ .

The above can be formulated as a constrained maximization problem,

$$\text{maximize } F \text{ under the constraints } \left\{ \begin{array}{c} F \leq \sqrt{xyz} \\ 0 \leq x,y,z \\ x+y+z \leq S+M. \end{array} \right.$$

Application of standard Langrange multiplier methods, detailed in Appendix B, tells us that the global maximum occurs when

$$x = y = z = \frac{S+M}{3}$$

so that  $F = \frac{(S+M)\sqrt{S+M}}{3\sqrt{3}}$ .

## **3.3.3 A** lower bound for C := AB + C

The upper bound on F gives us the following lower bound for the I/O cost of MMMA:

$$\left(\frac{mnk}{F} - 1\right)M = \left(\frac{3\sqrt{3}}{(S+M)\sqrt{S+M}}mnk - 1\right)M.$$

In this lower bound, M is a free variable meaning that different choices for M yield different lower bounds. In [47], [50], and [8], M is always equal to S. If we also make this choice, we obtain the lower bound:

$$\frac{3\sqrt{3}}{2\sqrt{2}}\frac{mnk}{\sqrt{S}} - S.$$

This lower bound can be found in [24].

It is possible to do better still. In order to find the greatest lower bound for any M, our goal is to find the M that maximizes:

$$\max_{M>0} \left( \frac{3\sqrt{3}Mmnk}{(S+M)\sqrt{S+M}} - 1 \right) \approx \max_{M>0} \left( \frac{3\sqrt{3}Mmnk}{(S+M)\sqrt{S+M}} \right)$$

when m, n, and k are large. Standard maximization techniques from calculus yield that the global maximum is attained when M = 2S so that the I/O lower bound (when m, n, and k are large so that the -M term can be ignored) becomes:

$$\left(\frac{3\sqrt{3}mnk}{(S+M)\sqrt{S+M}} - 1\right)M = \left(\frac{3\sqrt{3}mnk}{3S\sqrt{3S}} - 1\right)(2S) = \frac{2mnk}{\sqrt{S}} - 2S.$$

# 3.4 Summary

In this chapter, we proved that the operation C := AB + C where computation must be performed in terms of FMAs, and A, B, and C are distinct must have an I/O cost of at least  $2mnk/\sqrt{S} - 2S$ . Then, C := AB must have an I/O cost of at least  $2mnk/\sqrt{S} - 2S - \mathcal{O}(mn)$ . These lower bounds are of interest by themselves as a theoretical result. In the next chapter, we use them to help gain fundamental insights into how MMM must be implemented.

We believe that the proof techniques presented in this paper apply to algorithms outside of matrix multiplication. Generalizing the size of the phase is one technique that carries over to lower bound proofs that follow the same general strategy for any operation. In the domain of linear algebra, we believe this technique can be used in order to find the best possible constant coefficient for lower bounds as long as the matrix operands are distinct. For matrix operations where the operands are not necessarily distinct, we believe that these techniques can be combined with those from [8] to improve the lower bounds.

While the proof in this chapter only applies to algorithms that use FMA instructions, we hypothesize that it is possible to prove a lower bound with the same  $\frac{2mnk}{\sqrt{S}}$  highest ordered term even when the elementary additions are performed in different ways. In order to prove this to be true, we believe that a different high level proof strategy must be used, because the strategy does not provide a mechanism to reason about long range dependencies, like if a scalar multiplication occurs during a different phase from its corresponding scalar addition.

As a testament to its relevance, we note that techniques from this work have already been used by others [9].

# Chapter 4

# Optimal Algorithms or: The Lower Bound is Tight

## 4.1 Introduction

In Chapter 3, we obtained I/O lower bounds for MMM and MMMA. In this chapter, we use those lower bounds to derive properties of algorithms that could obtain those lower bounds.

From those properties, we derive an algorithm that has an I/O cost where the highest ordered term is the same as that of the lower bound, including its coefficient. We derive two other algorithms that attain the lower bound when ignoring the cost of writing to main memory. The three algorithms are in some sense symmetric to each other and so we say that they form a family of algorithms. We then show which of these algorithms will be favorable for different "shapes" of MMM, that is when different combinations of m, n, and k are large or small.

Portions of this chapter have been previously published as the techincal report [69]. The lower bounds and analysis of algorithms were obtained by the author of this dissertation, and the majority of the text written by him as well. It is under submission to ACM Transactions on Mathematical Software. Bradley Lowery and Julien Langou are to be added as co-authors as they have independently obtained the same result.

# 4.2 Optimal and read-optimal Algorithms

In Chapter 3, we obtained a tight constant on the I/O cost for matrix-matrix multiplication for machines with one level of cache. Assuming that computation is performed in terms of fused multiply-adds (FMAs), matrix-matrix multiplication must have an I/O cost of at least  $\frac{2mnk}{\sqrt{S}}$ , where S is the capacity of the cache. The paper then presents three algorithms for matrix-matrix multiplication. One of these attains the I/O lower bound, and the other two are optimal only in terms of the number of inputs into cache, however they can be considered to be optimal if a read plus a write costs the same as a read.

In this section, we describe and analyze these three algorithms. We discuss how to choose blocksizes for the algorithms. We then show that each of these algorithms is favorable for different shapes of matrix-matrix multiplication.

#### 4.2.1 Algorithms for one level of cache

Matrix-matrix multiplication that casts computations in terms of FMAs requires an I/O cost of least  $\frac{2mnk}{\sqrt{S}}$ . The goal for the algorithms in this section is to incur an I/O cost of only  $\frac{2mnk}{\sqrt{S}}$  plus a quadratic term <sup>1</sup>. To attain this goal, it is sufficient that: (1) each element of one of the operands is read from slow memory once and (2) each element of the other two operands is involved in  $\approx \sqrt{S}$  FMAs each time it is read from slow memory. We now present three algorithms for MMM that attain this goal.

<sup>&</sup>lt;sup>1</sup>Either  $\mathcal{O}(mn)$ ,  $\mathcal{O}(nk)$ , or  $\mathcal{O}(kn)$

Figure 4.1: Three algorithms for matrix multiplication that attain the lower bound for a single level of cache.

**Resident C.** We now describe an algorithm that keeps a block of C resident in fast memory during computation. See the top algorithm illustrated in Figure 4.1. Consider C := AB + C. Partition:

$$C \to \left(\begin{array}{c|c} C_{0,0} & \cdots & C_{0,n-1} \\ \hline \vdots & & \vdots \\ \hline C_{m-1,0} & \cdots & C_{m-1,n-1} \end{array}\right), \quad A \to \left(\begin{array}{c|c} A_0 \\ \hline \vdots \\ \hline A_{m-1} \end{array}\right), \quad B \to \left(B_0 \big| \cdots \big| B_{n-1} \right),$$

where  $C_{i,j}$  is  $m_c \times n_c$ ,  $A_i$  is  $m_c \times k$ , and  $B_j$  is  $k \times n_c$ . Then compute  $C_{i,j} += A_i B_j$  such that  $C_{i,j}$  is read from slow memory once, and then updated with a series of rank-1 updates. During  $C_{i,j} += A_i B_j$ , each element of  $C_{i,j}$ ,  $A_i$ , and  $B_j$  is read from slow memory one time, and each element of  $C_{i,j}$  is written to slow memory once. This gives the following I/O costs for each operand:

- $C_{i,j}$ :  $m_c n_c$  reads and  $m_c n_c$  writes.

- $A_i$ :  $m_c k$  reads.

- $B_i$ :  $kn_c$  reads.

With  $\lceil \frac{m}{m_c} \rceil \lceil \frac{n}{n_c} \rceil$  such  $C_{i,j} += A_i B_j$  suboperations performed during the overall MMM operation C += AB, the total input and output costs associated with each matrix are:

- C: mn reads and mn writes.

- $A: \lceil \frac{mnk}{n_c} \rceil$  reads.

- $B: \lceil \frac{mnk}{m_c} \rceil$  reads.

When  $m_c \approx n_c \approx \sqrt{S}^2$ , the total input cost is  $\frac{2mnk}{\sqrt{S}} + mn$ , and the total output cost is mn. Choosing  $m_c = n_c$  equalizes the input costs associated with A and B, and minimizes  $\lceil \frac{mnk}{n_c} \rceil + \lceil \frac{mnk}{m_c} \rceil$ . The highest ordered term in the cost of the Resident C algorithm is the same as the I/O lower bound for MMM. Thus the algorithm is optimal and the lower bound is tight.

**Resident B.** Another possibility is an algorithm that keeps a block of B resident in fast memory during computation. See the middle algorithm illustrated in Figure 4.1.

Partition:

$$C \to \left( C_0 \middle| \cdots \middle| C_{n-1} \right), \quad A \to \left( A_0 \middle| \cdots \middle| A_{n-1} \right),$$

$$B \to \left( \frac{B_{0,0} \middle| \cdots \middle| B_{0,n-1}}{\vdots \middle| \vdots} \right),$$

$$B_{m-1,0} \middle| \cdots \middle| B_{m-1,n-1} \right),$$

where  $C_j$  is  $m \times n_c$ ,  $A_p$  is  $m \times k_c$ , and  $B_{p,j}$  is  $k_c \times n_c$ .  $C_j += A_p B_{p,j}$  is implemented as a loop over vector-matrix multiplications.

During  $C_j += A_p B_{p,j}$ , each element of  $C_j$ ,  $A_p$ , and  $B_{p,j}$  is read from slow memory one time, and each element of  $C_j$  is written to slow memory once. This gives the following I/O costs for each operand:

- $C_i$ :  $mn_c$  reads and  $mn_c$  writes.

- $A_i$ :  $mk_c$  reads.

- $B_{p,j}$ :  $k_c n_c$  reads.

Note that  $m_c$  and  $n_c$  must be slightly less than  $\sqrt{S}$  so that there is room for a row of  $A_i$  and a column of  $B_j$  in cache.

With  $\lceil \frac{k}{k_c} \rceil \lceil \frac{n}{n_c} \rceil$  such  $C_j += A_p B_{p,j}$  suboperations performed during the overall MMM operation C += AB, the total input and output costs associated with each matrix are:

- $C: \lceil \frac{mnk}{k_c} \rceil$  reads and  $\lceil \frac{mnk}{k_c} \rceil$  writes.

- $A: \lceil \frac{mnk}{n_c} \rceil$  reads.

- B: nk reads.

If  $k_c \approx n_c \approx \sqrt{S}$ , the input cost is approximately  $\frac{2mnk}{\sqrt{S}} + nk$ , and the output cost is approximately  $\frac{mnk}{\sqrt{S}}$ . The input cost now attains near the I/O lower bound.

**Resident A.** A third possibility is an algorithm that keeps a block of A resident in fast memory during computation, as illustrated in Figure 4.1.

Partition:

$$C \to \left(\frac{C_0}{\vdots \atop C_{m-1}}\right), \quad A \to \left(\frac{A_{0,0} \mid \cdots \mid A_{0,k-1}}{\vdots \mid \qquad \vdots \atop A_{m-1,0} \mid \cdots \mid A_{m-1,k-1}}\right), \quad B \to \left(\frac{B_0}{\vdots \atop B_{k-1}}\right),$$

where  $C_i$  is  $m_c \times n$ ,  $A_{i,p}$  is  $m_c \times k_c$ , and  $B_p$  is  $k_c \times n$ .  $C_i += A_{i,p}B_p$  is implemented as a loop over matrix-vector multiplications.

During  $C_i += A_{i,p}B_p$ , each element of  $C_i$ ,  $A_{i,p}$ , and  $B_p$  is read from slow memory one time, and each element of  $C_i$  is written to slow memory once. This gives the following I/O costs for each operand:

- $C_i$ :  $m_c n$  reads and  $m_c n$  writes.

- $A_{i,n}$ :  $m_c k_c$  reads.

•  $B_p$ :  $k_c n$  reads.

With  $\lceil \frac{m}{m_c} \rceil \lceil \frac{k}{k_c} \rceil$  such  $C_i += A_{i,p} B_p$  suboperations performed during the overall MMM operation C += AB, the total input and output costs associated with each matrix are:

- C:  $\lceil \frac{mnk}{k_c} \rceil$  reads and  $\lceil \frac{mnk}{k_c} \rceil$  writes.

- A: mk reads.

- $B: \lceil \frac{mnk}{m_c} \rceil$  reads.

If  $m_c \approx k_c \approx \sqrt{S}$ , the input cost is approximately  $\frac{2mnk}{\sqrt{S}} + mk$ , and the output cost is approximately  $\frac{mnk}{\sqrt{S}}$ . The input cost attains near the I/O lower bound.

**Discussion.** These three algorithms and the shapes of the subproblems exposed by them have been described before, however their optimality has not been able to be analyzed in the context of the  $\frac{2mnk}{\sqrt{S}}$  lower bound before now. The Resident A algorithm was described as early as 1991 [53], and each of Resident A, Resident B, and Resident C appears in [41].

## 4.2.2 Algorithms for different shapes of MMM

The number of reads and writes from slow memory during the algorithms Resident A, Resident B, and Resident C depend on the shape of the input matrices. There are cases where one of the algorithms is more efficient than the other two, where we define efficiency by flops per I/O cost. The higher this value is, the more efficient the algorithm is. There are 2mnk flops performed during MMM, and the I/O lower bound is  $\frac{2mnk}{\sqrt{S}}$ . Thus our goal

for efficiency is  $\sqrt{S}$  flops per I/O. We will now examine the cases for which algorithms are efficient, assuming that m, n, and k are at least  $\sqrt{S}$ .

Resident C is efficient if and only if k is large. The Resident C algorithm reads  $\lceil \frac{mnk}{n_c} \rceil + \lceil \frac{mnk}{m_c} \rceil + mn$  elements from slow memory during MMM. If  $m_c = n_c = \sqrt{S}$ , this is approximately  $\frac{2mnk}{\sqrt{S}} + mn$ . This gives an efficiency of  $\left(\frac{1}{\sqrt{S}} + \frac{mn}{2k}\right)^{-1}$ . When k is large, this is approximately  $\sqrt{S}$ .

We can analyze Resident A and Resident B similarly. Here we ignore the I/O cost for writes. If the blocksizes are chosen to be equal to  $\sqrt{S}$ , Resident B has an efficiency of  $\left(\frac{1}{\sqrt{S}} + \frac{nk}{2m}\right)^{-1}$ , which is approximately  $\sqrt{S}$  when m is large. Resident A has an efficiency of  $\left(\frac{1}{\sqrt{S}} + \frac{mk}{2n}\right)^{-1}$ , which is approximately  $\sqrt{S}$  when n is large.

This shows that one must choose the right algorithm depending on the shape of the problem. For each of Resident A, Resident B, and Resident C, there is a minimal shape that can be implemented efficiently. For Resident C it is when m and n are  $\approx \sqrt{S}$ , and k is large. For Resident B it is when k and n are n are n are n are n are n are n and n is large. For Resident A it is when n and n are n and n is large. In each of these cases, the resident matrix must fit into fast memory, and the "other dimension" must be large so that the cost of moving the resident matrix into fast memory can be amortized. In fact, these minimal shapes are the exact shapes that are exposed by each of the algorithms after they have been partitioned by their outer two loops. Because these problems are the smallest, most basic problems that can be implemented efficiently, and because they are the same problem shapes that are exposed by the algorithms, we call these problem shapes optimal subproblems.

The fact that one must choose a different algorithm for MMM depend-

ing on problem shape and size has been noted before for distributed memory MMM [66, 55], and for hierarchical memory MMM [41, 83], but our analysis of the algorithms in terms of the tight I/O lower bounds is novel. In practice, shapes of MMM where one or two dimensions are small often arise as subproblems during matrix factorizations [40, 5]. Outside of DLA, other applications may use highly skewed matrix-matrix multiplication. In quantum chemistry, coupled cluster applications use tensors of one to eight dimensions, and from hundreds of bytes to hundreds of gigabytes in size [10]. Tensor contractions on these tensors, which are equivalent to MMM under permutations, range widely in size and shape as well, with contractions varying from perfectly "square" (m=n=k) to highly skewed, with ratios between m, n, and k as high as 10000 in higher-order coupled cluster methods [62].

## 4.2.3 A balancing act

In the previous parts of this section, we have assumed that I/O costs associated with all three matrices are equal. We analyzed algorithms assuming that a read and a write costs the same as a read, and we only looked at the read costs of all three algorithms.

In doing so, we reached the conclusion that we should take the following strategy for the algorithms Resident A, Resident B, and Resident C: Place a square block of the resident matrix in fast memory, and stream the other two operands through fast memory. This amortizes the I/O costs associated with the resident matrix, and equalizes the I/O costs associated with the streamed matrices.

What if the operands are not symmetric in terms of I/O costs? Suppose accessing elements of one of the matrices is more expensive than accessing

elements of another. For instance, accessing elements of C may be inherently more expensive than accessing elements of A or B, since elements of C must be read and written. In this case, it may make sense to use the algorithm that has the expensive matrix reside in fast memory.