Copyright by Jungrae Kim 2016

# The Dissertation Committee for Jungrae Kim certifies that this is the approved version of the following dissertation:

# Strong, Thorough, and Efficient Memory Protection against Existing and Emerging DRAM Errors

| Committee:              |

|-------------------------|

|                         |

| Mattan Erez, Supervisor |

| Yale Patt               |

| Tate 1 and              |

| Nur Touba               |

|                         |

| Calvin Lin              |

| Alaa Alameldeen         |

# Strong, Thorough, and Efficient Memory Protection against Existing and Emerging DRAM Errors

by

Jungrae Kim, B.S.E., M.S.

### DISSERTATION

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

#### DOCTOR OF PHILOSOPHY

To loving parents,

Namho Kim and Eunsung Lee,

for their endless love, support, and encouragement.

# Acknowledgments

First of all, I thank my great advisor, Professor Mattan Erez. Mattan is my role model as an open-minded, hard-working, and brilliant researcher. He kept encouraging me to develop new research ideas with in-depth discussion and rigorous feedback. I was fortunate to have him as my advisor and enjoyed working with him over the past 5 years.

I also would like to thank the other members of my dissertation committee: Professor Yale N. Patt, Professor Nur A. Touba, Professor Calvin Lin, and Dr. Alaa Alameldeen. Their valuable comments helped me develop and elaborate the concepts in my dissertation.

I thank Seh-Woong Jeong, Jaehong Park, Young Jun Kwon, Kyung-Mook Lim, Jinpyo Park, Joonseok Kim, Nak Hee Seong, Yoonhwan Kim, Suknam Kwon, and Sangyoon Lee at Samsung Electronics. I learned various aspects of computing systems from them and am proud to have been a member of a team which changed daily lives of the mankind. I am also thankful to the company for supporting my Ph.D study.

I am also thankful to Min Kyu Jeong, Ikhwan Lee, Joonsoo Kim, and Dam Sunwoo for their friendship. From the day one in Austin, their help and support made me and my family stand here. I also should acknowledge other friends in the LPH research group: Michael Sullivan, Dong Wan Kim, Jinsuk Chung, Minsoo Rhu, Seong-Lyong Gong, Tianhao Zheng, Song Zhang, Haishan Zhu, Esha Choukse, Sangkug Lym, Yongkee Kwon, Kyushick Lee, Benjamin Cho, and Nicholas Kelly. They gave me invaluable comments and feedback to my research and papers, and I would not have completed my Ph.D. research without their help; especially Mike, who collaborated on all of my papers.

Finally, I want to thank my family for their consistent support and endless love. Very special thanks to my wife, Sun Young Hwang; she has been supportive throughout the years and made my life full of joy with three loving children; Dana Dongha Kim, Julia Dongjoo Kim, and Justin Kim.

Strong, Thorough, and Efficient Memory Protection against Existing and Emerging DRAM Errors

Publication No.

Jungrae Kim, Ph.D.

The University of Texas at Austin, 2016

Supervisor: Mattan Erez

Memory protection is necessary to ensure the correctness of data in the presence of unavoidable faults. As such, large-scale systems typically employ Error Correcting Codes (ECC) to trade off redundant storage and bandwidth for increased reliability. Single Device Data Correction (SDDC) ECC mechanisms are required to meet the reliability demands of servers and large-scale systems by tolerating even severe faults that disable an entire memory chip.

In the future, however, stronger memory protection will be required due to increasing levels of system integration, shrinking process technology, and growing transfer rates. The energy-efficiency of memory protection is also important as DRAM already consumes a significant fraction of system energy budget. This dissertation develops a novel set of ECC schemes to provide strong, safe, flexible, and thorough protection against existing and emerging types of DRAM errors. This research also reduces energy consumption of such protection while only marginally impacting performance.

First, this dissertation develops Bamboo ECC, a technique with stronger-than-SDDC correction and very safe detection capabilities ( $\geq$  99.999994% of data errors with any severity are detected). Bamboo ECC changes ECC layout based on frequent DRAM error patterns, and can correct concurrent errors from multiple devices and all but eliminates the risk of silent data corruption. Also, Bamboo ECC provides flexible configurations to enable more adaptive graceful downgrade schemes in which the system continues to operate correctly after even severe chip faults, albeit at a reduced capacity to protect against future faults. These strength, safety, and flexibility advantages translate to a significantly more reliable memory sub-system for future exascale computing.

Then, this dissertation focuses on emerging error types from scaling process technology and increasing data bandwidth. As DRAM process technology scales down to below 10nm, DRAM cells are becoming more vulnerable to errors from an imperfect manufacturing process. At the same time, DRAM signal transfers are getting more susceptible to timing and electrical noises as DRAM interfaces keep increasing signal transfer rates and decreasing I/O voltage levels. With individual DRAM chips getting more vulnerable to errors, industry and academia have proposed mechanisms to tolerate these emerging types of errors; yet they are inefficient because they rely on multiple levels of redundancy in the case of cell errors and ad-hoc schemes with suboptimal protection coverage for transmission errors. Active Guardband ECC and All-Inclusive ECC make systematic use of ECC and existing mechanisms to provide thorough end-to-end protection without requiring redundancy beyond

what is common today.

Finally, this dissertation targets the energy efficiency of memory protection. Frugal ECC combines ECC with fine-grained compression to provide versatile and energy-efficient protection. Frugal ECC compresses main memory at cache-block granularity, using any left over space to store ECC information. Frugal ECC allows more energy-efficient memory configurations while maintaining SDDC protection. Its tailored compression scheme minimizes insufficiently compressed blocks and results in acceptable performance overhead.

The strong, thorough, and efficient protection described by this dissertation may allow for more aggressive design of future computing systems with larger integration, finer process technology, higher transfer rates, and better energy efficiency.

# **Table of Contents**

| Ackno   | wledg  | ments                                                    | V   |

|---------|--------|----------------------------------------------------------|-----|

| Abstra  | ct     |                                                          | vii |

| List of | Table  | es                                                       | xiv |

| List of | Figu   | res                                                      | xv  |

| Chapte  | er 1.  | Introduction                                             | 1   |

| 1.1     | Error  | s with Growing System Sizes                              | 2   |

|         | 1.1.1  | Limitations of Current SDDC Protection                   | 3   |

|         | 1.1.2  | Contribution w.r.t. Errors in Future Large-Scale Systems | 4   |

| 1.2     | Error  | s from Less-Reliable Process Technology                  | 4   |

|         | 1.2.1  | In-DRAM ECC Protection                                   | 5   |

|         | 1.2.2  | Limitations of In-DRAM ECC                               | 5   |

|         | 1.2.3  | Contribution w.r.t. Scaling-Induced Errors               | 6   |

| 1.3     | Error  | s from Less-Reliable Transfers                           | 6   |

|         | 1.3.1  | Current Transmission Protection                          | 8   |

|         | 1.3.2  | Limitations of Current Transmission Protection           | 9   |

|         | 1.3.3  | Contribution w.r.t. Transmission Errors                  | 10  |

| 1.4     | Prote  | ction Energy Efficiency                                  | 10  |

|         | 1.4.1  | Limitations of Current Protection                        | 11  |

|         | 1.4.2  | Contribution w.r.t. Energy Efficiency                    | 11  |

| 1.5     | Disser | rtation Organization                                     | 13  |

| Chapte  | er 2.  | Background                                               | 14  |

| 2.1     | Relial | bility Concepts                                          | 14  |

| 2.2     | DRA    | M                                                        | 17  |

| 2.3     | Error  | Correcting Codes                                         | 18  |

| Chapte | er 3. Data Errors Protection Mechanisms                  | <b>2</b> 2 |

|--------|----------------------------------------------------------|------------|

| 3.1    | Data Error Patterns                                      | 23         |

| 3.2    | ECC Detection Coverage                                   | 24         |

| 3.3    | Bamboo ECC                                               | 28         |

|        | 3.3.1 Organizations                                      | 29         |

|        | 3.3.1.1 Single Pin Correcting ECC                        | 29         |

|        | 3.3.1.2 Single Pin Correcting – Triple Pin Detecting ECC | 30         |

|        | 3.3.1.3 Quadruple Pin Correcting ECC                     | 32         |

|        | 3.3.1.4 Octuple Pin Correcting ECC                       | 33         |

|        | 3.3.2 Graceful Downgrade                                 | 33         |

|        | 3.3.3 Overheads                                          | 35         |

| 3.4    | Evaluation                                               | 38         |

|        | 3.4.1 Error Coverage Evaluation                          | 39         |

|        | 3.4.2 System Reliability                                 | 43         |

|        | 3.4.3 Performance and Energy                             | 49         |

| 3.5    | Related Work                                             | 50         |

| 3.6    | Summary                                                  | 56         |

| Chapte | er 4. Mechanisms against Manufacturing Faults            | 57         |

| 4.1    | DRAM Faults from Process Scaling                         | 58         |

| 4.2    | In-DRAM ECC                                              | 59         |

| 4.3    | ECC Guardband                                            | 62         |

|        | 4.3.1 Strict ECC Guardband                               | 63         |

|        | 4.3.2 Zero ECC Guardband                                 | 64         |

|        | 4.3.3 Active ECC Guardband                               | 65         |

| 4.4    | Active Guardband QPC ECC                                 | 68         |

|        | 4.4.1 ECC decoding                                       | 69         |

|        | 4.4.2 Fault Diagnosis and Erasure Decoding               | 71         |

|        | 4.4.3 Remapping                                          | 72         |

|        | 4.4.4 Overheads                                          | 73         |

| 4.5    | Evaluation                                               | 74         |

|        | 451 Manufacturability                                    | 75         |

|       | 4.5.2  | System Reliability                                     | 78   |

|-------|--------|--------------------------------------------------------|------|

|       | 4.5.3  | Performance and Energy                                 | 82   |

| 4.6   | Relate | ed Work                                                | 85   |

| 4.7   | Sumn   | nary                                                   | 88   |

| Chapt | er 5.  | Mechanisms against Command/Address Errors              | 89   |

| 5.1   | DRA    | M Transmission Errors                                  | 90   |

| 5.2   | Curre  | ent DRAM Practices                                     | 94   |

|       | 5.2.1  | DDR4 CCCA Signals                                      | 94   |

|       | 5.2.2  | DDR4 Reliability Features                              | 95   |

| 5.3   | All-In | aclusive ECC                                           | 97   |

|       | 5.3.1  | Extended Data ECC for Address Protection               | 98   |

|       | 5.3.2  | Extended Write CRC for Timely Write Address Protection | n100 |

|       | 5.3.3  | State and Timing Checker for Command Protection        | 101  |

|       | 5.3.4  | Extended CA Parity (eCAP)                              | 104  |

|       | 5.3.5  | Clock and Control Protection                           | 105  |

|       | 5.3.6  | Precise Diagnosis                                      | 105  |

|       | 5.3.7  | Correction Details                                     | 105  |

| 5.4   | Evalu  | ation                                                  | 106  |

|       | 5.4.1  | CCCA Reliability                                       | 107  |

|       |        | 5.4.1.1 Impact of undetected CCCA errors               | 108  |

|       |        | 5.4.1.2 Detection Coverage                             | 109  |

|       | 5.4.2  | Data Reliability                                       | 112  |

|       | 5.4.3  | System Reliability                                     | 113  |

|       | 5.4.4  | Hardware Overheads                                     | 117  |

| 5.5   | Relate | ed Work                                                | 118  |

| 5.6   | Sumn   | nary                                                   | 121  |

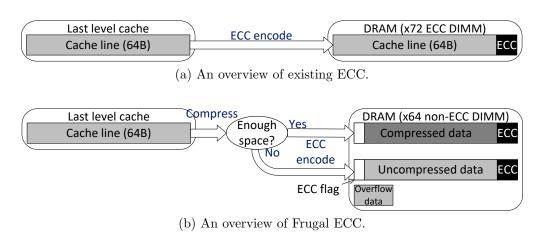

| Chapt | er 6.  | Efficient Protection using Compression                 | 123  |

| 6.1   | Fruga  | al ECC                                                 | 124  |

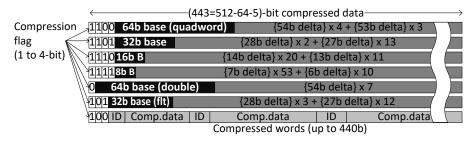

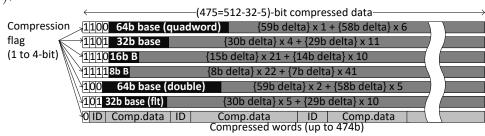

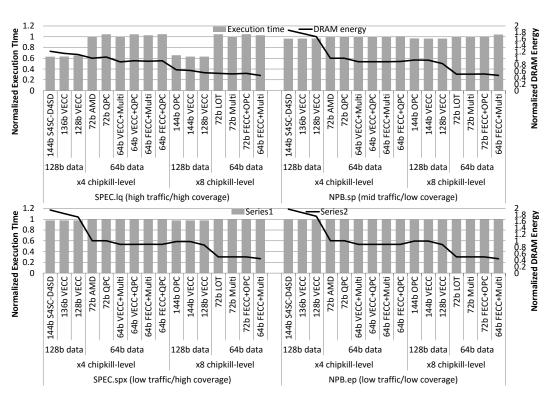

| 6.2   | Cover  | rage-oriented Compression                              | 127  |

|       | 6.2.1  | Fitting Base + Delta Compression                       | 128  |

|       | 622    | Floating-point Compression                             | 130  |

|         | 6.2.3  | Frequent Word Compression | 131 |

|---------|--------|---------------------------|-----|

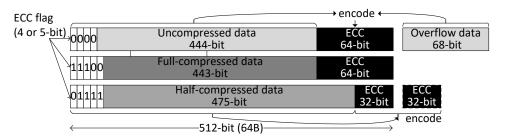

| 6.3     | ECC    | Flag Protection           | 132 |

| 6.4     | Fruga  | l ECC Organizations       | 133 |

|         | 6.4.1  | Frugal ECC for x4 SDDC    | 133 |

|         | 6.4.2  | Frugal ECC for ×8 SDDC    | 137 |

| 6.5     | Evalu  | ation                     | 137 |

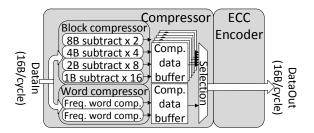

|         | 6.5.1  | Reliability               | 139 |

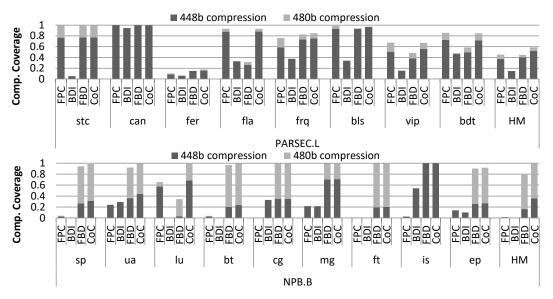

|         | 6.5.2  | Compression Coverage      | 141 |

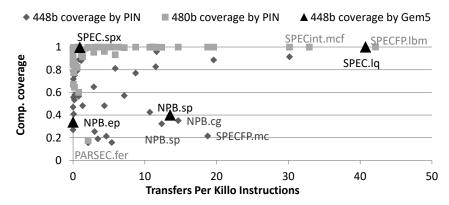

|         | 6.5.3  | Performance and Energy    | 145 |

|         | 6.5.4  | Hardware Overheads        | 148 |

| 6.6     | Relate | ed Work                   | 151 |

|         | 6.6.1  | Efficient ECC             | 151 |

|         | 6.6.2  | Memory Compression        | 153 |

| 6.7     | Sumn   | nary                      | 156 |

| Chapte  | er 7.  | Conclusion                | 157 |

| 7.1     | Futur  | e Research Directions     | 159 |

| Bibliog | graphy | 7                         | 161 |

| Vita    |        |                           | 186 |

# List of Tables

| 2.1 | Examples of ECCs with different distances                                                                                | 20  |

|-----|--------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | DRAM fault rates (in FIT) observed on the Jaguar supercomputer with 73K DDR2 DIMMs                                       | 25  |

| 3.2 | A comparison of the protection coverage of bit-level ECCs                                                                | 41  |

| 3.3 | A comparison of the protection coverage of SDDC ECCs with $\times 4$ and $\times 8$ DRAM devices                         | 42  |

| 4.1 | Traditional approaches for high reliability and high manufacturability.                                                  | 59  |

| 4.2 | A comparison of protection coverage using different QPC post-processing schemes                                          | 70  |

| 4.3 | The performance/energy simulation parameters of AG-ECC                                                                   | 83  |

| 5.1 | DDR4 DRAM commands with their allowed bank state and timing constraints                                                  | 103 |

| 5.2 | The impact of 1-pin CCCA errors across pin locations and commands                                                        | 108 |

| 5.3 | A comparison of the data and address protection coverage of Bamboo QPC with and without address protection               | 112 |

| 5.4 | Representative benchmark clusters and their bandwidths                                                                   | 114 |

| 5.5 | An evaluation of mean time to CCCA SDC failure on systems with 1.2M and 36M DRAM devices and high bandwidth utilization. | 116 |

| 6.1 | The frequent word compression mappings (per 64-bit data)                                                                 | 132 |

| 6.2 | A comparison of different SDDC and SDDC-level ECCs for ×4                                                                | 102 |

| 0.2 | devices over a 64-bit data channel                                                                                       | 134 |

| 6.3 | A comparison of different SDDC and SDDC-level ECCs for $\times 8$ devices                                                | 136 |

| 6.4 | The simulation parameters for the performance and energy evaluation                                                      | 147 |

# List of Figures

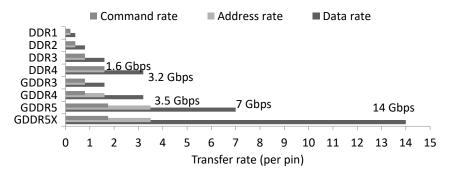

| 1.1  | The increasing DRAM transfer rates of command, address, and data signals over the past 15 years                       | 7  |

|------|-----------------------------------------------------------------------------------------------------------------------|----|

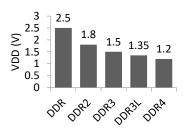

| 1.2  | The decreasing DRAM supply voltage levels                                                                             | 7  |

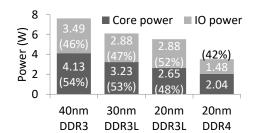

| 1.3  | DRAM power breakdown over core and I/O                                                                                | 7  |

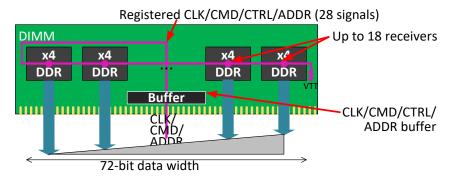

| 1.4  | The standard fly-by topology of DDR4 registered DIMM                                                                  | 8  |

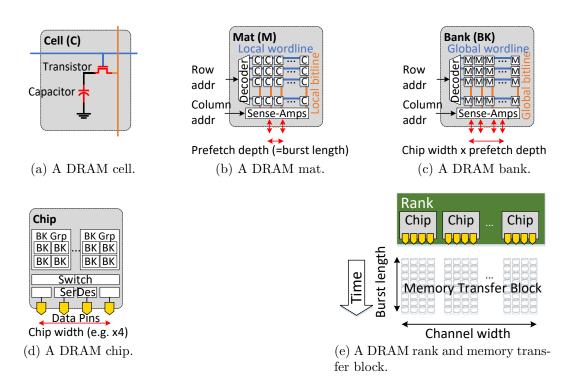

| 2.1  | The hierarchical organization of DRAM                                                                                 | 16 |

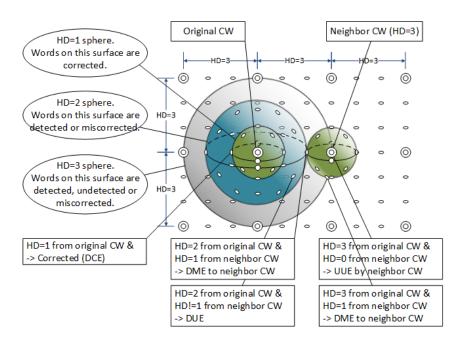

| 3.1  | Conceptual codespace of single symbol correcting codes                                                                | 26 |

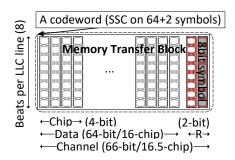

| 3.2  | Single Pin Correcting Bamboo ECC on $(64+2)$ -bit channel                                                             | 30 |

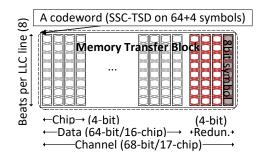

| 3.3  | Single Pin Correcting – Triple Pin Detecting Bamboo ECC on (64+4)-bit channel                                         | 31 |

| 3.4  | Quadruple Pin Correcting Bamboo ECC on (64+8)-bit channel                                                             | 31 |

| 3.5  | Octuple Pin Correcting Bamboo ECC on a (128+16)-bit channel.                                                          | 33 |

| 3.6  | The protection coverage and system reliability evaluation environment                                                 | 39 |

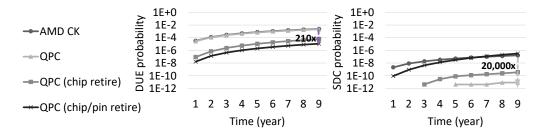

| 3.7  | The failure probability of a DDR 64-bit data channel over time with different bit-level protection mechanisms         | 44 |

| 3.8  | The failure probability of a DDR 64-bit data channel over time with different SDDC protection mechanisms              | 45 |

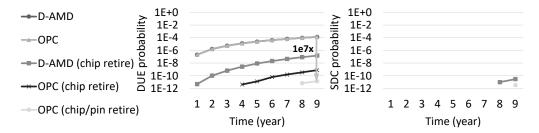

| 3.9  | The failure probability of a DDR 128-bit data channel with different DDDC protection mechanisms                       | 46 |

| 3.10 | The failure probability of a large system with 1,000,000 channels over time with different SDDC protection mechanisms | 47 |

| 3.11 | The failure probability of a large system with 1,000,000 channels over time with different DDDC protection mechanisms | 48 |

| 3.12 | The execution time slowdown of Bamboo ECC schemes (normalized to AMD chipkill)                                        | 50 |

| 3.13 | The SEC-DED codeword over $(64+8)$ -bit channel / 1-beat                                                              | 51 |

| 3.14 | The interleaving of 4 SEC-DED codewords over 288 bit channel / 1-beat                                                 | 51 |

| 3.15 | The interleaving of 2 SEC-DAEC codewords over 144 bit channel / 1-beat                                   | 52  |

|------|----------------------------------------------------------------------------------------------------------|-----|

| 3.16 | The 4-bit Symbol SDDC (SSC-DSD) over (128+16)-bit channel / 1-beat                                       | 53  |

| 3.17 | The 8-bit Symbol SDDC (SSC) over (64+8)-bit channel / 2-beat.                                            | 54  |

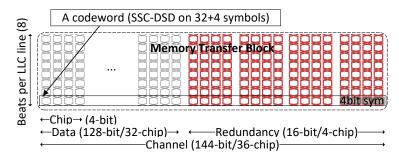

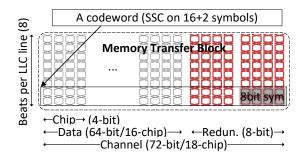

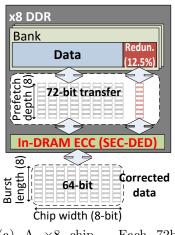

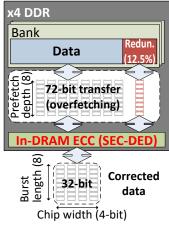

| 4.1  | In-DRAM ECC for DRAM chips with different data interface widths but the same 12.5% redundancy.           | 61  |

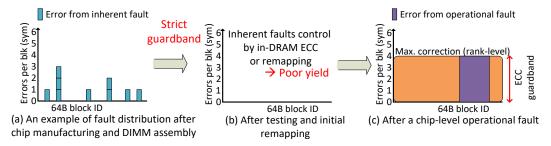

| 4.2  | A strict ECC guardband example with QPC Bamboo ECC                                                       | 63  |

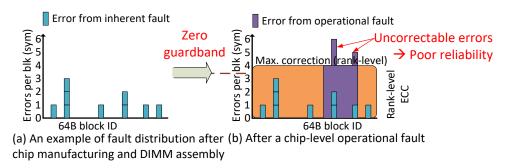

| 4.3  | A zero ECC guardband example with QPC Bamboo ECC. $$ .                                                   | 64  |

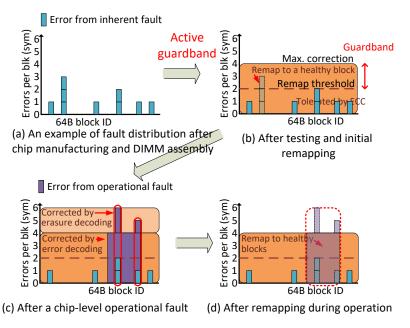

| 4.4  | An active ECC guardband example with QPC Bamboo ECC.                                                     | 68  |

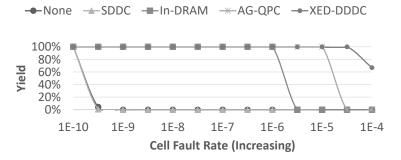

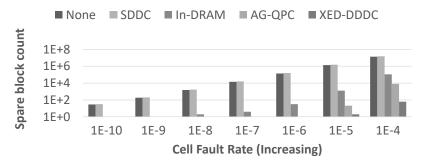

| 4.5  | A comparison of $16GB$ DIMM yields using different ECC schemes and varying cell fault rates              | 76  |

| 4.6  | A comparison of the number of spare 64B blocks needed to achieve 99.99% yield on $16GB$ DIMMs            | 77  |

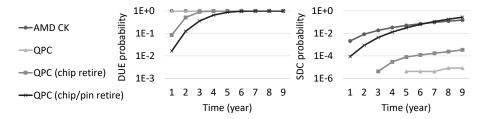

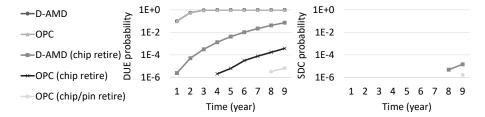

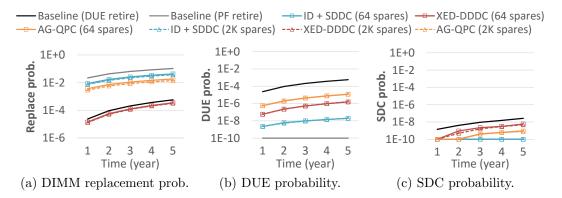

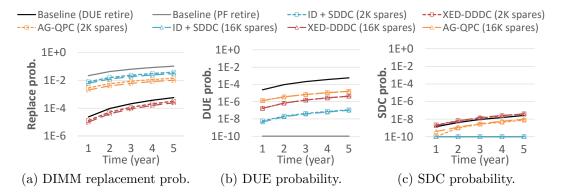

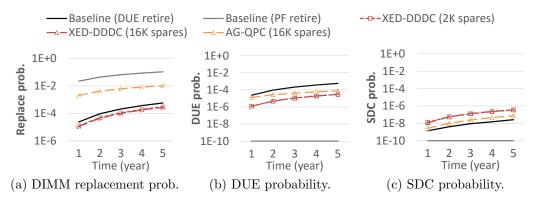

| 4.7  | The reliability of a 2-rank DRAM channel against both inherent and operational faults (CFR = $10^{-6}$ ) | 80  |

| 4.8  | The reliability of a 2-rank DRAM channel against both inherent and operational faults (CFR = $10^{-5}$ ) | 81  |

| 4.9  | The reliability of a 2-rank DRAM channel against both inherent and operational faults (CFR = $10^{-4}$ ) | 81  |

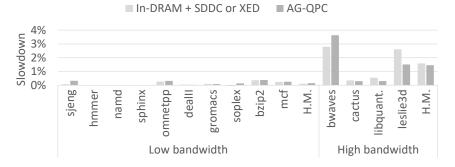

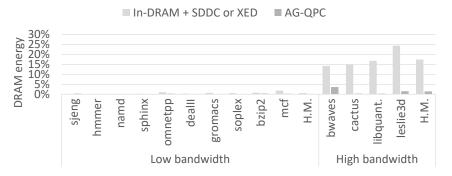

| 4.10 | A comparison of the IPC slowdown comparison between AG-QPC and in-DRAM-ECC-based schemes                 | 84  |

| 4.11 | A comparison of the DRAM energy efficiency between AG-QPC and in-DRAM-ECC-based schemes                  | 85  |

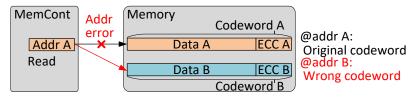

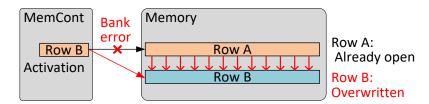

| 5.1  | A read address error example                                                                             | 91  |

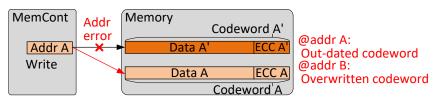

| 5.2  | A write address error example                                                                            | 91  |

| 5.3  | A command error example (duplicate activations)                                                          | 92  |

| 5.4  | The CCCA signal interface for DDR4 memory                                                                | 94  |

| 5.5  | The reliability features available with DDR4                                                             | 96  |

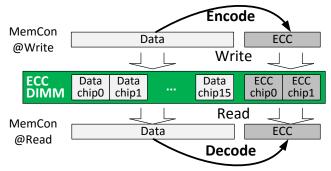

| 5.6  | A visualization of the extended Data ECC (eDECC) mechanisms.                                             | 99  |

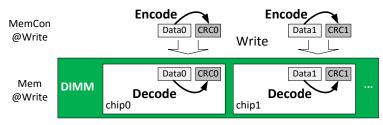

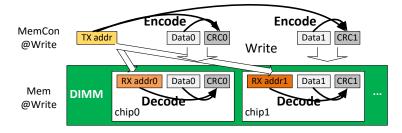

| 5.7  | An overview of the Extended Write CRC (eWCRC)                                                            | 101 |

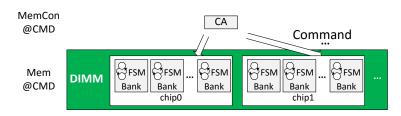

| 5.8  | An overview of the Command State and Timing Checker                                                      | 101 |

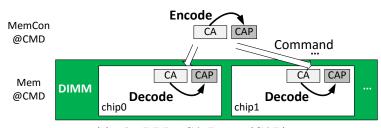

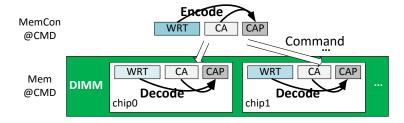

| 5.9  | An overview of the Extended CA Parity (eCAP)                                                             | 104 |

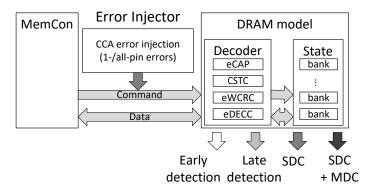

| 5.10 | The CCCA reliability evaluation environment                                                              | 106 |

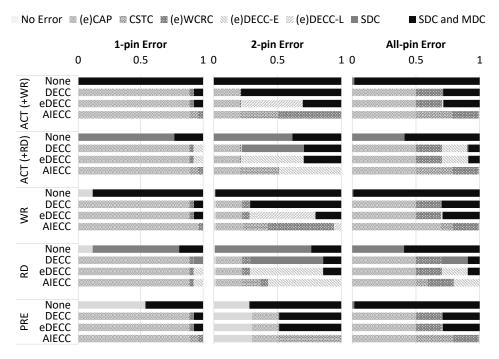

| 5.11 | The CCCA error detection coverage of an unprotected DDR4 DIMM (None), DDR4+DECC (DECC), DDR4+eDECC (eDECC and DDR4+AIECC (AIECC)                                                                          | ),<br>110 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 5.12 | A quantitative evaluation of the different AI-ECC components: eDECC, eWCRC, address protection (eDECC+eWCRC), CSTC, eCAP, command protection (CSTC+eCAP), eDECC+eWCRC+eCAP (for completeness), and AI-ECC | 111       |

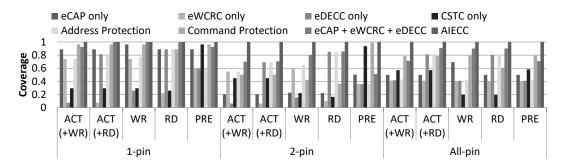

| 5.13 | An estimation on $\times 4$ DRAM CCCA FIT rates after protection with $10^{-22}$ BER                                                                                                                      | 115       |

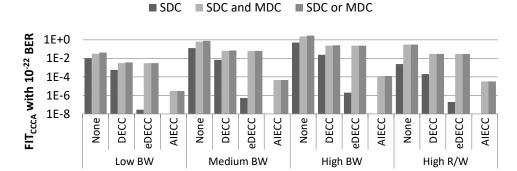

| 6.1  | A comparison between Frugal ECC and existing ECC                                                                                                                                                          | 124       |

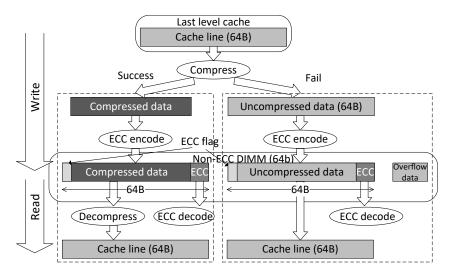

| 6.2  | Memory reads and writes with Frugal ECC using a 64-bit non-ECC DIMM                                                                                                                                       | 125       |

| 6.3  | The compressed data layout for the 448-bit target (64-bit redundancy)                                                                                                                                     | 128       |

| 6.4  | The compressed data layout for the 480-bit target (32-bit redundancy)                                                                                                                                     | 128       |

| 6.5  | The Frugal ECC layout for AMD chipkill and QPC Bamboo ECC (64-bit redundancy)                                                                                                                             | 134       |

| 6.6  | The Frugal ECC layout for $\times 4$ Multi-ECC (32-bit redundancy).                                                                                                                                       | 134       |

| 6.7  | Probabilities of a DUE and SDC for a single rank with 1 or 2-chip errors                                                                                                                                  | 140       |

| 6.8  | Probabilities of a DUE and SDC for a system with 100K DIMMs, assuming only 1 or 2-chip errors                                                                                                             | 140       |

| 6.9  | An evaluation on CoC compression coverage for 64-bit and 32-bit redundancy                                                                                                                                | 142       |

| 6.10 | A compression coverage comparison between CoC and prior memory compression schemes                                                                                                                        | 144       |

| 6.11 | The memory traffic and compression coverage results of all benchmarks measured with Pin and the four representative detailed simulations selected                                                         | 145       |

| 6.12 | A comparison of execution time and DRAM energy consumption (normalized to AMD chipkill)                                                                                                                   | 149       |

| 6.13 | A block diagram of the CoC compressor                                                                                                                                                                     | 149       |

# Chapter 1

## Introduction

DRAM errors are not rare. Field measurements show that a DRAM Dual Inline Memory Module (DIMM) suffers from an average of 0.65 – 330 errors per month [122, 48, 128, 129, 93, 127]. In large-scale systems with tens of thousands of DIMMs, these numbers translate into significant system-wide error rates. On the Jaguar supercomputer with 18K nodes and 73K DDR2 DIMMs, there are 250,000 DRAM errors per month on average, or there is a DRAM error once every 10 seconds [128]. With such frequent errors, the output of a large-scale computation is unreliable and the reliability of main memory has become a significant and growing concern of system designers and operators.

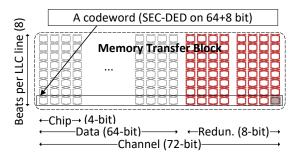

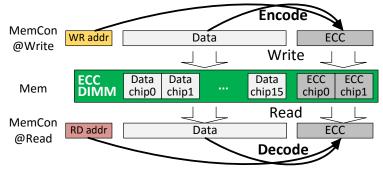

Large-scale systems, datacenters, and business-critical servers currently employ Error Correcting Codes (ECC), which trade off redundant storage and bandwidth for improved reliability. The most widely known ECC is Single Error Correcting — Double Error Detecting (SEC-DED), which can correct all 1-bit errors and detect all 2-bit errors. On 64-bit data, 8-bit redundancy is added for SEC-DED. The standard ECC DIMM has 8 redundant pins with 64 data pins, resulting in 12.5% redundant storage and transfer.

Highly reliable systems require stronger levels of protection. Single Device Data Correction (SDDC) ECC<sup>1</sup> can restore data of a dead chip and can tolerate more severe errors than SEC-DED. Field analyses report that SDDC significantly improves memory reliability by correcting 99.94% of all errors, compared to 91% with SEC-DED [50], and achieves a 42× better uncorrected DRAM error rate than SEC-DED [128]. Recent SDDC implementations use the same ECC DIMMs originally designed for SEC-DED [9].

While SDDC protection brings needed reliability improvements to current large-scale systems, future systems will require even stronger error correction and detection capabilities due to three main reasons: growing system sizes, less-reliable process technology, and increasing transmission error rates. Also, energy-efficiency of protection is important because ECC costs extra chips that consume a significant portion of a system's energy budget. Furthermore, ECC often necessitates energy-inefficient configurations. The following sections briefly describe these DRAM reliability challenges, current approaches that address those challenges, limitations of these current approaches, and the contributions of this dissertation.

# 1.1 Errors with Growing System Sizes

The number of DRAM devices per system is rapidly growing to support exploding data volumes and computation throughput. The U.S. Department of

<sup>&</sup>lt;sup>1</sup>SDDC is referred to as Chipkill, extended ECC, and ChipSpare protection by IBM, Sun (now Oracle), and HP, respectively [9, 53, 108, 42].

Energy expects exascale supercomputers, which are capable of a billion billion calculations per second, to be available by 2024 [94]. Such supercomputers may employ millions of DRAM DIMMs for more than 128 peta bytes of main memory [124]; this number of DRAM devices is 32× greater than the top supercomputer in 2016 [139].

#### 1.1.1 Limitations of Current SDDC Protection

The correction and detection strength of current SDDC protection may not be sufficient to deal with the growing system integration levels and their higher error rates. The mean time between uncorrectable errors in current systems with SDDC protection is as low as 9 days [93]. Without a stronger correction capability, future systems will suffer from degraded system-level reliability with an uncorrectable error every few hours.

The detection capability of a protection scheme is as important as its correction capability in large-scale computing. ECC has limited correction capability due to physical constraints (e.g., the amount of redundancy) and large-scale systems typically employ runtime support (e.g., checkpoint and restart [38, 27]) to correct rare ECC-uncorrectable errors. Such schemes mostly rely on ECC detection capability to trigger the state-restoration procedure so that uncorrectable errors, if any, should at least be detected by ECC to prevent applications from producing incorrect results. Despite the importance of detection, some SDDC implementations trade off detection capability for improved efficiency, missing up to 1.4% of double-chip-errors (Section 3.4).

#### 1.1.2 Contribution w.r.t. Errors in Future Large-Scale Systems

This dissertation presents a novel family of efficient ECC mechanisms for future large-scale systems. Bamboo ECC reduces service interruptions from uncorrectable errors by correcting more pin and chip errors than state-of-the-art SDDC mechanisms. Bamboo ECC also provides vastly superior detection capability against errors with any severity and eliminates the risk of silent data corruption to ensure safe system operation. As permanent faults generate more serious and uncorrectable errors with accumulation, Bamboo ECC provides fine-grained pin-level flexibility to aggressively retire such faults with minimal cost, thereby extending system lifetime.

## 1.2 Errors from Less-Reliable Process Technology

Shrinking process technology will make individual DRAM devices more vulnerable to errors. As DRAM technology continues to scale down to below 10nm, smaller transistors, capacitors, and wire pitches make DRAM cells more vulnerable to smaller defects, retention errors, and disturbance errors, respectively [70, 85, 82]. Current row and column sparing techniques fall short of screening out all the faulty cells, so these repeated and permanent errors can increase error rates even further, and can make error patterns more severe when faults that affect the same memory region accumulate over time.

#### 1.2.1 In-DRAM ECC Protection

In response, industry and academia have been exploring alternatives that are based on integrating ECC within DRAM chips [68, 14, 81, 85, 70, 67, 107]. In-DRAM ECC works by reading and processing redundant information within the DRAM chip, commonly allocating 6.25% or 12.5% additional bits for each memory read or write. By keeping this ECC processing and redundancy within each chip, the DRAM external interface remains mostly unchanged. In-DRAM ECC allows a memory chip to present itself to the processor as a reliable part even if inherent scaling faults exist, enabling future DRAM devices to be manufactured with high yield.

#### 1.2.2 Limitations of In-DRAM ECC

While in-DRAM ECC mitigates the issue of inherent faults at the boundary of a single device, its use within the context of highly-reliable systems raises an issue of increased redundancy compared to current practice. Highly-reliable systems already utilize ECC across a memory rank<sup>2</sup> (rank-level ECC) to protect against operational memory faults. As opposed to inherent faults, which exist when the system is first run, operational faults occur while the system operates (as a result of particle strikes, signaling errors, aging, etc.). Rank-level ECC commonly requires 12.5% redundancy in the form of redundant chips added to each rank. Thus, with in-DRAM ECC and rank-level ECC

<sup>&</sup>lt;sup>2</sup>A memory rank is a set of DRAM chips accessed simultaneously to provide the desired channel data width.

both applied, the combined storage redundancy grows to 26.6% (1.125  $\times$  1.125 = 1.266).

#### 1.2.3 Contribution w.r.t. Scaling-Induced Errors

This dissertation provides strong and efficient protection against both inherent and operational faults. Active Guardband ECC (AG-ECC) utilizes a novel and unique combination of ECC decoding and memory remapping that simultaneously achieves high efficiency, high reliability, and high yield. AG-ECC uses a strong rank-level ECC to tolerate both errors during operation and errors from imperfect process technology, eliminating the need for separate in-DRAM ECC protection against faulty cells. It not only restores the total amount of redundancy back to 12.5%, compared to up to 26.6% overhead in the proposed in-DRAM + rank-level ECC approaches, but also provides higher yield than in-DRAM ECC. AG-ECC can maintain reliability stronger than SDDC mechanisms available in current systems and significantly improves DRAM energy efficiency.

#### 1.3 Errors from Less-Reliable Transfers

DRAM transfers are getting more vulnerable to transmission errors. DRAM has consistently evolved to provide more data with less energy. Each recent generation of DRAM has more-than-doubled the data transfer rate of its predecessor (Figure 1.1), and has also decreased core and I/O voltages for better energy efficiency (Figure 1.2). Increasing signal transfer rates and

Figure 1.1: The increasing DRAM transfer rates of command, address, and data signals over the past 15 years.

Figure 1.2: The decreasing DRAM supply voltage levels.

Figure 1.3: DRAM power breakdown over core and I/O.

lowering I/O voltages each exacerbate the problem of transmission errors. A transmission error occurs when a signal is incorrectly transferred to or from memory; higher transfer rates and lower voltages increase the vulnerability to timing and electrical noise, respectively.

While current protection techniques primarily focus on protecting data transmissions, *Clock, Control, Command, and Address (CCCA)* signals should not be neglected. These signals typically operate at half the transfer rate of data signals, yet they may suffer from more transmission errors due to DIMM topology. On a DDR4 DIMM, for example, each CCCA signal visits up to

Figure 1.4: The standard fly-by topology of DDR4 registered DIMM.

18 DRAM chips sequentially and 27 CCCA signals are captured using a clock signal. On the other hand, each data signal has a dedicated connection and there is a strobe signal per up to 8 data signals. The larger number of receivers and the wider interface deteriorate CCCA signal quality by increasing reflections and signal skew, respectively, making CCCA transfers potentially more vulnerable to errors than data transfers despite the halved transfer rate. Signal and power integrity simulations on DDR4 registered-DIMM show that CCCA signals have a narrower time window to reliably receive signals than data signals. Also, evidence from a large-scale field study [127] strongly suggests that CCCA errors are already a severe problem for reliability-conscious systems, even at the modest 1.6 Gbps CCCA rate of DDR3.

#### 1.3.1 Current Transmission Protection

Traditionally, DRAM designs have managed the transmission error rate using sophisticated circuit techniques to improve signal quality (e.g., delay-locked loops, phase-locked loops, on-die termination, differential signaling, and

fly-by topology [56, 59, 60, 61, 66]) at the cost of consuming extra power. The price paid for reliable transmission is significant because roughly half of DRAM power is spent on I/O (Figure 1.3) [120]. Increasing transfer rates and tight power constraints have made circuit techniques alone insufficient to provide high levels of reliability and efficiency.

As a result, DRAM vendors have introduced ad-hoc architectural techniques in recent memory generations to protect transfers, such as *Cyclic Redundancy Check (CRC)* and *Command/Address Parity (CAP)* [60, 61, 66]. The 8-bit CRC on write data verifies the consistency of received data, while an even-parity on command/address signals verifies the consistency of received command/address. Once errors are detected by such schemes, they can be corrected by retransmitting the signals.

#### 1.3.2 Limitations of Current Transmission Protection

CAP provides limited detection capability of CCCA errors; it can detect only odd bit errors on command/address signals. Errors on clock and control signals (e.g., chip select and clock enable) and even-bit errors on command/address signals are not detected by CAP. Such errors can have disastrous impact that is not correctable by conventional data-only ECC, leaving a serious hole in system reliability.

Due to the lack of strong protection and the severity of the problem, recent DRAM generations passively limit CCCA rates for high reliability. DDR4 introduced *gear-down* mode which transfers CCCA signals at a quarter the

rate of data for reliability [60] and GDDR5X could not scale up CCCA rates along with data rates [66] (Figure 1.1). These designs trade off performance for CCCA reliability by lowering command bandwidth, adding command latency, and increasing access granularity—all of which degrade performance and efficiency.

#### 1.3.3 Contribution w.r.t. Transmission Errors

This dissertation presents All-Inclusive ECC (AI-ECC), a holistic memory error protection scheme that is able to safeguard DRAM data and CCCA signals against storage and transmission errors. Strong protection on any one component (i.e., data) provides limited benefits to overall reliability as any unprotected component will quickly become the reliability bottleneck. Therefore, current data-oriented ECC should be redesigned to thoroughly protect both data and CCCA. By leveraging the existing strong ECC schemes for the protection of CCCA errors, AI-ECC remedies the approach of protecting only or mostly DRAM data without discarding the extensive advancements made in the area of data protection.

## 1.4 Protection Energy Efficiency

In addition to the heightened need for stronger protection, energy efficiency of memory protection should be improved. DRAMs already consume more than 30% of total power in modern datacenters [97], and ECC overhead takes a significant portion of it; the 12.5% extra chips on ECC DIMMs

translate into  $\frac{1}{9}$  of the DRAM energy consumption.

#### 1.4.1 Limitations of Current Protection

Current SDDC ECCs increase DRAM energy consumption even further by forcing energy-inefficient memory configurations. SDDC mechanisms rely on narrower DRAM devices (e.g.,  $16 \times 4$  chips per channel) to reduce the number of affected bits from a chip failure and/or a wider channel (e.g., two ECC DIMMs in parallel) to increase redundancy amount. Narrow devices double the number of chips per access than energy efficient configurations with wider devices (e.g.,  $8 \times 8$  chips per channel) and roughly double the DRAM energy consumption per access. While a wider channel can increase the amount of redundancy per access, its larger access granularity often also results in a serious performance degradation due to overfetching and reduced memory-level parallelism. Fujitsu reports that pairing two 64b channels together in an 8 DIMM system to form four 128b data channels degrades integer application performance (SPECint2006 [130]) by 6% and memory-intensive benchmark (STREAM [43]) performance by 43%. The performance hit is even more staggering on a lower capacity node—with 4 DIMMs, the performance degradation for the integer and memory benchmarks are 28.3% and 46.3%, respectively [32].

#### 1.4.2 Contribution w.r.t. Energy Efficiency

This dissertation improves energy efficiency of main memory protection as well as protection strength. Frugal ECC (FECC) is an adaptive and strong

ECC technique that relies on opportunistic compression to offer an entirely new set of tradeoffs between reliability and ECC overheads. The insight behind FECC follows recent research which observes that compression at the cacheblock granularity can free up enough space for other information [89, 123]; FECC uses this free space for storing the ECC redundancy. Thus, when compression succeeds, FECC can match the performance of a conventional ECC organization that uses dedicated ECC memory devices with less, or even zero, dedicated redundancy.

While the concept is simple, two crucial innovations are introduced to make FECC truly effective. First, a new compression scheme maximizes the fraction of blocks that compress just enough for ECC rather than needlessly aiming for greater levels of compression. The second innovation is how to protect poorly compressed blocks. Not all memory blocks are sufficiently compressible and some blocks fail to yield enough spare footprint for the redundant information. To address these *compression exceptions*, FECC applies different ECC layouts and protects its layout meta-data separately to guarantee up to true SDDC protection.

This careful combination of compression and ECC layout simultaneously achieves superior reliability and lower overhead when compared to state-of-the-art ECC mechanisms. As an example, this dissertation presents the first true SDDC ECC on a narrow channel (i.e., single ECC DIMM) with wider devices (i.e., 8-bit wide DRAM chips) to reduce the number of DRAM chips per access and to improve DRAM energy efficiency.

## 1.5 Dissertation Organization

The remainder of this dissertation proceeds as follows: Chapter 2 lays out the conceptual foundations of this dissertation by reviewing the terminology and function of system reliability, DRAM, and ECCs. Chapter 3 develops strong ECC mechanisms against data errors. Chapter 4 introduces errors from imperfect process scaling and presents strong and efficient protection. Chapter 5 discusses transmission errors and provides thorough protection on data and CCCA signals. Chapter 6 presents mechanisms to improve energy efficiency of protection using fine-grained compression. Chapter 7 summarizes current findings and presents future research directions.

# Chapter 2

# Background

This chapter reviews the concepts and terminology that are fundamental and common to the mechanisms of this dissertation: reliability concepts, DRAM, and ECC. More detailed motivations of particular mechanisms will be provided at the beginning of its corresponding chapter: data errors patterns (Section 3.1), inherent faults from process scaling (Section 4.1), and transmission errors (Section 5.1).

# 2.1 Reliability Concepts

As a matter of terminology: a fault is a physical phenomenon or defect that may cause an error, an error is a discrepancy between the intended and actual state of a system, and a failure is the event that a system deviates from its intended service [15]. A fault may or may not generate an error depending on circumstances, and an error can be masked or corrected by error control systems. The aim of this research is to efficiently provide such an error control system to prevent DRAM errors from developing into a system failure.

Faults can be classified based on their error manifestation and time of occurrence. A *transient* fault is introduced by some temporary environmental

impetus (e.g., a high-energy particle strike), whereas a *permanent* fault is an irreversible physical defect that continually produces errors (e.g., stuckat bit) [128]. An *inherent* fault is a permanent fault introduced during the manufacturing process, and an *operational* fault is a fault during operation (either transient or permanent).

Reliability indicates continuity of service without a failure, often measured in Mean Time To Failure (MTTF) or Failures In Time (FIT, the number of failures in billion hours), and manufacturability indicates the ease with which a good product can be manufactured, measured in yield. A fault may affect reliability by incurring failures and an inherent fault may decrease manufacturability by making a chip defective. The aim of this dissertation is to efficiently provide fault tolerance mechanisms using Error Correcting Codes (ECC) to prevent DRAM faults from developing into a system failure or resulting in poor yield.

No error control system can diagnose and correct all possible errors. In general, an error control system handles an error in one of four ways: a Detectable and Correctable Error (DCE), a Detectable but Uncorrectable Error (DUE), a detectable but miscorrected error, or an undetectable and uncorrectable error. In the event of miscorrection or misdetection, incorrect data escapes the error control system, resulting in a possible Silent Data Corruption (SDC) failure. The implication of a DUE failure can vary depending on circumstances. A DUE during transmission can typically be corrected by retry, simplifying the correction of any detected errors. In the case of stor-

Figure 2.1: The hierarchical organization of DRAM.

age, a DUE indicates that some data has been lost. This loss of data could be acknowledged and tolerated (by an error tolerant application), it may be corrected by some higher-level protection mechanisms (such as checkpoint and restart [38] or a hierarchical state preservation and restoration system [27]), or it may indicate a fail-stop condition where forward progress is halted (but no SDC occurs).

#### 2.2 DRAM

Dynamic Random Access Memory (DRAM) is widely used as system main memory for its low cost and high density. The deeply hierarchical structure of DRAM is depicted in Figure 2.1. A DRAM cell stores each bit of data using a single transistor and a capacitor (Figure 2.1a). DRAM cells are organized into two-dimensional arrays, called banks, to amortize control overheads (Figure 2.1c). At a deeper look, each bank is physically sub-divided into 512×512 cell mats (Figure 2.1b) to reduce load capacitance and all data within neighboring mats are connected to one data pin for efficiency [142, 83, 60, 33]. A DRAM chip (or a device) consists of multiple banks to interleave per-bank accesses and hide long access latency (Figure 2.1d).

Most DRAMs use multiple data pins (DQs) to provide a parallel chip interface. A DRAM with an N-bit DQ interface is called a  $\times N$  chip (e.g., a  $\times 4$  or  $\times 8$  DRAM); the set of DRAM chips that are accessed together in parallel to provide the desired data bus width is called a rank (Figure 2.1e). A channel is a set of ranks that time-share physical command/address and data transfer lanes. A rank/channel comprises of Dual In-line Memory Modules (DIMMs) that are built from multiple DRAM chips on a PCB board. A rank can consist of a single DIMM (e.g., a  $\times 64$  rank using a  $\times 64$  DIMM) or multiple DIMMs (e.g., a  $\times 128$  rank using two  $\times 64$  DIMMs in parallel), and a DIMM can contain multiple ranks (e.g., a  $\times 64$  DIMM contains two  $\times 64$  ranks).

DRAM requires three commands to access a fresh piece of data. An activation command (ACT) fetches a row of data into an internal row buffer.

Then, a read or write command (RD or WR) uses a column address to select and transfer or overwrite a particular block from the activated row. To exploit data locality and amortize command overheads, an RD or WR transfers a block of data over multiple cycles—one beat of data is transferred through the rank at a time. The number of beats transferred during each access is called the memory burst length, and most recent DRAMs use a burst length of 8. A Memory Transfer Block (MTB) is the unit of memory access and is defined by burst length and channel data width; typical MTB sizes from burst length of 8 and  $\times 64/\times 128$  channels are 64B/128B, respectively (Figure 2.1e). Once a memory read or write completes, the DRAM bank must be restored to a ready state by issuing a precharge command (PRE). An access to an already-activated row (a row buffer hit) does not require an ACT or PRE command, potentially saving latency and command bandwidth for spatially local accesses. However, command bandwidth can be a limiting factor for programs lacking locality, especially in systems featuring fine-grained access granularities [10, 152, 153, 117]. Furthermore, DRAM requires periodic refresh commands (REF) to prevent data loss from leakage, further taxing the available command bandwidth.

## 2.3 Error Correcting Codes

Error Correcting Codes (ECC) have long been used to protect data against errors. ECC detects and corrects errors by adding redundant information whose value is generated algorithmically from the protected data. A data

and check value pair is called an ECC word. A valid word whose check bits are consistent with its data is called a codeword, while an invalid pair due to errors is called a non-codeword. The process of generating a codeword from data is called encoding and the process of detecting errors from a word and (possibly) restoring the original data is called decoding.

The protection strength of an ECC can be defined by its correction and detection coverage: X-correcting and Y-detecting codes can correct all of up to X errors and detect all of up to Y errors. These protection coverages can be theoretically extracted from the code distance: in information theory, the Hamming distance between two words of equal length is the number of positions at which their symbols differ, and the code distance is the minimum Hamming distance between two distinct codewords. Codes with distance d, if used for detection only, can detect all errors with less-than-d erroneous symbols (i.e., (d-1)-detecting codes), because these errors always result in a non-codeword. Alternatively, the same codes can detect and correct all errors with less-than- $\lfloor (d-1)/2 \rfloor$  erroneous symbols (i.e.,  $\lfloor (d-1)/2 \rfloor$ -correcting codes) by decoding a non-codeword into the nearest unique codeword.

Table 2.1 illustrates some examples of ECCs with different distances. In the figures, double-circles represent codewords; each diagram shows two neighboring codewords that are colored black and white. Black and white single-circles are non-codewords that are corrected to the codeword of the corresponding color. Codes with distance 3 can correct all single-symbol errors by finding the nearest unique codeword. However, two-symbol errors on codes

| Code<br>distance | Error handling between the neighboring codewords | two Name                                                         |                                                                    |  |

|------------------|--------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------|--|

|                  |                                                  | Binary symbol                                                    | Non-binary symbol                                                  |  |

| 3                | ● ○ ○ ○ ←1→ ←1→ ←Distance=3→                     | Single Error Correcting (SEC)                                    | Single Symbol Correcting (SSC)                                     |  |

| 4                |                                                  | Single Error Correcting -<br>Double Error Detecting<br>(SEC-DED) | Single Symbol Correcting -<br>Double Symbol Detecting<br>(SSC-DSD) |  |

| 5                |                                                  | Double Error Correcting (DEC)                                    | Double Symbol Correcting (DSC)                                     |  |

Table 2.1: Examples of ECCs with different distances.

with distance 4 can make a word equally distant from two codewords (gray single-circle); in that case the error is detectable yet uncorrectable. A typical ECC scheme uses a t-symbol correcting and (t+1) symbol detecting codes, which is effective in systems where errors accumulate symbol-by-symbol. Once the erroneous symbol count exceeds the correction capability, it will still be within the detection boundary.

ECCs can be categorized based on their symbol sizes. Binary ECCs use binary symbols and are most effective at protecting against random bit errors. Hamming [37] and BCH codes [44, 20] can correct a single erroneous bit in w bits of data using  $\lceil log_2(w+1) \rceil$  redundant bits (and they can detect one more bit-error by adding a parity bit).

Non-binary ECCs partition data into fixed-size symbols; error detection and correction then occur at the symbol granularity. The most widely used non-binary ECCs are Reed-Solomon (RS) codes [116], which can achieve the

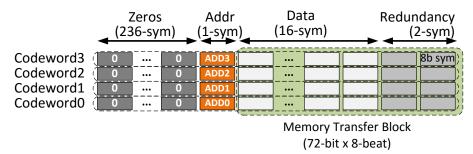

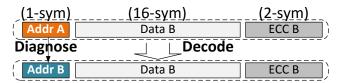

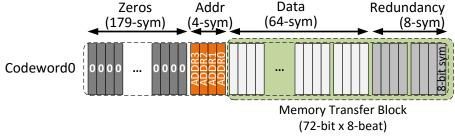

minimum possible redundancy for a given distance [125]. RS codes with 8-bit symbols can correct up to t symbol errors using 2t redundant symbols (and they can detect one more symbol error using an additional symbol) on up to 255-symbol (2040-bit) words; many SDDC schemes [9, 41] use 8-bit symbol RS codes because of the efficiency. As most memory configurations do not fully utilize such large word sizes, however, these SDDC schemes use smaller words and regard the remaining symbols as zeros (i.e., a shortened code). AI-ECC (Chapter 5) leverages the shortened nature of SDDC schemes to strongly protect address information without any additional redundancy.

The correction capability of RS codes can be increased using a priori knowledge about an error. Compared to a  $random\ error$  whose location and value are unknown, an erasure has its location known in advance (e.g., based on error history). Erasure decoding of RS codes can restore t symbol erasures using t redundant symbols, doubling the correction efficiency relative to random error decoding. AG-ECC (Chapter 4) utilizes erasure decoding to correct rare cases of overlapping inherent and severe operational faults, while either fault alone is corrected by random error decoding.

<sup>&</sup>lt;sup>1</sup>Current 8-bit RS SDDC schemes use anywhere from 18 symbols [9] to 144 symbols [77].

# Chapter 3

# **Data Errors Protection Mechanisms**

This chapter presents and evaluates a novel family of efficient single-tiered ECC mechanisms, called Bamboo ECC, for future large-scale systems. The advantages of Bamboo ECC can be roughly characterized by three important improvements. Strength: Bamboo ECC has superior correction capabilities and can correct more pin and chip errors than the state-of-the-art single-tiered ECC mechanisms, while requiring the same or less redundant storage and off-chip bandwidth. Safety: The vastly superior detection capability of Bamboo ECC all but eliminates the risk of silent data corruption with currently observed fault modes, ensuring safe system operation. Flexibility: Bamboo ECC can increase redundancy at 8b granularity, compared to 8B for the state-of-the-art SDDC techniques; this fine-grained redundancy allows for more adaptive graceful downgrade schemes (i.e., memories with faulty devices can continue operation with reduced-strength codes), further improving both reliability and system lifetime. When combined into a system context, these

Parts of this chapter appear in [77]. The author is the main contributor of the idea, implementation, and evaluation.

improvements can lead to orders of magnitude fewer silent data corruptions or greatly extended system lifetime.

Three main insights lead to the innovative code design. First, many faults manifest errors on a single data pin (DQ) due to the DRAM internal structure (e.g., a mat fault) or the DRAM external interface (e.g., a faulty data pin). Secondly, aligning ECC symbols to prevalent error patterns allows for more frequent corrections. Finally, while an ECC code guarantees detection of errors up to a certain severity, careful analysis reveals that some codes provide superior detection capabilities beyond these guarantees. These insights are described in more details below.

# 3.1 Data Error Patterns

Recent field studies of DRAM faults [122, 87, 48, 128, 129] indicate that memory errors follow some idiosyncratic trends due to the deeply hierarchical structure of DRAM (Section 2.2). DRAM cell arrays are sub-divided into  $512 \times 512$  cell mats and all data within neighboring mats are connected to a single DQ for efficiency [142, 83, 60, 33]. Therefore, a local fault commonly generates errors over a single DQ.

Table 3.1 presents DRAM fault rates observed in the Jaguar supercomputers with ×4 DDR2 chips [128]. It indicates that about half of all faults (49.6%) affect only a single bit. More importantly, 72.6% of all faults and 68.2% of permanent faults are confined to a single DQ. Furthermore, this analysis is likely to underestimate the true likelihood of a single DQ error

within an access for methodological reasons, as intermittent single-DQ faults that are separated in time may be classified as multi-DQ faults.<sup>1</sup> Finally, the majority of all faults (71.0%) are permanent, indicating even more severe errors may accumulate. These findings show that the need for strong ECCs to protect against accumulating faults, especially the accumulation of single DQ faults over time. Bamboo ECC focuses on this important single-DQ fault mode to improve correction capability.

# 3.2 ECC Detection Coverage

This section presents theoretical background on how Bamboo ECC improves detection coverage to eliminate SDCs even in very large scale systems (e.g., exascale computing) without increasing the redundancy ratio. Section 2.3 presents theoretical correction and detection coverages of ECC. A code with distance d, if used for detection only, can detect all errors with fewer than d erroneous symbols, or detect and correct all errors with fewer than  $\lfloor (d-1)/2 \rfloor$  erroneous symbols. Errors that exceed the theoretical coverage of a code can either be detected (resulting in a DUE) or they can lead to an SDC failure.

Another motivation of Bamboo ECC is that, in practice, the error de-

<sup>&</sup>lt;sup>1</sup>The observation that single-DQ errors are dominant is supported by other measurements. IBM reports that 91% of erroneous beats have a single bit corrupted [50], and other results from Jaguar report that 2-bit correction provides only marginally better correction coverage than 1-bit correction; both of these results indicate that errors tend to be confined to a single DQ.

| Fault Mode    | Number of failing DQs |                |                  |                 | Fault Rate      |                       |

|---------------|-----------------------|----------------|------------------|-----------------|-----------------|-----------------------|

| Tauti Wode    | 1                     | 2              | 3                | 4               | Transient       | Permanent             |

| Single-bit    | 32.8<br>(49.6%)       | N/A            |                  | 14.2<br>(21.5%) | 18.6<br>(28.1%) |                       |

| Single-word   | N/A                   | 1.7(2.6%)      |                  |                 | 1.4 (2.1%)      | $0.3 \\ (0.5\%)$      |

| Single-column | 6.0 $(9.1%)$          | 0.2 $(0.3%)$   | 0.1 $(0.1%)$     | 0.7 $(1.1%)$    | 1.4 (2.1%)      | 5.6 $(8.5%)$          |

| Single-row    | 2.6 $(4.0%)$          | 5.6 $(8.5%)$   | 0.1 $(0.2%)$     | 0.1 $(0.1%)$    | 0.2~(0.3%)      | 8.2 (12.4%)           |

| Single-bank   | 6.0 $(9.1%)$          | 2.5 $(3.8%)$   | $0.4 \\ (0.6\%)$ | 1.9 $(2.9%)$    | 0.8 (1.2%)      | $10.0 \\ (15.1\%)$    |

| Multiple-bank | $0.3 \\ (0.5\%)$      | 0.6 $(0.9%)$   | 0.1 $(0.1%)$     | 0.8 $(1.2%)$    | 0.3~(0.5%)      | 1.4 $(2.1%)$          |

| Multiple-rank | $0.3 \\ (0.4\%)$      | 0.3 $(0.4%)$   | 0.1 $(0.1%)$     | 3.1 $(4.7%)$    | 0.9 (1.4%)      | $\frac{2.8}{(4.2\%)}$ |

| Total         | 48.0<br>(72.6%)       | 9.2<br>(13.9%) | 0.7<br>(1.1%)    | 6.5<br>(9.9%)   | 19.2<br>(29.0%) | 46.9<br>(71.0%)       |

Table 3.1: DRAM fault rates (in FIT) observed on the Jaguar supercomputer with 73K DDR2 DIMMs.

Figure 3.1: Conceptual codespace of single symbol correcting codes.

tection coverage of all error codes is not equal: in general, scaling-up ECC codeword size (increasing codeword length, redundancy and correction capabilities proportionally) is associated with higher error detection coverage for severe errors. For example, two single-symbol correcting codes can be merged into a double symbol correcting one. While the latter can correct all of the errors that the former can, its larger codeword bestows stronger error detection capabilities. By maximizing its ECC word size, Bamboo ECC can safely reduce the SDC probability for severe errors down to  $\leq 0.0000006\%$ , without requiring more redundancy than what is currently available on a single ECC-DIMM.

An example illustrates why the practical error detection coverage of

an ECC code is determined by its word size. Figure 3.1 shows a conceptual codespace for a distance 3 (or Single Symbol Correcting (SSC)) code. A double circle indicates a valid codeword (CW) and a single circle indicates an erroneous non-codeword. A ball of Hamming Distance (HD) d represents all words that are d symbols different from a CW. If there is a single symbol error in a CW, the erroneous word is on the HD=1 (innermost) ball and the SSC code can always restore the original data by finding the nearest CW. If there are two symbol errors, the erroneous word is on the HD=2 ball and the error will be miscorrected to a neighboring CW if and only if it also falls on the HD=1 ball of the neighbor; otherwise, the error will result in a DUE. Note that the theoretical coverage of this code is not double symbol detection as there exists this potential for miscorrection. From a practical coverage perspective, however, the ratio of the number of miscorrections to the total number of words on each ball decreases with larger ECC word sizes as the code space becomes increasingly sparse. Thus, it can be seen that the error detection of a code for errors beyond its guaranteed coverage is maximized with the ECC word length. Likewise, three symbol errors on the HD=3 (outermost) ball may be undetected (if they fall on a neighboring CW), miscorrected (if they fall on another HD=1 ball), or they are otherwise detected. Again, it can be seen that the error detection of a code for errors beyond its theoretical coverage increases with the ECC word length.

High error detection of severe errors is fundamental for Bamboo ECC to ensure safe system operation. Therefore, all of our analyses in Section 3.4.1

are performed using real ECC decoding behavior in order to capture the practical error detection coverage of the codes for errors beyond their worst-case protection guarantees. This is in contrast to other studies that characterize system failure rates using only the worst-case behavior of ECC codes [54, 118]. An important observation of Bamboo ECC is that, in practice, silent data corruption can be eliminated without resorting to expensive ECC with high worst-case error detection coverage. By manipulating the size of the Bamboo ECC codeword and by matching code layout with expected fault modes, SDC rates can be extensively reduced without introducing additional redundancy or constraints on the memory channel size.

# 3.3 Bamboo ECC

Bamboo ECC protects the burst of data from a DQ to provide stronger correction and detection with equal or less redundancy than previously proposed ECC mechanisms. The following subsections describe the motivation, operation, and overheads of Bamboo ECC in greater detail. Section 3.3.1 describes some useful Bamboo ECC organizations. Section 3.3.2 shows how the flexibility of Bamboo ECC can be utilized to provide superior levels of protection over the lifetime of a system. Finally, Section 3.3.3 describes the cost that Bamboo ECC schemes pay to achieve their high levels of protection and storage efficiency.

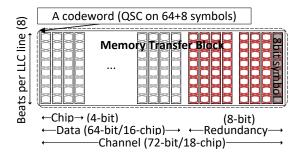

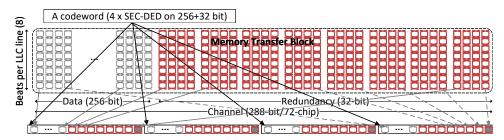

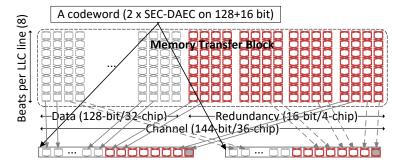

#### 3.3.1 Organizations

Bamboo ECC changes ECC layout to have per-DQ symbols over a memory transfer block. It groups the data of a single DQ as an ECC symbol; on a conventional 8-beat memory transfer block of DDR3/4, a per-DQ symbol has 8 bits of data. By aligning ECC symbols to frequent single-DQ faults, Bamboo ECC reduces the number of symbols to be corrected in the common case and requires less redundancy to correct common errors. The 8-bit symbols are encoded by a Reed Solomon code to achieve the minimum possible redundancy for its level of correction (i.e., 2 redundant symbols per symbol correction, Section 2.3). The per-DQ symbols also increase the ECC word size to a memory transfer block. This large ECC word can detect almost all severe errors, while resulting in manageable increases in decoding complexity and latency (Section 3.3.3).

Bamboo ECC is a family of codes. With per-DQ symbols, Bamboo ECC introduces redundancy at pin granularity and provides finer control over correction and detection capabilities compared to previous ECC mechanisms with per-chip symbols. The following subsections describe some of the efficient Bamboo ECC organizations. Other organizations can be used to meet different memory system constraints and reliability requirements.

#### 3.3.1.1 Single Pin Correcting ECC

The simplest Bamboo ECC is the Single Pin Correcting (SPC) organization (Figure 3.2), which can correct a bit or a pin error with 2 redundant

Figure 3.2: Single Pin Correcting Bamboo ECC on (64+2)-bit channel

pins. SPC requires just a quarter of the redundant storage of SEC-DED on a 64b data channel (3.1% vs. 12.5%) yet it provides a better correctable error rate.<sup>2</sup> One issue with SPC concerns the fixed granularity of commercial DRAM chips—while memories such as embedded DRAM (eDRAM) have the data width flexibility to support SPC, off-the-shelf memory chips are typically ×4 or ×8 DDR. Employing SPC with these chips will result in an inefficient use of pins and storage. Even on commodity DRAM chips, however, SPC can be efficiently employed as a component of a graceful degradation scheme, as described in Subsection 3.3.2.

#### 3.3.1.2 Single Pin Correcting – Triple Pin Detecting ECC

An extra ×4 DDR chip can provide 4 redundant Bamboo ECC symbols (Figure 3.3). This redundancy can be used as either a *Double Pin Correcting* (DPC) or Single Pin Correcting - Triple Pin Detecting (SPC-TPD) scheme;

<sup>&</sup>lt;sup>2</sup>SPC misses some SEC-DED-correctable error patterns. However, Subsection 3.4.2 shows that SPC has better uncorrectable error rates due to the rarity of these patterns and the fact that SPC has a lower raw error rate due to its lesser redundancy.

Figure 3.3: Single Pin Correcting – Triple Pin Detecting Bamboo ECC on (64+4)-bit channel

Figure 3.4: Quadruple Pin Correcting Bamboo ECC on (64+8)-bit channel

SPC-TPD usage has a very high detection coverage, detecting 100% of up-to-3-pin errors and  $\geq$ 99.9996% errors beyond this point, and is thus preferred. The stronger correction capability of DPC, on the contrary, is less helpful as faults affecting exactly 2 pins are infrequent (a field measurement on 2-bit symbol correction [128] showed little improvement over SEC-DED) while it can increase the SDC probability by aggressively miscorrecting severe errors. SPC-TPD can be configured as a (64+4)-DQ configuration over a 64-bit data channel, halving the redundancy of SEC-DED (6.25% vs. 12.5%).

#### 3.3.1.3 Quadruple Pin Correcting ECC

Bamboo ECC can provide stronger-than-SDDC protection with equal redundancy to state-of-the-art SDDC schemes by using a Quadruple Pin Correcting (QPC) organization. With two redundant ×4 chips, QPC has 8 redundant symbols (Figure 3.4) and can correct up to 4 symbol errors or any single chip-error. QPC can be configured in a (64+8)-DQ manner over a 64-bit data channel, in which case the redundant storage needs match those provided by conventional ECC DIMMs (12.5%). This storage efficiency for single-tiered, narrow-channel SDDC is only paralleled by the AMD chipkill scheme used in recent processors. QPC enjoys a stronger correction capability than AMD chipkill by correcting pin errors that are scattered over different chips. If there are two pin faults on two chips, QPC can correct both of them while AMD chipkill must report a DUE (or, in some cases, AMD chipkill results in SDC). As single-DQ faults are prevalent, this distributed error correction capability can reduce uncorrectable error rates significantly. In addition, QPC has a stronger detection capability due to its large codeword size. This leads to QPC detecting ≥99.999994% of all errors. A more in-depth comparison of the two ECC schemes is evaluated in Section 3.4.

One optimization to QPC is to limit its correction capability to reduce SDC rate even further, in a manner similar to the history mechanism used by AMD chipkill [9]. AMD chipkill uses the history of corrected symbol locations within each access to reduce SDC rates. If corrected symbol locations differ among words within an access, AMD chipkill discards the correction results

Figure 3.5: Octuple Pin Correcting Bamboo ECC on a (128+16)-bit channel.

and reports a DUE. The rationale behind this decision is that errors on different chips over a single access are very rare so that the symptom is likely to have been generated from miscorrections arising from a severe error. Similarly, QPC pessimistically reports a DUE if the diagnosed pin errors are not confined to a single chip or to two pins on different chips.

# 3.3.1.4 Octuple Pin Correcting ECC

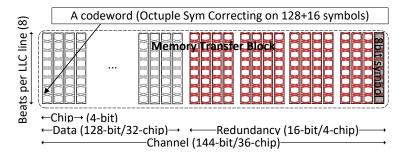

Bamboo ECC can correct errors on two ×4 chips or one ×8 chip by correcting 8 pin symbols. Octuple Pin Correcting (OPC) Bamboo ECC achieves 8 pin correction with 16 redundant pins, resulting in a 25% overhead on a 64-bit data channel or a 12.5% overhead on a 128-bit data channel (Figure 3.5). OPC is optimized in a manner similar to that of QPC and limits its correction capability to 2 chip errors or 4 independent pin errors to reduce the SDC rate.

# 3.3.2 Graceful Downgrade

The plethora of attractive organizations above allows a Bamboo ECCbased system to more fully utilize redundant bit steering (RBS) than existing ECC schemes. RBS is a graceful downgrade scheme proposed by IBM [21] and uses parts of the ECC check bits as hot spares, remapping faulty pins through these spares. The state-of-the-art RBS-based protection is *Double Device Data Correction (DDDC)*+1 from Intel, which can tolerate two sequential chip failures and a bit failure over a 128-bit data channel (Section 3.5). A gracefully downgrading Bamboo ECC-based system can correct more initial chip faults, more sequential chip faults, more end-of-life faults and has a better end-of-life detection capability than DDDC+1. In addition, a gracefully degrading Bamboo ECC system can diagnose and remap errors at the pin granularity, offering slower degradation for accumulating pin errors than a system that operates on coarse-grained symbols. Such a gracefully degrading Bamboo ECC scheme is described below.

OPC over a 128-bit data channel uses the same amount of redundancy (12.5%, or 16 pin symbols) as DDDC+1. After a chip retirement, the available redundancy decreases to 12 pins, but Bamboo ECC can still operate in *hextuple* pin correcting mode to correct up to 6 pin errors. Successive pin errors can be diagnosed and retired at the pin granularity—a luxury that non-Bamboo ECC codes do not enjoy.

After the available spare pins are exhausted due to further pin or chip retirement, the redundancy of the Bamboo ECC-based system decreases down to 8 pins, which is sufficient for QPC. Finally, following a third round of pin or chip retirement, the system can downgrade to SPC-TPD using the remaining 4 redundant (non-spare) pins. Due to the storage efficiency of SPC-TPD, the

Bamboo ECC-based system will still be able to correct a pin error and detect  $\geq 99.9996\%$  of errors. As a result, this graceful downgrade scheme can correct two concurrent chip errors in its initial OPC phase and then can correct up to 1 sequential chip error and 1 pin error. It can also handle finer grained errors, retiring faulty bits or pins as they accumulate.

Bamboo ECC-based graceful downgrade enjoys superior flexibility, and can be modified to work on a narrower channel. For a system with a 64-bit data channel, QPC (using 8 redundant pins) can be gracefully downgraded to SPC-TPD (with a 4 pin redundancy), correcting a sequence of 1 chip error and 1 pin error or up to 5 sequential pin errors while detecting most end-of-life errors.

#### 3.3.3 Overheads

The large ECC symbols and codewords of Bamboo ECC provide strong and efficient error protection at the expense of decoding complexity and latency. This section examines these costs, showing that the additional implementation overheads of Bamboo ECCs are modest and well-aligned to current technological trends. It is demonstrated later that Bamboo ECCs incur little performance overhead, and is expected that their memory bandwidth savings (for the same level of protection) will outweigh their costs.

Circuit overhead: RS codes with 8-bit symbols have modest encoding and decoding overheads to have a wide range of commercial applications, ranging

from CDs to satellites. AMD chipkill uses 8-bit RS codes with 16 data symbols and 2 redundant symbols; a corresponding fully parallel encoder requires 6 XOR2 gates of delay and consumes an area equivalent to about 1,600 NAND2 gates.<sup>3</sup>

With larger codewords, Bamboo ECCs have larger encoding/decoding overheads. Specifically, a fully parallel encoder for QPC (64-symbol data + 8-symbol redundancy) is 8 XOR2 gates deep, which is 2 gates more than AMD chipkill yet is still easily implementable within a single memory cycle (1.2GHz). Even the most complex Bamboo ECC presented, OPC with 128-symbol data and 16-symbol redundancy, requires only 10 logic levels. The fully parallel QPC encoder consumes about 25,000 NAND2 gates of area, a  $\times 16$  increase over that of AMD chipkill. DRAM data, however, does not arrive at the chip in an extremely wide parallel interface, rather transfers over multiple cycles, and as such narrower pipelined RS encoder [26] can be used to reduce the area of the encoder. Using a simplified gate-level model, a 16-way parallel QPC encoder derived from [26] is estimated to require 5,500 gates and a 32-way parallel encoder for OPC will require 11,000 gates. These area overheads do not represent a large amount of chip real estate considering the billions of gates available in recent processors and current trends indicate that logic cost and speed will continue to scale down more rapidly than DRAM [47].

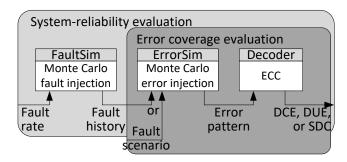

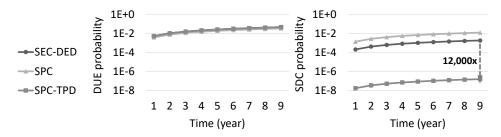

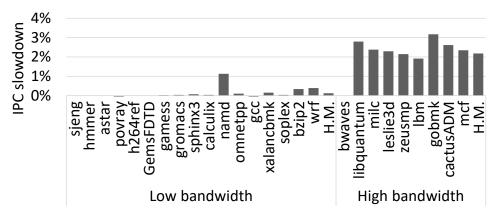

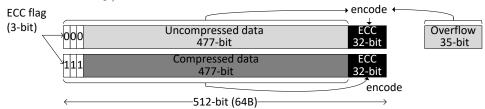

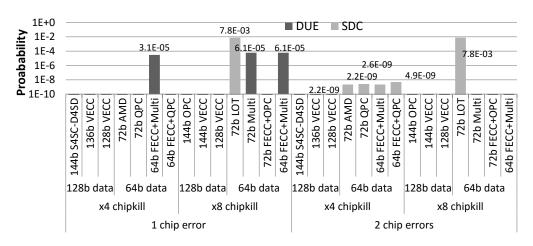

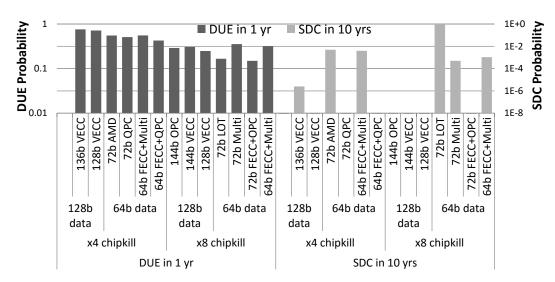

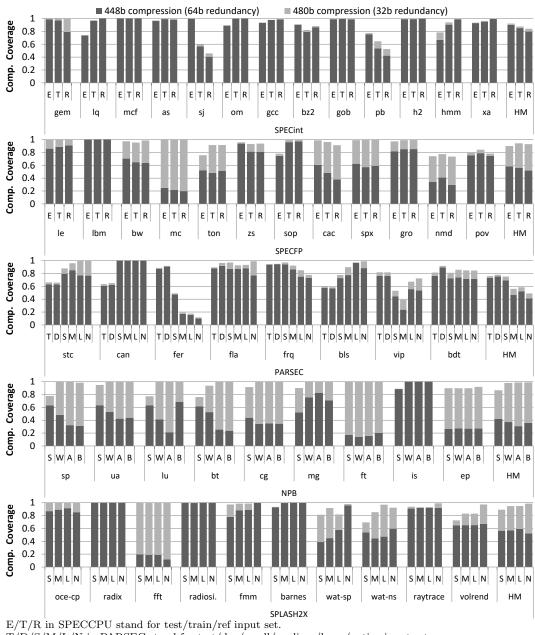

<sup>&</sup>lt;sup>3</sup>These delay and area estimates are found through standard-cell synthesis using the Synopsys toolchain and the 40nm TSMC standard cell library [135, 136], but are presented in a technology-independent manner.