Copyright

by

Donald Do Nguyen

2015

# The Dissertation Committee for Donald Do Nguyen certifies that this is the approved version of the following dissertation:

## **Galois: A System for Parallel Execution of Irregular Algorithms**

| Committee:                 |  |

|----------------------------|--|

| Keshav Pingali, Supervisor |  |

| Lorenzo Alvisi             |  |

| Richard Lethin             |  |

| David Padua                |  |

| Emmett Witchel             |  |

## **Galois: A System for Parallel Execution of Irregular Algorithms**

by

### Donald Do Nguyen, B.S.

#### **Dissertation**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

**Doctor of Philosophy**

The University of Texas at Austin

May 2015

# **Acknowledgments**

The work in this dissertation was supported by National Science Foundation grants CCF 1337281, CCF 1218568, ACI 1216701, and CNS 1064956. I was also supported by a Department of Energy Sandia Fellowship.

Writing a dissertation is largely a solitary task, but this dissertation would not exist without the support of colleagues, friends and family. Foremost, my adviser, Keshav Pingali gave me the advice, encouragement and freedom to pursue my ideas. Most importantly, Keshav taught me how to think about solving problems and pushed me towards addressing the important questions.

My committee members—Lorenzo Alvisi, Richard Lethin, David Padua and Emmett Witchel—gave me thoughtful comments and much needed perspective to help situate my work in a broader context.

My frequent collaborators, Amber Hassaan and Andrew Lenharth, were a pleasure to work with and were always receptive to my latest harebrained ideas. I owe special thanks to Andrew who opened my eyes to the mysteries of performance optimization.

Through the course of graduate school, I made many friends who provided welcome relief from the days (and nights) at my desk. I'd like to especially thank Yinon Bentor, Ben and Shannon Delaware, Thomas Finsterbusch, and Andrew Matsuoka. There is nothing finer than good drinks with good friends.

My greatest thanks goes to my family. My parents, Dieu and Trung worked tirelessly so that I was free to follow my passions. My brother, Andrew, introduced me to the wonders

of science, and the drive for exploration has stayed with me to this day. Of course, a life of adventure is meant to be shared. For that, I'm eternally grateful to my fiancée, Rose, who showed me that a head is only as good as the heart that sustains it.

Donald Do Nguyen

The University of Texas at Austin May 2015 **Galois: A System for Parallel Execution of Irregular Algorithms**

Publication No. \_\_\_\_\_

Donald Do Nguyen, Ph.D.

The University of Texas at Austin, 2015

Supervisor: Keshav Pingali

A programming model which allows users to program with high productivity and which produces high performance executions has been a goal for decades. This dissertation makes progress towards this elusive goal by describing the design and implementation of the Galois system, a parallel programming model for shared-memory, multicore machines. Central to the design is the idea that scheduling of a program can be decoupled from the core computational operator and data structures. However, efficient programs often require application-specific scheduling to achieve best performance. To bridge this gap, an extensible and abstract scheduling policy language is proposed, which allows programmers to focus on selecting high-level scheduling policies while delegating the tedious task of implementing the policy to a scheduler synthesizer and runtime system. Implementations of deterministic and prioritized scheduling also are described.

vii

An evaluation of a well-studied benchmark suite reveals that factoring programs into operators, schedulers and data structures can produce significant performance improvements over unfactored approaches. Comparison of the Galois system with existing programming models for graph analytics shows significant performance improvements, often orders of magnitude more, due to (1) better support for the restrictive programming models of existing systems and (2) better support for more sophisticated algorithms and scheduling, which cannot be expressed in other systems.

# **Contents**

| Acknov    | vledgm  | ents                                          | v   |

|-----------|---------|-----------------------------------------------|-----|

| Abstrac   | et      |                                               | vii |

| List of l | Figures |                                               | xii |

| Chapte    | r 1 In  | troduction                                    | 1   |

| Chapte    | r 2 A   | Data-Centric View of Parallelism and Locality | 7   |

| 2.1       | Mode    | l Problem: SSSP                               | 7   |

| 2.2       | Opera   | ttor Formulation                              | 9   |

|           | 2.2.1   | Baseline Execution Model                      | 12  |

|           | 2.2.2   | TAO Analysis                                  | 15  |

|           | 2.2.3   | Analysis of Iterative Fixpoint Algorithms     | 18  |

| 2.3       | Parall  | el Algorithms                                 | 23  |

|           | 2.3.1   | Delaunay Triangulation                        | 23  |

|           | 2.3.2   | Delaunay Mesh Refinement                      | 24  |

|           | 2.3.3   | Inclusion-Based Points-to Analysis            | 26  |

|           | 2.3.4   | Breadth-First Search                          | 27  |

|           | 2.3.5   | Approximate Diameter                          | 28  |

|           | 2.3.6   | Betweenness Centrality                        | 29  |

|        | 2.3.7 Connected Components                      | 29 |

|--------|-------------------------------------------------|----|

|        | 2.3.8 Preflow-Push                              | 30 |

|        | 2.3.9 PageRank                                  | 31 |

|        | 2.3.10 Support Vector Machines                  | 32 |

|        | 2.3.11 Matrix Completion                        | 34 |

| Chapte | r 3 Parallel Programming Models                 | 37 |

| Chapte | r 4 The Galois System                           | 40 |

| 4.1    | Principles of High-Performance Parallelism      | 40 |

| 4.2    | Separation of Concerns                          | 44 |

| Chapte | r 5 Parallel Data Structures                    | 48 |

| 5.1    | Memory Allocation                               | 49 |

| 5.2    | Exclusive Locking                               | 51 |

| 5.3    | Diffracted State                                | 54 |

| 5.4    | Approximate Value Stores                        | 55 |

| 5.5    | Sparse Graphs                                   | 61 |

| Chapte | r 6 Scheduling                                  | 63 |

| 6.1    | Scheduler Building Blocks                       | 63 |

|        | 6.1.1 Topology-Aware Bag of Tasks               | 64 |

|        | 6.1.2 Topology-Aware Priority Scheduler         | 67 |

| 6.2    | Compositional Scheduling Policies               | 73 |

|        | 6.2.1 Synthesis                                 | 76 |

|        | 6.2.2 Problems with Naive Composition           | 77 |

|        | 6.2.3 Relaxed Concurrent Semantics              | 81 |

|        | 6.2.4 Workset Composition                       | 83 |

|        | 6.2.5 Preliminary Implementation and Evaluation | 87 |

| 6.3      | Exploiting Data Locality                                | 97 |

|----------|---------------------------------------------------------|----|

| 6.4      | Coordinated Scheduling                                  | 00 |

| 6.5      | Related Work                                            | 01 |

| Chapter  | 7 Deterministic Scheduling 1                            | 03 |

| 7.1      | Interference Graph Scheduling                           | 04 |

|          | 7.1.1 Deterministic Interference Graph Scheduling       | 08 |

|          | 7.1.2 DIG Optimizations                                 | 10 |

|          | 7.1.3 Evaluation                                        | 13 |

| 7.2      | Refining Interference Graph Scheduling                  | 30 |

| 7.3      | Related Work                                            | 31 |

| Chapter  | * 8 Comparison with Other Parallel Programming Models 1 | 34 |

| 8.1      | Rewriting Programs to Conform to Scalability Principles | 35 |

|          | 8.1.1 Applying the Disjoint Access Principle            | 36 |

|          | 8.1.2 Applying the Virtualization Principle             | 38 |

|          | 8.1.3 Evaluation                                        | 42 |

| 8.2      | Parallel Programming Models                             | 54 |

|          | 8.2.1 Other Domain Specific Languages in Galois         | 55 |

|          | 8.2.2 Evaluation                                        | 58 |

| 8.3      | Related Work                                            | 69 |

| Chapter  | 9 Conclusion 1                                          | 71 |

| Bibliogr | raphy 1                                                 | 73 |

# **List of Figures**

| 2.1  | Example of SSSP                                                              | 8  |

|------|------------------------------------------------------------------------------|----|

| 2.2  | Illustration of the operator formulation                                     | 9  |

| 2.3  | Example of a cautious operator                                               | 13 |

| 2.4  | TAO analysis of algorithms                                                   | 14 |

| 2.5  | Example of node elimination                                                  | 18 |

| 2.6  | Pseudocode for Delaunay triangulation                                        | 24 |

| 2.7  | Example of Delaunay triangulation                                            | 25 |

| 2.8  | Pseudocode for Delaunay mesh refinement                                      | 26 |

| 2.9  | Pseudocode for preflow-push                                                  | 31 |

| 2.10 | Bipartite graph of documents and features                                    | 32 |

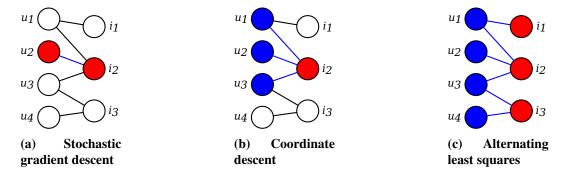

| 2.11 | Data access patterns for different matrix completion algorithms              | 34 |

| 4.1  | STAMP programming model                                                      |    |

| 4.2  | Example Galois program in C++                                                | 46 |

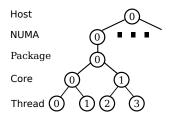

| 5.1  | Example memory hierarchy for a multicore machine                             | 49 |

| 5.2  | Marking a location with exclusive locking                                    | 52 |

| 5.3  | Using method flags to indicate desired support for transactional execution . | 53 |

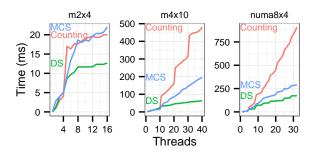

| 5.4  | Execution time of different barrier implementations                          | 54 |

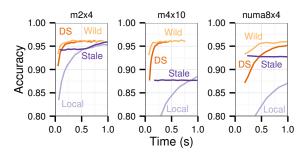

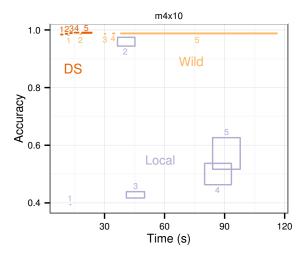

| 5.5  | Convergence of SVM-SGD on small input                                        | 58 |

| 5.6  | Speedup of SVM-SGD                                                        | 59  |

|------|---------------------------------------------------------------------------|-----|

| 5.7  | Convergence of GLMNET on large input                                      | 60  |

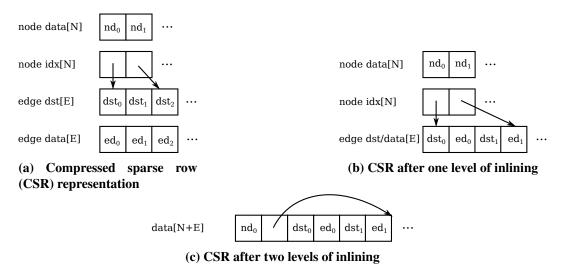

| 5.8  | Illustration of inlining graph data                                       | 61  |

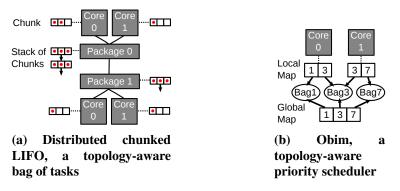

| 6.1  | Organization of distributed chunked LIFO and obim schedulers              | 64  |

| 6.2  | Pseudocode for distributed chunked LIFO                                   | 65  |

| 6.3  | Pseudocode for obim                                                       | 69  |

| 6.4  | Auxiliary functions for Figure 6.3                                        | 70  |

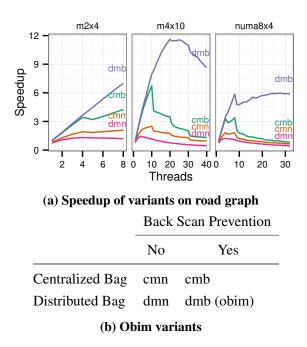

| 6.5  | Scaling of obim and its variants for SSSP application                     | 74  |

| 6.6  | Scheduling specification syntax                                           | 76  |

| 6.7  | Scheduling rule semantics                                                 | 77  |

| 6.8  | Application-specific scheduling specifications                            | 78  |

| 6.9  | Naive bucketed scheduler                                                  | 79  |

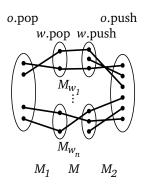

| 6.10 | Relationship between $M_1,M$ and $M_2$ in the proof of Theorem 6.2        | 86  |

| 6.11 | Concrete syntax of HL order (AS1) scheduling policy for PFP application . | 88  |

| 6.12 | Concrete syntax of Global: $G_1$ Local: $L_1$                             | 88  |

| 6.13 | Relative performance when varying synthesizer optimizations               | 89  |

| 6.14 | Datasets used in scheduler synthesis evaluation                           | 90  |

| 6.15 | Runtime of serial applications                                            | 92  |

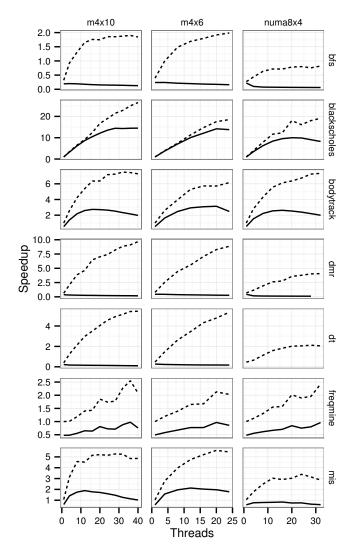

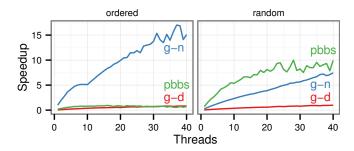

| 6.16 | Speedup over best serial applications                                     | 93  |

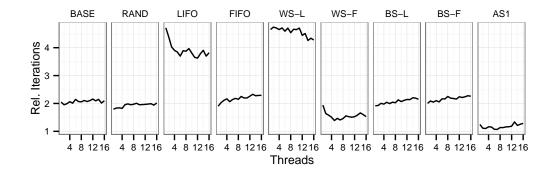

| 6.17 | Relative number of committed to total iterations for DMR                  | 94  |

| 6.18 | Relative number of committed to total iterations for DT                   | 95  |

| 6.19 | Relative number of committed iterations to serial version for PFP         | 96  |

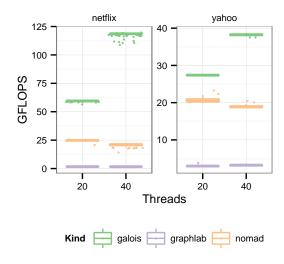

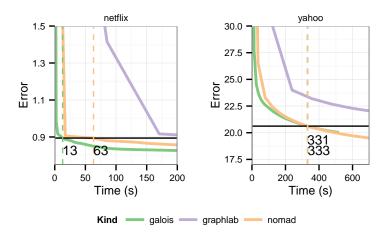

| 6.20 | Throughput of matrix completion operators                                 | 98  |

| 6.21 | Convergence of matrix completion                                          | 99  |

| 7.1  | Deterministic scheduler                                                   | 106 |

| 7 2  | Auxiliary functions for deterministic scheduler                           | 107 |

| 7.3  | Abort ratio and task execution rates                                                                     |

|------|----------------------------------------------------------------------------------------------------------|

| 7.4  | Atomic updates by application                                                                            |

| 7.5  | Speedup with and without CoreDet system on non-deterministic programs $$ . $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ |

| 7.6  | Speedup of selected deterministic and non-deterministic variants 122                                     |

| 7.7  | Baseline times for speedup calculations in deterministic evaluation 123                                  |

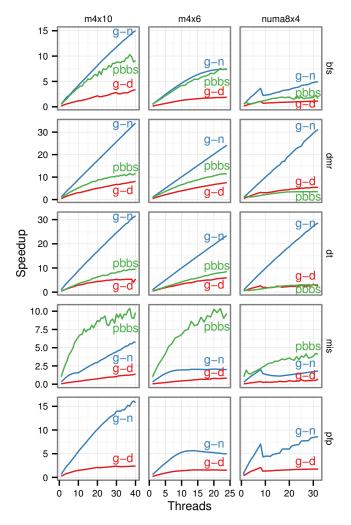

| 7.8  | Performance of variants relative to PBBS                                                                 |

| 7.9  | Performance without continuation optimization                                                            |

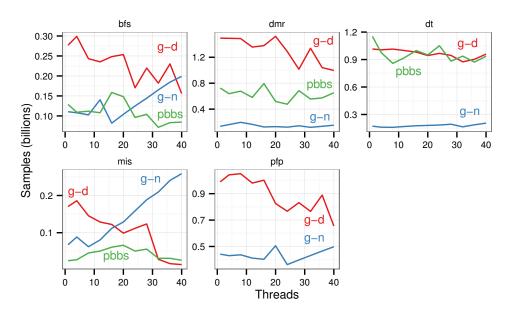

| 7.10 | DRAM performance                                                                                         |

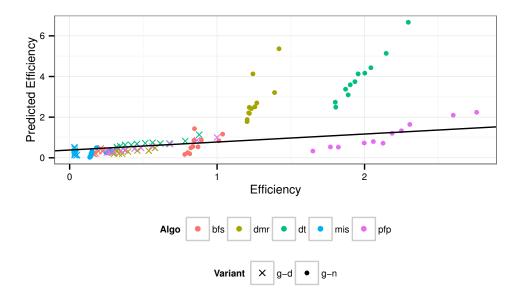

| 7.11 | Predicted efficiency across applications, variants and thread counts 129                                 |

| 7.12 | Effect of reordering input                                                                               |

| 8.1  | Original STAMP data structures and their scalable alternatives 137                                       |

| 8.2  | Example of converting fine-grain transactions into loop-based ones 140                                   |

| 8.3  | Scheduling virtualized transactions                                                                      |

| 8.4  | Comparison of Stampede and STAMP programs                                                                |

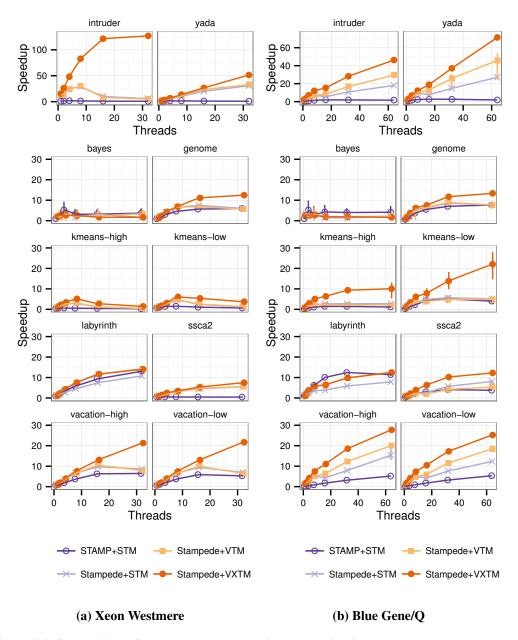

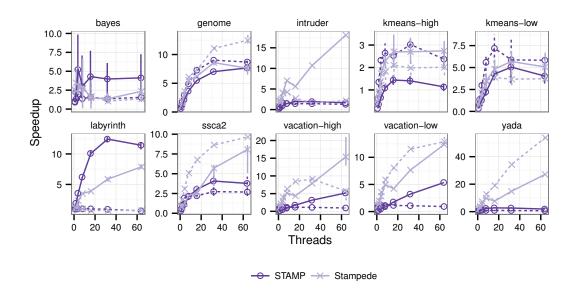

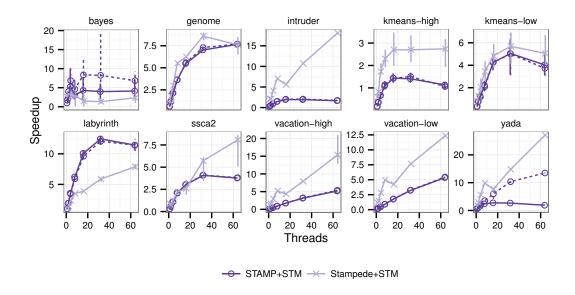

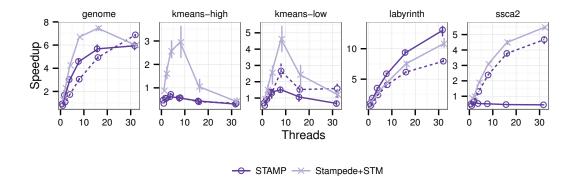

| 8.5  | Speedup of Stampede over STAMP sequential baseline                                                       |

| 8.6  | Speedup of STAMP and Stampede programs with STM and HTM 146                                              |

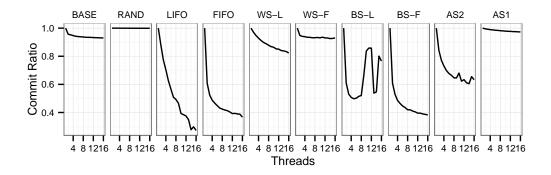

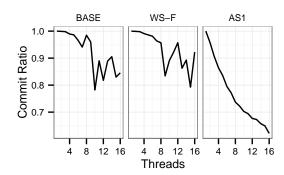

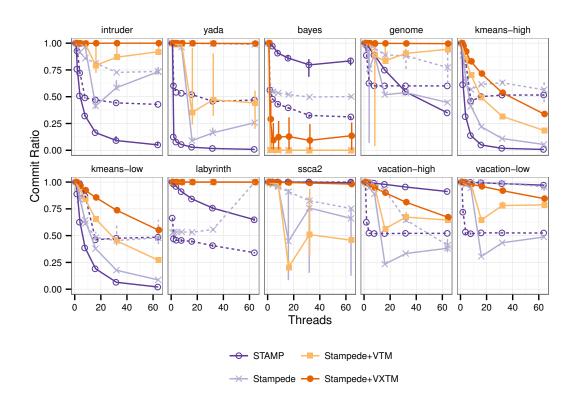

| 8.7  | Commit ratios                                                                                            |

| 8.8  | Performance of STAMP programs with scalable malloc                                                       |

| 8.9  | Performance of STAMP programs with XTM                                                                   |

| 8.10 | Approximate lines of code for each DSL feature                                                           |

| 8.11 | Summary of application differences                                                                       |

| 8.12 | Input characteristics                                                                                    |

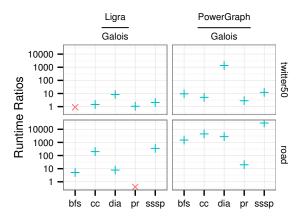

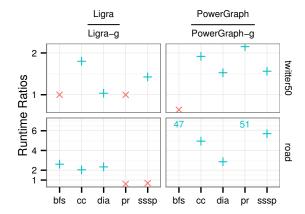

| 8.13 | Ratio of Ligra and PowerGraph runtimes to Galois                                                         |

| 8.14 | Ratio of Ligra and PowerGraph runtimes to Ligra-g and PowerGraph-g 162                                   |

| 8.15 | Runtime for DSLs and Galois with 40 threads                                                              |

| 8.16 | Approximate diameters computed                                                                           |

| 8 17 | Runtime of PowerGraph on distributed system 165                                                          |

| 8.18 | Runtime for DSLs and Galois with 8 threads | .66 |

|------|--------------------------------------------|-----|

| 8.19 | Runtime of out-of-core DSLs                | 68  |

# **Chapter 1**

## Introduction

Computing devices play a central role in society. With the rise of data centers, which accounted for 2% of domestic energy consumption in 2012 (Natural Resources Defence Council, 2014), and the ubiquity of mobile devices, there is increasing need to improve the efficiency of computation to reduce energy consumption. The best way to improve efficiency is to exploit parallelism and to minimize data movement.

This dissertation addresses performance through the lens of programming models; it investigates what software program abstractions lead to high performance programs. One traditional and successful model for programmer productivity is thinking of a program as an algorithm over data structures or, in the words of Niklaus Wirth, Program = Algorithm + Data Structure (Wirth, 1978). This model improves productivity because it divides writing a program into two parts: algorithms that are specific to the problem at hand, and data structures that are more general and can be reused among different programs.

This dissertation argues that parallel programs require a more refined model. The algorithm itself should be divided into parts, Algorithm = Operator + Schedule. The operator is the core computation that is specific to a problem, and the schedule is how the computation is mapped to particular hardware resources in time. In the same way data structures are reused among sequential programs, schedulers should be reused among parallel programs.

Given a decomposition of a program into *activities* or tasks, the *scheduling problem* is the assignment of these activities to processors, and the specification of an order in which each processor should execute the activities assigned to it. Scheduling is important for both sequential and parallel implementations of algorithms since it may affect locality and load balance; it may even effect the total amount of work performed by some programs, as will be shown shortly.

Scheduling can be done either statically by a compiler or dynamically by a runtime or operating system. Static scheduling can be used when dependences between activities are known statically and the execution time of each activity can be estimated accurately at compile-time. Stencil computations are the classic examples of algorithms amenable to static scheduling (for example see (Stock et al., 2014)). Dynamic scheduling is useful for problems in which (1) dependences between activities cannot be elucidated statically, or (2) new work is created dynamically so the number of activities is not known statically, or (3) accurate estimates of the time required to execute each activity are not available. The vast majority of algorithms, including almost all *irregular* algorithms (algorithms where the key data structures are sparse graphs) require dynamic scheduling.

For the most part, prior work on dynamic scheduling has focused on problems in which there are no dependences between activities, and new work is not created dynamically, so the only problem is that the time required to execute an activity cannot be determined accurately. Self-scheduling of DO-ALL loops in OpenMP is the classic example. Activities in this case correspond to iterations of the DO-ALL loop; the number of iterations is known before the loop is executed, and it is assumed that there are no dependences between iterations. However, different iterations may take different and unpredictable amounts of time to execute, so to ensure good load balance, OpenMP provides scheduling policies such as chunked dynamic self-scheduling, in which a processor gets a chunk of k iterations every time it needs work, and guided self-scheduling, in which the chunk size decreases steadily as the loop nears completion (Dagum and Menon, 1998). Chunking reduces the

overheads of scheduling and may improve locality.

More recently, attention has shifted to task-parallelism in which new activities are created dynamically, although it is still assumed that all activities are independent except for fork-join control dependences. In OpenMP 3.0, there is support for different dynamic scheduling policies such as breadth-first and work-first policies (Duran et al., 2008). Another popular technique is *work-stealing*. In work-stealing, each thread has a local deque that contains activities to execute. When a thread's local deque is empty, it selects the local deque of another thread, the victim, and tries to steal activities from it. Work-stealing is parameterized by the order maintained in the local deque (usually LIFO) and how a thread selects a victim (usually at random). Work-stealing was implemented in MultiLisp (Halstead, 1985) and was later popularized by the Cilk language (Blumofe et al., 1995), where it is used to implement fork-join parallelism. It is now available in many programming environments: Intel Threading Building Blocks (TBB) (Reinders, 2007) the Java library (Lea, 2000) and the .Net library (Leijen et al., 2009).

The key assumptions in such work on task-parallelism are that any dependences between activities are captured by fork-join control dependences and are known statically. While these assumptions are reasonable for regular (i.e., dense-array) algorithms and divide-and-conquer algorithms, they do not hold for most irregular graph algorithms because dependences in these algorithms are complex functions of runtime values (e.g., the shape of the graph and the values on nodes and edges), which may themselves change during execution.

An abstract description of parallelism in irregular algorithms is the following. At each step of the algorithm, there are certain *active nodes* in the graph where computation needs to be performed. Performing the computation at an active node may require reading or writing other graph nodes and edges, known collectively as the *neighborhood* of that activity. The neighborhood is usually distinct from the neighbors of the active node. In general, there are many active nodes in a graph, so a sequential implementation must pick

one of them and perform the appropriate computation.

In *unordered algorithms*, which are the focus of this dissertation, the implementation is allowed to pick *any* active node for execution. In contrast, *ordered algorithms* have a specific order in which active nodes must be executed. For unordered algorithms, the final output may be different for different orders of executing active nodes, but all such outputs are acceptable, a feature known as *don't-care non-determinism*. A parallel implementation of such an algorithm can process active nodes simultaneously, provided their neighborhoods do not overlap. This condition can be relaxed but is sufficient for correct execution. In general, the neighborhood of an activity is not known until the activity has finished execution.

The parallelism that results from processing activities in parallel subject to neighborhood and ordering constraints is *amorphous data-parallelism* (ADP) (Pingali et al., 2011). Efficient exploitation of amorphous data-parallelism requires far more sophisticated runtime support than fork-join parallelism or DO-ALL parallelism for the following reasons.

- 1. In most irregular algorithms, nodes become active dynamically, so the number of activities is not known statically.

- 2. In general, the neighborhood of an activity may be known only after the activity completes execution. Therefore, it may be necessary to use optimistic or speculative parallelization.

- 3. Most importantly, the number of activities that are executed by an algorithm may be different for different schedules. In some cases, the amount of work may differ by an asymptotic factor, as shown in the following chapter. If this is the case, it is critical to capture the scheduling of the more work-efficient scheduling.

For these reasons, even *sequential* implementations of irregular algorithms often use handcrafted, algorithm-specific scheduling policies; for example, some mesh refinement algorithms process triangles or tetrahedra in decreasing size order since this can reduce the

total amount of refinement work (Miller, 2004). Section 2.3 gives examples of the policies used in the literature. However, following these orders strictly can dramatically reduce parallelism, so parallel implementations of irregular algorithms often use more complex scheduling policies that trade off extra work for increased parallelism. These schedulers are themselves concurrent data structures and add to the complexity of parallel programming. In addition, they cannot easily be reused for other applications.

This dissertation introduces a flexible and efficient approach for specifying and synthesizing schedulers for sequential and parallel implementations of irregular algorithms. It distinguishes between *scheduling policies*, which are informal descriptions of the order in which activities should be processed (e.g., LIFO, FIFO, etc.), *scheduling specifications*, which are formal descriptions of scheduling policies, and *schedulers*, which are concrete implementations of scheduling specifications. A *schedule* is a specific mapping of activities to processors in time.

Of course, to address performance, efficient scheduling must be combined with scalable data structures. The main contribution of this dissertation is the design and implementation of a parallel programming model for unordered algorithms based on an extensible scheduling policy DSL and a library of parallel data structures. This system is called the Galois system.

Chapter 2 describes the core program abstraction in Galois, the operator formulation, and it also shows how the operator formulation is a natural abstraction for many algorithms. Chapter 3 summarizes existing programming models for parallelism. Chapter 4 introduces the design principles that guide the implementation of the Galois system. Chapter 5 and Chapter 6 describe the implementation concretely in terms of data structures and scheduling, respectively. To address one concern with unordered algorithms, their non-determinism, Chapter 7 presents a deterministic scheduling algorithm that permits unordered algorithms to be run non-deterministically or deterministically as desired.

To support the utility of the Galois system, Chapter 8 evaluates the Galois system

in two ways. First, it shows that the design principles introduced in Chapter 4 are sufficient conditions for scalability by showing that their manual application can substantially improve the performance of the STAMP benchmark suite, a well-studied but until now poorly performing benchmark suite. Second, Chapter 8 shows that the Galois system is a significant improvement over existing parallel programming models because (1) existing programming models can be reimplemented in Galois and obtain better performance than their original implementations and (2) the Galois system can express more sophisticated algorithms beyond the capabilities of previous systems, which result in orders of magnitude performance improvements for many graph analytics problems.

# Chapter 2

# A Data-Centric View of Parallelism and Locality

This chapter introduces the operator formulation of programs. Section 2.1 describes a model problem that illustrates the key ideas, and Section 2.2 generalizes the basic issues in the model problem to develop the operator formulation. Section 2.3 shows how various algorithms can be expressed with this formulation.

#### 2.1 Model Problem: SSSP

Given a weighted graph G=(V,E,w), where V is the set of nodes, E is the set of edges, and w is a map from edges to edge weights, the single-source shortest-paths (SSSP) problem is to compute the distance of the shortest path from a given source node  $s \in V$  to each node in the graph. Edge weights can be negative, but it is assumed that there are no negative weight cycles.

In most SSSP algorithms, each node is given a label that holds the distance of the shortest known path from the source to that node. This label  $\mathbf{dist}(v)$  is initialized to 0 for

Portions of this chapter have previously appeared in (Pingali et al., 2011), where the TAO classification was originally described.

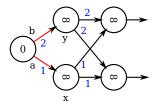

Figure 2.1: Example of SSSP (edge weights shown in blue)

s and  $\infty$  for all other nodes. The basic SSSP operation is *edge relaxation* (Cormen et al., 2009): given an edge (u, v) such that  $\mathbf{dist}(u) + w(u, v) < \mathbf{dist}(v)$ , the value of  $\mathbf{dist}(v)$  is updated to  $\mathbf{dist}(u) + w(u, v)$ . Each relaxation, therefore, lowers the  $\mathbf{dist}$  label of a node, and when no further relaxations can be performed, the resulting node labels are the shortest distances from the source to the nodes, regardless of the order in which the relaxations were performed. When relaxations are applied arbitrarily, this algorithm is called chaotic relaxation (Chazan and Miranker, 1969).

Nevertheless, some relaxation orders may converge faster and are therefore more work-efficient than others. For example, consider the graph in Figure 2.1. Edges in the graph where edge relaxation can be performed are shown in red. If edge b is relaxed, it will create new opportunities for edge relaxation at all the outgoing edges of node y. If those newly enabled edges are processed before edge a, those edges will be processed again once edge a is relaxed. However, if edge a is processed before edge b, processing edge b will not create any new opportunities for edge relaxation, and the total number of relaxation operations is reduced. Dijkstra's SSSP algorithm (Dijkstra, 1959) applies edge relaxation to all the outgoing edges of a node and relaxes each node just once by using the following strategy: from the set of nodes that have not yet been relaxed, pick one that has the minimal label.

However, Dijkstra's algorithm does not have much parallelism due to its reliance on a centralized priority queue, so some parallel implementations of SSSP use this rule only as a heuristic for priority scheduling: given a choice between two edges with different dist labels on their sources, they pick the one with the smaller label, but they may also

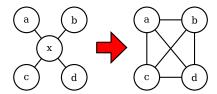

Figure 2.2: Illustration of the operator formulation

execute some edges out of priority order to exploit parallelism. One such algorithm is deltastepping SSSP (Meyer and Sanders, 1998). The price of this additional parallelism is that some nodes may be relaxed repeatedly. A balance must be struck between controlling the amount of extra work and exposing parallelism.

#### 2.2 Operator Formulation

To discuss common issues in parallel programs, it is convenient to use the terminology of the *operator formulation* (Pingali et al., 2011), a data-centric programming model for expressing parallelism in regular and irregular algorithms. The basic concepts of the operator formulation are illustrated in Figure 2.2.

- *Active nodes* are nodes in the graph where computation must be performed; they are shown as red dots in Figure 2.2.

- The computation at an active node is called an *activity*, and it results from the application of an *operator* to the active node. In some algorithms, it is more convenient to think in terms of active *edges* rather than active nodes. Without loss of generality, we will use the term active nodes. The operator is a composition of elementary graph operations with other arithmetic and logical operations.

Note that graphs themselves are general data structures; any other data structure can

be expressed as a graph. An array is a node with ordered neighbors. A pointer-based data structure is a graph of memory locations with edges corresponding to pointers to other memory locations.

• The set of graph elements read and written by an activity is its *neighborhood*. The neighborhood of the activity at each active node in Figure 2.2 is shown as a "cloud" surrounding that node. If there are several data structures in an algorithm, neighborhoods may span multiple data structures. In general, neighborhoods are distinct from the set of immediate neighbors of the active node, and neighborhoods of different activities may overlap. In a parallel implementation, the semantics of reads and writes to such overlapping regions must be specified carefully. The general term for what happens when two activities cannot proceed in parallel due to their neighborhoods is a *conflict*.

The SSSP algorithms described in the previous section can be expressed in the operator formulation. In chaotic relaxation and Dijkstra's algorithm, the operator is the edge relaxation operator. The active edges are edges where edge relaxation can be applied, and the neighborhood is the active edge and the corresponding endpoints of the edge.

In general, there may be multiple active nodes, so an algorithm must specify which order of executing active nodes is valid. There are two classes of ordering. In *unordered algorithms*, any order of processing active nodes is valid. The chaotic relaxation algorithm for SSSP is an example of an unordered algorithm. In *ordered algorithms*, the algorithm has a specific order in which active nodes are processed. Dijkstra's algorithm is an example. In that algorithm, active edges must be processed in priority order.

The operator formulation leads to a natural definition of parallelism.

**Definition 2.1.** Given a set of active nodes and an ordering on it, amorphous data-parallelism (ADP) is the parallelism that arises from simultaneously processing active nodes subject to neighborhood and ordering constraints.

Amorphous data-parallelism generalizes many common notions of parallelism. ADP with no neighborhood or ordering constraints is data parallelism (Hillis and Steele, 1986). ADP with no neighborhood constraints but where activities are ordered according to fork-join dependencies is nested data-parallelism (Blelloch, 1992). One can go even further. Instruction-level parallelism (Hennessy and Patterson, 2003) can be seen as an instance of ADP where (1) activities are processor instructions, (2) activities are ordered according to program instruction order, and (3) conflicts only occur when neighborhoods overlap and at least one activity writes to the overlapping region.

ADP also captures many models of consistency. If (1) conflicts only occur when neighborhoods overlap and at least one activity writes to the overlapping region and (2) active nodes can be processed in any order, then ADP generates serializable executions (Papadimitriou, 1986). If conflicts only occur when two activities have overlapping neighborhoods and both activities write to the overlapping region, then executions satisfy snapshot isolation (Berenson et al., 1995).

The operator formulation and ADP permit an abstract description of algorithms that highlights similarities between algorithms and parallelization techniques across application domains. At first glance, the chaotic relaxation algorithm for SSSP and the relabel-to-front algorithm for maximum flow, described in Section 2.3, seem very different, but it turns out they share many of the same properties in the operator formulation, and optimizations like ordered execution with priorities (e.g., Dijkstra's algorithm) that are used for SSSP also can be used with the maximum flow problem (e.g., HL ordering (Cherkassy and Goldberg, 1995)).

The next section gives a baseline execution model for programs in the operator formulation, and Section 2.2.2 and Section 2.2.3 describe two techniques to analyze and optimize programs based solely on their structure in the operator formulation.

#### 2.2.1 Baseline Execution Model

The baseline execution model is speculative execution. Shared data structures like graphs are stored in shared-memory, and active nodes are processed by some number of threads. A thread picks an active node from a workset<sup>1</sup> and speculatively applies the operator to that node, making calls to a graph library to perform operations as needed. The neighborhood of an activity grows incrementally as graph methods touch areas of the graph. To detect conflicts, the graph maintains logical locks associated with each node or edge of the graph. These locks are acquired by a thread before it can access that element. Locks are held until the activity terminates. If a thread acquires a logical lock for writing that has been already acquired by another thread (for reading or writing), a conflict is reported to the runtime system, which rolls back one of the conflicting activities. Lock manipulation is performed entirely by the methods in the graph class. In addition, to support rollback, each graph method that modifies the graph makes a copy of the data before modification.

If active elements are unordered, the activity commits when the application of the operator is complete, and all acquired locks are then released. If active elements are ordered, active nodes can still be processed in any order, but they must appear to commit in serial order. This can be implemented using a data structure similar to a reorder buffer in out-of-order processors. In this case, activities that have been executed out-of-order keep their locks and are held in a reorder buffer until they reach the head of the buffer or are aborted. Alternatively, a dependence graph can be used to schedule ordered tasks; although, whether dependence graph scheduling is possible depends on what the order is and how tasks behave (Hassaan et al., 2015).

For unordered active elements, transactional memory (Harris and Fraser, 2003; Herlihy and Moss, 1993) can be used to accelerate conflict detection and rollback in hardware, see Section 8.1.

What constitutes a neighborhood conflict can be refined or coarsened. A more re-

<sup>&</sup>lt;sup>1</sup>Throughout this dissertation, the colloquial term workset is used, although more formally, these objects behave as bags or multisets because they may contain duplicate items.

```

Workset ws(G.nodes())

foreach Node p in ws:

// Phase 1: reading neighborhood

int s = 0

for Node n in G.neighbors(p):

s += G.getData(n)

// Failsafe point

// Phase 2: writing to neighborhood

// elements written to were read in Phase 1

for Node n in G.neighbors(p):

G.getData(n) += s

```

Figure 2.3: Example of a cautious operator

fined conflict detection scheme would allow activities to proceed in parallel as long as the corresponding method calls commute with respect to the logical operations they are implementing (Kulkarni et al., 2011). Accesses in disjoint areas of neighborhoods are presumed to commute. A more coarse conflict detection scheme would allow activities to proceed only if their neighborhoods are disjoint. Two activities reading or writing the same graph element would result in a conflict. This scheme can be implemented with exclusive logical locks that use a compare-and-set instruction to mark a graph element with the id of the activity that touches it (see Section 5.2).

This speculative executor is sufficient to execute any program in the operator formulation, but it may be inefficient in practice. For instance, the polyhedral model (Feautrier and Lengauer, 2011) is a methodology that can optimize and schedule array programs with affine subscripts at compile time without speculation. One way to address the performance concerns of the baseline execution model is to identify specific program properties that make programs amenable to certain analysis or execution strategies and use a specialized executor instead of the baseline executor for these cases.

As an example, sometimes tasks are *cautious* (Méndez-Lojo et al., 2010), which means they read their entire neighborhood before writing to any element of it (see Figure 2.3 for an example). For unordered cautious tasks, conflict detection and correction can be done using lightweight mechanisms because the synchronization problem reduces to the

Figure 2.4: TAO analysis of algorithms

well-known dining philosopher's problem (Chandy and Misra, 1984). Conceptually, each abstract location can be *acquired* by an owner. The execution of a task can be divided into two phases: in the first phase, a task reads locations but does not write to any of them, acquiring ownership of these locations, and in the second phase, the task writes to some locations, but it does not write to any location that it did not read in the first phase, because it is cautious. The point between the first and second phase is called the *failsafe point*. For cautious tasks, conflicts are detected in the first phase, and rollback is implemented simply by releasing ownership of all locations. Once the failsafe point has been crossed, global data structures can be updated in place without the need for backup copies of modified data.

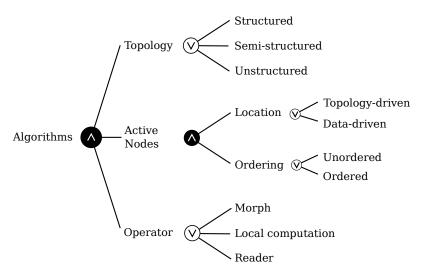

In this spirit, the following two sections describe methods of classifying programs with an eye towards identifying properties that are useful for optimized execution. The first is TAO analysis (Pingali et al., 2011) (see Section 2.2.2), which classifies programs along three dimensions: topology, active nodes and ordering. The second method focuses on properties of iterative fixpoint algorithms (see Section 2.2.3).

#### 2.2.2 TAO Analysis

TAO analysis (Pingali et al., 2011) is a method for structural analysis of algorithms with respect to their possible parallelizations. It is based on classifying algorithms and data structures along three dimensions.

- 1. Topology: graph topologies are classified according to the Kolmogorov complexity of their descriptions. Highly structured topologies can be described concisely with a small number of parameters, while unstructured topologies require verbose descriptions. The topology of a graph is an important indicator of the kinds of optimizations available to algorithm implementations; for example, algorithms in which graphs have highly structured topologies may be more amenable to static analysis and optimization.

- Structured: an example of a structured topology is a graph consisting of labeled nodes and no edges. This is isomorphic to a set or multiset; its topology can be described by a single number, the number of elements in the set or multiset. If the nodes are totally ordered, the graph is isomorphic to a sequence of stream. Cliques, i.e., graphs in which every pair of nodes is connected by a labeled edge, are isomorphic to square dense matrices with row/column numbers coming from the total ordering of the nodes. Their topology is completely specified by a single number, the number of nodes in the clique.

- *Semi-structured*: trees are classified as semi-structured topologies. Although trees have useful structural invariants, there are many trees with the same number of nodes and edges.

- *Unstructured*: general graphs fall in this category. Even among general graphs, some may be considered more structured than others. For instance, graphs whose nodes can be divided into partitions with a small edgecut versus graphs whose partitions have a large edgecut value.

- 2. *Active nodes*: This dimension describes how nodes become active and the order in which they must be processed.

- Location: nodes can become active in a topology-driven or data-driven manner. In topology-driven algorithms, the execution of the operator at some active node does not cause other nodes to become active. Common examples are algorithms that iterate over all the nodes or edges of a graph. In data-driven algorithms, an activity at one node may cause other nodes to become active, so nodes become active in a data-dependent and unpredictable manner. An example is the chaotic relaxation algorithm for SSSP.

- *Ordering*: As discussed in above, active nodes in some algorithms are ordered whereas in others they are unordered.

- 3. *Operator*: This final dimension describes how operators modify the graph.

- Morph: a morph operator may modify its neighborhood by adding or deleting nodes and edges, and it may also update values on nodes and edges. The Delaunay mesh refinement operator described in Section 2.3 is an example.

- Local computation: a local computation operator may update values stored on nodes and edges in its neighborhood, but it does not change the graph connectivity. Finite-difference computations are a classic example. The chaotic relaxation algorithm is another.

- Reader: an operator is a reader for a data structure if it does not modify it in any way. For example, the ray tracing operator is a reader for the scene being rendered.

These definitions can be generalized in the obvious way for algorithms that deal with multiple data structures. In that case, neighborhoods span multiple data structures, and the classification of an operator is with respect to a particular data structure. For example, in matrix

multiplication, C = AB, the operator is a local computation for C and a reader for matrices A and B.

TAO analysis can be used to organize programs into classes that share the same parallelization concerns. For topology-driven active nodes, if the topology and operator are known at compile-time, which is the case for many dense matrix codes, parallelization can also occur at compile-time in principle. In practice, to adapt to the variance in the execution time of tasks, high performance parallelizations of dense matrix codes may also include a runtime component for load balancing, for instance see the DAGuE system (Bosilca et al., 2012). A similar trend occurs in data-parallel codes, which also can be parallelized at compile-time, and often use a work-stealing scheduler (Blumofe et al., 1995) to balance work among threads at runtime, for instance see (Baskaran et al., 2009).

For sparse matrix codes, the topology (i.e., the structure of the sparse matrix) is not known until the input is read by the program. Compiler-based parallelization cannot be used, and the earliest time that parallelization can be attempted is *just-in-time*, after the input is read but before the bulk of computation begins. This is called the inspector-executor (Das et al., 1995) approach. If the matrix is discovered to be relatively dense or if it has dense subregions (e.g., nearly block-diagonal), the executor in the inspector-executor approach can apply dense matrix subroutines for parts of the sparse matrix; however, in terms of the classification of techniques, the earliest point at which the decision to apply these dense matrix subroutines is when the input is read even though the dense subroutines themselves may be parallelized at compile-time.

At the most extreme, parallelization may be done at *runtime*, interleaved with the parallelized computation itself. This is the case with data-driven active nodes and with most morph computations. Data-driven active nodes require runtime parallelization because active nodes are not known without executing the activity.

A similar conclusion holds for morph operators, but one special case is when the modification performed by the morph can be efficiently simulated without running the op-

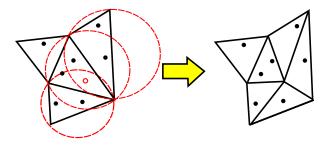

Figure 2.5: Example of node elimination of node x

erator itself. Examples are sparse matrix factorization codes like Cholesky and LU decomposition. In these codes, the operator performs a morph called *node elimination*, in which a node is removed from a graph and edges are inserted as needed between its erstwhile neighbors to make a clique (see Figure 2.5 for an example). This operator can simulated by a just-in-time analysis with simple arithmetic operations although the operator itself requires floating-point operations to compute the factored matrix values. In this application area, the simulation of the factorization operator is called *symbolic factorization* and is an important step in high-performance, parallel implementations (Gilbert and Schreiber, 1992). Symbolic factorization builds a dependence graph called an elimination tree. The actual factorization, called *numerical factorization*, uses the elimination tree to schedule tasks. LU has an analogous operator, but *pivoting* is often done to improve numerical stability. In terms of TAO analysis, the active nodes are data-driven, which means runtime techniques must be used for parallelization. To facilitate just-in-time parallelization, parallel LU implementations use *partial pivoting* instead, in which the operator is coarsened to multiple nodes and pivoting only occurs within a coarsened operator.

TAO analysis is useful for understanding which parallelization strategies are feasible given a program. The following section describes another type of analysis that explores possible ways of implementing a particular class of programs, iterative fixpoint algorithms.

#### 2.2.3 Analysis of Iterative Fixpoint Algorithms

Iterative fixpoint algorithms are programs that consist of operators that repeatedly read and write memory locations until some convergence property is met. A special case of iterative

fixpoint algorithms are asynchronous fixpoint algorithms (Bertsekas and Tsitsiklis, 1989). They are asynchronous because values read may not correspond to the value most recently written. Asynchronous algorithms<sup>2</sup> are amenable to parallel and distributed computation because they can tolerate long commutation delays. One example of an asynchronous fixpoint algorithm already introduced in this chapter is the chaotic relaxation algorithm for SSSP.

Iterative algorithms as a class tend to benefit from the same kinds of transformations. Since some of these transformation change the operator or the asymptotic behavior of the algorithm, they are not typical optimizations in the compiler community sense of the term, but nevertheless, they are techniques that application programmers use to improve the performance of programs.

The foremost transformation is tolerating asynchrony. Whether a program can tolerate stale updates is a deep algorithmic property, but once known, parallelizing systems can exploit this property to restructure communication to follow more efficient patterns at the machine level. For instance, as originally developed, using stochastic gradient descent (SGD) for solving linear support vector machines (SVMs) requires reading the most recent values for the weight vector, but the recently introduced Hogwild approach (Recht et al., 2011) eschews a serializable locking policy for racy reads and writes. This is possible because the algorithm tends to still converge even in the presence of noisy or stale data (see Section 5.4).

The remaining transformations can be summarized as follows: *what* does the operator do, *where* in the graph is it applied, and *when* is the corresponding activity executed?

What does the operator do? In general, the operator expresses some computation on the neighborhood elements. In some graph problems such as SSSP, operators can be implemented in two general ways called here *push* style or *pull* style. A push-style operator reads

<sup>&</sup>lt;sup>2</sup>In contrast to asynchronous algorithms which will converge for any communication delay, partially asynchronous algorithms only converge when communication delays are bounded. For the purpose of the discussion in this section, asynchronous and partially asynchronous algorithms are treated interchangeably.

the label of the active node and writes to the labels of its neighbors; information flows from the active node to its neighbors. A push-style SSSP operator attempts to update the dist label of the immediate neighbors of the active node by performing relaxations with them. In contrast, a pull-style operator writes to the label of the active node and reads the labels of its neighbors; information flows to the active node from its neighbors. A pull-style SSSP operator attempts to update the dist label of the active node by performing relaxations with each neighbor of the active node. In a parallel implementation, pull-style operators require less synchronization since there is only one writer per active node.

Usually, the operator represents the smallest logical unit of parallel computation, but in some cases, the convergence of a fixpoint algorithm can be sped up by coarsening the graph to speed up the flow of information across the graph. In its simplest form, coarsening may simply be scheduling multiple activities as one unit or treating subgraphs as a single node or edge, but the transformations used in practice may also incorporate algorithmic performance improvements that change the behavior of the operator or the representation of subgraphs for the coarsened algorithm. The multigrid method for solving linear systems is a classic example as well as elimination-based dataflow analysis of programs (Allen and Cocke, 1976). The basic idea is to transform the graph into a smaller subproblem, solve the subproblem and interpolate the results back onto the original graph. The transformation, subproblem solving and interpolation steps are application-specific. A related idea is preconditioning, which is used in iterative linear solvers to preprocess an input to improve convergence or performance; in this case, the core operation remains the same whether or not preconditioning is used.

**Where is the operator applied?** As in TAO analysis, active nodes can be *topology-driven* or *data-driven*.

In a *topology-driven* computation, active nodes are defined structurally in the graph, and they are independent of the values on the nodes and edges of the graph. The Bellman-Ford SSSP algorithm is an example (Bellman, 1958; Ford and Fulkerson, 1962); this al-

gorithm performs |V| supersteps, each of which applies a push-style or pull-style operator to all the edges. Practical implementations terminate the execution if a superstep does not change the label of any node. Topology-driven computations can be parallelized by partitioning the nodes of the graph between processing elements.

In a *data-driven* computation, nodes become active in an unpredictable, dynamic manner based on data values, so active nodes are maintained in a workset. In a data-driven SSSP program, only the source node is active initially. When the label of a node is updated, the node is added to the workset if the operator is push-style; for a pull-style operator, the neighbors of that node are added to the workset. Data-driven implementations can be more work-efficient than topology-driven ones since work is performed only where it is needed in the graph. However, load-balancing is more challenging, and careful attention must be paid to the design of the workset to ensure it does not become a bottleneck.

When is an activity executed? When there are more active nodes than threads, the implementation must decide which active nodes are prioritized for execution and when the side-effects of the resulting activities become visible to other activities. There are two popular models that are called here *autonomous scheduling* and *coordinated scheduling*.

In autonomous scheduling, activities are executed with transactional semantics, so their execution appears to be atomic and isolated. Parallel activities are serializable, so the output of the overall program is the same as some sequential interleaving of activities. Threads retrieve active nodes from the worklist and execute the corresponding activities, synchronizing with other threads only as needed to ensure transactional semantics. This fine-grain synchronization can be implemented using speculative execution with logical locks or lock-free operations on graph elements. The side-effects of an activity become visible externally when the activity commits.

Coordinated scheduling, on the other hand, restricts the scheduling of activities to rounds of execution, as in the Bulk-Synchronous Parallel (BSP) model (Valiant, 1990). The execution of the entire program is divided into a sequence of supersteps separated by barrier

synchronization. In each superstep, a subset of the active nodes is selected and executed. Writes to shared-memory, in shared-memory implementations, or messages, in distributed-memory implementations, are considered to be communication from one superstep to the following superstep. Therefore, each superstep consists of updating memory based on communication from the previous superstep, performing computations, and then issuing communication to the next superstep. Multiple updates to the same location are resolved in different ways as is done is the varieties of PRAM models, such as by using a reduction operation (JaJa, 1992).

Application-specific priorities Of the different algorithm classes discussed above, data-driven, autonomously scheduled algorithms are the most difficult to implement efficiently. However, they converge much faster than algorithms that use coordinated scheduling for some problems (Bertsekas and Tsitsiklis, 1989). Moreover, for high-diameter graphs like road networks, data-driven autonomously scheduled algorithms may be able to exploit more parallelism than algorithms in other classes; for example, in BFS, if the graph is long and skinny, the number of nodes at each level will be quite small, limiting parallelism if coordinated scheduling is used.

Autonomously scheduled, data-driven graph analytics algorithms benefit from application-specific priorities and priority scheduling to balance work-efficiency and parallelism. One example is delta-stepping SSSP (Meyer and Sanders, 1998), the most commonly used parallel implementation of SSSP. The workset of active nodes is implemented, conceptually, as a sequence of bags, and an active node with label d is mapped to the bag at position  $\lfloor \frac{d}{\Delta} \rfloor$ , where  $\Delta$  is a user-defined parameter. Idle threads pick work from the lowest-numbered non-empty bag, but active nodes within the same bag may execute in any order relative to each other. The optimal value of  $\Delta$  depends on the graph.

The general picture is the following. Each task t is associated with an integer *priority(t)*, which is a heuristic measure of the importance of that task for early execution relative to other tasks. For delta-stepping SSSP, the priority of an SSSP relaxation task is the value

$\lfloor \frac{d}{\Delta} \rfloor$ . A task  $t_1$  has earlier priority than a task  $t_2$  if  $\mathbf{priority}(t_1) < \mathbf{priority}(t_2)$ . It is permissible to execute tasks out of priority order, but this may possibly lower work efficiency.<sup>3</sup> A good parallel runtime system must permit application programmers to specify such application and input-specific priorities for tasks, and the system must schedule these fine-grain tasks with minimal overhead and minimize priority inversions.

### 2.3 Parallel Algorithms

This section introduces several algorithms using the concepts of the operator formulation, TAO analysis and analysis of fixpoint algorithms. Pseudocode for these algorithms is written using the Galois programming model (see Chapter 4), which is a sequential, object-oriented programming model augmented with a *Galois unordered-set iterator*, which is similar to set iterators in C++ or Java but permits new items to be added to a set while it is being iterated over.

• foreach T e in S: B(e) — The loop body B(e) is executed for each item e of type T in set S. The order in which iterations execute is indeterminate and can be chosen by the implementation. There may be dependences between the iterations. An iteration may add items to S during execution.

### 2.3.1 Delaunay Triangulation

Finding the Delaunay triangulation (DT) of a set of points is a classic computational geometry problem. There are many algorithms for finding the triangulation; this section describes the incremental algorithm of Bowyer and Watson (Bowyer, 1981; Watson, 1981). Initially, there is one large triangle that covers all the points. Then, point p calculates the triangle that contains it and calculates all triangles whose circumcircles include p. This is the cavity

<sup>&</sup>lt;sup>3</sup>If the priority order must be strictly followed, the algorithm is ordered and different schedulers must be applied (Hassaan et al., 2015). This dissertation focuses on implementing unordered algorithms.

```

1 Workset ws(points)

2 foreach Point p in ws:

3    Triangle t = findTriangleContaining(p)

4    Cavity c(t)

5    c.expand()

6    c.retriangulate()

7    G.update(c)

```

Figure 2.6: Pseudocode for Delaunay triangulation

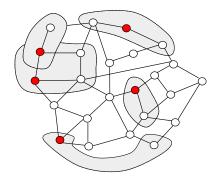

of p. Finding the triangle that contains a point can be accomplished with a spatial acceleration structure like a kd-tree or oct-tree over triangles. The cavity is re-triangulated, p is removed, and the next point is processed. This process continues until there are no more points to process. Figure 2.6 shows the pseudocode. G is the graph representing the triangulation. Figure 2.7 shows an example of processing one point. To reduce the amount of time spent updating the acceleration structure, it can be built over a subset of triangles and a geometric search within the mesh can be used to find the enclosing triangle.

All orders of processing points lead to the same Delaunay triangulation. Clarkson and Shor have shown that selecting points at random is optimal (Clarkson and Shor, 1989). Amenta et al. present an algorithm called biased randomized insertion order (BRIO) that takes advantage of spatial locality while still maintaining the optimality of randomness (Amenta et al., 2003). Briefly, let n be the number of points to triangulate. Points are processed in  $\log n$  rounds. The probability that a point is processed in the final round is  $\frac{1}{2}$ . For the remaining points, the probability that they will be processed in the next-to-last round is  $\frac{1}{2}$ , and so on until the first round. For the first round, all remaining points are processed with probability one. Within a round, points are processed according to the spatial divisions of an oct-tree.

### 2.3.2 Delaunay Mesh Refinement

Delaunay mesh refinement (DMR) (Chew, 1993) is an algorithm related to Delaunay triangulation. Given a Delaunay triangulation, triangles may have to satisfy additional quality

Figure 2.7: Example of processing an active point (hollow and red) for Delaunay triangulation. Circles are circumcircles of triangles containing the active point.

constraints beyond that guaranteed by triangulation. To improve the quality of a triangulation, Delaunay mesh refinement iteratively fixes "bad" triangles, which do not satisfy the quality constraints, by adding new points to the mesh and re-triangulating. Refining a bad triangle may itself introduce new bad triangles, but it can be shown that, at least in 2D, this iterative refinement process will terminate and produce a guaranteed-quality mesh. In 3D, naive refinement may terminate with tetrahedral elements with large aspect ratios (Li and Teng, 2001), which adversely affects the convergence and stability of numerical algorithms like the finite element method (Strang and Fix, 1973).

Figure 2.8 shows the pseudocode for this algorithm. It is similar to Delaunay triangulation, except that activities are centered on triangles rather than points. In both cases, a cavity is expanded and re-triangulated. However, in DMR, new bad triangles can be created that must be processed as well. They are tracked in a workset. Additionally, different orders of processing bad triangles lead to different meshes, but all such meshes satisfy the quality constraints and are acceptable outcomes of the refinement process (Chew, 1993). In contrast, for Delaunay triangulation, different orders still produce the same triangulation.

Naive implementations of DMR have quadratic worst-case running times (Ruppert, 1993) although they perform well in practice. Miller proved sub-quadratic worst-case time of a modification of DMR that processes triangles in decreasing circumcircle diameter together with other changes (Miller, 2004). In Shewchuk's Triangle program, bad triangles are placed into buckets according to their minimum angle, each bucket stores triangles in

```

1 Workset ws(G.badTriangles())

2 foreach Triangle t in ws:

3    if !G.contains(t):

4        continue

5        Cavity c(t)

6        c.expand()

7        c.retriangulate()

8        G.update(c)

9        ws.addAll(c.badTriangles())

```

Figure 2.8: Pseudocode for Delaunay mesh refinement

FIFO order, and buckets are processed in increasing angle order (Shewchuk, 1996). Kulkarni et al. showed that a parallel implementation of DMR that distributes the initial bad triangles among threads and uses thread-local stacks for newly created bad triangles performs well in practice (Kulkarni et al., 2008).

### 2.3.3 Inclusion-Based Points-to Analysis

Inclusion-based points-to analysis (PTA), also known as Andersen's algorithm (Andersen, 1994), is a flow and context-insensitive static analysis that determines the points-to relation for program variables. PTA is a fixpoint algorithm that computes the least solution to a system of set constraints. The basic algorithm maintains a workset of program variables whose points-to relations need to be computed. For each variable in the workset, the algorithm examines the system of constraints to see if the current variable satisfies the constraints. If so, the algorithm continues processing the remaining variables. If not, some set of program variables are modified to satisfy the constraints. These modified variables are then added to the workset, and the algorithm continues until the workset is empty. Hardekopf and Lin showed how the basic fixpoint algorithm augmented with sophisticated cycle detection can scale to large problem sizes (Hardekopf and Lin, 2007). From this algorithm, Méndez-Lojo et al., 2010). The results in Section 6.2.5 are based on this implementation.

Since this is a fixpoint algorithm, all orders of processing variables will produce

the same solution. Many heuristics have been proposed for organizing the workset, such as processing variables in least recently fired (LRF) order (Pearce et al., 2003) or dividing the workset into current and next parts (Nielson et al., 1999). Variables are processed from the current part, but newly active variables are enqueued onto the next part. When the current part is empty, the roles of the current and next parts are swapped. Hardekopf and Lin report that the divided workset approach performs better in practice (Hardekopf and Lin, 2007).

### 2.3.4 Breadth-First Search

Given an unweighted graph G=(V,E) and a starting node  $s\in V$ , breadth-first search (BFS) numbering is the problem of labeling each node with the length of the shortest path from s to that node. BFS is a special case of the SSSP problem, where all edge weights are one. Depending on the structure of the graph, there are two important optimizations. For low-diameter graphs, it beneficial to switch between push and pull-based operators, which reduces the total number of memory accesses (Beamer et al., 2012). For high-diameter graphs, it is beneficial to use autonomous scheduling. Coordinated execution with high-diameter graphs produces many rounds with very few activities per round, while autonomous execution can exploit parallelism among rounds.

BFS algorithms apply the relaxation operator until convergence. For a push-based operator, the active node is a labeled node, and the operator assigns labels to unlabeled neighbors of the active node. For a pull-based operator, the active node is an unlabeled node, and the operator assigns it a label if it can find a labeled neighbor. At the beginning of the computation, it is more efficient to use a push-based operator since there are few labeled nodes and each edge relaxation propagates information through the graph; conversely, it is advantageous to switch to a pull-based implementation towards the end of the computation when most nodes are labeled, particularly for low-diameter graphs. It is possible to blend coordinated and autonomous scheduling as well to create a hybrid algorithm. Initially, the algorithm uses coordinated scheduling of the push and pull-based operators.

After a certain number of rounds of push-based traversals, the algorithm switches to prioritized autonomous scheduling with a priority function that favors executing nodes with smaller BFS numbers.

### 2.3.5 Approximate Diameter

The diameter of a graph is the maximum length of the shortest paths between all pairs of nodes. One exact algorithm is to compute all-pairs shortest-paths and return the maximum distance found. The cost of computing this exactly is prohibitive for any large graph, so many applications call for an approximation of the diameter (DIA) of a graph.

One algorithm is based on finding pseudo-peripheral nodes in the graph. The eccentricity  $\mathbf{ecc}(v)$  of a node v is the maximum shortest distance between v and any other node. A node is pseudo-peripheral if for every node u with distance  $\mathbf{ecc}(v)$  from v,  $\mathbf{ecc}(u) = \mathbf{ecc}(v)$ . The algorithm begins by computing a BFS from an arbitrary node. Then, it computes another BFS from the node with maximum distance, discovered by the first BFS. In the case of ties for maximum distance, the algorithm picks a node with the least degree. It continues this process until the maximum distance does not increase.

Another algorithm is to use the coordinated execution of BFS from k starting nodes at the same time. The k parameter is often picked such that the search data for a node fits in a single machine word so that it can be updated using machine atomic instructions. A bit-vector records whether the node has been visited by a BFS from starting node i < k. Edge relaxation performs logical-or on bit-vectors. The diameter is estimated by the maximum distance reached by the k breadth-first searches, which is a lower-bound on the diameter.

Another possibility is to use probabilistic counting (Flajolet and Martin, 1985), which estimates the number of unique vertex pairs with paths with a distance at most k. When the estimate converges, k is an estimation of the diameter of the graph.

### **2.3.6** Betweenness Centrality

Given a graph G=(V,E) and a pair of nodes s,t, the betweenness score of a node v is the fraction of shortest paths between s and t that pass through v. The betweenness centrality (BC) of v is the sum of all its betweenness scores for all possible pairs s,t in G. A popular algorithm by Brandes (Brandes, 2001) computes the betweenness centrality of all nodes by using forward and backward breadth-first graph traversals. There are two major dimensions of parallelization. One dimension is to compute the scores for multiple source nodes at a time (outer loop parallelism). This is completely data-parallel. The other dimension is to parallelize the computation of the scores with respect to a single source node (inner loop parallelism). Inner loop parallelization can be accomplished by using the same techniques as breadth-first search (Prountzos and Pingali, 2013).

### 2.3.7 Connected Components

In an undirected graph, a connected component (CC) is a maximal set of nodes that are reachable from each other. One algorithm to compute the connected components of a graph is to iteratively apply BFS, choosing as a starting node any unvisited node in the graph until there are no more unvisited nodes. This algorithm is O(|V|+|E|) but has a sequential dependency on the results of previous breadth-first searches. A more parallel algorithm is based on a concurrent union-find data structure. It is a topology-driven computation where each edge of the graph is visited once to add it to the union-find data structure. Another algorithm is based on iterative label propagation. Each node of the graph is initially given a unique id. Then, each node updates its label to be the minimum value id among itself and its neighbors. This process continues until no node updates its label, and it will converge slowly if the diameter of the graph is high. The complexity of this algorithm is O(d(|V|+|E|)) where d is the diameter of the graph.

#### 2.3.8 Preflow-Push

Given a directed graph G=(V,E), a capacity function  $c:E\to\mathbb{R}^+$  mapping edges to non-negative values, and source and sink nodes  $s,t\in V$ , the preflow-push algorithm computes the maximal flow from source to sink. Unlike in maxflow algorithms based on augmenting paths, nodes in preflow-push can temporarily have more flow coming into them than going out. Each node n maintains its excess inflow  $\operatorname{excess}(n)$ . Each node n also has a label called height, which is an estimate of the distance from n to t in the residual graph induced by unsaturated edges. Nodes with non-zero excess that are not the source nor sink are contained in a workset. These nodes are called active nodes (Goldberg and Tarjan, 1988). The preflow-push algorithm repeatedly selects a node from the workset. Each node tries to eliminate its excess by pushing flow to a neighbor (see Figure 2.9). Pushing flow may cause a neighbor to become active. A node can only push flow to a neighbor at a lower height. If a node is active but no neighbors are eligible to receive flow, the node relabels itself, increasing its height to one more than its lowest height neighbor.

Cherkassy and Goldberg show the importance of two heuristics named global relabeling and gap relabeling (Cherkassy and Goldberg, 1995). Global relabeling is a technique that periodically reassigns heights by performing a breadth-first traversal from the sink. The frequency of global relabeling is determined empirically. Gap relabeling is a technique that preemptively removes from the workset any nodes that cannot push flow to the sink. The key insight is that if no node has height h, all nodes with height greater than h cannot push flow to the sink. Cherkassy and Goldberg also consider two orders for processing active nodes: HL order, where nodes are processed in decreasing height order, and FIFO order.

```

1

Workset ws(\{s\})

foreach Node u in ws:

3

L1:

4

while u.excess > 0:

5

for Node v : u.neighbors():

float cap = G.edgeData(u, v)

7

if cap > 0 && u.height == v.height + 1:

8

pushFlow(u, v, min(cap, u.excess))

9

if v != s \&\& v != t :

10

ws.add(v)

if u.excess == 0:

11

12

break L1

13

relabel (u)

14

if *:

15

globalRelabel()

```

Figure 2.9: Pseudocode for preflow-push

### 2.3.9 PageRank

PageRank is an algorithm for computing the importance of nodes in an unweighted graph. At its core is the following update rule

$$\mathbf{w}^{(i+1)}(v) = \alpha + (1 - \alpha) \sum_{u \in I(v)} \frac{\mathbf{w}^{(i)}(u)}{|N(u)|}$$

where  $\mathbf{w}^{(i)}(v)$  is the current PageRank value for v at iteration i, I(v) and N(v) are the incoming and outgoing neighbors of v respectively, and  $0 \le \alpha < 1$  is some fixed damping parameter. The update rule is applied until the PageRank values converge.

Algorithms differ in how this update rule is scheduled. Topology-driven algorithms update all nodes. In the early implementations of the Google search engine, PageRank was computed using power iteration (Brin and Page, 1998), which is a topology-driven approach. Data-driven algorithms update only nodes whose neighbors' PageRank value has changed significantly. Another data-driven approach is to take samples from the graph (Leskovec and Faloutsos, 2006). Algorithms also vary in the consistency model used; in some cases, very weak consistency models have been used, like unsynchronized updates to shared

Figure 2.10: Bipartite graph of documents and features

PageRank values (Low et al., 2010). Convergence can vary significantly with scheduling and consistency model. A possible priority function is to prefer earlier execution of nodes with the greatest change in value.

The PageRank algorithm can be reduced to a sparse matrix-vector multiply. Instead of working on the input graph, the algorithm works on the transpose of the graph with edge weights added corresponding to the number of outgoing neighbors in the original input graph. That is, given an input graph G and its adjacency matrix representation A, the algorithm processes a matrix T, such that  $T_{ji} = A_{ij} \cdot |N(i)|$ . The topology-driven and coordinated sweep of the PageRank update above to all the nodes in the graph is equivalent to the following matrix product,  $w^{(i+1)} = T \mathbf{w}^{(i)}$ .

### 2.3.10 Support Vector Machines

Given a set of documents, a set of keywords (i.e., the *features*), and a partial function on documents indicating whether a document belongs to a class (i.e., binary classification), the problem is to learn a classifier for all documents. These inputs can be modeled as a bipartite graph with documents on one side and keywords on the other side; if a keyword k appears in a document k, there is an undirected edge k0, whose weight is the frequency of that keyword in that document, as shown in Figure 2.10 (weights are not shown in this figure).