Copyright

by

Youngtaek Kim

2013

# The Dissertation Committee for Youngtaek Kim Certifies that this is the approved version of the following dissertation:

# Characterization and Management of Voltage Noise in Multi-Core, Multi-Threaded Processors

Committee:

| Lizy K. John, Supervisor  |

|---------------------------|

| Earl E. Swartzlander, Jr. |

| Earl E. Swartziander, 31. |

| Adnan Aziz                |

| Michael J. Schulte        |

| Vijay Janapa Reddi        |

# Characterization and Management of Voltage Noise in Multi-Core, Multi-Threaded Processors

## by

Youngtaek Kim, B.S.E.E.; M.S.

## **Dissertation**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

**Doctor of Philosophy**

The University of Texas at Austin

May 2013

# **Dedication**

To my family and friends

### Acknowledgements

First of all, I would like to express my profound gratitude to my academic advisor, Prof. Lizy K. John. She gave me priceless advice and help in completing my doctoral degree. In addition, I am deeply grateful to my dissertation committee members, Prof. Earl E. Swartzlander, Jr., Prof. Adnan Aziz, Dr. Michael J. Schulte, and Dr. Vijay Janapa Reddi, and Dr. Srilatha (Bobbie) Manne for their comments, guidance, and encouragement on my Ph.D. proposal and dissertation.

I am grateful to the current and the former AMDers, Jungseob Lee, Dr. Sanjay Pant, Dr. William Lloyd Bircher, Dr. Madhu S. Sibi Govindan, Tom Snodgrass, Indrani Paul, and Mgr. Andrew Kegel, who helped me to finish my internship at Advanced Micro Devices, Inc. with great results.

I am thankful to Laboratory for Computer Architecture (LCA) people, Jungho, Jee Ho, Faisal, Umar, Arun, Karthik, Jian, Ciji, Dimitris, Jeff, Ankita, and Don, for giving me many helps on campus life and attending and discussing my proposal and dissertation practice talks.

I would like to thank the current and the graduated UT Ph.D. students, Junyoung, Jaehong, Junsoo, Ikhwan, Dr. Hyunjin Kim, Dr. Yongchan Ban, Dr. Wooyoung Jang, Dr. Inwook Kong, for encouraging me and celebrating my achievements.

There are several friends I would like to acknowledge individually. First, I am enormously grateful to Myoungjun, one of my closest friends. His words encouraged me whenever I felt down. Secondly, I would like to thank Boongeo -Jinwoo, Ikjoong, and Hyunook, my good friends for more than twenty years.

Finally, I would like to thank my father, my mother, and my elder sister and her family for their devotion and support of my life and study. I am grateful to my extended family for their considering me. I would also like to thank my father-in-law, my mother-in-law, my grandmother-in-law, my sister-in-law and her family, and my brother-in-law for their hearted words and helps during my Ph.D. study. Last but most importantly, I am heartedly grateful to my wife, Kyoungpil, my lovely daughter, Hyemin, and my proud son, Minho, for they have cheered me on all through my work on my Ph.D. degree.

**Characterization and Management of Voltage Noise in**

**Multi-Core, Multi-Threaded Processors**

Youngtaek Kim, Ph.D.

The University of Texas at Austin, 2013

Supervisor: Lizy K. John

Reliability is one of the important issues of recent microprocessor design.

Processors must provide correct behavior as users expect, and must not fail at any time.

However, unreliable operation can be caused by excessive supply voltage fluctuations

due to an inductive part in a microprocessor power distribution network. This voltage

fluctuation issue is referred to as inductive or di/dt noise, and requires thorough analysis

and sophisticated design solutions. This dissertation proposes an automated stressmark

generation framework to characterize di/dt noise effect, and suggests a practical solution

for management of di/dt effects while achieving performance and energy goals.

First, the di/dt noise issue is analyzed from theory to a practical view. Inductance

is a parasitic part in power distribution network for microprocessor, and its characteristics

such as resonant frequencies are reviewed. Then, it is shown that supply voltage

fluctuation from resonant behavior is much harmful than single event voltage

Voltage fluctuations caused by standard benchmarks such as SPEC fluctuations.

CPU2006, PARSEC, Linpack, etc. are studied.

Next, an AUtomated DI/dT stressmark generation framework, referred to as

AUDIT, is proposed to identify maximum voltage droop in a microprocessor power

distribution network. The di/dt stressmark generated from AUDIT framework is an

vii

instruction sequence, which draws periodic high and low current pulses that maximize voltage fluctuations including voltage droops. AUDIT uses a Genetic Algorithm in scheduling and optimizing candidate instruction sequences to create a maximum voltage droop. In addition, AUDIT provides with both simulation and hardware measurement methods for finding maximum voltage droops in different design and verification stages of a processor. Failure points in hardware due to voltage droops are analyzed.

Finally, a hardware technique, floating-point (FP) issue throttling, is examined, which provides a reduction in worst case voltage droop. This dissertation shows the impact of floating point throttling on voltage droop, and translates this reduction in voltage droop to an increase in operating frequency because additional guardband is no longer required to guard against droops resulting from heavy floating point usage. This dissertation presents two techniques to dynamically determine when to tradeoff FP throughput for reduced voltage margin and increased frequency. These techniques can work in software level without any modification of existing hardware.

# **Table of Contents**

| Table of C  | ontents                                                      | ix   |

|-------------|--------------------------------------------------------------|------|

| List of Tab | oles                                                         | xiii |

| List of Fig | ures                                                         | XV   |

| Chapter 1:  | Introduction                                                 | 1    |

| 1.1.        | Motivation                                                   | 5    |

|             | 1.1.1. Automatic Stressmark Generation                       | 5    |

|             | 1.1.2. Dynamic Management of Voltage Margins                 | 6    |

| 1.2.        | Objectives                                                   | 7    |

| 1.3.        | Thesis Statement                                             | 7    |

| 1.4.        | Contributions                                                | 8    |

| 1.5.        | Organization                                                 | 9    |

| Chapter 2:  | Background and Related Work                                  | 11   |

| 2.1.        | Power Distribution Network and Resonant Frequency            | 11   |

| 2.2.        | Current draw, Voltage Fluctuation, and Voltage Margin        | 15   |

| 2.3.        | Manual di/dt Stressmark                                      | 17   |

| 2.4.        | Charactersistics of Current Waveform and Voltage Fluctuation | 19   |

| 2.5.        | Related Work                                                 | 20   |

|             | 2.5.1. Characterizing Inductive Noise                        | 20   |

|             | 2.5.2. Impact of Compiler Optimization                       | 22   |

|             | 2.5.3. Managing Inductive Noise                              | 23   |

| Chapter 3:  | Methodology                                                  | 27   |

| 3.1.        | Method for Characterizing Voltage Droop                      | 27   |

|             | 3.1.1. Simulation Method                                     | 27   |

|             | 3.1.2. Hardware Measurement Method                           | 29   |

|             | 3.1.2.1. System hardware                                     | 30   |

|             | 3.1.2.2. Measurement equipment                               | 31   |

| 3.2         | Benchmarks                                                   | 34   |

| 3.3.      | Metri  | cs        |                                                           | 37    |

|-----------|--------|-----------|-----------------------------------------------------------|-------|

| Chapter 4 | : Anal | ysis of V | Voltage Noise in Microprocessor                           | 39    |

| 4.1.      | Volta  | ge Droop  | Analysis for Standard Benchmarks                          | 39    |

|           | 4.1.1. | Voltage   | Droop Analysis using Simulation                           | 39    |

|           | 4.1.2. | Voltage   | Droop Analysis using Hardware Measurement                 | 42    |

| 4.2.      | Synch  | nronizati | on (Alignment) effect of Multiple Threads                 | 46    |

| 4.3.      | Impac  | et of Con | npiler Optimization on Voltage Droop                      | 49    |

|           | 4.3.1. | Compi     | ler Impact on Performance, Power, and Reliability         | 50    |

|           | 4.3.2. | Experi    | mental Results                                            | 51    |

|           | 4      | 1.3.2.1.  | Experimental Setup                                        | 52    |

|           | 4      | 1.3.2.2.  | Result of miniFE                                          | 52    |

|           | 4      | 1.3.2.3.  | Result of High-Performance Linpack                        | 55    |

|           | 4      | 1.3.2.4.  | Result of SPEC CPU2006                                    | 57    |

|           | 4.3.3. | Summ      | ary of Compiler Optimization Impact                       | 62    |

| 4.4.      | Sumn   | nary      |                                                           | 63    |

| Chapter 5 | : AUD  | OIT Fran  | nework to Generate di/dt Stressmarks                      | 64    |

| 5.1.      | AUD    | IT Frame  | ework                                                     | 65    |

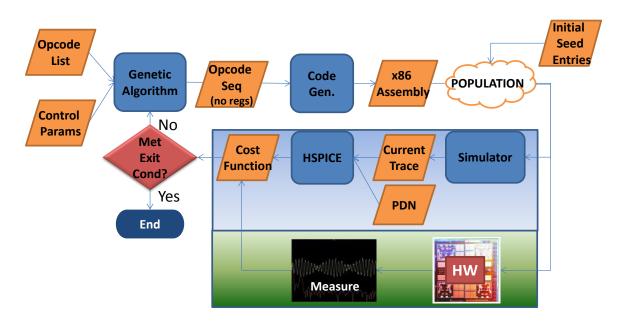

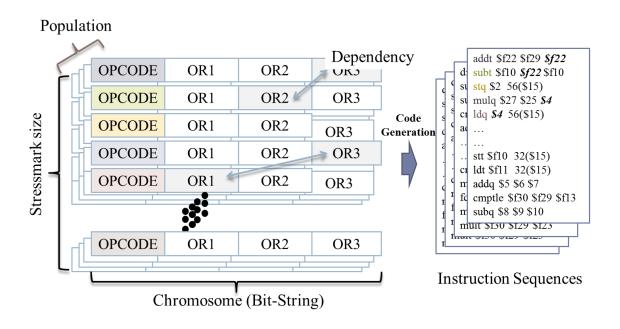

|           | 5.1.1. | Instruc   | tion Scheduling using the Genetic Algorithm               | 67    |

|           | 5.1.2. | Frame     | work Control using the Genetic Algorithm                  | 68    |

|           | 5.1.3. | Instruc   | tion Sequence Generation for the Genetic Algorithm        | ı .70 |

|           | 5.1.4. | Depen     | dency Control and Register Assignment                     | 70    |

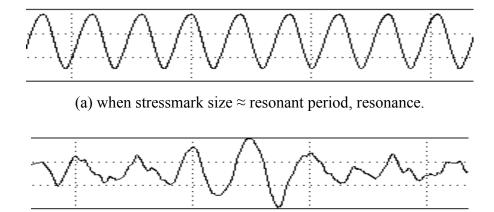

|           | 5.1.5. | Stressr   | nark Size and Resonant Frequency                          | 71    |

|           | 5.1.6. | Manag     | gement of Search Space                                    | 72    |

|           | 5      | 5.1.6.1.  | Reduction of the number of instruction types              | 72    |

|           | 5      | 5.1.6.2.  | Reduction of code length scheduled using sub-<br>blocking | 73    |

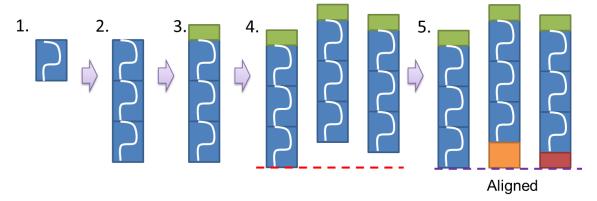

|           | 5.1.7. | Adopti    | on of Dithering Algorithm for Guaranteed Alignmen         | nt 74 |

|           | 5.1.8. | Code (    | Generation for Multiple Threads                           | 77    |

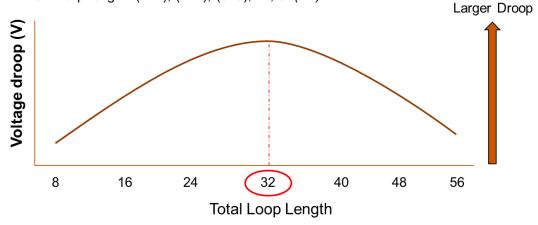

|           | 5.1.9. | Sweep     | for Finding a Resonant Frequency                          | 77    |

| 5.2.      | Exper  | rimental  | Results using AUDIT Framework                             | 79    |

|           | 5.2.1. | Result    | ts of AUDIT Simulation Path           | 79  |  |

|-----------|--------|-----------|---------------------------------------|-----|--|

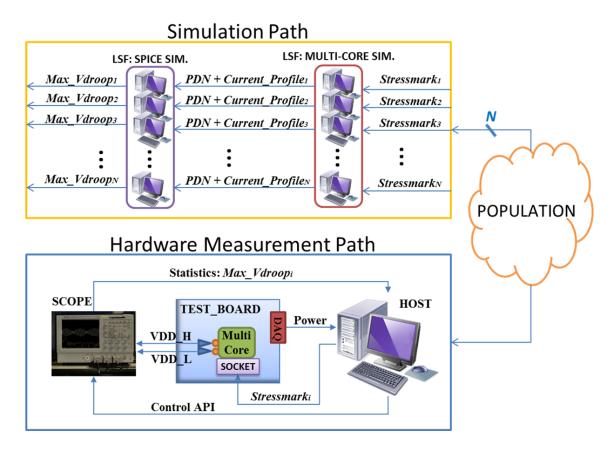

|           | 5.2.2. | Resul     | ts of AUDIT Hardware Measurement Path | 86  |  |

|           | 5      | 5.2.2.1.  | Experimental setup                    | 86  |  |

|           | 5      | 5.2.2.2.  | Voltage droop analysis                | 87  |  |

|           | 5      | 5.2.2.3.  | Voltage droop probability             | 90  |  |

|           | 5      | 5.2.2.4.  | Voltage droop vs. voltage at failure  | 91  |  |

|           | 5      | 5.2.2.5.  | AUDIT loop analysis                   | 93  |  |

|           | 5      | 5.2.2.6.  | Impact of FP throttling               | 95  |  |

|           | 5      | 5.2.2.7.  | AUDIT on a different processor        | 97  |  |

| 5.3.      | Sumn   | nary      |                                       | 97  |  |

| Chapter 6 | : Dyna | amic Ma   | anagement of Supply Voltage Margin    | 99  |  |

| 6.1.      | Mana   | gement    | of Voltage Guardband                  | 100 |  |

| 6.2.      | Work   | load Inc  | luced Voltage Margins                 | 102 |  |

|           | 6.2.1. | Di/dt     | Stressmarks                           | 102 |  |

|           | 6.2.2. | Floati    | ng-Point Activity                     | 103 |  |

|           | 6.2.3. | Floati    | ng-Point (FP) Unit Throttling         | 105 |  |

| 6.3.      | Deter  | mining    | Voltage Margins                       | 107 |  |

| 6.4.      | Dynai  | mic FP    | ic FP Throttling                      |     |  |

| 6.5.      | Exper  | rimental  | Results                               | 111 |  |

|           | 6.5.1. | Exper     | imental Setup                         | 111 |  |

|           | 6.5.2. | Perfor    | mance with FP Throttling              | 112 |  |

|           | 6.5.3. | Energ     | y Efficiency                          | 115 |  |

|           | 6.5.4. | Dynar     | nic Scheme                            | 117 |  |

|           | 6.5.5. | Multi-    | -core Execution                       | 119 |  |

|           | 6.5.6. | Impro     | ved Dynamic Scheme                    | 121 |  |

| 6.6.      | Sumn   | nary      |                                       | 124 |  |

| Chapter 7 | : Cond | clusion a | and Future Research                   | 126 |  |

| 7.1.      | Sumn   | nary and  | l Conclusion                          | 126 |  |

| 7.2.      | Future | e Resear  | rch                                   | 128 |  |

|           | 7.2.1. | Exten     | sion to AUDIT                         | 128 |  |

| 7.2.2.       | Improvement of Dynamic Scheme for Managing Voltage Margins |

|--------------|------------------------------------------------------------|

| 7.2.3.       | Charaterization and Management of Voltage Noise in GPU129  |

| Bibliography |                                                            |

## **List of Tables**

| Table 3.1: | Comparison of sampling and triggering methods for hardware         |     |

|------------|--------------------------------------------------------------------|-----|

|            | measurement.                                                       | .32 |

| Table 3.2: | Standard benchmarks and stressmarks used in this dissertation      | .36 |

| Table 4.1: | An architecture configuration for SimpleScalar.                    | .40 |

| Table 4.2: | Comparison of experimental methodology between Valluri and         |     |

|            | John [67] and this dissertation.                                   | .51 |

| Table 4.3: | Runtime, power, maximum voltage droop, and energy of miniFE        |     |

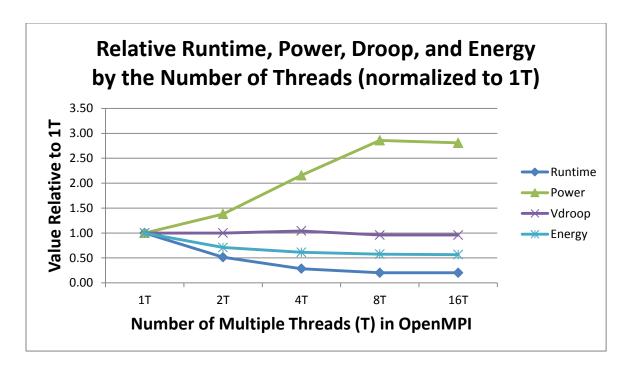

|            | with increase of the number of threads.                            | .53 |

| Table 4.4: | Runtime, power, maximum voltage droop, and energy of High-         |     |

|            | Performance Linpack (8T) with different libraries and optimization | n   |

|            | levels. The values are normalized to the Original BLAS and         |     |

|            | O0 case                                                            | .56 |

| Table 4.5: | SPEC CPU2006 1T Results with -O3 (normalized to -O0)               | .58 |

| Table 4.6: | SPEC CPU2006 4T Results with -O3 (normalized to -O0)               | .60 |

| Table 5.1: | Base architecture configuration for SimpleScalar                   | .81 |

| Table 5.2: | Five different PDNs for circuit simulation                         | .81 |

| Table 5.3: | Maximum voltage droops of SPEC CPU2006, hand-coded [24], an        | d   |

|            | automatic di/dt stressmarks. Supply voltage is 1V (Vnom=1V)        | .83 |

| Table 5.4: | Voltage at failure relative to A-Res 4T failure point              | .93 |

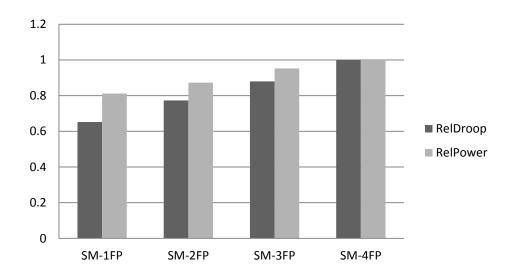

| Table 5.5: | Impact of FP throttling on relative droop (relative to 4T SM1) and |     |

|            | failure point (relative to 4T <i>A-Res</i> ).                      | .96 |

| Table 5.6: | Droop and failure results for a 45-nm AMD Phenom II processor.     |     |

|            | Droop and failure point are shown relative to SM2                  | .97 |

| Table 6.1: | Frequency boost possible with FP Throttling                | 109   |

|------------|------------------------------------------------------------|-------|

| Table 6.2: | Algorithm for dynamic voltage guardband manegement using   |       |

|            | FP-IPC                                                     | 111   |

| Table 6.3: | Improved algorithm for dynamic voltage guardband managemen | t.122 |

# **List of Figures**

| Figure 1.1: | Voltage margins to manage fluctuations                               |

|-------------|----------------------------------------------------------------------|

| Figure 2.1: | Power distribution network (PDN)12                                   |

| Figure 2.2: | 1st, 2nd, and 3rd resonance droops in the frequency domain13         |

| Figure 2.3: | 1st, 2nd, and 3rd resonance droops in the time domain                |

| Figure 2.4: | Sudden current changes in a multi-core processor cause supply        |

|             | voltage fluctuation. When [aligned + resonant], voltage margin       |

|             | violations occur                                                     |

| Figure 2.5: | Current draws (top) and corresponding voltage fluctuations (bottom): |

|             | 1st droop only excitation (left) and 1st droop resonance (right)18   |

| Figure 2.6: | Scope shots of voltage fluctuation in production processor:          |

|             | 1st droop only excitation (left) and 1st droop resonance (right)18   |

| Figure 2.7: | Different current pulse shapes (top) and corresponding voltage       |

|             | fluctuations (bottom). The current intensity is the same in HSPICE   |

|             | simulation                                                           |

| Figure 3.1: | Current-voltage simulation                                           |

| Figure 3.2: | AMD Bulldozer module. Adopted from Butler et al. [8]31               |

| Figure 3.3: | Hardware measurement set-up                                          |

| Figure 3.4: | Oscilloscope and differential probe used in this dissertation34      |

| Figure 3.5: | Thread configuration for multi-core system (T=thread)                |

| Figure 4.1: | Maximum voltage droop of SPEC CPU2006 in simulation. Vdd is          |

|             | 1.0V41                                                               |

| Figure 4.2: | Occurrence (inclusive) at each voltage droop at Vdd=1.0V42           |

| Figure 4.3:  | .3: Hardware measurements of droop (relative to 4T <i>SM1</i> ) for SPE0   |  |  |

|--------------|----------------------------------------------------------------------------|--|--|

|              | CPU2006                                                                    |  |  |

| Figure 4.4:  | Alignment: misaligned-destructive (top) and aligned-constructive           |  |  |

|              | (bottom)47                                                                 |  |  |

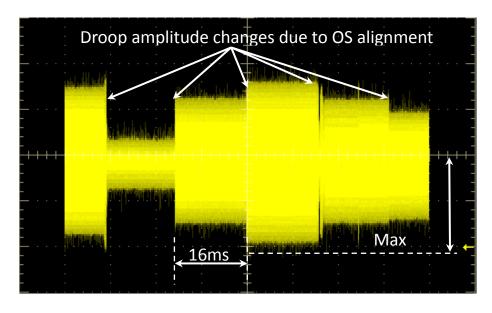

| Figure 4.5:  | Scope shot of <i>natural dithering</i> due to OS interactions for resonant |  |  |

|              | stressmark over a period of 100 ms                                         |  |  |

| Figure 4.6:  | Runtime, power, droop, and energy of miniFE (relative to 1T case)5         |  |  |

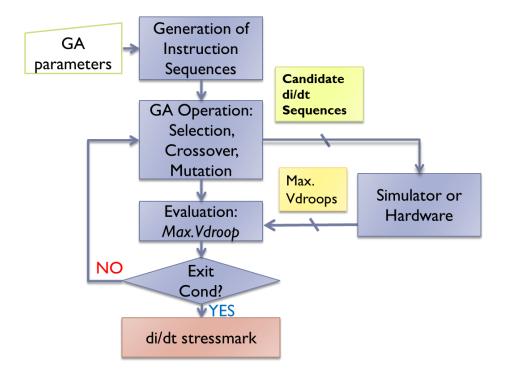

| Figure 5.1:  | AUDIT framework for di/dt stressmark generation using simulators           |  |  |

|              | and hardware.                                                              |  |  |

| Figure 5.2:  | Simulation and hardware measurement paths to get max voltage               |  |  |

|              | droops6                                                                    |  |  |

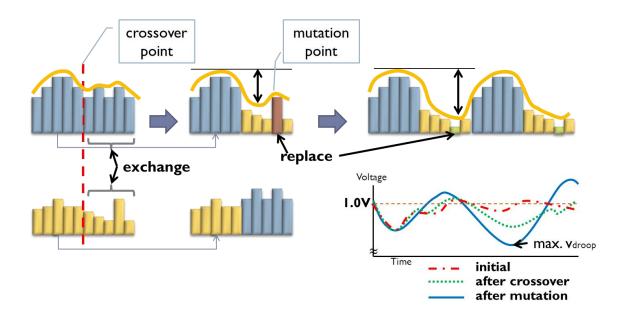

| Figure 5.3:  | Conceptual instruction scheduling in the Genetic Algorithm68               |  |  |

| Figure 5.4:  | Control of stressmark generation framework using Genetic                   |  |  |

|              | Algorithm. 69                                                              |  |  |

| Figure 5.5:  | Instruction sequence generation for Genetic Algorithm70                    |  |  |

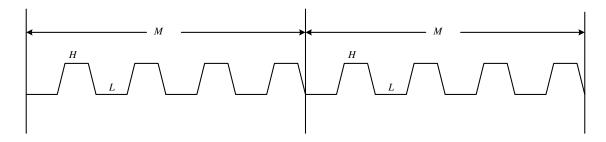

| Figure 5.6:  | Stressmark size and resonant period                                        |  |  |

| Figure 5.7:  | Periodic activity waveform for inducing power supply resonance             |  |  |

|              | and large voltage droops.                                                  |  |  |

| Figure 5.8:  | Code generation steps for multiple threads7                                |  |  |

| Figure 5.9:  | Frequency sweep to find resonance frequency. A loop length of 32           |  |  |

|              | hits the resonant frequency and causes the largest voltage droop79         |  |  |

| Figure 5.10: | Current waveform according to generation number84                          |  |  |

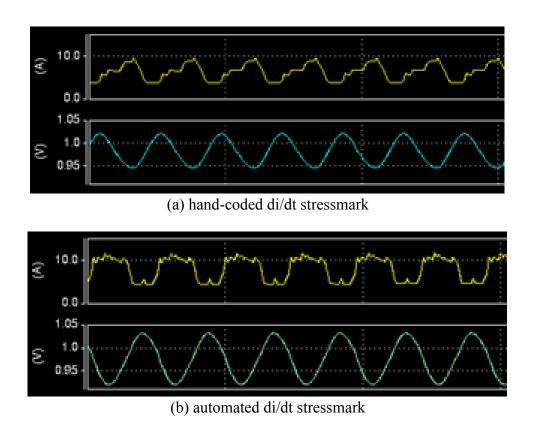

| Figure 5.11: | Current and voltage waveform of hand-coded and automated di/dt             |  |  |

|              | stressmark in Arch2-PDN2 84                                                |  |  |

| Figure 5.12: Hardware measurements of droop (relative to 4T <i>SM1</i> ) for SPEC |                                                                         |     |

|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----|

|                                                                                   | CPU2006, PARSEC, and stressmarks.                                       | 88  |

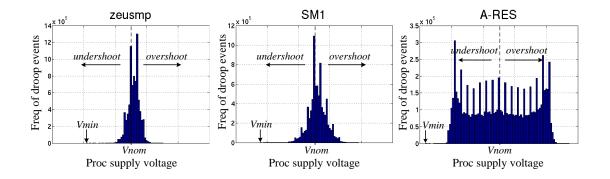

| Figure 5.13:                                                                      | Frequency of droop events.                                              | 91  |

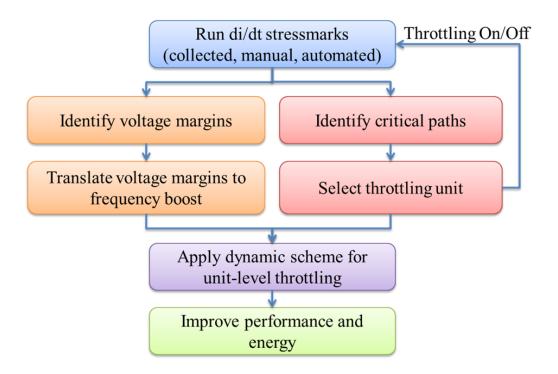

| Figure 6.1:                                                                       | Workflow for dynamic voltage guardband management                       | 102 |

| Figure 6.2:                                                                       | Relative voltage droop and power with varying issue rate of             |     |

|                                                                                   | FP ops                                                                  | 105 |

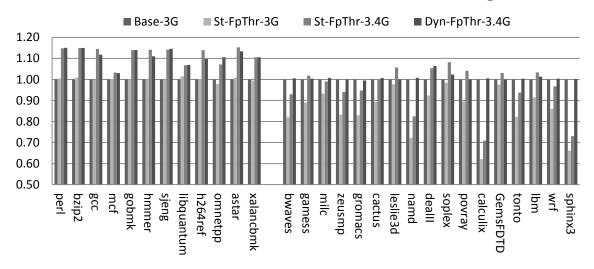

| Figure 6.3:                                                                       | Relative performance impact of FP throttling with and without           |     |

|                                                                                   | frequency boost relative to Base-3G.                                    | 114 |

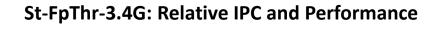

| Figure 6.4:                                                                       | IPC and performance for <i>St-FpThr-3.4G</i> relative to <i>Base-3G</i> | 115 |

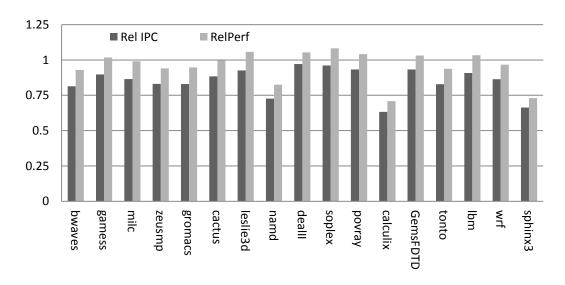

| Figure 6.5:                                                                       | Energy-delay product (E*D) with static and dynamic schemes.             |     |

|                                                                                   | The values are relative to <i>Base-3G</i> .                             | 116 |

| Figure 6.6:                                                                       | Average FP-IPC for benchmarks.                                          | 118 |

| Figure 6.7:                                                                       | Performance with 8T execution relative to <i>Base-3G</i> case           | 120 |

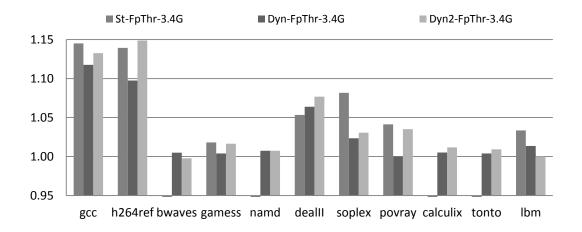

| Figure 6.8:                                                                       | Results with improved dynamic scheme ( <i>Dyn2-FpThr-3.4G</i> )         | 123 |

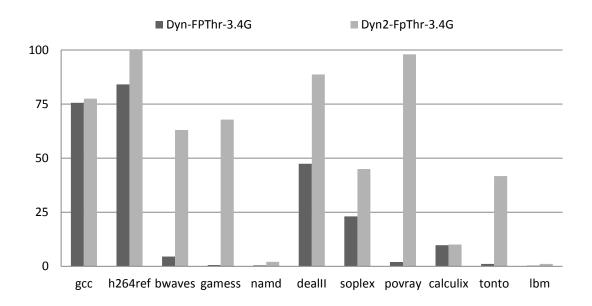

| Figure 6.9:                                                                       | Percent time spent with FP throttling enabled                           | 124 |

## **Chapter 1: Introduction**

For decades, microprocessors have been vastly used in our everyday lives; from electronic devices for personal use to workstations for business purposes and to supercomputers for scientific calculations. To support such various purposes and user experiences, microprocessor design needs to set different performance, power, and reliability goals according to the applications.

High performance is crucial for scientific calculations that need to be processed as fast as possible. Boosting the clock speed of a processor is one of the simplest ways of achieving the high performance goal. However, because of the increasing gap between processor and memory speeds, referred to as *memory wall*, such frequency boost is inefficient for increasing performance. To fill in the performance gap between processor and memory, designers have integrated a larger cache into the processor to compensate for a long latency of off-chip memory accesses.

Low power consumption is important for mobile hand-held devices to sustain a battery life as long as possible. Microprocessors also require low-power operations to reduce heat and resulting needs for expensive cooling method. As technology scales down, power density goes up and the increasing power density will cause more thermal hotspots on a microprocessor. A dynamic voltage and frequency scaling effectively reduces the total power consumption of a processor, and other techniques such as clock gating and power gating are useful to reduce dynamic power consumption.

Reliability is a fundamental requirement of processor design. Processors must work correctly across a range of applications regardless of process variations, voltage variations, environmental noise, and the aging of the system. However, guaranteeing

reliability is one of the most complicated tasks in microprocessor design; it is difficult to analyze and resolve a reliability problem that usually lies across multiple design stages in a complex architecture.

Recently microprocessor design entered this new era where power and reliability are prime design constraints. The traditional design goal, high performance, is hard to achieve by increasing CPU clock frequency only. Improving performance with frequency boost is not simple anymore because the frequency boost is limited by power and reliability constraints. Generally increasing frequency needs more power, and higher frequency makes a processor circuit more susceptible to voltage noise. As power increases, the processor's temperature quickly rises and gives more variations on reliability.

Using parallelism such as multiple cores and multiple threads can achieve high performance goal. However, multiple cores and multiple threads on the same processor not only require additional power consumption but also induce more switching noise, compared to a single core and a single thread. Multiple critical paths would exist and it is difficult to identify and analyze all of them.

Supply voltage noise issue caused by rapid current changes will be more critical to guarantee the reliability in future microprocessors. Cloud computing and big data require high performance and low power processors to serve many users simultaneously. The processor used in server systems will integrate multiple cores, even GPUs, into a single chip as many as possible to improve performance and power efficiency. Because of the power issues frequently referred to as the *power wall* problem, the maximum frequency and power will hardly go beyond 4GHz and 200W, respectively. Power supply voltages have been getting closer to the threshold voltages of underlying transistors, so

the magnitude of supply voltage fluctuations will not shrink much. However, due to the more complex architecture, analyzing critical paths will be more difficult. As technology scales, supply voltage noise will give more impact on cell delay [65]. In other words, process technology advance will increase the sensitivity of cell delay. In addition, the smaller feature size, the more susceptible to process and thermal variations microprocessor circuits are. Therefore, it is important to be aware of supply voltage noise issues because both the complexity of microarchitecture and the variability of microprocessor circuit will increase in future microprocessor design.

This dissertation focuses on reliability issues arising from supply voltage fluctuations. Supply voltage fluctuation, referred to as *inductive* or *di/dt noise*, is caused by sudden change of current draw in microprocessors and the power distribution network. Parasitic inductance on the die, package and the board often disturb the current flow from the voltage regulator on board to processor components on die. Such disturbance causes a temporary lack of electric charge that is needed for powering the processor components. Decoupling capacitance can be a solution for storing and providing electric charge to processor components when voltage emergency arises. However, capacitance can also induce voltage fluctuation because of the characteristics of RLC circuits.

The rate of current change is determined by program behavior. When an instruction sequence flows through a microprocessor architecture, internal microprocessor components will be turned on and then be turned off, and it changes current draw. It is difficult to predict the amount of current draw cycle by cycle because many instructions are on the fly across different pipeline stages and different paths. There are many sensitive paths on cores that can lead to catastrophic failures when the system is stressed by reduced noise margins, and it is imperative that one have the tools necessary

to identify these paths [45].

Increasing CPU clock frequency for high performance has been limited because of power constraints. One of the most effective ways to decrease power is to scale down the supply voltage. However, circuits become more susceptible to supply voltage noise due to near threshold voltage operations, and even a small amount of supply voltage fluctuation may cause reliability problems at the lower power supply voltages. Now designers need to analyze the supply voltage noise and devise solutions for guaranteeing reliable processor behavior with very low supply voltages. Low power goals and techniques need to be managed in tandem with the reliability goals of the processor.

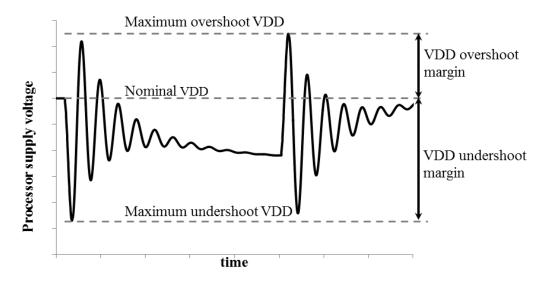

Voltage margins (a.k.a. voltage guardband) are introduced to compensate for potential supply voltage fluctuations in the system. Fluctuations caused during program execution must stay within allowed margins, as shown in Figure 1.1. These margins need to be designed carefully to be power-efficient and prevent malfunctions from program-induced voltage fluctuations. The voltage margins guard against process variations, system power supply variation, and workload induced voltage droops. These margins are set conservatively, and are on the order of 15% to 20% of supply voltage [23]. However, as shown later in this dissertation, standard applications running under normal conditions do not exhibit voltage variations anywhere close to the worst case margins. By guarding against the worst case scenarios, a lot of performance is lost. For instance, according to Reddi et al. [55], a 20% voltage margin translates into a 33% frequency loss.

Figure 1.1: Voltage margins to manage fluctuations.

#### 1.1. MOTIVATION

This section describes the motivation and background of this research.

#### 1.1.1. Automatic Stressmark Generation

Specialized benchmarks, referred to as stressmarks, are used to study the susceptibility of processors to voltage fluctuations. Stressmarks may or may not be used to set the voltage margins; however, they are necessary to develop an understanding of the susceptibility of the system being analyzed. Stressmarks can be collected from existing benchmarks that have produced high di/dt stresses in the past. However, most existing benchmarks such as SPEC CPU2006 focus on high performance only, so they may not generate periodic, high and low current draw under normal condition [24]. Moreover, standard benchmarks require a long simulation time in an early design stage.

On the other hand, stressmarks can be specially designed to induce voltage

fluctuations in microprocessors. In many cases, designers manually generate a di/dt stressmark to test their processor/system. However, the manual generation of a di/dt stressmark is tedious and time-consuming. Designers need to recreate stressmarks whenever an architectural change occurs. In addition, the search space is extremely large, so it is not feasible for designers to manually generate and test every possible combination of parameters, configurations, and instruction scheduling to fully utilize a processor/system.

In this dissertation, an automatic di/dt stressmark generation framework is proposed to produce significant voltage droops. A Genetic Algorithm (GA) is utilized, and several techniques are developed to generate and optimize candidate di/dt stressmarks.

### 1.1.2. Dynamic Management of Voltage Margins

Stressmarks are benchmarks designed to stress a processor in various ways, such as generating the worst case power or the worst case voltage droops. Stressmarks designed to induce large di/dt voltage droops are used to determine the voltage guardband due to workload induced di/dt noise. Di/dt stressmarks consist of a region of high power instructions followed by a region of low power instructions [19][24][26][27]. Analysis presented in Chapter 5 of this dissertation has shown that on x86 processors the high power region typically contains a high number of floating point (FP) or Streaming SIMD Extensions (SSE) instructions, while the low power region generally contains NOPs. The high power region can consist of other types of instructions, such as instructions from the integer pipeline, but the resulting voltage droop from these

instructions is significantly less than the droop from instructions that execute on the FP path because operations that use FP pipeline dissipate relatively large amounts of power and thus lead to large di/dt fluctuations. Hence, the worst case guardband of the system is determined using operations that utilize the FP pipeline. If the workload does not have high FP pipeline utilization, then the system can be run with a lower voltage guardband, which can be translated into a higher operating frequency.

In this dissertation, two algorithms are presented to dynamically control FP throttling and adjust the operating frequency in order to trade off frequency for FP throughput to improve the performance of both FP-intensive and non-FP-intensive programs.

#### 1.2. OBJECTIVES

The objective of this dissertation is to characterize di/dt noise and to develop a method to manage voltage margins. The specific objectives are as follows:

- Characterize di/dt noise in different microprocessors with various benchmarks

- Develop a method for generating effective di/dt stressmarks automatically in both simulation and real hardware environments

- Examine software optimization impact on di/dt noise

- Develop a technique for managing trade-offs between performance and di/dt noise for multi-core processors

#### 1.3. THESIS STATEMENT

Automated stressmark generation framework to generate stressmarks to

characterize supply voltage noise in multi-core, multi-threaded processors can be constructed using genetic algorithms and a voltage fluctuation measurement/simulation framework. A dynamic voltage margin management scheme using functional unit throttling increases system performance while suppressing supply voltage noise.

#### 1.4. CONTRIBUTIONS

This dissertation makes the following contributions:

- The existing di/dt stressmarks and their behavior in single and multi-core systems are discussed and analyzed.

- An automated stressmark generation framework is proposed, which

- generates an effective di/dt stressmark without comprehensive knowledge of a microprocessor system,

- o utilizes a Genetic Algorithm to generate a benchmark that creates a maximum voltage droop in a given microprocessor and PDN,

- reduces designers' time to generate a hand-coded di/dt stressmark and/or to simulate typical benchmarks that are possibly irrelevant to inducing maximum voltage droop,

- utilizes real multi-core hardware to generate di/dt stressmarks quickly and automatically,

- applies a novel method referred to as dithering to align stressmarks in multicore systems,

- o compares the maximum voltage droop and catastrophic behavior of standard benchmarks, manually generated stressmarks, and automated stressmarks, and

- o analyzes di/dt noise of a state-of-the-art x86 multi-core processor with multithreading and architectural throttling effects.

- An FP throttling mechanism on a state-of-the-art x86 processor is analyzed, resulting in

- a study of frequency boost, performance, and energy-delay product benefits

made possible by FP throttling,

- o a study of the impact of FP throttling with multi-core execution, and

- o new algorithms to dynamically manage FP throttling and their analysis.

#### 1.5. ORGANIZATION

Chapter 2 reviews the background of di/dt noise analysis and related work on the di/dt issue. Current draw, voltage fluctuations, and voltage margins are described, and power distribution networks and resonant frequencies are discussed as they affect nature of di/dt noise. Related work is categorized into three folds; characterization of di/dt noise, compiler impact on di/dt noise, and management of di/dt noise.

Chapter 3 presents the methodology of this dissertation. Simulation and hardware measurement environments are introduced. Benchmarks used in this work are categorized in several ways. Metrics are defined to characterize performance, power, and voltage noise.

Chapter 4 investigates voltage noise problems in microprocessors in more detail; the relationship of current waveform and voltage fluctuation and synchronization effect in multi-core, multi-threaded processors. Voltage noise under different compiler optimization levels is analyzed. Two different optimization levels are applied to various

benchmarks, and the variations in performance, power, voltage droop, and energy are compared.

Chapter 5 describes the AUDIT framework that generates a di/dt stressmark to characterize voltage noise. The application of a Genetic Algorithm (GA) is also explained in detail. Simulation and hardware measurement paths for pre- and post-silicon processor models are introduced.

Chapter 6 suggests a method to dynamically manage voltage margins. The effect of the existing throttling of floating-point units is measured and the amount of the voltage margin reduction is analyzed. An algorithm is introduced to find an optimal tradeoff between performance and voltage margin reduction. Chapter 7 concludes the dissertation and suggests possible future research directions.

## Chapter 2: Background and Related Work

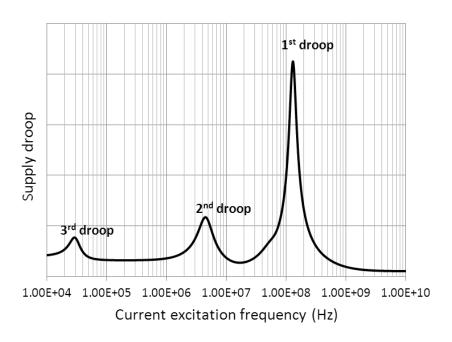

In a microprocessor, the supply voltage is provided through a power distribution network (PDN), which can be represented as a distributed RLC circuit with resonance frequencies. Varying current (di/dt) can cause fluctuations of the supply voltage that are proportional to the inductance (L) of the circuit ( $v = L \cdot di/dt$ ). Voltage droop is maximized if the periodic, large current variation occurs at the resonance frequency of the PDN. A resonance frequency in the mid-frequency (50 to 200MHz) range is the most significant [44]. Significant supply voltage droop may cause reliability problems in a microprocessor. Reddi [50] discusses the voltage fluctuation problem, and presents experiments illustrating the gravity of the situation. Low voltage increases the delay of signals, which could affect the timing between two flip-flops in a microprocessor circuit. Also, insufficient voltage could fail to set bit-signals properly and lead to soft errors. In this chapter, background on inductive (di/dt) noise is presented.

#### 2.1. POWER DISTRIBUTION NETWORK AND RESONANT FREQUENCY

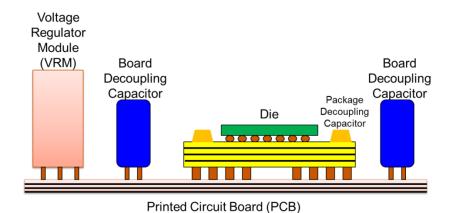

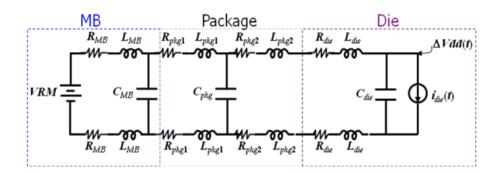

The power distribution network (PDN) of a typical microprocessor consists of inductive and resistance elements on the motherboard (*MB*) or Printed Circuit Board (*PCB*), package, and die (see Figure 2.1). The parasitic resistance of the network causes a droop (IR drop) in the power supply proportional to the current drawn from the network. In addition, the inductance in the network causes undershoots and overshoots in the power supply (referred to as the di/dt drop), which depend on the rate of change of the load-current. To mitigate the inductive noise in the power supply, decoupling capacitance, commonly referred to as decap, is added at different locations in the power

supply network as illustrated in Figure 2.1. The amount of added decap progressively increases away from the die to counter the effect of increasing inductance parasitics. The series combination of parasitic inductance (L) and decap (C) results in various resonance frequencies ( $1/2\pi\sqrt{LC}$ ) in the network, as shown in Figure 2.2 and 2.3 in the frequency and time domains.

(a) Physical structure of power distribution network. Adopted from Popovich [22].

(b) Simplified RLC circuit model of power distribution network.

Figure 2.1: Power distribution network (PDN)

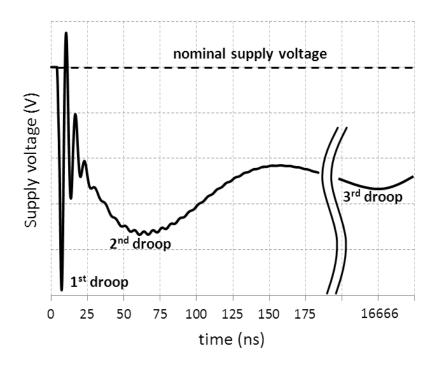

The prominent resonance frequencies shown in Figure 2.2 and 2.3 are the 1st droop resonance due to the interaction of package and on-die inductance ( $L_{pkg2} + L_{die}$ ) with on-die decap ( $C_{die}$ ), the 2nd droop resonance due to the interaction of socket and package inductance ( $L_{pkg1}$ ) with package decap ( $C_{pkg}$ ), and the 3rd droop resonance due to the interaction of board inductance ( $L_{MB}$ ) with decap on the board ( $C_{MB}$ ). A periodically varying load can induce one or more of these resonances and cause excessive undershoots and overshoots. Although 2nd and 3rd droop resonance can also impact the reliability of the system, they can be mitigated by techniques such as load line based voltage regulator modules [56] and are beyond the scope of this work. Although AUDIT in Chapter 5 is discussed in the context of first droops, it can be tuned to excite any of the three types of droops.

Figure 2.2: 1st, 2nd, and 3rd resonance droops in the frequency domain.

Figure 2.3: 1st, 2nd, and 3rd resonance droops in the time domain.

The 1st droop resonance is a strong function of package inductance ( $L_{pkg2}$ ) and ondie decap ( $C_{die}$ ), and is typically in the range of 50MHz – 200MHz. Examples of events causing large first droop are power wakeup of one or more blocks present in the design or a sudden up or down surge in the processor activity. When such rapid events occur periodically at the 1st droop resonance frequency, they may cause 1st droop resonance resulting in large, sustained undershoots and overshoots in the power supply. 1st droop can be mitigated by explicitly adding decoupling capacitance on the die [44]. However, there are limits to the feasibility of this approach due to area constraints and the leakage of the decap. Several architectural techniques that limit the rate of change of activity in the processor are effective in suppressing the first droop [17][19][24][47], but they may have a negative impact on performance.

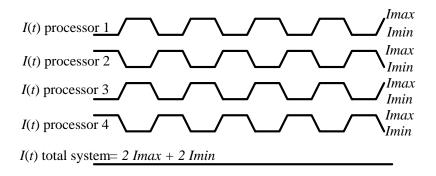

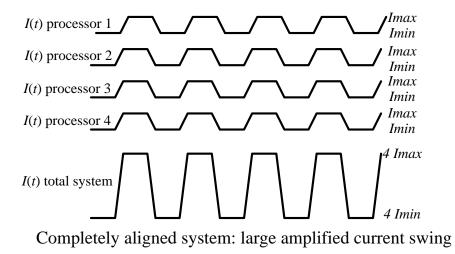

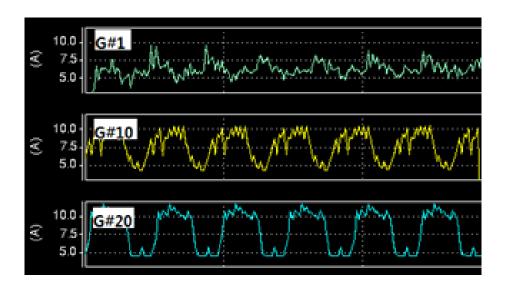

#### 2.2. CURRENT DRAW, VOLTAGE FLUCTUATION, AND VOLTAGE MARGIN

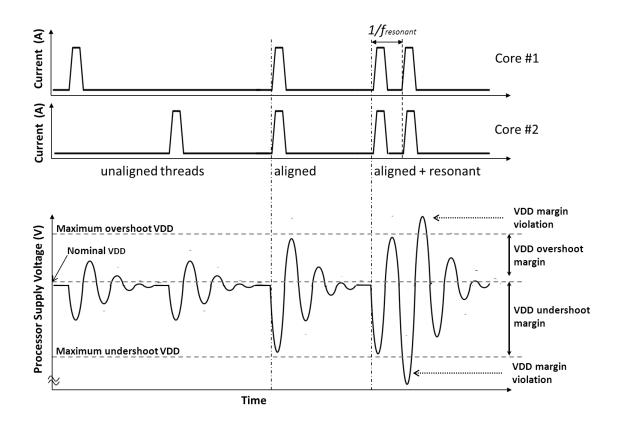

Figure 2.4 shows possible current changes and the corresponding voltage fluctuations in a multi-core processor. Each core runs a program and its current changes by time are in the top of Figure 2.4. When rapid current change occurs, processor supply voltage fluctuates and then it is quickly damped (bottom of Figure 2.4). Interestingly the magnitude of fluctuation is affected by two factors: the sum of two cores' current (current intensity) and periodic behavior of current draw. When the changes from low to high current loads are aligned between two cores that share the same supply voltage, the total current is doubled and it causes larger voltage fluctuation. When the current changes are periodic and meet the resonant frequency of the PDN, the following voltage fluctuations are additive to the previous ones and then the magnitude of fluctuation increases.

Figure 2.4: Sudden current changes in a multi-core processor cause supply voltage fluctuation. When [aligned + resonant], voltage margin violations occur.

Figure 2.4 also shows voltage margins from nominal voltage (VDD). When the voltage fluctuations go down under the nominal voltage, it is called an undershoot (droop). When voltage fluctuations go over the nominal voltage, it is called an overshoot. Voltage margins are set to guarantee correct behavior even with the worst case fluctuation. If the voltage fluctuation goes beyond the voltage margin, it causes a voltage margin violation and operations become unreliable. Overshoot is more harmful than undershoot because overshoot may cause permanent damage to the internal circuits of a microprocessor.

#### 2.3. MANUAL DI/DT STRESSMARK

To analyze the impact of supply voltage droop on performance and reliability, it is imperative to create instruction patterns (stressmarks) that stress the PDN of the processor to cause large undershoots and overshoots. Traditionally, stressmarks have been generated manually with the knowledge of power consumption of different patterns of instructions and details of the PDN. This subsection describes a methodology for manually generating stressmarks.

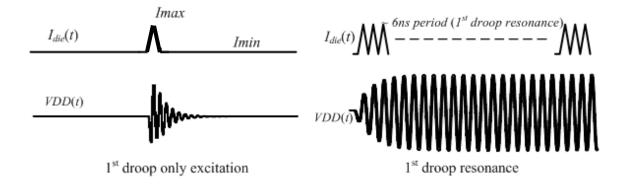

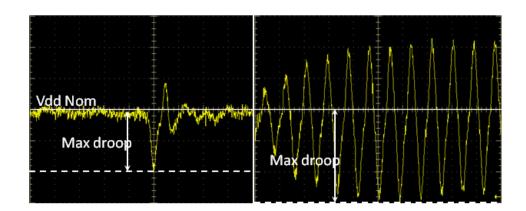

The first step for manually designing stressmarks requires analysis of the power consumptions of different instruction patterns. To induce large di/dt droops, the processor cores should switch simultaneously from a low-power state to a high-power state as quickly as possible. For the low-power state, instructions such as a NOP that consume a low amount of power can be chosen. For the high-power state, floating point or SIMD instructions that consume lots of power and that can attain the highest IPC supported by the target machine are selected. If a single high-di/dt event occurs where the machine executes a pattern of low-power instructions followed by a pattern of high-power instructions, there will be a droop in supply voltage, but the droop will taper off quickly as shown on the left side of Figure 2.5. However, a pattern that repeats periodically at the resonant frequency of the PDN will build in amplitude and not only generate a larger droop than a single event but one that repeats regularly, thereby increasing the probability of system failure (right side of Figure 2.5). Both these conditions help to build an effective first droop stressmark. This dissertation covers 1st droop only excitation and 1st droop resonance in the analysis. Figure 2.6 is the screen shot of an oscilloscope that shows a production processor's voltage levels.

Figure 2.5: Current draws (top) and corresponding voltage fluctuations (bottom): 1st droop only excitation (left) and 1st droop resonance (right).

Figure 2.6: Scope shots of voltage fluctuation in production processor: 1st droop only excitation (left) and 1st droop resonance (right).

Several challenges exist in manually designing the stressmarks. First, resonant frequencies can change between different boards in the same product line and between different products (such as client versus server). Therefore, multiple stressmarks need to be developed to target different resonance frequencies and different system configurations. Second, because the periodicity of the low-power and high-power

instructions depends on the operating frequency, multiple stressmarks need to be written for the various operating frequencies of the system. Finally, it is very time consuming to explore different combinations of instructions manually for the high-power and low-power portions of the loop. This dissertation addresses all these issues by automating the process of generating di/dt stressmarks.

#### 2.4. CHARACTERSISTICS OF CURRENT WAVEFORM AND VOLTAGE FLUCTUATION

Voltage fluctuations by different shapes of current waveform are described in here. To induce a maximum voltage droop in a given environment, it is important to know the characteristics of di/dt voltage noise affected by current variations. Previous work [16][24] provide good analysis that this dissertation extends to add several factors to be considered when generating a di/dt stressmark.

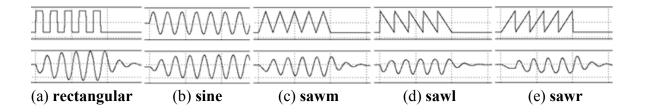

Shape of current waveform: Maximum voltage droop is affected by the shape of the current waveform. Three types of current waveforms are generated and simulated: saw-tooth, sine, and rectangular. The corresponding voltage fluctuations show that rectangular-shaped current waveform is most effective to induce high voltage droop (Figure 2.7). It is difficult to make sudden current changes, but it is shown that the events like pipeline flush are able to generate huge interrupts of current draw in a program [52].

**Ratio of high-to-low period**: The width of the high-current pulse in the resonant period is adjusted and tested. Both wider and narrower widths than a half of resonant period alleviate the voltage droop. According to this observation, high and low current draw periods should be evenly distributed to induce a large voltage droop.

**Difference of current intensity**: Current intensity is very important to make a large voltage droop. However, even though a high current draw occurs, if the previous or the next current draw is also high enough, voltage hardly fluctuates.

The three aforementioned factors are critical to generate a di/dt stressmark for a defined microarchitecture and PDN. This dissertation uses these factors to analyze maximum voltage droop induced in different combinations of microarchitectures and PDNs.

Figure 2.7: Different current pulse shapes (top) and corresponding voltage fluctuations (bottom). The current intensity is the same in HSPICE simulation.

#### 2.5. RELATED WORK

### 2.5.1. Characterizing Inductive Noise

There has been some previous work on hardware analysis of production systems. In [56], Reddi et al. measured and analyzed droops on a two-core Intel system and discussed constructive and destructive interference between processors and the difference

in droops between average and worst-case scenarios. This information was used to design a noise-aware thread scheduler to mitigate some of the di/dt stresses in the system. To date, the work by Reddi is the most detailed analysis of droops on hardware.

This dissertation expands on that work by analyzing a more complex system with multi-threading and up to eight logical processors. In addition, it is shown that constructive interference occurs more often than expected due to OS effects, and this knowledge is used to design effective stressmarks.

More recently, Miller et al. examined voltage emergencies in multi-core processors [34] with increasing numbers of cores, and showed how global synchronization points create large stresses in the system. This work used power variability as a proxy for di/dt stresses and examined the hardware at a coarse granularity of 1-ms intervals. This dissertation uses true voltage droop measurements and fine-grained sampling to detect first-order droops and discuss droop values as well as voltage failure points in hardware.

One of the major contributions of this dissertation is automatic stressmark generation using real hardware. Joseph, Brooks, and Martonosi presented a hand-coded di/dt stressmark [24]. Their basic idea was to create a sequence in which a high-current instruction follows a low-current instruction. The high-current component typically consisted of a memory load/store instruction and the low-current component consisted of a divide instruction followed by a dependent instruction, resulting in a long pipeline stall. However, their di/dt stressmark was manually crafted for a specific microarchitecture based on the knowledge of the current draw of various instructions. Furthermore, they focused only on memory-intensive behavior such as loads and stores and increased current draw by accessing L1 and L2 data caches. In contrast, the approach in this

dissertation does not require microarchitectural knowledge and relies on measured voltage droops in a closed-loop measurement infrastructure.

Ketkar and Chiprout proposed a di/dt stressmark generation methodology using integer linear programming (ILP) [27]. They extracted current draw for certain instructions from a register transfer language (RTL) model for the hardware. Linear programming with constraints was used to maximize voltage droop. However, they focused only on the ALU. It is difficult to make ILP relationships of instructions for all the pipeline stages and the caches; hence, it is difficult to apply their technique to an entire processor, especially one with out-of-order processing, multiple cores, and complex shared resource structures.

Joshi et al. [26] presented a methodology for generating maximum-power viruses and mentioned in passing that high-power and low-power instruction sequences from two different power optimizations can be interleaved to generate a di/dt stressmark. This was only a suggestion, without implementation details or results. Also, they did not talk about the importance of repeating the sequence at the PDN's resonant frequency. Neither di/dt effects nor voltage droops were the focus of Joshi's work.

A significant number of other studies have focused on preventing, reducing, or recovering from di/dt effects or voltage droops [3][5][6][7][8][9][10][15][17][18][21][22] [23]. However, none of these focus on automatically generating di/dt stressmarks.

## 2.5.2. Impact of Compiler Optimization

Valluri and John [67] studied compiler optimization effects on performance and power. The conclusions are that (1) performance improvement by reducing the number of instructions brings energy reduction and that (2) performance improvement by increasing

the overlap in program increases average power dissipation. However, in Valluri and John's work, power is represented as the average power of overall execution. It is problematic because a voltage emergency occurs in a much shorter period than the program execution time, that is, from tens of nano-seconds to micro seconds compared to several minutes.

Reddi et al. proposed a dynamic scheduling workflow based on a checkpoint-and-recovery mechanism to suppress voltage emergencies [51]. Once a code part causes a voltage margin violation, it is registered as a hotspot, and NOP injection and/or code rescheduling is performed by the dynamic compiler. This flow is independent of the architecture or workload. However, users should be careful to set an initial voltage margin properly to avoid frequent voltage emergencies.

# 2.5.3. Managing Inductive Noise

A number of previous papers have explored how to reduce the voltage guardband of the system in order to achieve better performance. The work that comes closest in terms of a hardware implementation is the work by Lefurgy et al. [33] which addressed actively monitoring and managing the voltage guardband based on the use of a critical path monitor or CPM. The CPM monitors the critical pathways in the chip and increases the voltage guardband if the CPM detects potential errors. Although the CPM is a very effective mechanism, it requires additional hardware, monitoring mechanisms, and tuning of the CPM to detect and correct possible errors. The technique in this dissertation on the other hand, is very simple to implement and manage, and only requires a characterization effort to determine the frequency boost possible with FP throttling.

A number of papers have dealt with mitigating voltage droops using software techniques [17][19][57]. These techniques recognize the existence of repetitive code with high di/dt transition activity and dampen or eliminate this activity through software techniques. Software mitigation of noise does not guarantee that all errors will be eliminated. In fact, the software techniques learn from errors detected by hardware (such as a CPM) and adjust the software only after errors are detected. The FP throttling mechanism avoids errors altogether by suppressing the structures which generate the largest voltage droops.

Other work has examined using hardware techniques to manage high droops [40][47][48][49]. Some of the work focuses on using hardware to detect that a resonant droop is about to build and suppresses the droop before it reaches its peak droop value, while others focus on mechanisms to dampen the difference between the high and low power regions by techniques such as throttling issue rates or staged activation and deactivation of clock gated units. All these techniques address the issue of di/dt noise. However, this dissertation is the first to characterize the impact of FP throttling, translate that characterization to a frequency increase, and present results with static and dynamic schemes showing the benefits of the performance increase with FP throttling.

Another body of work explores detecting and mitigating errors via circuit techniques [10][11]. The research using Razor systems assumes that errors will occur and inserts redundancy within latches. Although effective, Razor requires significant new hardware and a completely different design methodology that fundamentally changes the way processors are designed. The FP throttling technique on the other hand, works well with existing systems where the floating point unit is a large contributor to the voltage droop in the system.

There are a wide range of architectural techniques that utilize some type of detection and recovery mechanism to deal with errors [2][16][37] and use redundant structures or replay mechanisms to detect and correct errors. All these techniques incur additional complexity or hardware overhead which FP throttling with frequency boost avoids.

Finally, there are other methods in which the processor frequency can be boosted [38][58]. Frequency boosting techniques such as Turbo Core or Turbo Boost <sup>TM</sup> are in use in state-of-the-art systems from both AMD and Intel. Turbo Core allows the chip to run at a higher frequency than that visible to software. The highest frequency software visible ACPI P-state (P0) is determined under the assumption that all cores on the system are running a high power benchmark under worst case operating conditions. When those conditions are not met, either because not all cores are active or the threads are not high-power threads, the hardware allows the cores to enter a boosted frequency state based on the availability of power headroom. Once the power headroom is depleted, the application returns to a lower power, lower performance DVFS state until power headroom is once again available.

Turbo Core is available on the hardware this dissertation used for the experiments. There is one major difference between the frequency boost possible with Turbo Core and that resulting from FP throttling. With FP throttling, the processor can boost the frequency without an increase in voltage, resulting in a linear increase in power for a potentially linear increase in performance. Turbo Core, on the other hand, requires an increase in both frequency and voltage, resulting in a cubic increase in power. Hence, it is not as efficient as a method for boosting performance. However, it also does not incur any IPC loss due to FP throttling. Turbo Core was disabled for the

analysis presented in this paper in order to study the impact of FP throttling; however, combining the two techniques offers interesting research opportunities in the future.

# **Chapter 3: Methodology**

This chapter describes the overall experimental methodology used in this dissertation. Either a simulation or a hardware measurement method can be used according to the availability of a post-silicon processor. Especially the hardware measurement method in this dissertation enables designers to capture maximum voltage droops on a post-silicon processor. But a simulator has advantages of reconfigurability and the technique in this dissertation can work with simulation models as well, To characterize di/dt behavior, various benchmarks and stressmarks are run from standard benchmarks, such as SPEC CPU2006, to automatically generated stressmarks. Runtime, power, and maximum voltage droop are useful metrics to characterize di/dt noise.

#### 3.1. METHOD FOR CHARACTERIZING VOLTAGE DROOP

To characterize voltage droop on a microprocessor, designers can take either a simulation-based estimation or a hardware-based measurement method according to the current design stage or to the availability of the processor model.

#### 3.1.1. Simulation Method

Simulation enables designers to estimate voltage fluctuations in early design stage even without silicon and to examine microprocessor events that cause voltage fluctuations in more detail, compared to hardware measurement. Simulation is also repeatable; it should give the same results if all the simulation inputs and parameters are the same as that of a previous simulation. However, the accuracy of simulation is the main issue, so the processor model should be well correlated to its current or expected

implementation on silicon.

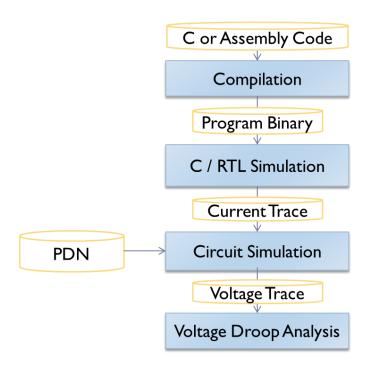

Figure 3.1 shows the current-voltage simulation method. First, a program code is provided with C or assembly format. Next, the program code is compiled and run on a system simulator to estimate current draw per cycle in a microprocessor. During the system simulation, all the activities are counted every cycle and converted as power consumption per cycle. To get instantaneous current values, the obtained cycle power numbers are divided by a DC supply voltage. Then, the current trace from the system simulator is fed to the circuit simulator to simulate voltage fluctuation. After collecting the voltage trace, it is analyzed to identify a maximum voltage droop.

Figure 3.1: Current-voltage simulation.

In this dissertation, for the power (current) simulator, the combination of SimpleScalar [60] and Wattch [7] is selected to estimate current load variations per cycle in a microprocessor. The original simulator is modified to generate a current trace per cycle by dividing the power per cycle by the supply voltage. The modified power simulator is based on the activity counter of each unit in a microprocessor, so it is good at much each unit in the microprocessor is showing how The modification for per-cycle power benchmarks/stressmarks during each cycle. estimation can be applied to another system-level power simulator if such a simulator provides activity monitors for internal units. For circuit simulation, HSPICE [21] is used to simulate the current trace and to measure voltage droop. The current value per cycle from the system-power simulator is converted to HSPICE format as a current source. During the HSPICE simulation, maximum, minimum, and peak-to-peak values of voltage are measured. Instead of HSPICE simulation, the convolution of the processor's current trace and the PDN's impulse response can be used if the result shows enough accuracy compared to HSPICE circuit simulation.

#### 3.1.2. Hardware Measurement Method

Hardware measurement can show real voltage fluctuations on silicon. Most benchmarks/stressmarks finish quickly, so the entire run of each benchmark is possible. However, it is not repeatable; it is difficult to get the same voltage fluctuation at the same time with the previous runs due to many sources of uncertainty in a real system such as OS scheduling for multiple threads. Hardware measurement methods require system hardware such as processors, packages/sockets, and motherboards (MB), and

measurement equipment such as an oscilloscope, differential probe and cable, etc.

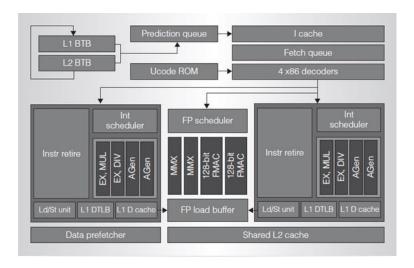

#### 3.1.2.1. System hardware

The multi-core processor mainly used in this dissertation is an AMD Orochi processor, which consists of four Bulldozer modules on the single processor chip. Each Bulldozer module (Figure 3.2) can execute two threads via a combination of shared and dedicated resources [8]. The front-end and floating-point logic is shared between two threads on the same module; however, the rest of the core components (integer and retire logic, load/store unit, first-level TLB, and first-level cache) are separate. Each thread can issue four integer instructions per cycle, however, the two threads together can only issue four floating point instructions per cycle due to the sharing of the floating point units. A thread can have a maximum IPC of four. One Bulldozer module has one 64 KB I-Cache, two 16 KB D-Caches for two hardware threads, and 2MB of L2 cache. Four Bulldozer modules share an 8MB L3 cache. A more detailed description of the Bulldozer module and architectural features is given in [8][12][68]. An AMD Phenom<sup>TM</sup> II X4 Model 925 processor is also used for hardware measurement. The package/socket used is an AM3 and the motherboard is specially designed to provide many test points including supply voltage rails.

Figure 3.2: AMD Bulldozer module. Adopted from Butler et al. [8].

# 3.1.2.2. Measurement equipment

Voltage variations can be measured by probing power supply rails on the hardware system. There are two possible methods to measure voltage variations on hardware: sampling and triggering. The pros and cons of each measurement method are summarized in Table 3.1. This dissertation used sampling for power measurement and triggering for voltage droop measurement, because the sampling rate is not high enough to capture 1st droop and because triggering is good at capturing extreme values such as maximum voltage droop.

|             | Sampling with DAQ                                            | Triggering with Oscilloscope              |

|-------------|--------------------------------------------------------------|-------------------------------------------|

| Pros        | - Users can easily handle the measurement                    | - Accurate (error < 5mV)                  |

|             |                                                              | - FFT analysis is possible                |

| Cons        | - Typically sampling rate is too low to capture di/dt events | - High-bandwidth oscilloscope is required |

|             | - DAQ cable is too far from on-die VDD rails → false noise   | - Probing test pins is difficult          |

| Application | Good for power measurement                                   | Good for di/dt measurement                |

Table 3.1: Comparison of sampling and triggering methods for hardware measurement.

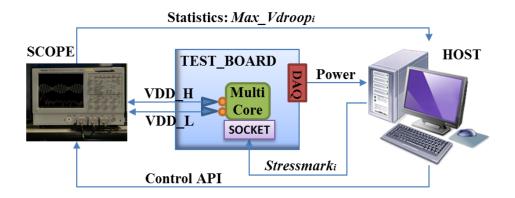

The experimental set-up for hardware in this dissertation is shown in Figure 3.3. Voltage droops on the hardware are measured with a Tektronix TDS5104B oscilloscope (shown in Figure 3.4.(a)) and a 1.7-GHz Tektronix P6248 differential probe (shown in Figure 3.4.(b)) for triggering on large voltage droops. The probing points for the power supply voltage are attached to the package and on-die connections to enable accurate voltage droop measurements. The oscilloscope triggers and records the di/dt events at a sampling rate of 5 gigasamples/second (GS/s).

Power is profiled using a National Instrument's Data Acquisition (DAQ) card (NI-PCIe 6353), whose sampling rate is up to 1.2 megasamples/second (MS/s) (Figure 3.3). A differential cable transfers multiple signals from the power supply lines on the motherboard to the DAQ card in the PC.

(a) Lab environment

(b) Hardware measurement

Figure 3.3: Hardware measurement set-up

(a) Oscilloscope: 1GHz bandwidth Tektronix TDS5104B shows voltage response and frequency analysis

(b) Differential Probe: 1.7-GHz Tektronix P6248 probes processor's power rail

Figure 3.4: Oscilloscope and differential probe used in this dissertation.

#### 3.2. BENCHMARKS

To analyze a processor's normal behavior, standard benchmark suites such as SPEC CPU2006 [62] and PARSEC [5] are mainly used because they represent various programs frequently running on the processor. However, standard benchmarks may not fully exercise a given architecture. For example, a load/store-intensive standard benchmark cannot frequently activate execution units such as the ALU. For some of the studies, supercomputing benchmarks such as *miniFE* [35] and *High-Performance Linpack* [20] are used.

In order to study the susceptibility of processors to voltage fluctuations, designers often resort to specialized benchmarks called di/dt stressmarks. The di/dt stressmarks are either collected from benchmarks that have produced high di/dt stresses in the past or manually designed to induce voltage fluctuations in microprocessors. Stressmarks based on excerpts from real programs may not expose many vulnerabilities of a system; hence often manual generation of stressmarks is done by engineers who are familiar with the

intricacies of the design. However the manual generation of stressmarks is tedious; several works addressed the complexities involved with stressmark generation and developed tools and methodologies to generate stressmarks automatically [1][2][3][4].

In this dissertation, both standard benchmarks and stressmarks are run to represent the usual and extreme user cases. SPEC CPU2006 and PARSEC are selected as standard benchmarks, the existing power and di/dt stressmarks are collected, and synthetic di/dt stressmarks are generated manually or automatically. Table 3.2 lists the benchmarks used in this dissertation.

| Name         | Benchmark Type  | Multi-Threading  | Etc.                 |  |

|--------------|-----------------|------------------|----------------------|--|

| SPEC CPU2006 | Standard        | Multi-programmed | CINT(integer):       |  |

|              | Benchmark Suite | (NO dithering)   | 12 benchmarks        |  |

|              |                 |                  | CFP(floating-point): |  |

|              |                 |                  | 19 benchmarks        |  |

| PARSEC       | Standard        | Multi-threaded   | 12 benchmarks        |  |

|              | Benchmark Suite |                  |                      |  |

| SM1, SM2,    | Manual di/dt    | Multi-threaded / | Industry-level [43]  |  |

| SM-Res       | Stressmark      | Multi-programmed |                      |  |

|              |                 | (dithering)      |                      |  |

| miniFE       | Supercomputing  | Multi-threaded   | Highly scalable      |  |

|              | (HPC) Benchmark |                  |                      |  |

| HP Linpack   | Supercomputing  | Multi-threaded   | High-performance,    |  |

|              | (HPC) Benchmark |                  |                      |  |

| A-Ext,       | Automated di/dt | Multi-programmed | AUDIT in this        |  |

| A-Res        | Stressmark      | (dithering)      | dissertation         |  |

Table 3.2: Standard benchmarks and stressmarks used in this dissertation.

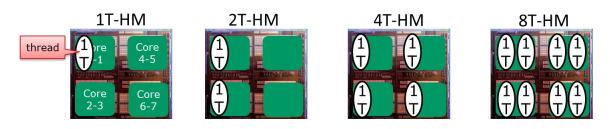

Thread configuration for multi-threading in a multi-core system is set as in Figure 3.5. With up to 4T (4 threads) only one thread runs on each core. When more than 4T one or more cores will run multiple threads. The number of threads will be evenly

distributed. Each program of multi-programmed runs needs to be fixed to a designated processor using *process affinity*, and both Windows and Linux OSes provide the functionality. The configurations in Figure 3.5.(a) are for homogeneous threads, i.e., multiple copies of the same program, and those in Figure 3.5.(b) for heterogeneous threads.

(a) Thread configurations for Homogeneous (HM) threads.

(b) Thread configurations for Heterogeneous (HT) threads.

Figure 3.5: Thread configuration for multi-core system (T=thread).

#### 3.3. METRICS

**Voltage droop** is the main metric of this dissertation. Voltage droop is measured as the difference between the nominal voltage and the measured power supply voltage. Maximum voltage droop during the benchmark run is measured at the difference between the nominal voltage and the lowest power supply voltage during the entire run. The unit

of voltage droop used is mili-volt, **mV**.

In hardware measurement, checking power is necessary to verify that voltage droop is a reasonable range. **Power** can be represented as several ways. Average power, P, is supply voltage (V) times average current (I),  $P = V \times I$ . Instantaneous power reflects voltage and current variations at a specific time,  $p(t) = v(t) \times i(t)$ . The unit of power is wattage, W. However, high power does not always mean high di/dt noise.

**Performance** is defined as the reciprocal of runtime. Runtime is required to estimate energy or energy-delay. **Energy** is computed as the product of runtime and average power, and represents trade-offs between performance and power. Energy is multiplied by runtime to obtain energy-delay product.

# **Chapter 4: Analysis of Voltage Noise in Microprocessor**

This chapter analyzes voltage droops caused by various benchmarks under different conditions. First, voltage droops caused by standard benchmarks such as SPEC CPU2006 and PARSEC are measured on the multi-core hardware and are analyzed to understand typical use case of programs. Next, synchronization effect by multiple threads is discussed and examined to see whether the corresponding di/dt noise is critical on multi-core, multi-threaded systems. The *natural dithering* effect caused by OS interference is observed and introduced. Finally, this chapter studies the compiler optimization impact on voltage droops with various benchmarks by adding a new perspective to Valluri and John's prior discussion [60].

#### 4.1. VOLTAGE DROOP ANALYSIS FOR STANDARD BENCHMARKS

## 4.1.1. Voltage Droop Analysis using Simulation

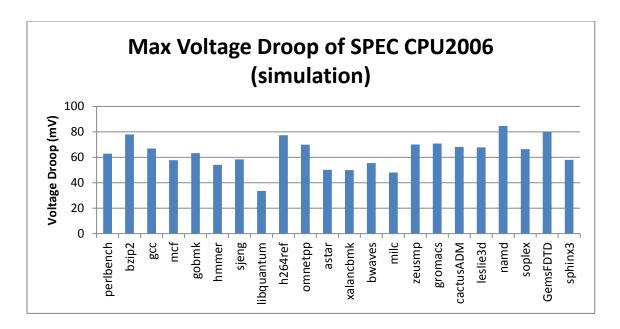

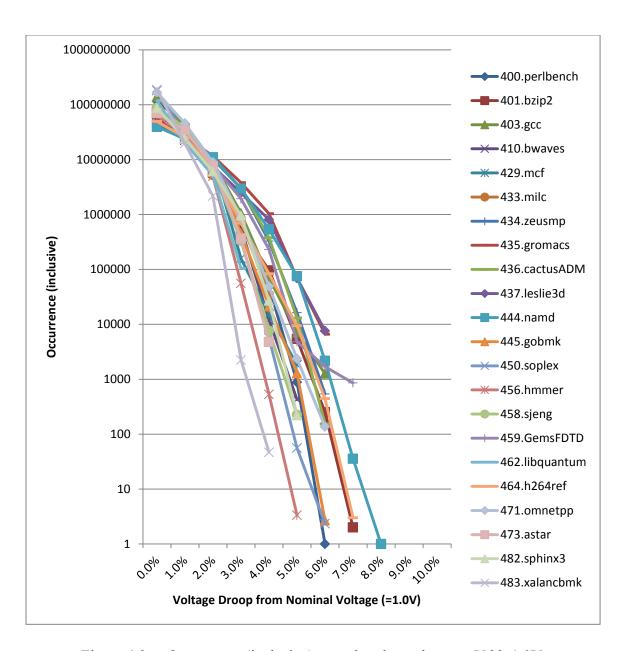

The simulation method is used to analyze voltage droops on standard benchmarks in more detail. Simulation can identify the number of occurrences of voltage droops as well as the maximum voltage droop. Table 4.1 shows the architecture configuration used in the experiments in this section. The configuration targets a general 4-wide processor. In here, 22 benchmarks in the SPEC CPU2006 suite were run, and each benchmark runs 100 million instruction cycles using SimPoint [59]. The simulator was warmed-up for 10 million instruction cycles, and then traced di/dt for 90 million instruction cycles. PDN [61] has 5 to 16A of current swing, and two RLC stages. The nominal voltage was set to 1.0V.

| Parameter          | Values                                            |

|--------------------|---------------------------------------------------|

| CPU Clock          | 3 GHz                                             |

| Fetch/Decode/Issue | 4- / 4- / 4-instruction per cycle                 |

| EXU                | 2 alu, 2 mul/div, 2 falu, 2 fmul/fdiv, 2 mem-port |

| RUU / LSQ          | 128 / 64                                          |

| Branch Predictor   | Combined, 64Kb                                    |

| ВТВ                | 1K entries                                        |

| L1 I/D-Cache       | 64KB / 16KB, 2-way                                |

| L2 Cache           | 2MB, 16-way                                       |

Table 4.1: An architecture configuration for SimpleScalar.

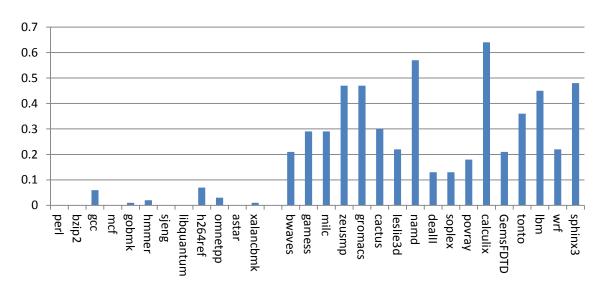

Figure 4.1 shows the maximum voltage droop of the SPEC CPU2006 benchmarks. Y axis of Figure 4.1 is the maximum voltage droop in mV from the nominal voltage set to 1V. Among 22 benchmarks, *namd* has the largest maximum voltage droop, and *libquantum* has the smallest maximum voltage droop. The overall maximum voltage droop in the SPEC CPU2006 varied from 3.4% to 8.5%. One can identify the maximum droop from Figure 4.1, but the graph does not tell whether the maximum droop comes from a single, rare event, in other words, whether how many similar droops occur or not. Figure 4.2 shows the distribution of voltage droop levels during the entire run of each SPEC CPU2006 benchmark. X axis is the percentage of droop from the nominal voltage of 1.0V. Y axis is the number of occurrences in logarithmic scale. The number of occurrences in Figure 4.2 is inclusive, that is, 0.0% includes all the number of occurrences of voltage droops. Even though *GemsFDTD*'s maximum voltage droop is less than *namd*, *GemsFDTD* has more frequent voltage droop at 7% from nominal

voltage. Benchmarks *leslie3d* and *gromacs* do not have an 8% or 7% of voltage droop, but the number of occurrences of two benchmarks is much higher than others. This result implies that a voltage droop analysis only with the maximum voltage droop could ignore the possibility of real failures resulting from highly frequent and comparably larger droops. Voltage at failure analysis is considered and explained in the following chapter.

Figure 4.1: Maximum voltage droop of SPEC CPU2006 in simulation. Vdd is 1.0V.

Figure 4.2: Occurrence (inclusive) at each voltage droop at Vdd=1.0V.

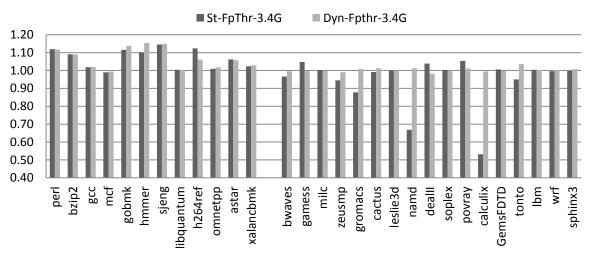

# 4.1.2. Voltage Droop Analysis using Hardware Measurement

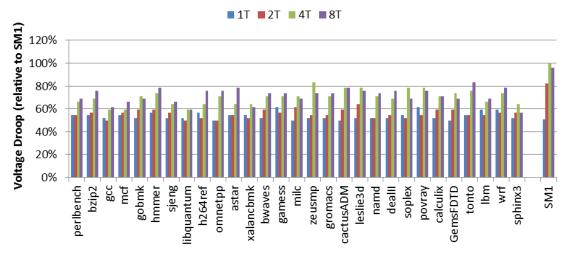

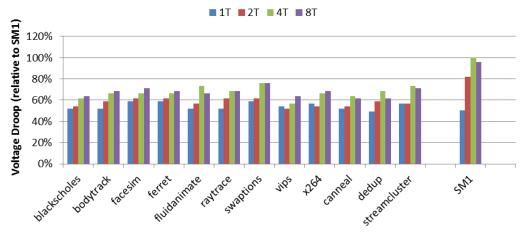

Figure 4.3 shows the maximum droop measured from running the SPEC