Copyright

by

Golam Rasul Chowdhury

2014

## The Dissertation Committee for Golam Rasul Chowdhury Certifies that this is the approved version of the following dissertation:

# Integrated Temperature Sensors in Deep Sub-Micron CMOS Technologies

| Committee:                 |  |

|----------------------------|--|

|                            |  |

| Arjang Hassibi, Supervisor |  |

|                            |  |

| Earl E. Swartzlander       |  |

|                            |  |

| Jack Lee                   |  |

|                            |  |

| Deji Akinwande             |  |

|                            |  |

| Ali Akhar Merrikh          |  |

# Integrated Temperature Sensors in Deep Sub-Micron CMOS Technologies

by

Golam Rasul Chowdhury, B.Sc., M.Sc.

#### **Dissertation**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

**Doctor of Philosophy**

The University of Texas at Austin

May 2014

## **Dedication**

Dedicated to my late parents,

Mansur A. Chowdhury and Aziza B. Chowdhury

#### Acknowledgements

I would like to take this opportunity to acknowledge a group of people who had helped me to pursue my education at this point in my career. My education in general, and specifically this work, would have not happened without their support.

My deepest and sincere gratitude goes to my advisor, Prof. Arjang Hassibi. His constant guidance, and wise mentorship, and always push-for-excellence taught me how to turn an idea into a valuable research work. In addition, I am especially grateful to him to arrange the tape out with TSMC as the last piece of my Ph.D. work.

I would like to thank Professor Earl Swartzlander, Professor Jack Lee, Professor Deji Akinwande, and Dr. Ali Akbar Merrikh at Advanced Micro Devices (AMD) to serve on my dissertation committee.

I would like to specifically thank Professor Earl Swartzlander for his guidance, and help during the course of my research. I visited him many times, and received many suggestions from him that helped me to improve the quality of my work.

I am particularly grateful to Professor Jack Lee for his guidance that helped me to understand the fundamentals and basics of nano-technology and device physics. I am impressed seeing his vast, and depth of knowledge on this topic and his generosity in sharing it. Indeed, his course that I took was one of the best courses that I have taken in graduate school.

Professor Deji Akinwande always offered me a friendly access to him, and I received many good advices from him that helped me to complete this work.

During the testing of my chip I have discussed test related matters with Dr. Ali Akbar Merrikh, and I am grateful to him for his help.

I would like to thank my group members in Prof. Hassibi's team who helped me in many ways. Dr. Arun Manickam and Dr. Rituraj Singh helped with the tape out process with TSMC. Wooyoung Jung and Yousof Mortazavi helped me greatly in the experimental part of my project.

Graduate students and Friends at UT; SK. Fahad Chowdhury and Manzur Rahman extended their help, support, and encouragement to me during my Ph. D.

I am very grateful to GlobalFoundries, and TSMC for fabricating the chips for my research, and making the idea real. I would like to specifically thank Dr. Eric Soenen at TSMC, Austin, for supporting the fabrication of the second and final chip with TSMC.

I would like to thank a team of people at AMD who helped me in many ways beyond technical. My Director Dru Cabler, Managers Dr. Moises Robinson, and Len Disanza facilitated tape out of my chip with GlobalFoundries, allowed me to take breaks from my job to attend classes at UT, and focus on my research work. Their support was also instrumental to allow me use AMD labs to characterize my chip. I had many technical discussions with Michael Nix, Technical Fellow at AMD. Dr. Shawn Searles offered his help to integrate my chip into AMD's test chip. My coworkers Firas Abughazaleh, Farid Barakat, Curt Brody, Dr. Ahmed Younes, and Dr. Jay Fletcher offered me many helpful discussions. Vu Le and Raymond Lee have offered me some help with the layout of the chips. Dr. Alvin Loke, Dennnis Fischette, and Tintin Wee reviewed the papers I submitted for publications. Dru Cabler and Dr. Robinson facilitated the filling of patent related to this work. Robert Palomares helped me with some lab setup.

At my present work at Synaptics, I would like to offer a special thanks to Dr. Mucahit Kozak for many helpful discussions I had with him which helped me improve the quality of my research work. Marshal Bell, David Klein, Dr. Yihong Yang, and Dr.

Mucahit Kozak have reviewed the writing of my dissertation, and provided valuable feedback. My Senior Director Steve Lo has encouraged me towards the completion of my degree. Mahmoud Sadollahi helped me during the data collection in the lab.

My friends Ayman Kabire helped me with the layout of the test board. Dr. Mohammad Zeidan at National Instruments helped me with some valuable lab works. I thank them for their kind help and support. My friends at Silicon Labs; Farris Bar helped me with data collection in the lab, and Dr. Abdulkerim Coban shared his knowledge of delta-sigma techniques with me. I thank them both for their help.

I would like to thank Melanie Gullick for her kind help in many logistic matters during the entire course of my graduate studies. Special thanks to Andrew Kieschnik for helping me with CAD issues, and responding to my emails sometimes very late at night. Robert Pennman helped me with the formatting of my dissertation, and I appreciate his kind help as well. Special thanks to Robin Farlow, Vice Principal at Austin Peace Academy, for proof reading the chapters of my dissertation.

My special gratitude and prayers go to my dear late parents, Mansur A. Chowdhury and Aziza B. Chowdhury. They were the source of inspiration for my education.

A very dear and respected person in my life, Khondoker Khaled, provided me with financial support for my high school and undergraduate studies. At this time, I express my sincere gratitude to him and his family for their support for my education.

At the end, I would like to specially thank my wife, Rubeena Shahnaz for her continuous support during the entire course of my Ph. D. work. I acknowledge the sacrifice that Rubeena, my son Raiyan Chowdhury, and my daughter Afnaan Chowdhury made for my Ph. D.

**Integrated Temperature Sensors in Deep Sub-Micron CMOS**

**Technologies**

Golam Rasul Chowdhury, Ph. D.

The University of Texas at Austin, 2014

Supervisor: Arjang Hassibi

Integrated temperature sensors play an important role in enhancing the

performance of on-chip power and thermal management systems in today's highly-

integrated system-on-chip (SoC) platforms, such as microprocessors. Accurate on-chip

temperature measurement is essential to maximize the performance and reliability of

these SoCs. However, due to non-uniform power consumption by different functional

blocks, microprocessors have fairly large thermal gradient (and variation) across their

chips. In the case of multi-core microprocessors for example, there are task-specific

thermal gradients across different cores on the same die. As a result, multiple temperature

sensors are needed to measure the temperature profile at all relevant coordinates of the

chip. Subsequently, the results of the temperature measurements are used to take

corrective measures to enhance the performance, or save the SoC from catastrophic over-

heating situations which can cause permanent damage. Furthermore, in a large multi-core

microprocessor, it is also imperative to continuously monitor potential hot-spots that are

prone to thermal runaway. The locations of such hot spots depend on the operations and

instruction the processor carries out at a given time.

Due to practical limitations, it is an overkill to place a big size temperature sensor

nearest to all possible hot spots. Thus, an ideal on-chip temperature sensor should have

viii

minimal area so that it can be placed non-invasively across the chip without drastically changing the chip floor plan. In addition, the power consumption of the sensors should be very low to reduce the power budget overhead of thermal monitoring system, and to minimize measurement inaccuracies due to self-heating.

The objective of this research is to design an ultra-small size and ultra-low power temperature sensor such that it can be placed in the intimate proximity of all possible hot spots across the chip. The general idea is to use the leakage current of a reverse-bias *p-n* junction diode as an operand for temperature sensing. The tasks within this project are to examine the theoretical aspect of such sensors in both Silicon-On-Insulator (SOI), and bulk Complementary Metal-Oxide Semiconductor (CMOS) technologies, implement them in deep sub-micron technologies, and ultimately evaluate their performances, and compare them to existing solutions.

### **Table of Contents**

| List of Tables                                                                    | xiv |

|-----------------------------------------------------------------------------------|-----|

| List of Figures                                                                   | XV  |

| Chapter 1: Motivation and Outline                                                 | 1   |

| 1.1 MOTIVATION                                                                    | 1   |

| 1.2 OUTLINE                                                                       | 5   |

| Chapter 2: Integrated Temperature Sensors                                         | 6   |

| 2.1 INTRODUCTION                                                                  | 6   |

| 2.2 TEMPERATURE SENSORS IN MULTI-CORE MICROPROCESS                                |     |

| 2.3 SENSORS FOR THERMAL AND POWER MANAGEMENT WIT                                  | TH  |

| 2.4 DESIGN CHALLENGES IN SUB-MICRON TECHNOLOGIES                                  |     |

| Chapter 3: Existing Architectures for On-chip Integrated Temperature Sensor       | s14 |

| 3.1 INTRODUCTION                                                                  | 14  |

| 3.2 ON-CHIP TEMPERATURE SENSOR ARCHITECTURES                                      | 15  |

| 3.2.1 Temperature Sensors with Forward Biased Bipolar Junction Transistors (BJTs) | 15  |

| 3.2.2 MOSFET-based Temperature Sensors                                            | 20  |

| 3.2.3 Resistor-Based Temperature Sensors                                          | 25  |

| 3.2.4 Thermal Diffusivity Sensor                                                  | 28  |

| 3.3 REMOTE AND DISTRIBUTED ON-CHIP TEMPERATURE SEN                                |     |

| 3.4 SUMMARY AND CONCLUSION                                                        | 34  |

| Chapter 4: An On-Chip Temperature Sensor with a Self-Discharging Diode            | 36  |

| 4.1 INTRODUCTION                                                                  | 36  |

| 4.2 SELF-DISCHARGING DIODE TEMPERATURE SENSOR                                     | 36  |

| 4.2.1 Basic Concept and Theory of Operation                                       | 37  |

| 4.2.2 Mathematical Formulation                                                    | 38  |

| 4.2.3 Time-to-Digital Convertor (TDC)                                                    | 40 |

|------------------------------------------------------------------------------------------|----|

| 4.2.4 p-n Junction Diodes in CMOS Processes                                              | 40 |

| 4.3 CIRCUIT DESIGN OF THE PROPOSED SENSOR                                                | 41 |

| 4.3.1 The Transistor Level Schematic of the Sensor                                       | 42 |

| 4.3.1.1: Reference Circuit                                                               | 43 |

| 4.3.1.2: Temperature Sensing Diode and Sampling Circuit                                  | 44 |

| 4.3.1.3: The Isolation Buffer (Pseudo-Differential Amp )                                 | 47 |

| 4.3.1.4: The Dynamic Comparator                                                          | 48 |

| 4.3.1.5: The Post Amplifier (post-Amp)                                                   | 49 |

| 4.4 TIMING DIAGRAM AND PULSE DURATION                                                    | 50 |

| 4.5 MEASUREMENT UNCERTAINTIES AND ERRORS                                                 | 52 |

| 4.5.1 Errors Due to Nonlinearity                                                         | 52 |

| 4.5.1.1 C <sub>P</sub> Nonlinearity                                                      | 52 |

| 4.5.1.2 Nonlinearity of the Diode Sampling Circuit                                       | 53 |

| 4.5.2 Errors Due to Offsets                                                              | 53 |

| 4.5.3 Errors Due to Charge Injection                                                     | 54 |

| 4.5.4 Leakage of the Sampling Switches                                                   | 54 |

| 4.6 LAYOUT AND FABRICATION                                                               | 55 |

| 4.7 MEASUREMENT RESULTS                                                                  | 56 |

| 4.8 PERFORMANCE COMPARISON                                                               | 59 |

| 4.9 SUMMARY                                                                              | 60 |

| Chapter 5: Delta-Sigma (Δ-Σ) Modulation Techniques                                       | 61 |

| 5.1 INTRODUCTION                                                                         | 61 |

| 5.2 BASIC ARCHITECTRUE OF A FIRST-ORDER DISCRETE-TIME MODULATOR                          |    |

| 5.3 SIGNAL AND NOISE TRANSFER FUNCTIONS OF THE FIRST-ORDER $\Delta$ - $\Sigma$ MODULATOR |    |

| 5.4 CONTINUOUS-TIME $\Delta$ - $\Sigma$ MODULATOR                                        | 65 |

| 5.5 ADVANTAGES OF CONTINUOUS-TIME $\Delta$ - $\Sigma$ MODULATOR O'DISCRETE-TIME          |    |

| 5.6 SUMMARY                                                                              | 68 |

|                                                                                          |    |

| Cn | Loop Loop                                                                           | _   |

|----|-------------------------------------------------------------------------------------|-----|

|    | 6.1 INTRODUCTION                                                                    | 69  |

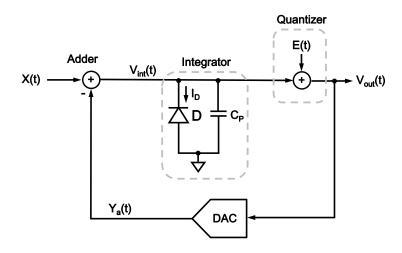

|    | 6.2 ARCHITECTURE                                                                    | 71  |

|    | 6.3 CIRCUIT DESIGN OF THE $\Delta$ - $\Sigma$ MODULATOR                             | 73  |

|    | 6.3.1 The Start-up/Reset Circuit                                                    | 74  |

|    | 6.3.2 The Temperature Sensing <i>p-n</i> Diode                                      | 75  |

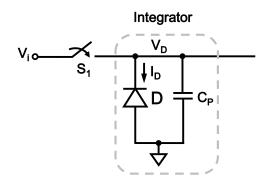

|    | 6.3.3 The Integrator                                                                | 77  |

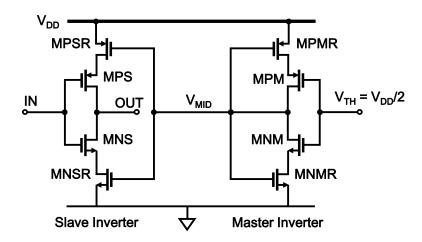

|    | 6.3.4 The Comparator                                                                | 77  |

|    | 6.3.5 The D-Flip-Flop as the Sampler                                                | 80  |

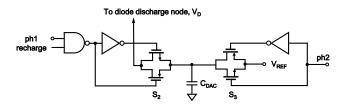

|    | 6.3.6 The Reference Feedback DAC                                                    | 81  |

|    | 6.3.7 Digital Filter                                                                | 82  |

|    | 6.4 MEASURING TEMPERATURE FROM D <sub>OUT</sub>                                     | 83  |

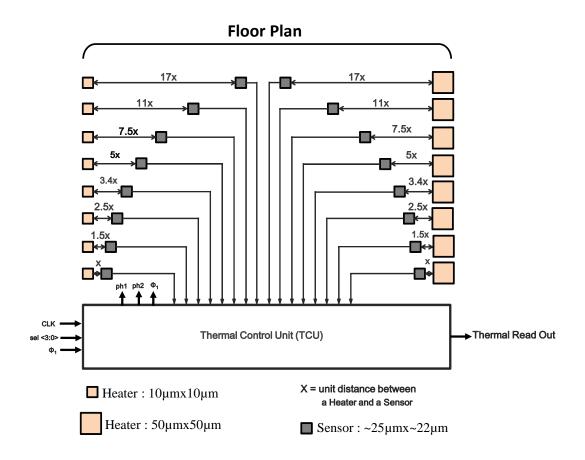

|    | 6.5 A THERMAL MONITORING SYSTEM USING SELF-DISC<br>DIODES WITHIN A DELTA-SIGMA LOOP |     |

|    | 6.6 LAYOUT AND FABICATION                                                           | 89  |

|    | 6.7 SIMULATION RESULTS                                                              | 91  |

|    | 6.8 POST-SILICON MEASURED DATA                                                      | 93  |

|    | 6.8.1 Selecting the bandwidth of the Digital Filter                                 | 97  |

|    | 6.8.2 Measurement of Diode Current                                                  | 98  |

|    | 6.9 SOURCES OF NOISE IN THE SENSOR                                                  | 100 |

|    | 6.9.1 Quantization Noise                                                            | 100 |

|    | 6.9.2 Diode Shot Noise                                                              | 101 |

|    | 6.9.3 Reset Noise                                                                   | 102 |

|    | 6.9.4 Feedback Noise                                                                | 102 |

|    | 6.10 INACCURACY OF TEMPERATURE MEASUREMENTS                                         | 106 |

| Ch | apter 7: Summary and Future Works                                                   | 109 |

|    | 7.1 SUMMARY                                                                         | 109 |

|    | 7.2 SUGGESTIONS FOR FUTURE WORKS                                                    | 111 |

|    | 7.2.1 On-Chip Digital Filter                                                        | 111 |

|    | 7.2.2 On-Chip Look Up Table                                                         | 111 |

| 7.2.3 Use Larger Diode to Increase Speed and Accuracy | 112 |

|-------------------------------------------------------|-----|

|                                                       |     |

| References                                            | 113 |

### **List of Tables**

| Table 3.1: Qualitative comparison of existing thermal sensing solutions              | 34 |

|--------------------------------------------------------------------------------------|----|

| Table 4.1: Performance Comparison.                                                   | 50 |

| Table 6.1: Summary of Monte-Carlo simulation results for the offset of the invention | te |

| comparator.                                                                          | 79 |

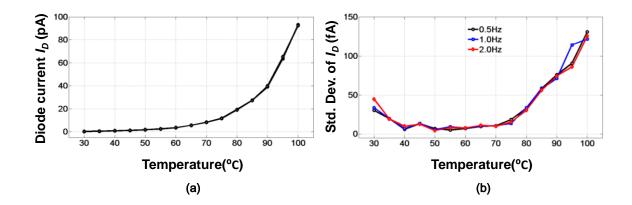

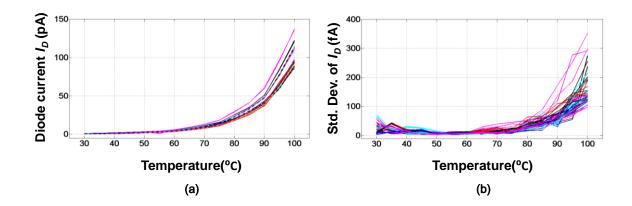

| Table 6.2: Diode leakage currents and standard deviations (sigma) of a sensor        | 98 |

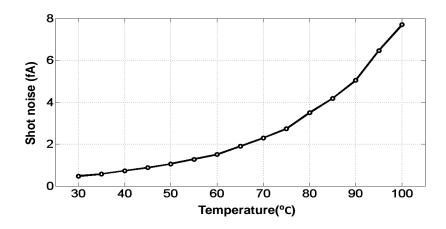

| Table 6.3: Diode shot noise and total noise for the modulator of Table 6.210         | )4 |

## **List of Figures**

| Figure 2.1: Xeon® EX processor core count trend                                             | 7        |

|---------------------------------------------------------------------------------------------|----------|

| Figure 2.2: An integrated function of power and thermal control unit                        | 10       |

| Figure 2.3: An Example of DVFS operation to manage on chip power and the                    | ermal    |

| profile                                                                                     | 11       |

| Figure 3.1: A Typical Temperature Sensor Architecture                                       | 14       |

| Figure 3.2: CMOS cross-section of (a) vertical <i>p-n-p</i> BJT, (b) lateral <i>p-n-p</i> B | JT, and  |

| (c) vertical <i>n-p-n</i> BJT                                                               | 16       |

| Figure 3.3: Block diagram of a <i>p-n-p</i> BJT temperature sensor                          | 16       |

| Figure 3.4: Temperature properties of voltages in a BJT temperature sensor.                 | 18       |

| Figure 3.5: Block diagram of a MOSFET based sensor.                                         | 20       |

| Figure 3.6: The PTAT current generator of the sensor presented in Fig. 3.5                  | 21       |

| Figure 3.7: Block diagram of a temperature sensor based on the delay of a ch                | ain of   |

| inverters                                                                                   | 23       |

| Figure 3.8: Block diagram of a resistor-based temperature sensor                            | 26       |

| Figure 3.9: Linear to temperature dependent bias current (a) and almost indep               | pendent  |

| of temperature bias current (b)                                                             | 26       |

| Figure 3.10: Current starved inverter chain based ring oscillator                           | 27       |

| Figure 3.11: Cross-section of a thermal diffusivity sensor.                                 | 28       |

| Figure 3.12: Practical implementation of the electro-thermal FLL.                           | 29       |

| Figure 3.13: Block diagram of a temperature sensor with remote sensing                      | 32       |

| Figure 3.14: Circuit inside the BJT sense stage to provide the biasing current              | s to the |

| sensors                                                                                     | 33       |

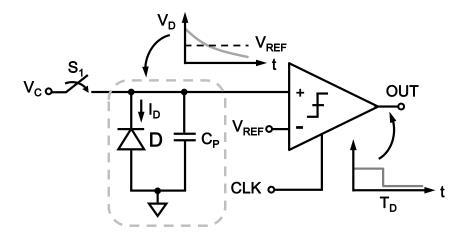

| Figure 4.1: Proposed temperature sensor architecture.                                       | 37       |

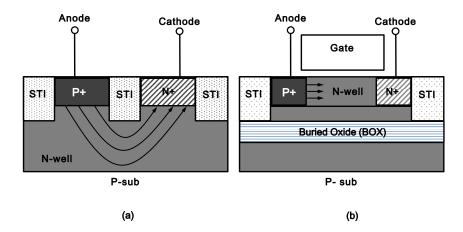

| Figure 4.2: Cross-sectional view of a <i>p-n</i> diode showing the direction of current flow         |

|------------------------------------------------------------------------------------------------------|

| by the arrows in a (a) bulk diode, and (b) SOI diode41                                               |

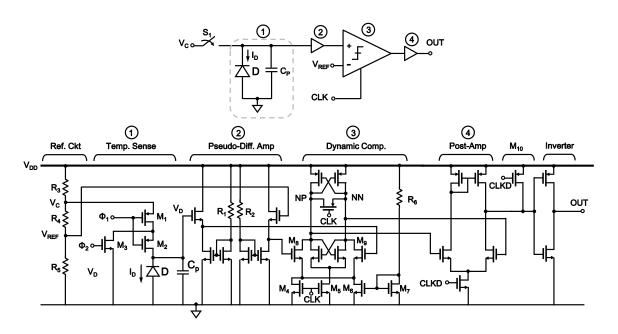

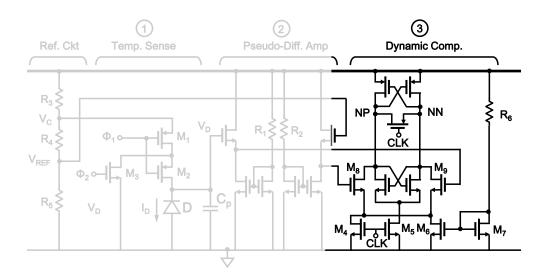

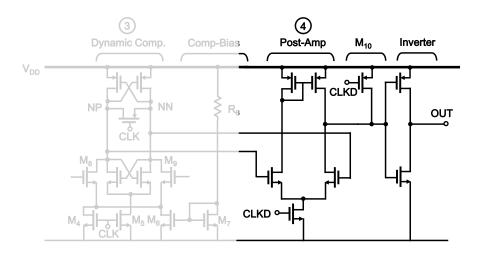

| Figure 4.3: The complete transistor level schematic of the sensor                                    |

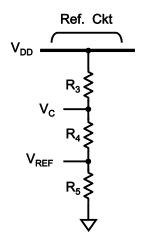

| Figure 4.4: The reference circuit of the sensor                                                      |

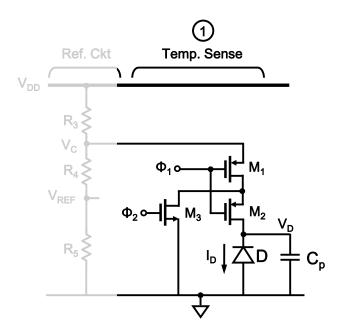

| Figure 4.5: Temperature sensing diode, and sampling circuit of the sensor44                          |

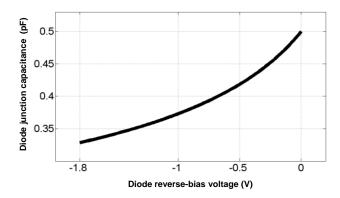

| Figure 4.6: An example of diode junction capacitance as a function of its reverse-bia                |

| voltage45                                                                                            |

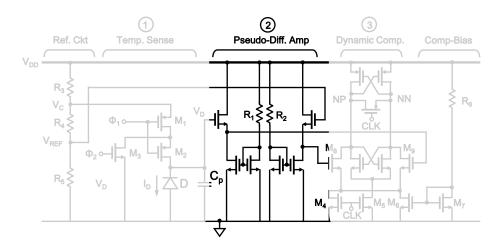

| Figure 4.7: The pseudo-differential Amplifier as the isolation buffer47                              |

| Figure 4.8: The dynamic comparator of the sensor                                                     |

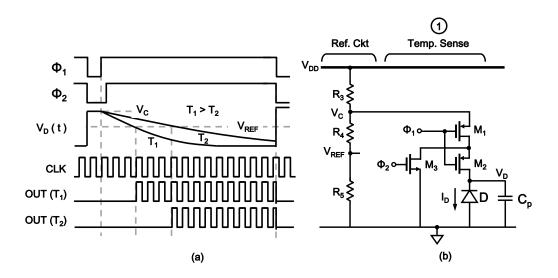

| Figure 4.9: The post amplifier (Post-Amp) of the sensor                                              |

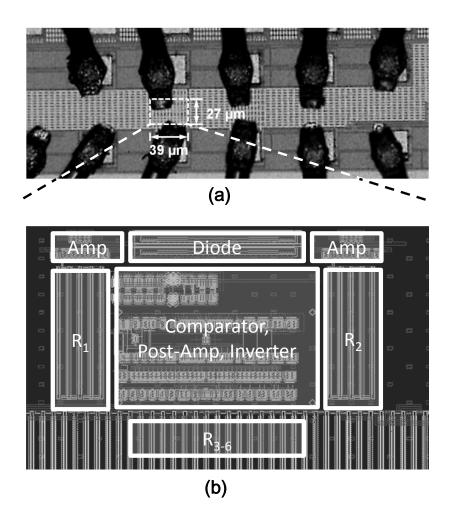

| Figure 4.10: (a) The timing diagram of the first sensor in 32nm SOI, and (b) diode                   |

| with the sampling and reference circuits                                                             |

| Figure 4.11 (a) Chip micrograph, and (b) layout of the on-chip temperature sensor.                   |

| 55                                                                                                   |

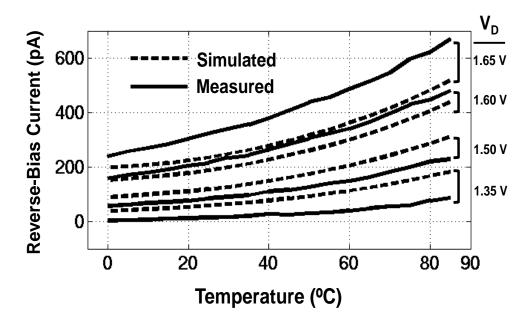

| Figure 4.12: Simulated vs. measured diode reverse-bias currents for various $V_D$ . 56               |

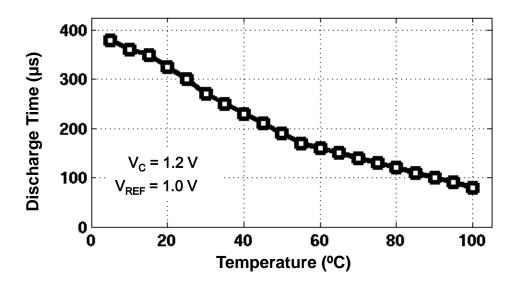

| Figure 4.13: Measured discharge time as a function of temperature                                    |

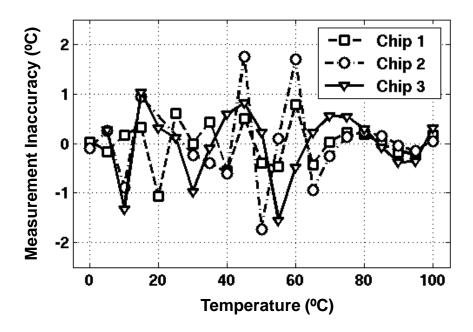

| Figure 4.14: Measurement inaccuracy vs. temperature                                                  |

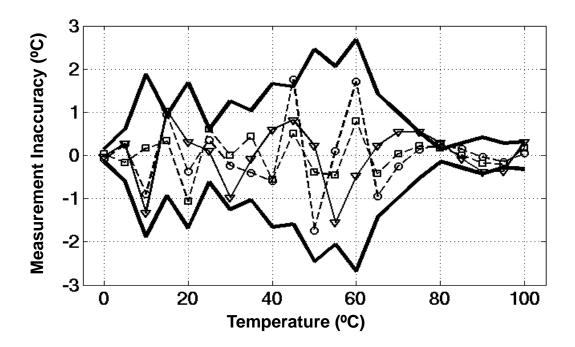

| Figure 4.15: Measurement inaccuracy vs. temperature for 3 different chips, bold line                 |

| indicate $\pm 3\sigma$ values. 59                                                                    |

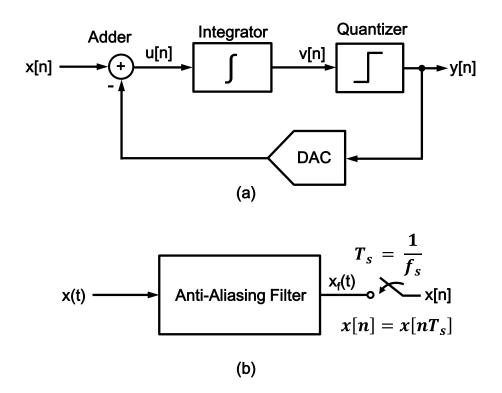

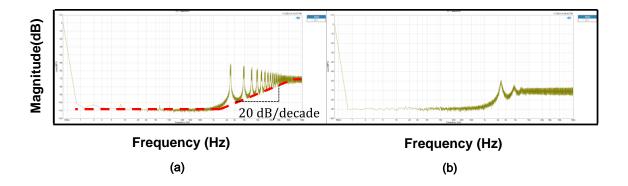

| Figure 5.1: Basic architecture of a first-order discrete-time $\Delta$ - $\Sigma$ modulator (a), and |

| front-end anti-aliasing filter and sampler (b)                                                       |

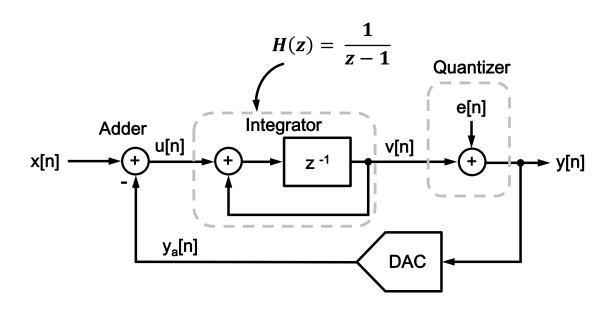

| Figure 5.2: Linear model of a first-order discrete-time $\Delta$ - $\Sigma$ modulator63              |

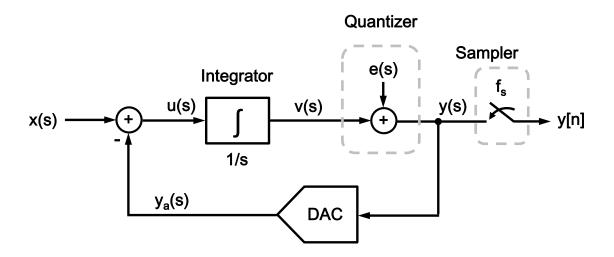

| Figure 5.3: Linear model of a first order continuous-time $\Delta$ - $\Sigma$ modulator65            |

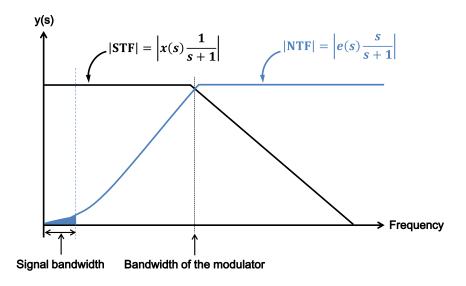

| Figure 5.4: Frequency response of a first-order continuous-time $\Delta$ - $\Sigma$ modulator. 66    |

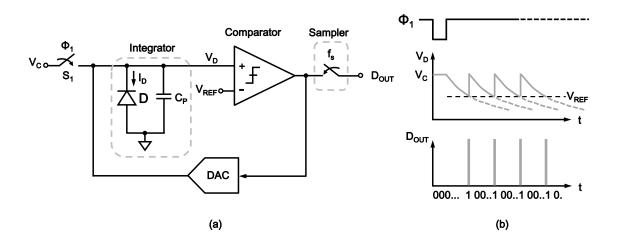

| Figure 6.1: Basic concept of the sensor in a delta-sigma loop (a), and timing diagram               |

|-----------------------------------------------------------------------------------------------------|

| (b)69                                                                                               |

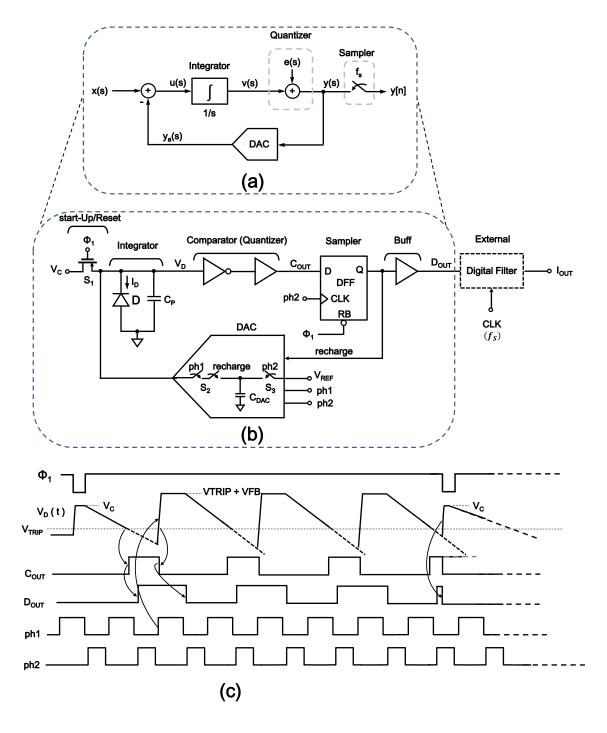

| Figure 6.2: Basic block diagram of a first-order continuous-time $\Delta$ - $\Sigma$ modulator (a), |

| basic architecture of the proposed $\Delta$ - $\Sigma$ modulator (b), and its timing                |

| diagram (c)70                                                                                       |

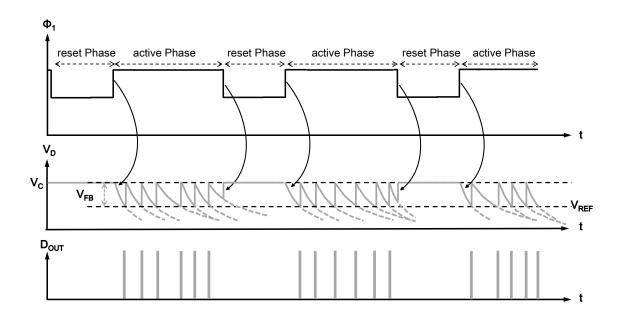

| Figure 6.3: Timing diagram showing pulse density modulated output73                                 |

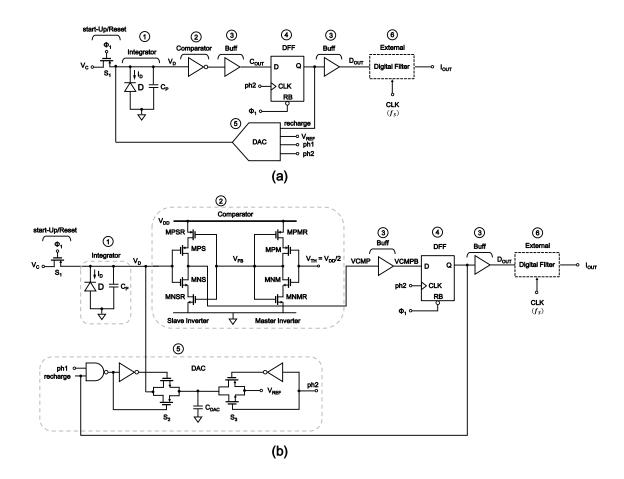

| Figure 6.4: The block diagram (a), and complete schematic of the first-order $\Delta$ - $\Sigma$    |

| modulator, (b)74                                                                                    |

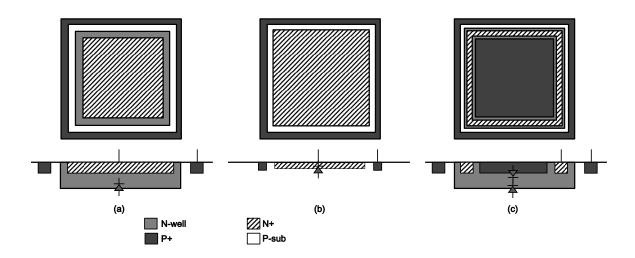

| Figure 6.5: Top and cross-sectional views of different <i>p-n</i> diode architectures,              |

| Nwell/Psub (a), N+/Psub (b), and P+/Nwell (c)                                                       |

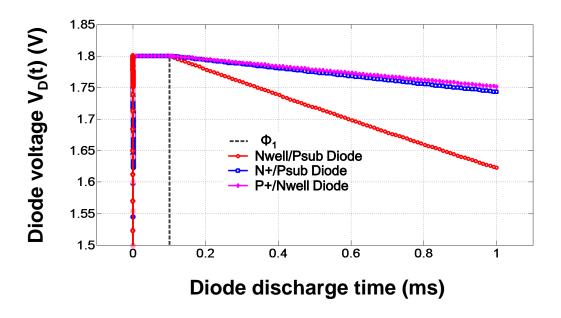

| Figure 6.6: Simulation showing the discharges of the three available diodes76                       |

| Figure 6.7: The continuous-time integrator of the $\Delta$ - $\Sigma$ modulator                     |

| Figure 6.8: Proposed switching voltage (offset) compensated comparator78                            |

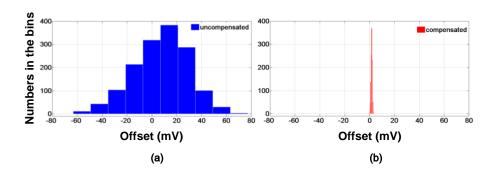

| Figure 6.9: Monte-Carlo simulations showing offset voltages of uncompensated                        |

| comparator (a), and compensated comparator (b)79                                                    |

| Figure 6.10: The reference DAC of the $\Delta$ - $\Sigma$ modulator                                 |

| Figure 6.11: The linear model of the proposed modulator in time domain83                            |

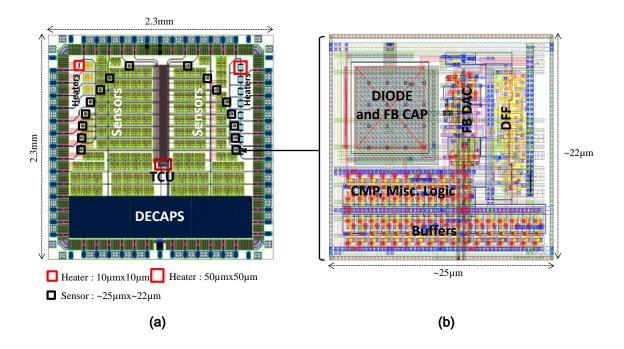

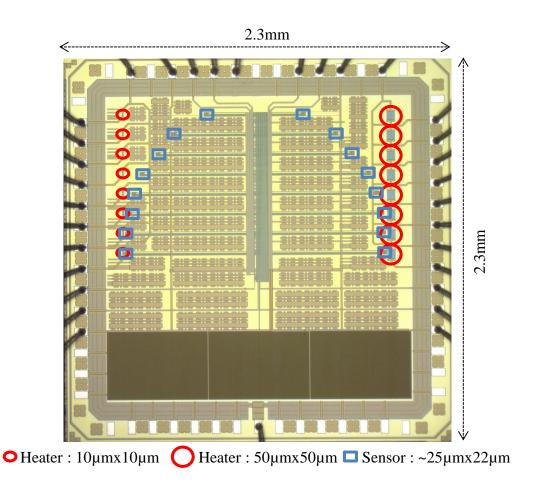

| Figure 6.12: Floor plan of the chip showing all 16 sensors, heaters, and thermal                    |

| control unit.                                                                                       |

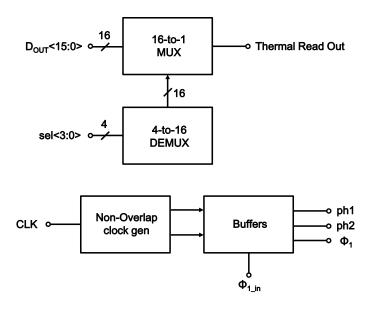

| Figure 6.13: Block Diagram of the Thermal Control Unit (TCU)86                                      |

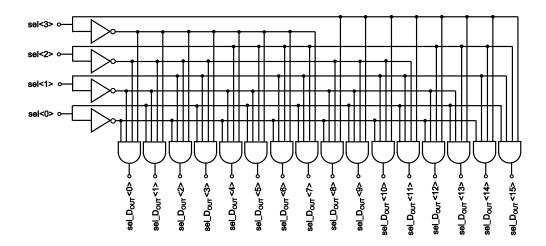

| Figure 6.14: 4-to-16 DEMUX of the TCU.                                                              |

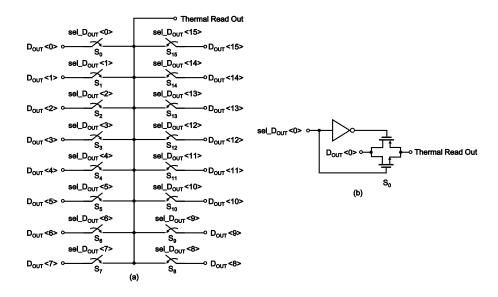

| Figure 6.15: 16-to-1 MUX of the TCU (a), and schematic of each switch (b)88                         |

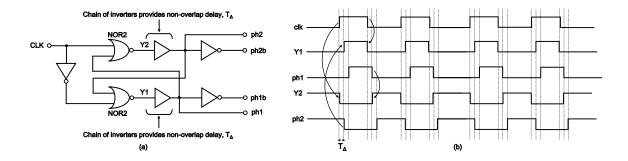

| Figure 6.16: The two-phase non-overlap clock generation circuit (a), and its timing                 |

| diagram (b)88                                                                                       |

| Figure 6.17: | The layout of the chip (a), and layout of one $\Delta$ - $\Sigma$ Modulator sensor (b) | )).              |

|--------------|----------------------------------------------------------------------------------------|------------------|

|              | 89                                                                                     | )                |

| Figure 6:18: | Chip micrograph90                                                                      | )                |

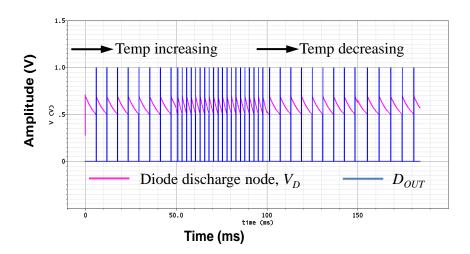

| Figure 6.19: | Simulation results showing 1-bit data and diode discharge voltage $V_D$                | at               |

|              | different temperatures91                                                               | l                |

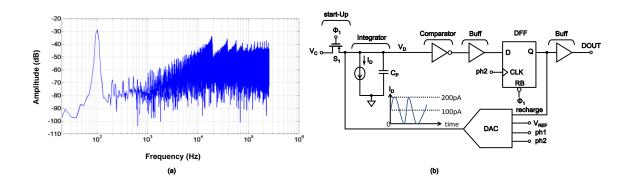

| Figure 6.20: | Simulation results showing FFT of 1-bit data, (a), and simulation test                 | -                |

|              | setup with the diode replaced with a sine wave current, (b)92                          | 2                |

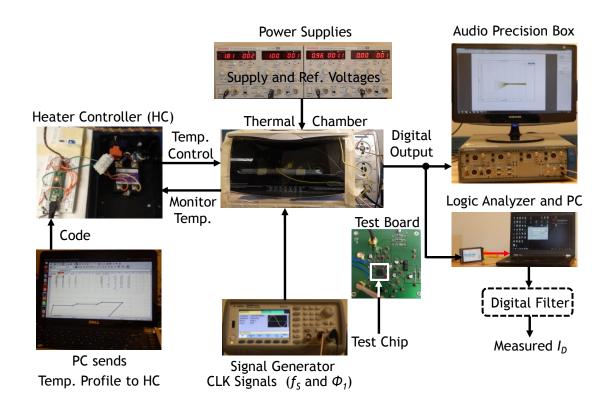

| Figure 6.21: | Measurement setup. 93                                                                  | 3                |

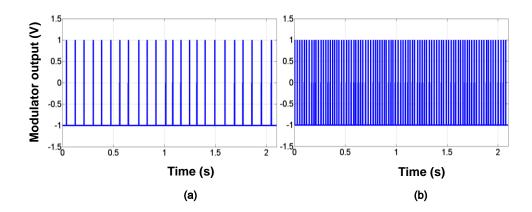

| Figure 6.22: | Simulation results showing 1-bit digital output of the modulator at 30                 | ) <sup>0</sup> C |

|              | (a) and at 50°C (b)94                                                                  | 1                |

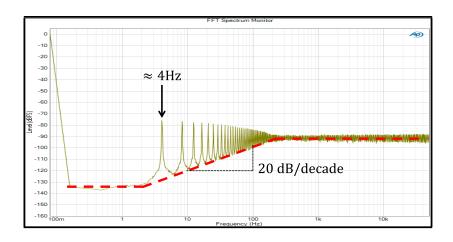

| Figure 6.23: | FFT spectrum of the 1-bit data at 30°C with no dither applied95                        | 5                |

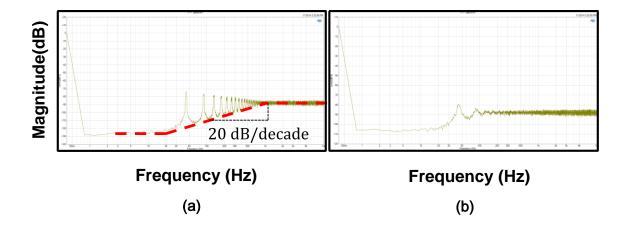

| Figure 6.24: | FFT spectrum of the 1-bit data at 50°C with no dither applied (a), and                 | 1                |

|              | with 10mV dither applied (b)96                                                         | 5                |

| Figure 6.25: | FFT spectrum of the 1-bit data at 100°C with no dither applied (a), ar                 | nd               |

|              | with 10mV RMS dither applied (b)                                                       | 7                |

| Figure 6.26: | The profile of diode leakage current, $I_D$ , (a) and standard deviations of           | of $I_D$         |

|              | (b) for three different reset rates, 0.5Hz, 1.0Hz, and 2.0Hz99                         | )                |

| Figure 6.27: | Diode shot noise for the modulator of Table 6.2105                                     | 5                |

| Figure 6.28: | Diode currents $I_D$ (a), and their sigma (noise) values (b), for all 16               |                  |

|              | sensors measured. 105                                                                  | 5                |

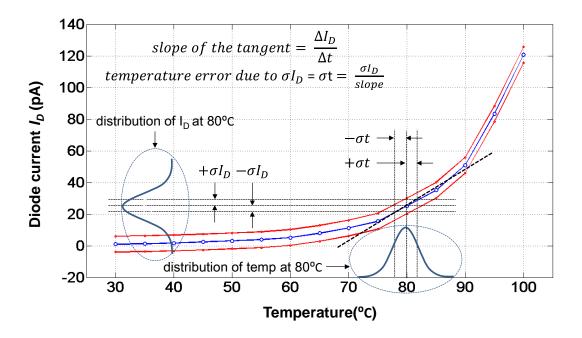

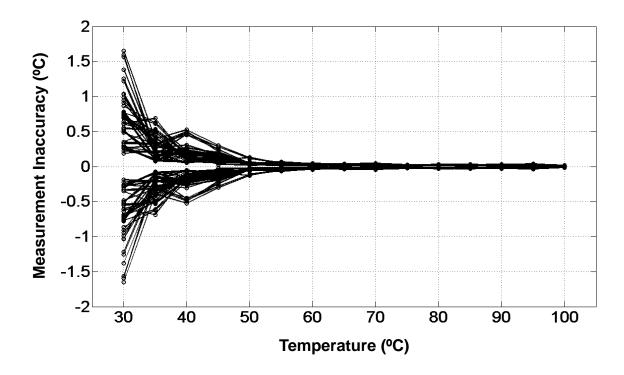

| Figure 6.29: | Measurement of inaccuracy of temperature106                                            | 5                |

| Figure 6.30: | Measurement inaccuracy vs. temperature for 16 different sensors. 107                   | 7                |

#### **Chapter 1: Motivation and Outline**

#### 1.1 MOTIVATION

Over the past few decades, the semiconductor industry has seen a revolutionary increase in computing performance due to the dramatic increase of integration following the trend predicted by Gordon Moore [1-2]. With the scaling of technology, today's highly integrated SoCs (System-on-Chips) and microprocessors, integrate more components on a smaller chip; yet they continuously offer more processing power at higher speeds than ever before. Due to the aggressive scaling along with higher level of integration, and increased operating speed, the power consumption per unit area of an integrated circuit (ICs) is increasing very fast, and the projections for future generations suggest a rise in Central Processing Unit (CPU) power [3]. The power of a chip is dissipated mainly as heat. Therefore, increased power consumption can lead to higher junction temperatures, which in turn can affect the device performance, and in case of over-heating the reliability of a chip [4]. The power and thermal management of high-power density chips is therefore becoming imperative; yet it remains costly and challenging.

Dynamic Voltage-Frequency Scaling (DVFS) is an on-chip technique used for many years in both high-performance computing (e.g., servers and desktops) and power-efficient mobile (e.g., laptops and smart phones) applications to manage thermal limits by dynamically adjusting the power consumption levels [5]. Generally speaking, DVFS depends on continuous monitoring of on-chip thermal profiles using on-chip temperature

sensors. As a result, integrated temperature sensors are becoming an integral part of all high-performance SoCs as they are an integral part of any thermal management (and DVFS) system.

While implementation of on-chip sensors is a simple concept, the actual implementation of them in the context of DVFS is extremely challenging. Today's massively integrated SoCs which include millions of transistors include many different functional blocks that consume power very in-homogeneously. Hence, it is common to see a large and time-varying thermal gradient across SoCs. Furthermore, in some specific architecture (*e.g.*, microprocessors), burst operations are common which can result in localized hot spots. Excessive heat from such local hot spots may result in rapid device aging, lower reliability, increased electro-migration, and even total chip failure.

Managing the dissipated heat, and temperature profile of the chips is also important in power-efficient computing platforms. The main reason is that these systems, unlike, desktop, mainframes, and stationary systems; do not have high-performance and reliable heat sinks. To avoid thermal runaway scenarios that can cause irreversible damage, the temperature across the chip in these applications should also be continuously monitored by deploying multiple temperature sensors, and adjusting the performance accordingly.

It is important to recognize that independent of the application or platform, in all SoCs with DVFS, temperature information is not used for managing the heat dissipation only, but it is also being leveraged to maximize the overall performance. For example, in multi-core microprocessors, the workload is continuously shuffled between different

cores before the temperature rises to a critical level. Alternatively, the clock rate and/or voltage level is dynamically adjusted to boost system performance within a certain thermal budget [6-7].

Since integrated temperature sensors do not participate in the main activities of the SoC, *e.g.*, in the computing operations of a microprocessor, but rather, play an auxiliary role of on-chip temperature measurement, their area should be kept small to reduce cost, broadly defined. In addition, their power consumption should also be very small which will also help to reduce error in temperature measuring caused by self-heating. Such criteria make the design of such sensors difficult as they have a tradeoff with the accuracy and response-time, *i.e.*, larger area sensor with a high power budget exhibit high accuracy and fast response time.

The desired number of sensors in a SoC, their exact coordinates on the die, and their performance, depend greatly on DVFS algorithm, integrated circuit (IC) packaging, and cooling system (if any). The particular application that is targeted in this research is a highly integrated multi-core processor which requires many sensors on multiple locations across the die to monitor the temperature profile of the chip. Particularly, the focus is on the sensor block implementation.

Creating integrated temperature sensors using deep sub-micron Complementary Metal-Oxide-Semiconductor (CMOS) digital processes is not an easy task. Such processes are mainly optimized for logic functions and digital processes, and neither analog nor sensing functions. Therefore, one needs to deal with challenges like reduced voltage headroom, increased process variations, and increased transistor leakage [8]-[9].

In this dissertation, the concept, design, and implementation of an extremely small and ultra-low power temperature sensor are presented. Because of its ultra-small size and extremely low power, many of these sensors can be placed on the chip to reliably monitor the on-chip thermal profile. The general idea is to use the temperature dependent reverse-bias leakage current of a *p-n* diode to monitor the thermal profile of the chip. In this sensor, the diode junction capacitance is first charged to a fixed voltage. Subsequently, the diode capacitance is allowed to self-discharge through its temperature dependent reverse-bias current.

In the first implementation of the sensor in a 32nm Silicon-On-Insulator (SOI) technology, the temperature dependent diode discharge time is measured using a Time-to-Digital Converter (TDC). Finally, a single-bit first-order delta-sigma modulator is implemented in which the self-discharging *p-n* diode is used as the integrator. The temperature dependent reverse-bias current of the *p-n* diode is measured at the output of the modulator with an off-chip digital filter. As the diode reverse-bias current is related to the temperature, so the chip temperature can be extracted if this current is measured accurately. Thus, the accuracy of such a sensor depends on the accuracy of the current measured at the output of the modulator. This implementation was carried out in an 180nm technology. The delta-sigma based sensor is designed with the objective of making it like of a standard cell because of its small size and low power. Hence, it would be very easy to place this standard cell of temperature sensor in the closest proximity of all hot spots. In this implementation, an array of such sensor standard cell is placed on the chip. The goal is to characterize each one of these sensors.

#### 1.2 OUTLINE

Chapter 2 reviews the integrated temperature sensors in the context of their roles in monitoring the on-chip thermal profile of microprocessors with DVFS. The additional role of integrated temperature sensors in managing on-chip power in systems utilizing DVFS is also highlighted in this chapter.

To understand the need for a new approach to integrated temperature sensor design to assist in on-chip thermal and power monitoring, an understanding of existing solutions is required. Chapter 3 studies various temperature sensor design architectures with their merits and demerits.

The design, simulation, and implementation of a sensor with a *p-n* diode in a 32nm SOI CMOS technology are presented in Chapter 4. The post silicon results of this sensor are compared with the existing sensors targeting similar applications.

In order to improve the temperature measurement, we propose a first-order deltasigma architecture-based sensor. An overview and basics of delta-sigma modulation is presented in Chapter 5.

The design, simulation, and implementation of a sensor based on a first-order single-bit delta-sigma modulator are presented in Chapter 6. The architecture of this design uses a reverse-bias *p-n* diode, and it was implemented in an 180nm bulk CMOS technology. Chapter 7 is dedicated to the summary of this dissertation, and future works.

#### **Chapter 2: Integrated Temperature Sensors**

#### 2.1 INTRODUCTION

With the evolution of integrated circuit fabrication, temperature sensors are being integrated on-chip for various applications. Such integrated on-chip temperature sensors are widely used in measurement, instrumentation, and control systems. Research in developing application-specific temperature sensors is currently driven by some key applications. Few examples of such key applications are, monitoring of food, and other perishables with Radio-Frequency Identification (RFID) tags [10]-[13], temperature compensation of Micro-Electro-Mechanical Systems (MEMS) resonators in integrated clock reference chips [14]-[16], and thermal management of large SoCs [17]-[19].

Temperature sensors in RFID tags need to be low-cost, and their power consumption has to be ultra-low. MEMs frequency reference circuits employ temperature compensation based on temperature reading of accurate on-chip temperature sensors. MEMS resonators are designed to provide very accurate clock reference solutions. Thus, high accuracy, and high resolution temperature sensors are needed for MEMs resonators. In the case of on-chip thermal management of large SoCs, the temperature sensors must be able to monitor, and measure the temperature of all possible hot spots in real time. Due to the existence of large thermal gradients across their die, it is important that the temperature sensors reside in the closest proximity of the hot spots to sense, and measure the temperature [17], [20]-[21] accurately. As a result, their physical size must be small enough such that multiple of them can be placed on almost anywhere with little

limitations. Placement of many such small-size temperature sensors can provide better overall system level accuracy. This is despite the fact that small-size sensors are generally less accurate compared to large-size ones. In addition, their power consumption must also be low to limit the overall power budget, and also eliminate measurement inaccuracy due to self-heating.

#### 2.2 TEMPERATURE SENSORS IN MULTI-CORE MICROPROCESSORS

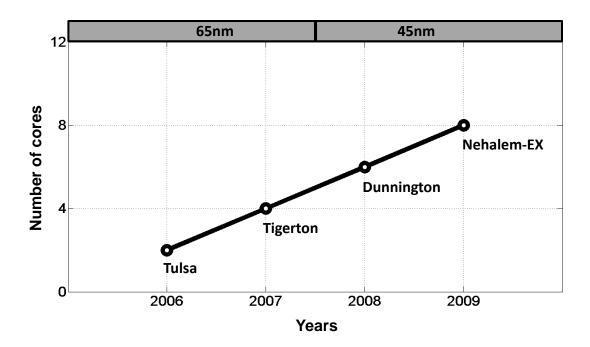

Figure 2.1: Xeon® EX processor core count trend.

In a multi-core microprocessor, multiple central processing units (CPUs) and graphics processing unit (GPU) are integrated onto the same chip. Due to aggressive integration, and technology scaling, the number of cores integrated on the same chip is increasing very fast while the total chip area is also scaling down. As an example, the

core count trend in Intel's Xeon EX processor is shown in Fig. 2.1[22]. It is evident from Fig. 2.1 that the core count per chip is increasing very fast as the technology is scaling down. In a microprocessor each core needs to have temperature sensors. Thus, as the number of cores in a microprocessor is increasing, it requires many sensors to monitor the thermal profile of the entire chip. This also demands that the sensors be very small in size, and their power consumption also be very low.

#### 2.3 SENSORS FOR THERMAL AND POWER MANAGEMENT WITH DVFS

Dynamic voltage and frequency scaling (DVFS) [23]-[25] is a commonly used power management technique where the clock frequency of the processor is decreased to allow a corresponding reduction in the power supply voltage. This reduction of frequency, and supply voltage is typically performed sequentially in multiple steps. During DVFS the (dynamic) power consumption of the processor is significantly reduced which can lead to significant reduction in energy required for a computation. The relationship between dynamic power ( $p_{dynamic}$ ) of a CMOS circuit, power supply voltage, and operating speed (frequency) is [26]

$$p_{dynamic} \propto C_L \cdot V_{DD}^2 \cdot f_{clk}. \tag{2.1}$$

Where,  $V_{DD}$  is the supply voltage,  $C_L$  is the load capacitance, and  $f_{clk}$  is the clock frequency. During the high performance computation the processor temperature can rise significantly due to the high dynamic power dissipation. The high power dissipation has the following disadvantages-

- High power systems tend to run hot, that causes the processor and other system components to fail if no corrective measures like DVFS or cooling (if any) are employed to bring the temperature down. The failure rate of a processor doubles for every 10°C rise in on-chip temperature [27].

- It complicates the cooling solutions of integrated circuits for heat removal, and thus increases the production cost. Intel estimates that more than \$1/W per processor chip will be added once the processor power dissipation exceeds 35-40 W [28].

- It increases the operation costs; such as the electricity bills for air conditioning of the computer, and system rooms. 8% of US electricity in 1998 was attributed to the internet, which is projected to grow to about 30% by 2020 [29].

- It shortens the battery or UPS (Un-interrupted Power Supply) life. The processor power doubles every four years, consequently the average battery or UPS life will be shortened [30].

The major processor manufacture (Intel) has announced that the processor power dissipation doubles every four years [29]. Therefore Dynamic voltage frequency scaling (DVFS) is accepted as a technique to reduce power, and energy consumption of microprocessors by sequentially lowering the supply voltage, and operating speed (frequency). From Equation (2.1) it is evident that lowering the supply voltage is an effective way to reduce the power dissipation because of the quadratic relationship between power, and  $V_{DD}$ . Again, according to Equation (2.1), lowering only the operating frequency  $f_{clk}$  can reduce the power consumption, but the energy consumption remains the same because the computation needs more time to finish. Thus, lowering the supply

voltage, and operating frequency together reduces the power, and energy consumption further.

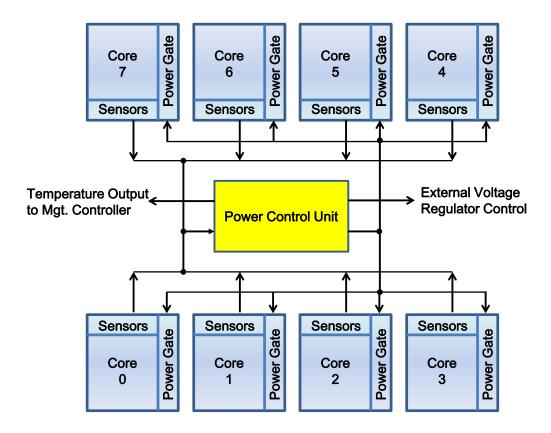

Figure 2.2: An integrated function of power and thermal control unit.

Fig. 2.2 shows an integrated function of power and thermal control units of a multi-core processor where multiple temperature sensors are placed in each core [22]. The temperature information from the sensors is used by the appropriate power and thermal management unit, for example DVFS, within the processor. When the temperature rises to the peak junction temperature of the devices, the sensors throttle the processor which activates the DVFS. The DVFS sequentially reduces the supply voltage, and frequency in steps until the chip cools down to a safe level, and then the processor is

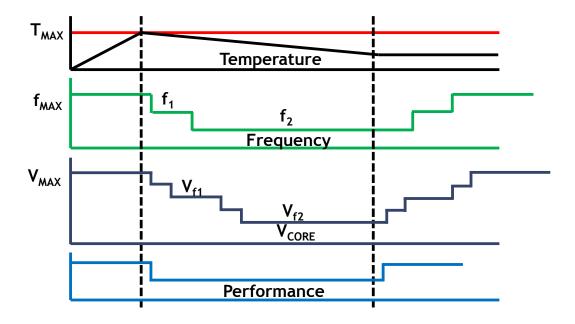

allowed to go into high performance mode again. Fig. 2.3 illustrates the concept of operation of DVFS [22].

Figure 2.3: An Example of DVFS operation to manage on chip power and thermal profile.

If the temperature of the chip rises to some preset level  $(T_{MAX})$  while the chip is operating at some maximum speed  $(F_{MAX})$ , and supply voltage  $(V_{MAX})$ , then DVFS reduces the supply voltage level, and frequency gradually until the chip cools down to a safe temperature level. During DVFS the chips operate at lower performance mode. The example of DVFS operation shown in Fig. 2.3 does not show the details of any label on the axes. The purpose of this figure is to simply show the basic concept of DVFS operation without any detailed and accurate information about the axes.

In multi-core SoCs the temperature information from the sensors is also used to manage the power dissipation by work load shuffling between the cores. When a core temperature rises to a dangerous level, then some of the high performance computational work load from it can be shuffled to another core which is not in a high performance mode at that time. Thus, the temperature sensor plays an important role in work load shuffling which balances the load between the cores of a multi-core processor to minimize the temperature gradient across the chip. This protects the cores from getting hot due to excessive power dissipation resulting from high performance work load.

Thus, the temperature sensors in a large SoC with multiple cores play the crucial role of monitoring, and measuring the on-chip temperature. The power and thermal management unit of the processor uses the temperature readings to activate the DVFS and/or work load shuffling to bring the processor temperature to a safe level. In applications with a built in cooling system (like a cooling fan) the temperature reading from the sensors is used to control the fan.

#### 2.4 DESIGN CHALLENGES IN SUB-MICRON TECHNOLOGIES

Integrating temperature sensors into digital platform faces design challenges due to aggressive scaling. Temperature sensors in computing platforms must be fully integrated in a SoC where vast majority of the circuits are digital. Therefore, the sensors would be using the process technology which is aggressively scaled, and optimized for the digital logic. Analog circuit design in such process faces numerous challenges like reduced voltage headroom, increased transistor leakage, and wider process variations. Such challenges demand extra effort, and time to design analog intensive circuits in sub-

micron technologies, especially in deep submicron technologies. One objective of this research is to shift as much design as possible into the digital domain. This design approach can not only simplify the design task, but it can also reduce the design effort, and time.

Another important aspect of design is portability. That means a design is expected to be robust enough such that it can be ported from one technology node to another with minimum design change, and effort. This is very important for minimizing the time to market a product, and is certainly becoming more and more demanding in developing a product in sub-micron technologies. However, while it is much easier to port digital circuits from one technology node to another, the same is not true for analog circuits. Many design specifications, for example gain, bandwidth, stability of an amplifier, may not just stay the same when an analog circuit is ported to a different technology node. Analog circuits need to be re-designed, and re-simulated thoroughly which requires changes of some or all device sizes, even though the same architecture is used.

The primary target application of the temperature sensor of this research is in the digital platform. Therefore, it is expected that, along with the rest of the digital circuit, the sensor must be ready to port from one technology node to another with very little design change, and effort such that it does not become a road block to time to market. A digital design centric architecture for a temperature sensor would be the perfect choice to achieve this goal. As a result, in addition to small size, and low power consumption, the architecture of the temperature sensor of this research has been chosen to be digital centric.

## Chapter 3: Existing Architectures for On-chip Integrated Temperature Sensors

#### 3.1 INTRODUCTION

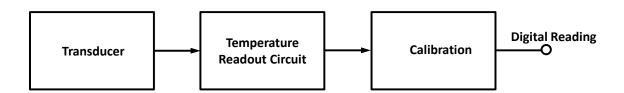

The block diagram of a typical temperature sensor is shown in Fig. 3.1. The temperature sensing circuit (transducer) produces an analog output, generally in the form of an analog voltage, in response to the temperature being sensed. This analog quantity is then converted into digital format through an analog-to-digital converter (ADC). The digital output is further processed and calibrated, if necessary, to produce the final output which represents the temperature being sensed. The detection range and accuracy of a temperature sensor depends greatly on the transducer and the sensing readout circuit which includes the ADC (or quantizer). In this chapter, the previously implemented on-chip integrated temperature sensor topologies are discussed including their achieved performances, merits, and limitations.

Figure 3.1: A Typical Temperature Sensor Architecture.

#### 3.2 ON-CHIP TEMPERATURE SENSOR ARCHITECTURES

Various on-chip temperature-sensing circuit topologies have been proposed and implemented. Most of these systems rely on temperature dependent properties of integrated devices in silicon VLSI technologies as for their transducer component. Examples are MOS transistors, bipolar junction transistors (BJTs), and resistors. As a result, on-chip temperature sensor architectures and topologies are generally categorized based on their transducers. In the following, we review them in more detail.

# 3.2.1 Temperature Sensors with Forward Biased Bipolar Junction Transistors (BJTs)

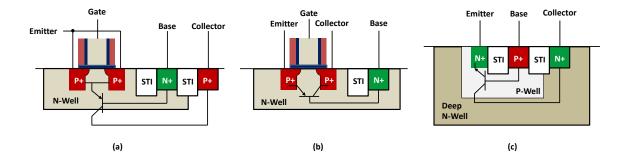

The most widely used architecture for on-chip temperature measurement takes advantage of the proportional-to-absolute-temperature (PTAT) property of the voltage difference between two forward-biased BJTs; a structure which is generally referred to as thermal diodes [31]. In CMOS technology, parasitic BJTs with ratioed currents are commonly used in band-gap circuits to generate a constant reference voltage [32]. The same characteristics can be leveraged to create temperature sensors without requiring any extra fabrication step (or modification) in standard CMOS processes [33]-[35]. The three possible configurations of CMOS BJTs are shown in Fig. 3.2 [17]. The choice between *p-n-p* and *n-p-n* BJT depends on their availability in the process technology. As illustrated, in an NWELL-only CMOS process *p-n-p* BJT is the only choice, and to get an *n-p-n* BJT a triple well process is required.

Figure 3.2: CMOS cross-section of (a) vertical *p-n-p* BJT, (b) lateral *p-n-p* BJT, and (c) vertical *n-p-n* BJT.

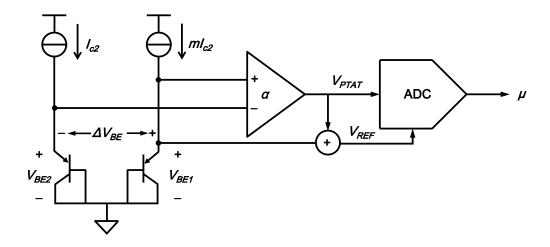

Figure 3.3: Block diagram of a *p-n-p* BJT temperature sensor.

The block diagram of a BJT based temperature sensor is shown in Fig. 3.3 [31]- [35]. A pair of currents with ratio m is used to bias the pair of BJTs having the same emitter area to develop voltages  $V_{BE1}$ ,  $V_{BE2}$ , and  $\Delta V_{BE}$ . The BJT voltages are expressed as

$$V_{BE1} = \frac{\eta kT}{q} \ln \left( \frac{mI_{c2}}{I_s} \right), \tag{3.1}$$

and

$$V_{BE2} = \frac{\eta kT}{q} \ln \left( \frac{l_{c2}}{l_S} \right), \tag{3.2}$$

Where, k is the Boltzmann's constant  $(1.38 \times 10^{-23} \text{ J/}^0\text{K})$ ,  $\eta$  is the diode ideality factor  $(\approx 1.0)$ , T is the absolute temperature in Kelvin, q is the elementary electric charge  $(1.60 \times 10^{-19} \text{ Columb})$ , and  $I_s$  is the diode reverse saturation current.  $I_{c2}$  and  $mI_{c2}$  are the two collector (emitter) biasing currents.

From Equations (3.1) and (3.2) it may appear that the diode base-emitter voltages have positive temperature co-efficient due to the presence of the temperature term T. However, the reverse saturation current  $I_s$  has a strong positive temperature dependency. As a result,  $V_{BE}$  has a negative temperature co-efficient.  $V_{BE}$  changes almost linearly with temperature with a slope of approximately -2 mV/°C. Thus, it is possible to design temperature sensor that utilizes  $V_{BE}$  as an operand. However,  $I_s$  varies with process. The effect of the process variations can be compensated by trimming the bias currents, and thus normalizing the  $(I_c/I_s)$  term in the equation for  $V_{BE}$ . The diode ideality factor,  $\eta$ , is also a process dependent parameter, and it is typically close to unity.

In contrast, the differential voltage between the two base-emitter voltages is independent of the reverse saturation current,  $I_s$ . By combing Equations (3.1) and (3.2)

$$\Delta V_{BE} = V_{BE1} - V_{BE2} = \frac{\eta kT}{q} \ln(m).$$

(3.3)

Which demonstrates that the output voltage,  $\Delta V_{BE}$ , is proportional to the absolute temperature (PTAT), and the current ratio [33]-[35]. Typically, an analog-to-digital converter (ADC) is used to convert this PTAT voltage into digital format. Thus, the

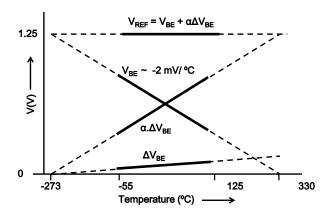

output of the ADC represents the temperature, T. Temperature properties of various voltages of a BJT based sensor is shown in Fig. 3.4 [31].

Figure 3.4: Temperature properties of voltages in a BJT temperature sensor.

The thermal sensitivity of the PTAT voltage  $\Delta V_{BE}$  is very small. For example, for a current ratio of 10, and diode ideality factor  $\eta = 1.0$ ,  $\Delta V_{BE}$  changes by about 200  $\mu$ V for each degree change of temperature. Thus, this type of sensor needs high precision data converter to accurately estimate the temperature. Typically, a switched capacitor based delta-sigma ADC is used in the sensor built with BJTs [31]. Due to the need for high precision, the ADC used in this type of sensors tends to be relatively large and power hungry.

As shown in Figs. 3.3 and 3.4, an appropriate gain factor  $\alpha$  is used to generate a positive temperature dependent voltage  $V_{PTAT}$  ( $\alpha$ .  $\Delta V_{BE}$ ), and a temperature independent reference voltage,  $V_{REF}$ . The delta-sigma ADC acts on these two voltages, and produces a digital output code  $\mu$  which represents the temperature of the circuit. The reference voltage  $V_{REF}$  is approximately equal to the band-gap reference voltage (~ 1.25V).

The accuracy of BJT-based sensors depends on diode ideality factor, and accuracy of the current ratio of the two bias currents. Diode ideality factor is a process dependent parameter. Careful and meticulous layout for good matching alone cannot guarantee the required matching between the individual current mirrors to achieve the desired level of accuracy. Therefore, on-chip dynamic element matching, bias trimming, and post-fabrication calibration techniques are used in this type of sensor to improve accuracy. Any mismatch between the emitter areas of the two diodes contributes to sensor inaccuracy. Typically, bigger physical sizes with multiple unit devices are used to match between the two diodes which increase overall area of the sensor.

The biggest advantage of the BJT based temperature sensors is that the PTAT voltage  $\Delta V_{BE}$  is directly proportional to the temperature being measured. However, for the aforementioned reasons, while this specific class of on-chip temperature sensors tend to be accurate, they have to be large, and power hungry, resulting in reduced benefit from advanced technology (e.g., below 65nm CMOS).

Standalone BJT based temperature sensors have been successfully implemented [36]-[39]. After on-chip trimming and calibration they can achieve  $3\sigma$  inaccuracy of a fraction of a degree of temperature [37]. BJT based temperature sensors have also been implemented in large SoCs, like microprocessor in submicron technologies. The  $3\sigma$  inaccuracy of such sensors can be several degree of temperature [38]-[39].

#### **3.2.2 MOSFET-based Temperature Sensors**

Many physical properties of MOSFETs have temperature dependency. As a result, MOSFET-based temperature sensors have been successfully implemented by utilizing the temperature sensitivities of the various MOSFET physical properties.

The relationship between the drain current and gate to source voltage of a MOSFET operating in sub-threshold region can be expressed as [40]

$$V_{GS} - V_{TH} = \left(\frac{skT}{q}\right) \ln\left(\frac{I_D}{I_0}\right). \tag{3.4}$$

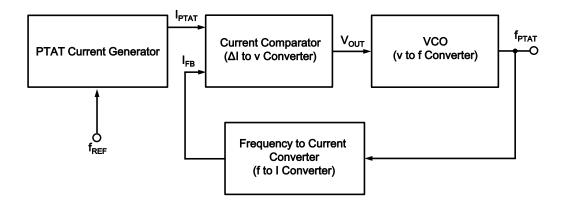

$I_0$  is a process dependent parameter,  $I_D$  is the drain current, and s is the sub-threshold slope factor. A VCO based low-power temperature sensor using MOSFET-based sensing devices operating in sub-threshold mode has been recently proposed as an alternative choices to BJT-based sensors [41].

Figure 3.5: Block diagram of a MOSFET based sensor.

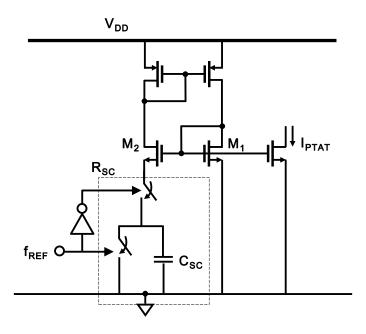

The block diagram of the MOSFET based sensor is shown in Fig. 3.5 [41]. The operation is based on creating a PTAT current, which is a linear function of temperature, using the circuit illustrated in Fig. 3.6. It can be shown that PTAT current of this circuit, denoted by  $I_{PTAT}$ , is [41]

$$I_{PTAT} = \frac{skT}{qR_{SC}} \ln\left(\frac{K_2}{K_1}\right),\tag{3.5}$$

Figure 3.6: The PTAT current generator of the sensor presented in Fig. 3.5.

The resistor  $R_{SC}$  is defined as

$$R_{SC} = \frac{1}{f_{REF} \cdot C_{SC}},\tag{3.6}$$

Using Equations (3.5) and (3.6), finally  $I_{PTAT}$  can be expressed as

$$I_{PTAT} = \left(\frac{skT}{q}\right) \left(f_{REF} \cdot C_{SC}\right) \ln \left(\frac{K_2}{K_1}\right). \tag{3.7}$$

where, s is the sub-threshold slope factor,  $R_{sc}$  is a switch capacitor resistor implemented by using the external clock  $f_{REF}$ , and an on-chip switched capacitor  $C_{SC}$ ,  $K_1$ , and  $K_2$  are the aspect ratio of the transistors  $M_1$  and  $M_2$  respectively operating in sub-threshold.

The external reference clock  $f_{REF}$  of Equation (3.7) is independent of temperature. Thus, in sub-threshold mode  $I_{PTAT}$  is PTAT. The current comparator converts the difference of this  $I_{PTAT}$  current and the feedback current  $I_{FB}$  into a voltage which is used to drive the voltage controlled oscillator (VCO). When the loop is stable and locked,  $I_{PTAT}$  and  $I_{FB}$  become equal, and at that point  $f_{PTAT}$  represents the temperature. After a one temperature point calibration an accuracy of  $\pm 1.8$ °C was obtained over the temperature range of 10°C to 80°C [41].

In another approach, a time-to-digital converter (TDC) based temperature sensor has been implemented in which the time it takes for the MOSFET sub-threshold current to charge a capacitor to a fixed threshold is measured. After an initial batch calibration, a one-point calibration of individual sensors was performed to achieve inaccuracies of a few degrees over the limited temperature range of  $40^{\circ}$ C to  $90^{\circ}$ C [42]. Yet, the size and power consumption of this sensor is too high. The inaccuracy was improved to  $\pm 1^{\circ}$ C after a two-point calibration over the range of  $-10^{\circ}$ C to  $30^{\circ}$ C [43]. An auto-calibrated all digital CMOS temperature sensor has been introduced in [44] that utilizes a TDC to generate the final digital output. This sensor is relatively small, and it consumes less power. However, it operates over the limited temperature range of  $0^{\circ}$ C  $\sim 60^{\circ}$ C with the

measurement error bounded by  $-5.1^{\circ}$ C ~  $3.4^{\circ}$ C. Even with calibrations, these types of sensors are not as accurate as BJT based sensors due to excessive process variations, and their temperate range is also very narrow. They require expensive multi-point calibrations to increase their accuracy.

A dual delay locked loop (DLL) based all digital temperature sensor has been proposed to remove the effects of process variations with calibration at only one temperature point [45]. A reference clock with a multiphase delay line is used to generate a fixed delay to calibrate the temperature measurement errors. Thus, the calibration cost at high volume production can be reduced. However, the temperature sensors with dual DLLs occupy too large chip area and they consume excessive power at milliwatt level.

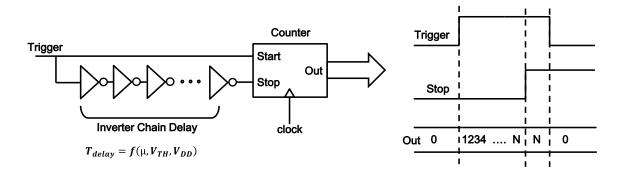

Figure 3.7: Block diagram of a temperature sensor based on the delay of a chain of inverters.

Temperature sensors have also been implemented by using the temperature dependent propagation delay of CMOS inverters. Fig. 3.7 shows the block diagram of

such a sensor [46]. The average propagation delay of a CMOS inverter with equal strengths of PMOS and NMOS devices can be expressed as [46]

$$T_p = \frac{(L/W)C_L}{\mu C_{OX}(V_{DD} - V_{TH})} \ln \left( \frac{3V_{DD} - 4V_{TH}}{V_{DD}} \right). \tag{3.8}$$

Where W and L are the width and length respectively of the PMOS and NMOS devices of the inverter,  $C_{OX}$  is the oxide capacitance, and  $C_L$  is the load capacitance of the inverter. The temperature dependent parameters are the mobility,  $\mu$ , and the threshold voltage  $V_{TH}$ . If the supply voltage  $V_{DD}$  is constant and much bigger than  $V_{TH}$ , then the temperature dependence of  $T_p$  will be mainly determined by the temperature dependence property of mobility. The temperature dependence of mobility is expressed as [46]

$$\mu = \mu_0 \left(\frac{T}{T_0}\right)^{km}.\tag{3.9}$$

In Equation (3.9), T is the actual temperature to be measured,  $T_0$  is a reference temperature, and km is a constant between -1.2 to -2.0. Because mobility has a negative temperature co-efficient as expressed in Equation (3.9), the propagation delay of the inverter in Equation (3.8) has a positive temperature co-efficient.

As evident in Equation (3.8), the propagation delay also varies with the variations of  $V_{DD}$  and  $V_{TH}$ . In addition, the temperature dependency of the mobility is not fixed (km = -1.2 to -2.0). Hence, the propagation delay of an inverter suffers from variations of process and supply voltage. As a result, temperature sensors built with this architecture require multiple temperature point calibration. The temperature sensor implemented

based on inverter delay has achieved inaccuracies of about  $\pm 0.5$ °C over the range from 0°C to 90°C with a fixed supply voltage and after a two-point calibration [47].

In submicron technologies, the propagation delay is expected to vary more over process variations, and the accuracy of this type of sensor would be worse requiring more rigorous calibrations. Thus, though simple in architecture, the actual implementation of MOSFET based sensors would be costly.

#### **3.2.3 Resistor-Based Temperature Sensors**

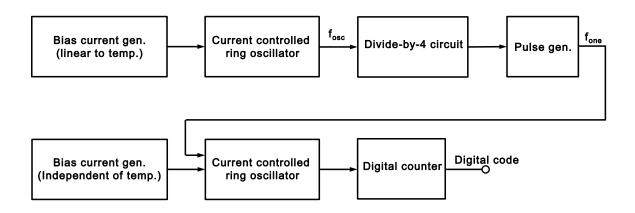

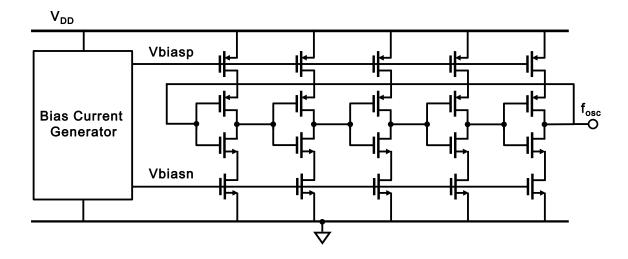

Integrated temperature sensors have been implemented that use on-chip temperature-variant resistor (thermistor) [48]-[51]. In the implementation of [48] illustrated in Fig. 3.8, a temperature-dependent poly resistor is used to generate a temperature-dependent current. A current-controlled (starved) ring oscillator driven by this bias current is then used to produce a digital output representing the on-chip temperature. The bias current generator of the upper part of the sensor, shown in Fig. 3.9(a), uses a poly resistor which varies almost linearly with temperature. The current starved inverter chain based ring oscillator of the sensor shown in Fig. 3.10 produces oscillations ( $f_{osc}$ ) proportional to the bias current  $I_{source}$  ( $I_{sink}$ ) given by [48]

$$f_{osc} = \frac{I_{source}}{NV_{DD}C_L}. (3.10)$$

Where N (=5) is the number of inverters in the ring oscillator,  $C_L$  is the load capacitance seen by the inverters, and  $V_{DD}$  is the power supply. In this implementation,  $I_{source}$  and

$f_{osc}$  vary inversely with temperature. This means, the pulse width (time period) of  $f_{osc}$  is a linear function of temperature.

Figure 3.8: Block diagram of a resistor-based temperature sensor.

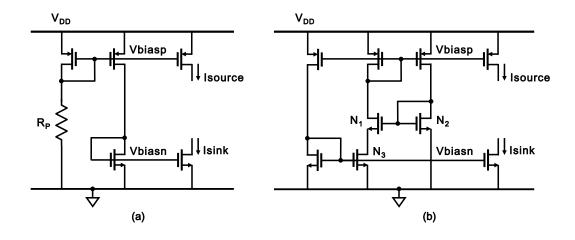

Figure 3.9: Linear to temperature dependent bias current (a) and almost independent of temperature bias current (b).

Figure 3.10: Current starved inverter chain based ring oscillator.

The lower part of the sensor in Fig. 3.8 uses the same ring oscillator as the upper part of the sensor. The temperature independent bias current generator is shown in Fig. 3.9(b). To minimize power, transistors  $N_1$  and  $N_2$  are operated in sub-threshold region, and  $N_3$  is operated in linear region. The divide-by-4 circuit in Fig. 3.8 divides down  $f_{osc}$  by a factor of 4, and the pulse generator of the upper part selects a single cycle pulse  $(f_{one})$  from this low frequency clock. The ring oscillator of the lower part produces a high frequency clock  $(f_{out})$  that is almost temperature independent, but it is activated only during the time interval of the temperature dependent single pulse  $(f_{one})$ . The digital counter counts the temperature independent clocks of the lower ring oscillator during the time interval of the temperature dependent single pulse producing the final digital output corresponding to the on-chip temperature.

Resistor based temperature sensor can achieve relatively good accuracy though they need calibration because on-chip resistor vary with process, and temperature. The physical size of resistor based sensor is high and their power consumption is also high. In another implementation, a thermistor based temperature to digital converter was implemented to provide accurate and low-noise compensation of temperature induced variation of MEMS resonant frequency [51]. The temperature to digital converter included a tunable switched-capacitor resistor, a multi-bit quantizer, a digital delta-sigma modulator, a Phase Locked Loop (PLL). The temperature sensor in this MEMS-based oscillator was the key component to provide temperature stability better than  $\pm 0.5$  ppm over a -40°C to +80°C temperature range. However, this level of high accuracy came at the expense of about 13.1 mW of power consumption at 3.3V supply in 180nm CMOS.

#### 3.2.4 Thermal Diffusivity Sensor

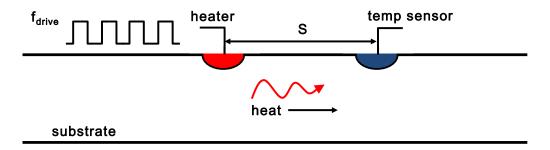

Temperature can also be sensed by measuring the thermal diffusivity of silicon which is strongly temperature-dependent [52]. As shown in Fig. 3.11, a thermal diffusivity sensor is created by realizing a heater and a temperature sensor embedded in the same silicon substrate [52]. Electrical signal ( $f_{drive}$ ) applied to the heater induces local temperature variations in the substrate, through which they diffuse, and after a delay are being detected by the temperature sensor.

Figure 3.11: Cross-section of a thermal diffusivity sensor.

Thermal diffusivity of pure silicon substrate has a strong temperature dependency which is defined as [52]

$$D_{si} \approx \frac{1}{T^{1.8}}.\tag{3.11}$$

In this implementation, the heater is made up with  $n^+$  diffusion resistor, and  $p^+/Al$  ( $p^+$  diffusion and Aluminum) thermopile is used as the temperature sensing circuit inside the sensor. The distributed R-C (resistor and capacitor) of the substrate acts as a low pass filter creating a temperature dependent phase shift of  $f_{drive}$  defined by

$$\emptyset \propto S \sqrt{\frac{f_{drive}}{D_{Si}}} \propto T^{0.9}$$

(3.12)

Where s is the distance (spacing) between the heater and the sensor. The sensor uses a phase digitizer based on a  $\Delta$ - $\Sigma$  modulator to digitize the phase shift and produces the final digital output. Temperature sensors built with this idea [52] reported good accuracy but their size is very big, and they consume too much power.

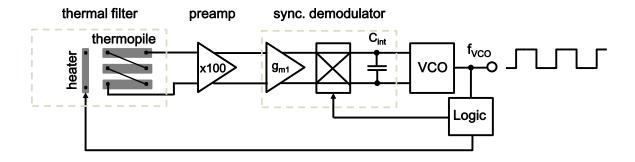

Figure 3.12: Practical implementation of the electro-thermal FLL.

In another implementation, a temperature to frequency converter (TFC) was implemented in which an  $n^+$  diffusion resistor was used as a heater while the temperature sensor was a thermopile realized in  $p^+$  diffusion/aluminum thermocouples [53]. The output frequency is determined by the phase shift of the electro-thermal filter formed by the heater, and the temperature sensor. The filter's phase shift is determined by the geometry of the thermal path between the heater and the sensor, and by the temperature dependent rate at which the heat diffuses through the substrate. The filter was used as the frequency-determining component of a frequency-locked loop (FLL), whose output frequency is then a well-defined function of temperature. Using this approach, a TFC with an inaccuracy of  $\pm 0.5$  C (3 $\sigma$ ) over the industrial temperature range (-40 $^{\circ}$ C to 105 $^{\circ}$ C) has been realized in a standard 0.7  $\mu$ m CMOS process. The practical implementation of this sensor is shown in Fig. 3.12, and it consists of a preamplifier with a gain of 100 [53].

The output of the preamplifier is then applied to a synchronous demodulator consisting of a transconductor,  $g_{m1}$ , a chopper, and an integrating capacitor  $C_{int}$ . Finally the VCO (voltage to frequency converter) produces the final frequency output  $f_{VCO}$ . In the practical implementation, the preamplifer, synchronous demodulator, and two electrothermal filters were implemented on a 2.3 mm<sup>2</sup> chip. The on chip electronics dissipates (excluding the heaters) 2.5mW power from a 5V supply. VCO and the heater driver logic were implemented off-chip [53].

#### 3.3 REMOTE AND DISTRIBUTED ON-CHIP TEMPERATURE SENSING

MOSFET-based sensors typically consume less power, but they depend on the temperature dependent properties of transistor threshold voltage, mobility, and biasing current, all of which vary with the process. Thus, they require calibration at multiple temperature points to achieve the desired level of accuracy. Lightly doped N-well and poly resistors (thermistors) are used in the resistor based sensors. But their temperature dependence is not well defined, and they too require calibration at multiple temperature points to achieve desired accuracy. The size and power consumption of the thermal diffusivity sensor is very high. For these reasons, these sensors are not used in microprocessor applications which need many sensors to be deployed across their chips to monitor the temperature.

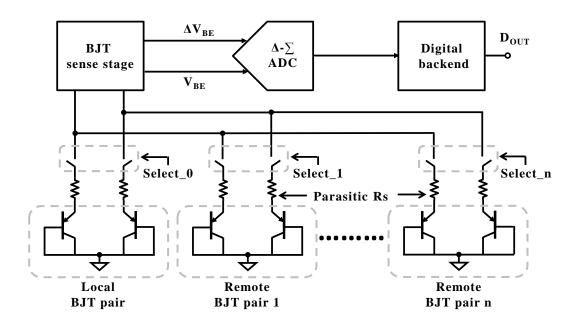

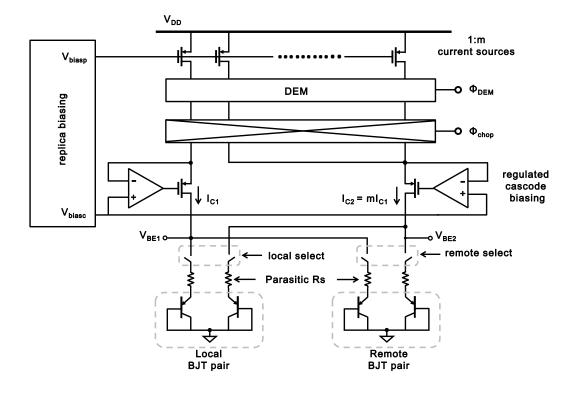

Existing on-chip thermal monitoring solutions for the multi-core processors employ the technique previously presented in Fig. 3.3 using parasitic BJT devices. Fig. 3.13 shows an implementation of an Intel temperature sensor in 32nm bulk CMOS Hi-K metal gate [54], and Fig. 3.14 [54] shows the circuit used to implement the BJT sense stage. Due to large physical size and power consumption of the sensors their placement close to the hot spots becomes very expensive, and prohibitive. As a result, remote sensing is employed by placing the BJTs close to the hot spots, and by placing the  $\Delta$ -  $\Sigma$  ADC based core analog circuit in a less congested region. A pair of forward biased BJTs (remote sensors) is placed close to each hot spot. The BJTs are forward biased with a pair of currents from the central bias generation circuits as shown in Fig. 3.14.

Figure 3.13: Block diagram of a temperature sensor with remote sensing.

The forward biased BJT pair (with a current ratio of say 10) is relatively large in size. The differential voltage  $\Delta V_{BE}$  across the pair of the remote sensor diodes is digitized by the ADC. Typically a delta-sigma ( $\Delta$ - $\Sigma$ ) ADC is used as shown in Fig. 3.13. The ADC in Fig. 3.13 has to measure the voltages ( $V_{BE}$ , and  $\Delta V_{BE}$ ) of all the remote sensors.

Figure 3.14: Circuit inside the BJT sense stage to provide the biasing currents to the sensors.

Due to the long routes between the BJT sense stage and the remote sensors, the sampling of these voltages by the ADC is slower. In addition, the routings between the sense stage and the ADC can also be quite long. The routing of these analog signals must be done very carefully to avoid possible coupling with the digital signals which are common in a microprocessor. The ADC needs to measure all the remote sensors one at a time, thus the temperature readout speed is low. The total area and power of the thermal monitoring utilizing remote sensing are still very high. As a result due to physical size, power, and complexity of remote sensing, the sensors are not optimally placed close to all possible hot spots. Thus, the overall system level performance of thermal monitoring is still under optimized.

#### 3.4 SUMMARY AND CONCLUSION

| Sensor Type               | Area<br>(Size)  | Power         | Accuracy | Design<br>Effort | Limitations / Challenges                                         |

|---------------------------|-----------------|---------------|----------|------------------|------------------------------------------------------------------|

| ВЈТ                       | Large           | High          | Good     | Very<br>High     | Calibration<br>Trimming                                          |

| MOSFET                    | Medium          | Low           | Medium   | High             | Aggressive Calibration Curvature Correction                      |

| Thermistor                | Large           | Medium        | Good     | Medium           | Calibration at multiple temperature points, Curvature Correction |

| Si Thermal<br>Diffusivity | Large           | Very<br>High  | Good     | Very<br>High     | Calibration<br>Trimming                                          |

| Goal of this research     | Ultra-<br>Small | Ultra-<br>Low | Good     | Low              | Calibration, Curvature<br>Correction                             |

Table 3.1: Qualitative comparison of existing thermal sensing solutions

A comparison between the different existing on-chip temperature sensing techniques is presented in Table 3.1. BJT-based sensors are the most widely used sensors as they offer good accuracy, but they require calibrations, trimming, dynamic element matching, and curvature corrections to achieve the desired level of accuracy. As a result, they are large in size and consume more power. Thermistor-based sensors also suffer from large area, and higher power consumption. While MOSFET-based sensors can consume comparatively less power, they are also large in size. Both thermistor and MOSFET-based sensors suffer from process variations, and they require costly calibrations at multiple temperature points to get the required level of accuracy.

Due to process variations, thermistor and MOSFET-based sensors are not used for

integrating into the microprocessor platforms. BJT-based sensors are facing increasing challenges for integration into multi-core processors due to their large size and high power consumption. Thus, there is a need to explore alternative thermal monitoring solutions for today's multi-core processors where temperature sensors can be placed in the closest proximity of all possible hot spots. If these sensors are tiny enough consuming very little power, and providing the final temperature outputs in digital format then they will be the most attractive solutions. They can be distributed across the chip increasing overall accuracy, and redundancy (reliability) of on-chip thermal monitoring. The redundancy is desirable, because if one sensor becomes non-functional or faulty, then the redundant sensor can support temperature measurement. Due to bigger size, and high power consumption of the BJT based sensor, today's multi-core processors cannot afford redundancy in placing extra sensors. Typically, one ADC is used per core to measure the remote sensors in that core, so if this ADC becomes faulty then the thermal monitoring of that core is at risk. This could be avoided if additional ADCs are used as redundant between the cores. However, due to size and power constraints it is very challenging to provide redundancy in today's multi-core processors.

# Chapter 4: An On-Chip Temperature Sensor with a Self-Discharging Diode

#### **4.1 INTRODUCTION**

In this Chapter, the concept of the proposed temperature sensor using self-discharging diodes is presented. In addition, the design, on-chip implementation, and measurement results are presented. The proposed sensor presented here was built in GlobalFoundries 32nm SOI CMOS technology to be incorporated into a microprocessor system having multiple computing (CPUs) and graphics cores.

#### 4.2 SELF-DISCHARGING DIODE TEMPERATURE SENSOR

This section describes the proposed sensor architecture in details. The architecture presented here is a basic architecture based on the idea of implementing a temperature sensor with a reverse-biased p-n junction diode. It is important to recognize that the same idea presented here can be used to develop other kinds of sensor architectures utilizing the temperature dependent reverse-bias current of a p-n junction diode as an operand. For example, Chapter 6 focuses on the implementation of a temperature sensor with a continuous time first-order delta-sigma modulator where the reverse-bias p-n diode acts as a continuous time integrator.

## 4.2.1 Basic Concept and Theory of Operation