Copyright

by

Jing Zeng

2005

# The Dissertation Committee for Jing Zeng certifies that this is the approved version of the following dissertation:

# Improving Timing Verification and Delay Testing Methodologies for IC Designs

| Committee:                   |

|------------------------------|

| T. 1. A. A.1. 1              |

| Jacob A. Abraham, Supervisor |

| Magdy S. Abadir              |

| Anthony P. Ambler            |

| Nur A. Touba                 |

| Martin D. F. Wong            |

# Improving Timing Verification and Delay Testing Methodologies for IC Designs

$\mathbf{b}\mathbf{y}$

Jing Zeng, B.S., M.S.

# **DISSERTATION**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

# DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN  ${\rm May} \ 2005$

Dedicated to my families

- with love and gratitude

# Acknowledgments

This has been the longest journey I have embarked on in my life. Now it is coming to an end. I want to thank everybody in my family for going through all the ups and downs of school, work and life with me. With this journey as a constant backdrop, my life has seen many changes over the years. The most recent change is that I became a mother to my 6 month old son Connor. I want to thank my son for bringing me so much joy with his beautiful, amazing presence during some of my most stressful days. In his own way, Connor encourages me to finish my dissertation so that he could spend more time with his mother. I want to thank my husband Dan for the sacrifice, patience, and loving kindness he showed me during the final finishing of my thesis. I would like to thank my parents for their love for me, for instilling values of the importance of knowledge in me and always encouraging me to strive for the best. I am also grateful to my parents-in-law who are tremendously helpful with Connor and many other things. I thank my sister for wishing me well from Canada.

I am grateful to my supervisor, Prof. Jacob Abraham, for agreeing to supervise my research topics, for offering constructive criticism and helping me to stay the course over the years. I appreciate that Dr. Magdy Abadir, my manager at Freescale Semiconductor, who is also the co-supervisor of my committee, has been an invaluable mentor to me over many years. Dr. Abadir provides a work environment very conducive to research and development. From our technical discussions, many ideas

sprung forth and became part of this thesis. I appreciate other committee members, Prof. Martin D. F. Wong, Prof. Nur Touba and Prof. Tony Ambler for taking the time to read and evaluate this dissertation. A special thanks to Prof. Wong for agreeing to staying on my committee after joining the faculty at University of Illinois at Urbana-Champaign and for his kind words of encouragement.

My friend and lab mate, Rob Sumners, has helped me greatly over the years through his friendship, wisdom, perspective, and technical discussion. I would like to thank Nari, Jayanta and Robin for their help, support and encouragement during this process. I also thank Melanie Gulick, Linda Frost, Debi Prather, Diana Perez, Shirley Watson, Barbara Schleier, Andrew Kieschnick and many other helpful staff members at the ECE department. My journey would not have been possible without their kindness and involvement.

# Improving Timing Verification and Delay Testing Methodologies for IC Designs

| Ρ | ublication No. |  |

|---|----------------|--|

|   |                |  |

Jing Zeng, Ph.D.

The University of Texas at Austin, 2005

Supervisor: Jacob A. Abraham

The task of ensuring the correct temporal behavior of IC designs, both before and after fabrication, is extremely important. It is becoming even more imperative as the demand for performance increases and process technology advances into the deep sub-micron region.

This dissertation tackles the key issues in the timing verification and delay testing methodologies. An efficient methodology is presented to identify false timing paths in the timing verification methodology which utilizes ATPG technique and timing information from an ordered list of timing paths according to the delay information. This dissertation also presents a speed binning methodology which utilizes structural delay tests successfully instead of functional tests. In addition, it establishes a methodology which quantifies the correlation between the timing verification prediction and actual silicon measurement of timing paths. This quantification methodology lays the foundation for further research to study the impact of deep submicron effects on design performance.

# Table of Contents

| Ackno                                                                                   | wledg | ments                                                                   | v   |

|-----------------------------------------------------------------------------------------|-------|-------------------------------------------------------------------------|-----|

| Abstra                                                                                  | ct    |                                                                         | vii |

| List of                                                                                 | Table | es                                                                      | xi  |

| List of                                                                                 | Figu  | res                                                                     | xii |

| Chapte                                                                                  | er 1. | Introduction                                                            | 1   |

| 1.1                                                                                     | Scope | e of the Thesis                                                         | 2   |

| 1.2                                                                                     | Backg | ground and Related Work                                                 | 4   |

|                                                                                         | 1.2.1 | Timing Verification                                                     | 4   |

|                                                                                         |       | 1.2.1.1 Timing Simulation                                               | 5   |

|                                                                                         |       | 1.2.1.2 Timing Analysis                                                 | 5   |

|                                                                                         |       | 1.2.1.3 Statistical Timing Verification                                 | 7   |

|                                                                                         | 1.2.2 | Delay Fault Testing                                                     | 8   |

|                                                                                         |       | 1.2.2.1 Transition Fault Tests                                          | 12  |

|                                                                                         |       | 1.2.2.2 Path Delay Tests                                                | 13  |

|                                                                                         |       | 1.2.2.3 At-Speed Memory BIST Test                                       | 14  |

|                                                                                         |       | 1.2.2.4 BIST for Delay Faults                                           | 17  |

| Chapter 2. Utilizing ATPG Technique and Timing Informtion for False Path Identification |       | a-<br>18                                                                |     |

| 2.1                                                                                     | Envir | conment for False Path Identification                                   | 20  |

| 2.2                                                                                     | Logic | Path Sensitization                                                      | 22  |

|                                                                                         | 2.2.1 | Example Circuit                                                         | 25  |

| 2.3                                                                                     |       | Path Condition: False Path Identification Using Logic Delay Information | 26  |

| 2.4                                                                                     |       | oved False Path Identification Algorithm                                | 34  |

|            | 2.4.1         | Example Circuit                                                      | 35      |

|------------|---------------|----------------------------------------------------------------------|---------|

|            | 2.4.2         | Efficiency of Revised Slow Path Criterion                            | 37      |

|            | 2.4.3         | The Effectiveness and Limitation of Revised Slow Path Criterion      | 39      |

|            | 2.4.4         | Timing Accuracy                                                      | 40      |

| 2.5        | A Mo          | re Efficient Version of the Improved Algorithm                       | 40      |

| 2.6        | Bridg<br>Mode | ing the Gap between the Physical Design and Testing                  | 41      |

| 2.7        | Exper         | rimental Results                                                     | 43      |

| 2.8        | Concl         | usions                                                               | 46      |

| Chapter 3. |               | Correlating Structural Tests with Functional Tests for Speed Binning | s<br>48 |

| 3.1        | Defini        | ition of Speed Binning                                               | 48      |

|            | 3.1.1         | Types of Speed Failures                                              | 49      |

|            | 3.1.2         | Structural Tests for Defect Detection vs Speed Binning               | 50      |

| 3.2        | Differ        | ent Types of Structural Tests                                        | 53      |

|            | 3.2.1         | At-Speed Memory BIST Test                                            | 54      |

|            | 3.2.2         | Transition Fault Tests without Going through Arrays                  | 54      |

|            | 3.2.3         | Transition Fault Tests Going Through Arrays                          | 54      |

|            | 3.2.4         | Path Delay Tests                                                     | 55      |

| 3.3        | Corre         | lating Structural with Functional Frequencies                        | 58      |

|            | 3.3.1         | Sample Module Results                                                | 59      |

|            | 3.3.2         | Wafer Probe Results                                                  | 63      |

|            | 3.3.3         | Validation of Structural Tests                                       | 67      |

| 3.4        |               | lation of Structural with Functional Tests for Speed                 | 68      |

|            | 3.4.1         | Sample Module Results                                                | 69      |

|            |               | Wafer Probe Results                                                  | 72      |

| 3.5        |               | usions                                                               | 73      |

| Chapter 4. |        | Correlation between the Pre-Silicon Path Pre-<br>diction and Post-Silicon Path Measurement    |     |

|------------|--------|-----------------------------------------------------------------------------------------------|-----|

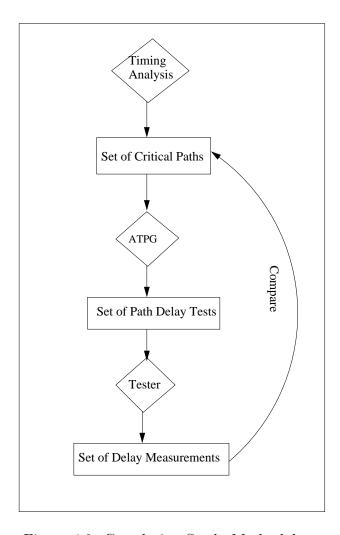

| 4.1        | Meth   | odology for Correlation Study                                                                 | 78  |

| 4.2        |        | the Correlation between the Pre-silicon Path Predicted Post-silicon Path Measurement          | 78  |

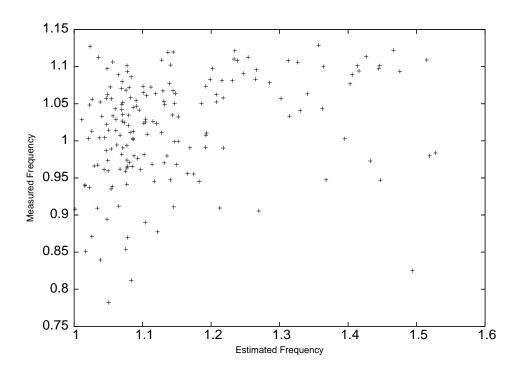

|            | 4.2.1  | Do the Measured and STA Predicted Speed Data Correlate?                                       | 80  |

|            | 4.2.2  | Do the Measured and STA Predicted Path Ranks Correlate?                                       | 81  |

|            | 4.2.3  | What Do the Correlation Distribution between Measured and STA Predicted Path Ranks Look Like? | 85  |

|            | 4.2.4  | Are the Parts with Better Correlation Coefficients Faster Parts?                              | 86  |

| 4.3        | Concl  | usions                                                                                        | 87  |

| Chapt      | er 5.  | Conclusions and Future Research                                                               | 93  |

| 5.1        | Futur  | e Research Directions                                                                         | 93  |

| Bibliog    | graphy | y                                                                                             | 98  |

| Vita       |        |                                                                                               | 108 |

# List of Tables

| 2.1 | Statistics for MPC7455                                                       | 44 |

|-----|------------------------------------------------------------------------------|----|

| 2.2 | False Paths Identified using Different Algorithms                            | 45 |

| 2.3 | Comparison of Algorithms                                                     | 46 |

| 3.1 | Path delay coverage nums                                                     | 59 |

| 3.2 | Speed Binning Results with the Average of the Measured Fmax                  | 73 |

| 3.3 | Speed Binning Results with the Average of the Corresponding Structural Tests | 73 |

| 4.1 | Breakdown of Parts in Different Speed Bins                                   | 87 |

# List of Figures

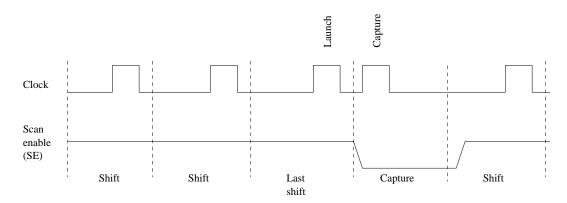

| 1.1  | Launch-off-shift pattern timing                                            | 10 |

|------|----------------------------------------------------------------------------|----|

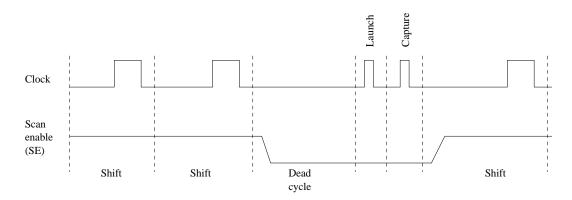

| 1.2  | Broadside-pattern timing                                                   | 11 |

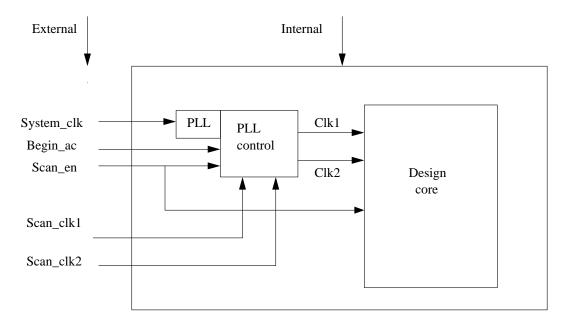

| 1.3  | Phase-Locked Loop (PLL) Clock Generation with Internal and External Clocks | 12 |

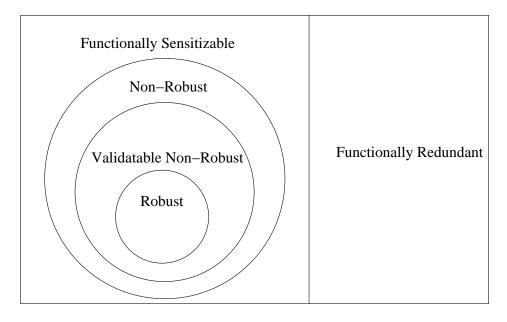

| 1.4  | A Classification of Path Delay Faults                                      | 15 |

| 1.5  | Memory BIST                                                                | 16 |

| 2.1  | Critical Timing Path                                                       | 19 |

| 2.2  | Logic Constraints                                                          | 21 |

| 2.3  | False Path due to Violation of the After Value Criterion .                 | 23 |

| 2.4  | Effect of side-inputs                                                      | 24 |

| 2.5  | Example Circuit                                                            | 26 |

| 2.6  | Logical False Paths: Path $P_1$ , $P_3$ and $P_6$                          | 27 |

| 2.7  | Non-Robust Testable Paths: Path $P_4$ and $P_5$                            | 28 |

| 2.8  | Path $P_2$ : violates $e_n$                                                | 29 |

| 2.9  | Path with Race Condition                                                   | 30 |

| 2.10 | General Multiple Race Condition                                            | 30 |

| 2.11 | Upper Bound Identified for Race Conditions                                 | 33 |

| 2.12 | Algorithm B                                                                | 36 |

| 2.13 | Path $P_2$ and Converging Paths: $P_4$ and $P_5$                           | 37 |

| 2.14 | Algorithm C                                                                | 41 |

|      | Ports of Custom Design Blocks                                              | 42 |

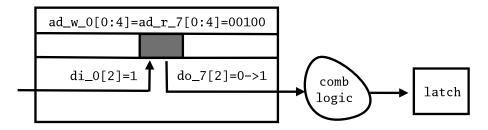

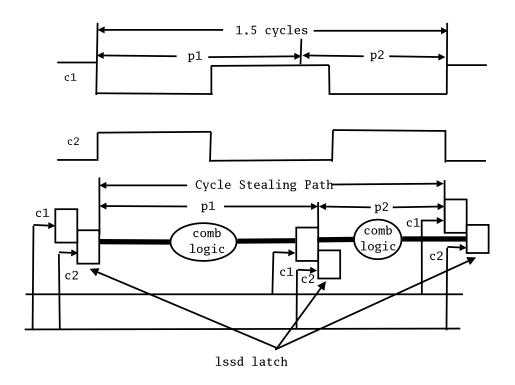

| 3.1  | Memory Path Delay with Transition Launched from Data Output Port           | 56 |

| 3.2  | A Cycle Stealing Path                                                      | 57 |

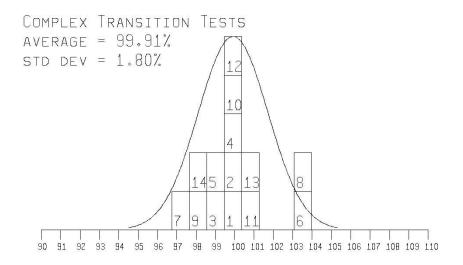

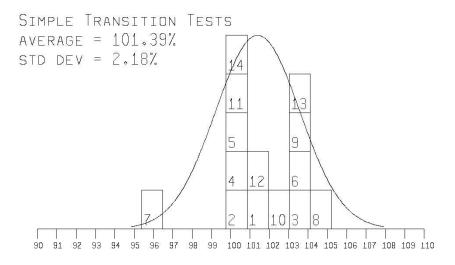

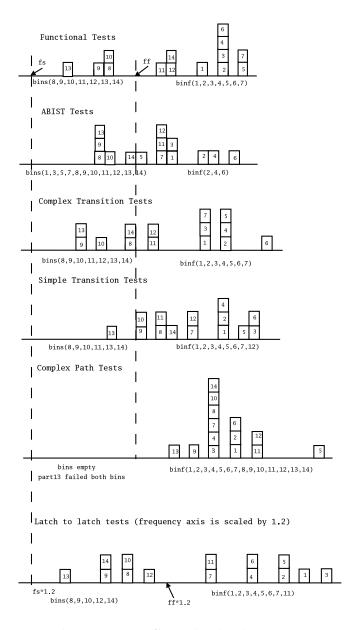

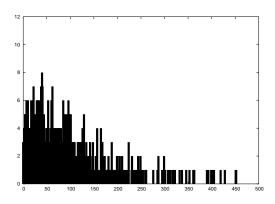

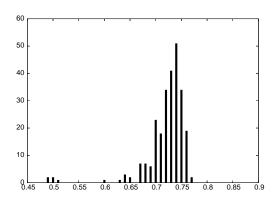

| 3.3  | Transition Test Frequency Distribution                                     | 60 |

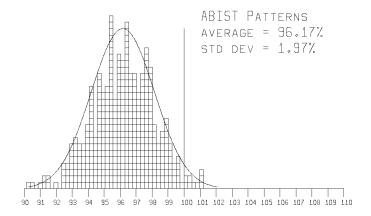

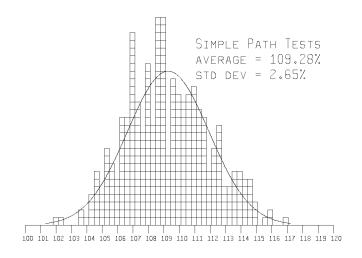

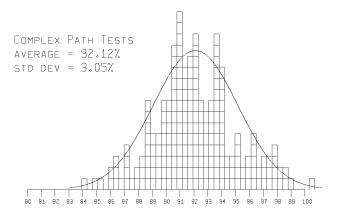

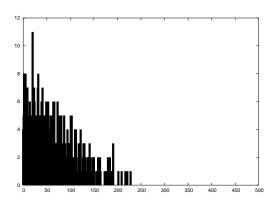

| 3.4  | ABIST Frequency Distribution                                               | 61 |

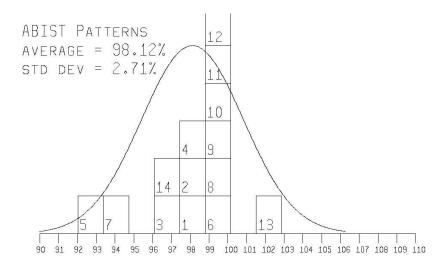

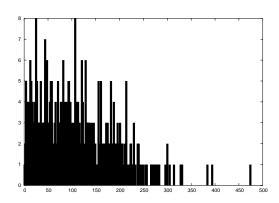

| 3.5  | Path Test Frequency Distribution                                           | 62 |

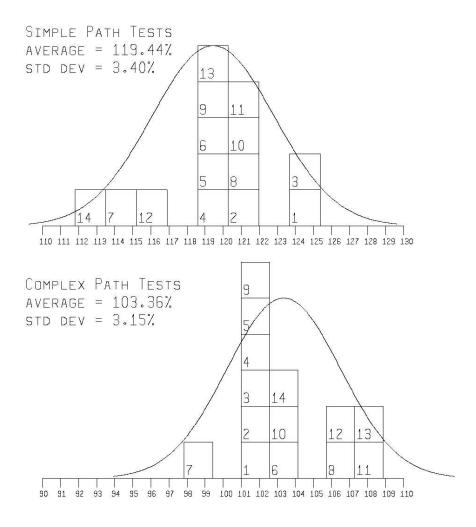

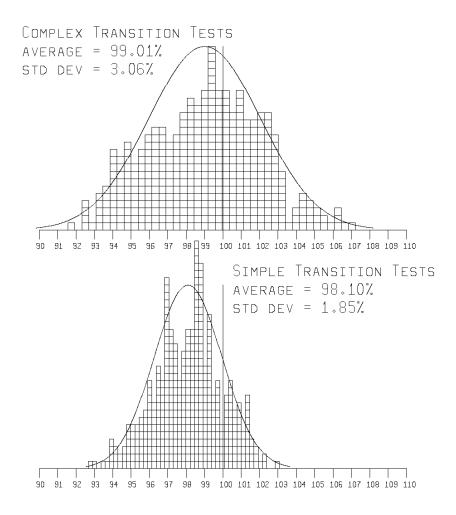

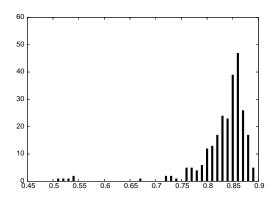

| 3.6  | Transition Test Frequency Distribution                                           | 65 |

|------|----------------------------------------------------------------------------------|----|

| 3.7  | ABIST Frequency Distribution                                                     | 66 |

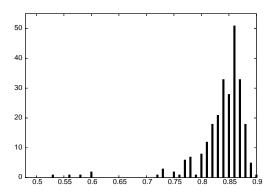

| 3.8  | Simple Path Test Frequency Distribution                                          | 66 |

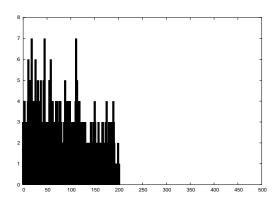

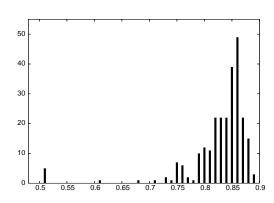

| 3.9  | Complex Path Test Frequency Distribution                                         | 67 |

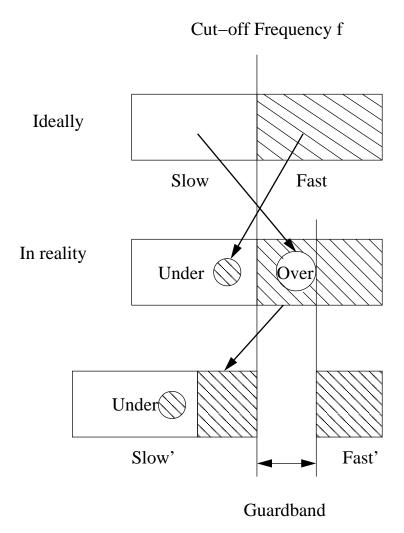

| 3.10 | Illustration of Guardband                                                        | 70 |

| 3.11 | Speed Binning Data                                                               | 75 |

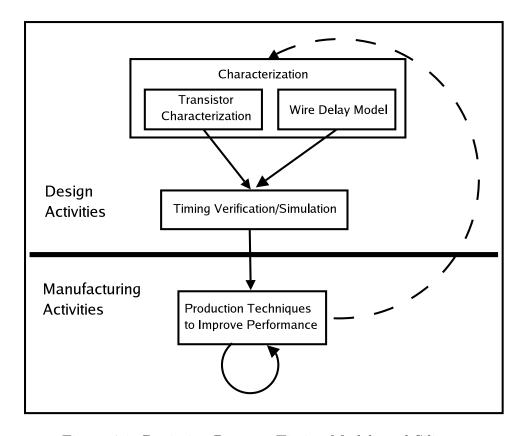

| 4.1  | Deviation Between Timing Models and Silicons                                     | 77 |

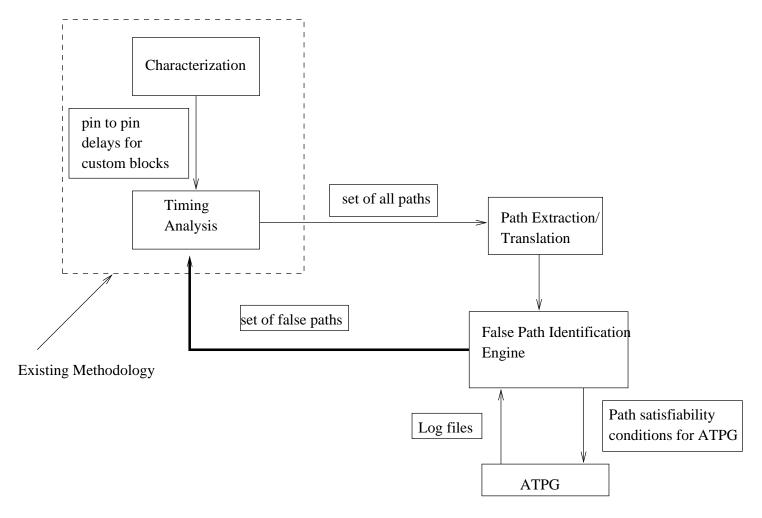

| 4.2  | Correlation Study Methodology                                                    | 79 |

| 4.3  | Correlation between Measured and STA Predicted Speed Data                        | 81 |

| 4.4  | Histogram of Rank Differences for Part 1                                         | 84 |

| 4.5  | Histogram of Rank Differences for Part 2                                         | 88 |

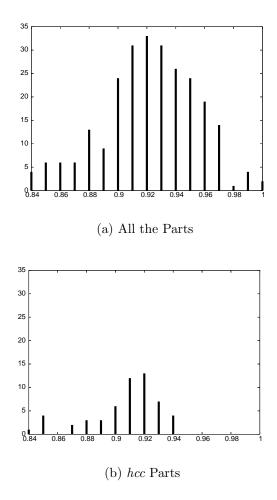

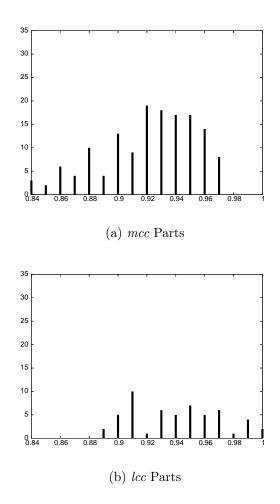

| 4.6  | Histogram of Concordance Coefficients for the Delay Paths (Voltage: $v_1$ )      | 89 |

| 4.7  | Histogram of Concordance Coefficients for the Delay Paths (Voltage: $v_0, v_2$ ) | 90 |

| 4.8  | Histogram of Parts in Normalized Functional Frequency Bins                       | 91 |

| 4.9  | Histogram of Parts in Normalized Functional Frequency Bins                       | 92 |

| 5.1  | New Static Timing Verification Methodology                                       | 97 |

# Chapter 1

# Introduction

High performance Very Large Scale Integration (VLSI) circuits are characterized by high complexity and large variations in component delays. They are also required to operate at increasingly high clock speeds which do not allow for much design margin. In such a scenario, it is imperative and more challenging to ensure the correct operation of such circuits within the allowed timing constraints.

Timing verification refers to pre-fabrication verification of the temporal behavior of a design database. Delay testing, on the other hand, refers to post-fabrication timing verification which subjects each chip to functional or structural test vectors at the rated clock speed.

Timing analysis is at the core of the timing verification and delay testing methodologies. The objective of timing analysis is to improve the accuracy of critical path identification in a design cycle. For testing, timing analysis improves the selection of critical paths for delay test generation. This goal of testing is important as it guarantees that the device fully meets customer performance expectations.

# 1.1 Scope of the Thesis

We first describe the problems that are being addressed in this thesis, then define the scope of the thesis.

#### • False Path Identification

In industry, static timing analysis or structural timing analysis (STA) is the dominating approach in the design methodology to guarantee that the chip design meets the specified clock frequency before the actual fabrication. This structural approach can be very efficient. It scales well with complex, high performance circuits.

The downside of STA is that a transition is assumed to propagate along a path without verifying that there is indeed some pattern of input stimuli that could sensitize the path. A path is considered sensitizable if a transition at the head of the path (launch point) can be propagated to the tail of the path (capture point). The transition may not be sensitized due to unsatisfiable logic conditions. This is the false path problem with the structural analysis [21]. The false path problem could result in a large percentage of identified paths being unsensitizable.

## • Speed Binning Utilizing Structural Tests

Speed binning is used to sort working ICs based on their performances and to assign them to appropriate price points. The use of functional vectors has been an industry standard for speed binning of high-performance ICs. This practice can be prohibitively expensive as ICs become faster and more complex. In comparison, structural patterns

target performance related faults in a more systematic manner, which makes structural testing an attractive alternative for speed binning.

## • Pre-silicon and Post-silicon Timing Path Correlation

The lack of correlation between pre-silicon prediction and post-silicon measurement of timing paths highlights the disconnect between the design methodology and silicon bring-up efforts. During pre-silicon timing verification, a set of critical timing paths,  $S_1$ , is identified. Engineering efforts are then spent optimizing  $S_1$ . During the post-silicon phase, often a different set of critical timing paths  $S_2$ , which gates the speed of the silicons, is identified. Trade-offs of power and area to speed up timing paths in  $S_1$  during optimization do not necessarily translate into speed-up for timing paths in  $S_2$ , which gate the performance of the actual silicons. This is caused by process variations, power noise, crosstalk, thermal effects etc., [24] [27][56], and also sometimes certain design practice contributes to the situation as will be described in Chapter 4.

To tackle the above listed problems, the principal contributions of this thesis are detailed below.

- Efficient utilization of automatic test pattern generation (ATPG) technique and timing information for false path identification in the timing verification methodology.

- Replacing functional tests with structural tests for speed binning.

Quantification of the correlation between the pre-silicon predictions and post-silicon measurements of timing paths.

Before we discuss the specifics of the research of this thesis, we describe the background and related work on timing verification and delay testing.

# 1.2 Background and Related Work

## 1.2.1 Timing Verification

Timing verification determines the maximum delay of the circuit under some given component delay model. It also reports the critical timing paths with the maximum delay in the circuit. A critical (timing) path is a path in a circuit, which due to its cumulative delay, limits the operation of the circuit at the desired speed [73]. This critical (timing) path information can be used to decrease the delay of the circuit during performance optimization if the circuit violates some timing constraints. The terms timing paths and paths will be used interchangeably in this thesis.

The problem under investigation is the determination of the maximum delay at which the sequential circuit can be clocked, given the individual component delays, set-up and hold constraints, clock skews, etc. It has been generally carried out in two phases: determining the delays of the combinational blocks of the circuits, then calculating the minimum feasible clock period of the whole circuit.

To determine the delay of a combinational logic block, there are two broad categories of techniques [73]: timing simulation (also called dynamic timing verification) and timing analysis.

#### 1.2.1.1 Timing Simulation

The timing simulation approach simulates the logic functions on each gate and propagates signals through the gates based on the gate functions and the signal delays. This approach relies on input patterns which are impossible to generate for all of the paths since the number of paths can be exponential with respect to the number of inputs. Accurate gate delay estimation depends on many factors from the gate-specific capacitance and slew rate to factors like voltage, temperature and process variations [55]. It is also prohibitively expensive to perform delay simulation of paths at the chip-level. Due to the above reasons, timing simulation is generally used for detailed timing characterization for library cells and custom designed circuits.

#### 1.2.1.2 Timing Analysis

Structural timing analysis obtains bounds on the maximum delay of a circuit by analyzing the topological structures. To estimate the delay of timing paths in a circuit, certain assumptions of gate delay models need to be made. The simplistic gate delay model is the fixed delay model, where the delay of each gate is assigned a single delay value. A bounded delay model assumes that each gate delay can vary independently of each other in a range [22]. More refined delay models take into consideration that the delay may depend on the fanout [60][62], or on the transition propagated through the gate (rising or falling) [67][74]. In [12], authors present a delay model that includes gate inertia, i.e., the impulse at an input must be

long enough to change the value at the output of a gate. In [63], authors take into consideration electrical phenomena at the transistor-level and determine the gate delay based on values and transitions at nodes that do not belong to the path, or that are visible only at the transistor-level.

Structural timing analysis attempts to efficiently process the exponential number of timing paths in the circuit using linear structural algorithms which do not take into consideration the circuit functionality. It is generally used iteratively to allow the timing issues with a certain number of critical timing paths fixed before it is run again to generate another set of critical paths. Unfortunately, not all the timing paths identified using such analysis can be sensitized since functional information of the circuit is not taken into consideration. The cost of optimization and iteration is expensive without any performance improvement when spent on optimizing unsensitizable paths. It leads to underestimation of the circuit speed, and becomes worse as the demand for the higher performance circuits grows. An unsensitizable critical timing path becomes a bottle-neck to time-to-market and translates into trading power and area for a perceived but nonexistent performance gain.

There has also been much work on sensitization criteria and algorithms to find the maximum circuit delay. Benkoski et al. [6] have proposed a static path sensitization criterion. A *viable* criterion is defined in [54] where the side-inputs of the path under consideration either settle to non-controlling values or terminate a viable path under the test with larger (or equal) delay. In [15], authors have defined conditions for *vigorous* sensitization of a path.

In industry, designers perform timing analysis to find the frequency

at which the design should work correctly after manufacturing. Timing analysis requires information about a design's logic gate and interconnect delays. For a design using standard cell libraries, the library description provides information about logic gate delays. For custom-designed logic, a thorough circuit simulation provides the logic gate delays. Interconnect delays are either estimated from the interconnect's dimensions (leading to an estimate of the associated resistance and capacitance), or the resistance and capacitance values are extracted from the design layout with extraction tools. Because a design must operate over a range of voltages and temperatures, and component delays vary with the operating voltage and temperature, timing analysis is usually performed at various temperature and voltage corners.

## 1.2.1.3 Statistical Timing Verification

As CMOS technologies continue to evolve and advance and minimum feature sizes continue to decrease, circuit timing reflects many important effects such as process variations, power noise, crosstalk, thermal effects, etc. These effects are hard to predict and model deterministically. Statistical timing analysis and timing simulation approaches attempt to better handle the deep sub-micron timing effects [2][9][45][46][49][56][59].

In the statistical approach, instead of fixed delays, delay variables with correlated variations among themselves, will be used to produce a statistical distribution, rather than best-case and worst-case models. This approach attempts to predict the percentage of circuits that will run at a given speed, while allowing the adjustment of timing criteria to reach the acceptable mix of yield vs performance for a given IC design.

Statistical timing verification is not the focus of this thesis.

## 1.2.2 Delay Fault Testing

At 0.13 micron and below, IC manufactures are starting to see more defects that are not caught by traditional stuck-at fault testing [3]. Defects like high impedance metal, high impedance shorts and crosstalk are not caught by traditional stuck-at tests. Instead they show up as timing failures that can only be caught by at speed testing. These defects are called timing defects, compared to logic defects which cause the failures of the circuit functionality. One study on a microprocessor design shows that if scanbased at-speed tests were removed from the test program, the escape rate went up nearly 3% [71]. Another study carried out at Standford University showed that, for 0.7 and 0.35 micron technology respectively, the detection of 30% to 35% of defective parts of circuits designed with standard cells depended on at-speed tests. Also 3 out of 116 defective parts would be missed when tested at slower than the expected operating speed at normal operating voltage [78].

The two at-speed fault models most widely used today include the path delay model and the gate fault model [18][32][33][34][67]. Path delay tests target faults which model manufacturing defects or process problems that can cause cumulative delays along the design's critical paths. Gate fault tests target faults which model manufacturing defects at the inputs and output of a gate. Under the gross delay fault model, a gate fault can be detected along any path, while under the small gate fault model, faults of different sizes are detected along different paths. Research has been done to propagate transitions along the longest paths [35][60]. A comparison

between the gate fault model and the path fault model is presented in [38]. Other at-speed fault models include segment delay fault [29][30].

At-speed path delay or gate fault tests require test patterns with two parts. The first part launches a logic transition value along a path, and the second part captures the response at a specified time determined by the system clock speed. If the captured response indicates that the logic involved did not transition as expected during the cycle time, the path fails the test and is considered to be defective.

Two types of scan methods can be used for at-speed testing: launchoff-shift and broadside [44]. In the launch-off-shift method (Fig. 1.1), the last shift of the scan chain load also launches the transition event. The critical timing is the time from the last shift (or launch) clock to the capture clock. The figure also shows the launch clock is skewed so that it is late in its cycle, and the capture clock is skewed so that is is early in its cycle. This skewing creates a higher launch-to-capture clock frequency than the standard shift clock frequency. The main advantage of launch-off-shift method is that it only requires the ATPG tool to create combinational patterns, which are quicker and easier to generate. The main disadvantage (for mux-DFF designs) is that it imposes restrictions on the routing of the SE signal. The SE signal must switch from 1 to 0 very quickly, because after the second pattern (a shifted version of the first pattern) appears at the flip-flop outputs, the tester must capture the circuit response in a time equal to the system clock cycle time. One way to meet this requirement is to route the SE signal as a clock tree. However, routing another highspeed signal with clock-like accuracy, in addition to the clocks required for system operation, can be expensive. An alternative is to use a pipelined

Figure 1.1: Launch-off-shift pattern timing

approach for SE signal distribution. Also the nonfunctional logic related to operating SE at a high frequency can contribute to yield loss. Another downside is that it could detect non-functional delay faults and scan chain shifting is usually done at lower frequencies.

In the broadside method (Fig.1.2), the entire scan data shifting can be done at slow speeds in test mode, and then two at-speed clocks are pulsed for launch and capture in functional mode. Once the values are captured, the data can be shifted out slowly in test mode. This method also allows using the late and early skewing of the launch and capture clocks within their cycles. The main advantage of this broadside approach is that the timing of the SE transition is no longer critical, because the launch and capture clock pulses occur in functional mode. Adding extra dead cycles after the last shift can give the SE additional time to settle. Another advantage of broadside approach is that it does not require scan chains to shift at-speed. From the design point of view, this makes broadside method simpler to implement. The ATPG problem is now sequential, as a result more faults can be detected in functional mode. The downside is

Figure 1.2: Broadside-pattern timing

that the test generation time can be longer and a higher pattern count might result. In this thesis, we use broadside scan method to apply our at-speed tests.

There are two main sources for the at-speed test clocks for test application: external ATE and on-chip clocks. Traditionally, ATE has always supplied the test clocks. However, the cost of the tester increases as the clocking speeds and accuracy requirements rise. The second source of clocks come from inside the chip itself. An IC design includes a phase-locked loop (PLL) or other on-chip clock generating circuitry. Because the purpose of a delay test is to verify that the circuitry can operate at a specified clock speed, it makes sense to use the actual on-chip functional clocks. On-chip functional clocks are not only more accurate, but also avoid the problem of importing high-speed clock signals into the device. In this scenario, the tester provides the slower test shift clocks and control signals, and the programmable on-chip clock circuitry provides the at-speed launch and capture clocks. Using these functional clocks reduces the ATE requirements, enabling the use of a less expensive tester. An example of

Figure 1.3: Phase-Locked Loop (PLL) Clock Generation with Internal and External Clocks

a programmable PLL is shown in Fig.1.3, combinations of system clock  $(System\_clk)$  and scan clocks  $(Scan\_clk1$  and  $Scan\_clk2)$  are used to generate the internal clock signals feeding to the design core (Clk1 and Clk2).

#### 1.2.2.1 Transition Fault Tests

Transition faults include slow-to-rise or slow-to-fall faults placed at the inputs and output of each gate. The number of transition faults in a design scales linearly with the size of the design. In order to detect a transition fault, an ATPG tool operates under the gross delay fault assumption and does not necessarily travel the longest path which limits the maximum operating frequency. So in general, a transition test may not always expose a small delay fault along a critical path. As a result, in a fixed-cycle testing scheme, a good portion of the transition tests are not suitable for delay defect testing if the paths being tested are too short compared to the functional cycle time. There have been many research attempts to overcome this problem [35][60][79].

# 1.2.2.2 Path Delay Tests

The path delay fault model concerns itself with propagation delays along one or more paths exceeding the timing constraint. A path is said to have a delay fault if the delay of the path is greater then the given timing constraint, and this excess delay is the size of the path delay fault. This model does not try to assign the excess delay to any sub-path or point-to-point connection. It also makes no assumption about the individual component delays. Path delay fault model is general enough to include the gate delay fault model.

An often-cited hurdle for path-delay testing is the large number of paths that a combinational circuit can have. In [65], it is shown that the number of paths can be an exponential function of gates. For example, the benchmark circuit c6288 [10] is known is have 1.98 x 10<sup>20</sup> paths [73]. To contain the so-called path explosion problem in path delay testing, several criteria for selecting paths have been proposed. In [43], an algorithm is given that identifies a set of paths including the longest delay path through every net. Realizing that some selected paths may be untestable, authors generate tests for longest delay testable paths through all the nets [60]. Vigorous path sensitization criteria are developed where the timing of side inputs of delay paths are taken into consideration [15].

There are different types of path delay tests. Some of the path delay

tests are called *robust* tests [17][67]. A robust test is supposed to detect a delay fault it targets regardless of the presence of other delay faults in the circuit under test. A non-robust test [17][67] is guaranteed to detect the fault it targets only if no other delay faults affect the circuit. Since non-robust tests are prone to fault masking, test generation procedures select robust tests (e.g., [14][50][53][60][64][66]). A non-robust test for a path will still be valid if we can guarantee that the side-paths which can invalidate the test are delay fault-free. Such a non-robust test is called a *validatable non-robust testable*. It has been shown that up to 43% of the paths in the ISCAS85 benchmark circuits are not even non-robustly testable [17]. Considerable work has been done to classify these remaining non-robustly testable paths based on delay fault testability. One such classification is shown in Fig. 1.4.

The set of path delay faults in a circuit can be divided into those that are functionally sensitizable and those that are functionally redundant. A non-robust untestable delay fault can still affect the timing of a circuit if it may be sensitized along with other non-robust untestable delay faults. These delay faults are considered functionally sensitizable [17], or multiply-testable [26]. Functionally redundant path delay faults correspond to those paths that cannot be sensitized for any combination of component delay values.

# 1.2.2.3 At-Speed Memory BIST Test

Testing of on-chip memories requires delivery of a huge number of pattern stimuli to the memory and the readout of an enormous amount of cell information [11]. As the number of memory bits per chip continues

Figure 1.4: A Classification of Path Delay Faults

to increase exponentially and fault sensitivity increases, memory faults become more complex. As a result, applying any memory testing algorithm of complexity higher than O(n) becomes prohibitively expensive [11].

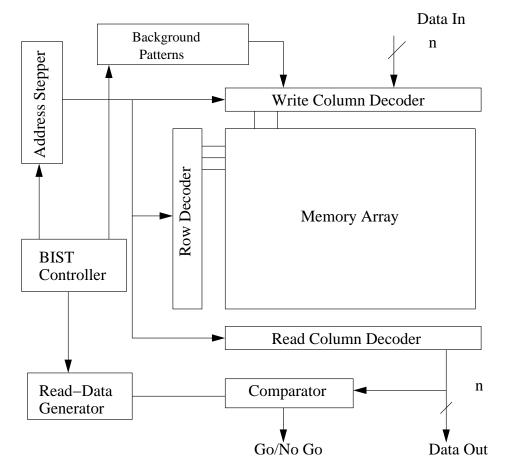

With memory BIST, the entire memory testing algorithm is implemented on-chip, and operates at the speed of the circuit, which is 2 to 3 orders of magnitude faster than a conventional memory test [28]. The following test hardware is needed for memory BIST (Fig. 1.5):

- A memory BIST controller.

- An Address decoder.

- A MUX circuit feeding the memory during self-test from the controller.

- A *comparator* for response checking.

Figure 1.5: Memory BIST

• A Background Pattern inserter or Data Generator for inserting test patterns into memory columns.

If memory BIST related logic is conditioned to run at functional speed, memory BIST can be used to catch timing related faults inside the memories. This is especially important for high performance ICs in which the custom designed memories gate the frequency.

#### 1.2.2.4 BIST for Delay Faults

It is also possible to test circuits for timing delays using BIST [11]. A delay fault BIST testing system has the standard BIST architecture, but with a hybrid pattern generator optimized to test both stuck-at faults and delay faults. While pseudo-random vectors provide good coverage of stuck-at faults, they can also cover a large percentage of transition faults if applied at high speed. Coverage of path delay faults frequently requires additional circuit modifications. When pseudo-random patterns are applied to the circuit, some long combinational paths that are non-functional in the sequential mode can be activated. When this happens, BIST can produce timing failures even in a circuit that meets the functional timing requirements. In such cases, the clock rate of BIST should be lowered below the specification. A suitable clock rate can be found by timing simulation. The power consumption of at-speed BIST can exceed the power rating of the chip. This is because of the high signal activity that random vectors cause in some circuits. Both peak and average power for BIST should be analyzed and corrected. BIST for delay faults technique is not the focus of this thesis.

# Chapter 2

# Utilizing ATPG Technique and Timing Information for False Path Identification

In this chapter, false path identification (FPI) techniques are discussed. First we have the following definitions.

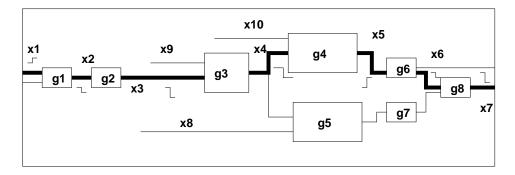

A **critical** timing path (P) is characterized by a set of n nodes  $x_1, x_2, \ldots, x_n$  and a set,  $T = \{t_1, t_2, \ldots, t_n\}$ , of signal transitions such that  $t_i \in T$  represents the logic value transition on  $x_i$ . Node  $x_i$  is called a **path** input for path P. Many of these path inputs are associated with gate devices  $g_i$  of path P which can have other inputs which are called **side** inputs. The transition  $t_i$  of each node  $x_i$  is characterized by a pair of booleans  $\langle b_i, a_i \rangle$  where  $b_i$  and  $a_i$  are the initial (or **b**efore) and final (or **a**fter) boolean values at node  $x_i$ , respectively.  $b_i$  and  $a_i$  are always complementary to each other, since we are concerned with the signal transition on every node along the path.  $\{b_1, b_2, \ldots, b_n\}$  is called the Before set and  $\{a_1, a_2, \ldots, a_n\}$  is called the After set. The time frame associated with the application of the before set is considered the **previous time frame**, while that associated with the application of the after set is the **current** time frame.

In Fig. 2.1, there are 8 library cells and/or custom macros in the circuits, path inputs  $x_1, x_2, ..., x_7$  of gates  $g_1, g_2, ..., g_8$ , go through transi-

Figure 2.1: Critical Timing Path

tions < 0, 1 >, < 1, 0 >, < 1, 0 >, < 1, 0 >, < 0, 1 >, < 1, 0 > and < 1, 0 >. Gates  $g_i$  can have other inputs like  $x_9$  for gate  $g_3$ ,  $x_{10}$  for gate  $g_4$  which are side inputs of the bold-faced path in the figure.

Definition: a false path is a path along which a specified logic transition cannot be sensitized.

Timing paths identified using structural timing analysis are considered to start from the **launch point** and end at the **capture point**. Each node  $x_i$  is either the primary input or output of a sequential element, library component or custom macro.  $x_i$  depends combinationally upon a set of sequential elements and primary inputs. Timing paths with outputs of sequential elements as their launch points and inputs of sequential elements as their capture points are called **latch to latch timing paths**.

Timing paths are generally listed in the timing reports based on their timing slacks. **Timing slack** is defined as the required arrival time minus the actual arrival time at a capture point of a timing paths. Static timing analysis can be configured to run so that only the single worst case timing path is generated for each capture point in the circuit. These paths are called **main paths**. Main paths can be ordered based on their timing slacks at the capture points with the path with the worst slack showing up first in the report.

Besides the main path for a particular capture point, paths converging to the same capture point, with differences in timing slacks from that of the main path within a given threshold can be generated. These paths are called **subpaths**. Subpaths and their corresponding main path form a group of **converging paths**.

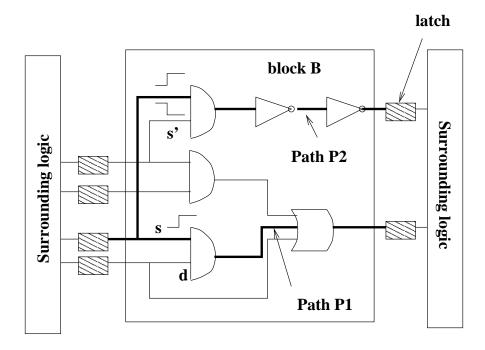

### 2.1 Environment for False Path Identification

Certain assumptions need to be made about the environmental condition of a logic block before analyzing the stand-alone operation of such a block. Such assumptions include the range and arrival of primary input vectors to the block. A single-stepping transition mode of operation [22][23] is used where all circuit nodes are assumed to have stabilized to their final values under the first input vector before a second primary input vector is applied. This reflects the assumption that the block of interest is embedded in a scan latch/flip-flop based synchronous sequential system (Fig. 2.2). In this setting, a particular timing path could be false due to the following.

- local constraints: logic constraints of the block containing the path,

- external/environmental constraints: constraints imposed by the logic feeding the latches which surround the block containing the path.

Figure 2.2: Logic Constraints

As shown in Fig. 2.2, paths  $P_1$  and  $P_2$  are two timing paths under consideration. Designs built with a test methodology which inserts scan latches between a block and its surrounding logic are considered. The latches are illustrated using shaded boxes in the figure. We can see the following.

- Path  $P_1$  is false since d feeds into both the and and or gates. It violates  $local \ constraints$ .

- Path  $P_2$  is false and violates external constraints if s and s' are constrained by the surrounding logic to be one-hot.

In general, in a System On Chip (SOC) setting, block B can be a processor itself or a peripheral device. Currently the analysis is restricted to local

constraints within combinational blocks. An enhanced scan latch/flip flop based environment is further assumed, where an arbitrary vector pair can be applied to the combinational portion of a sequential circuit. With this assumption, we are being conservative in identifying false paths.

# 2.2 Logic Path Sensitization

In order to check whether a transition can be sensitized through a path P, we need to check if every  $x_i$  on the path can take up the values  $b_i$  as well as  $a_i$ , which is equivalent to checking the satisfiability of the following Boolean functions.

- $e_a$  = True iff for all i,  $x_i = a_i$  can be justified simultaneously when evaluated in the current time frame,

- $e_b$  = True iff for all i,  $x_i = b_i$  can be justified simultaneously when evaluated in the previous time frame.

The subscripts in the above terms  $e_a$ ,  $e_b$  help to indicate the evaluation of different criteria. We call the boolean function which checks the satisfiability of all the  $a_i$ s the after value criterion, while the corresponding one for  $b_i$ s the **b**efore value criterion.

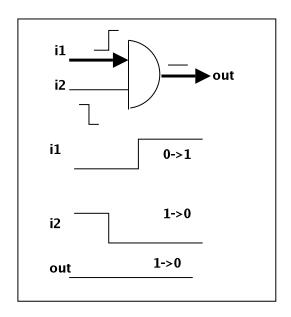

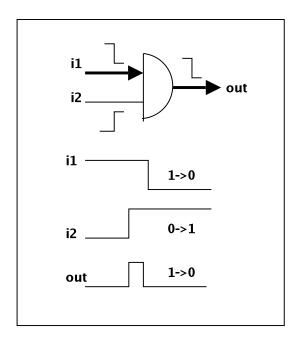

Failing to satisfy any of the  $a_i$  implies that P is combinationally false. In Fig. 2.3, it shows a 2-input AND gate with inputs  $i_1$  and  $i_2$  and output out. Let us consider the critical path section P ( $i_1$ , out) and the  $0 \to 1$  transition at  $i_1$ . If at the same time, the transition on  $i_2$  can only be  $1 \to 0$ , then out can not assume its final value 1. A delay of the  $0 \to 1$  transition along path p cannot manifest at the capture point.

Figure 2.3: False Path due to Violation of the After Value Criterion

On the other hand, failure to satisfy a given  $b_i$  does not necessarily make a timing path false. For example, in Fig. 2.4, for a 2-input AND gate, having inputs  $i_1$  and  $i_2$  and output out. Let us take the critical path  $\{i_1, out\}$  and the  $1 \to 0$  transition on both nodes. If  $i_1$ , which is on the critical path, is undergoing a  $1 \to 0$  and the side input,  $i_2$ , is undergoing a  $0 \to 1$  transition then the before value criterion is not satisfied. But if the transition on  $i_2$  happens before the transition on  $i_1$  (which is a possibility since the path  $\{i_1, out\}$  is the critical path) then there exists a functional test for this delay path. To account for the effect of the side inputs, the values in the before set only need to be checked when controlling values on the side inputs of the corresponding gates are assumed.

The following criteria take into consideration the violation of the  $before\ set$  when the side-nodes of path P have controlling values.

Figure 2.4: Effect of side-inputs

- $e_n$  = True iff respective non-controlling values can be assigned simultaneously at all side-nodes when evaluated in the current time frame,

- $e_{rb}$  = True iff  $x_i=b_i$  can be justified simultaneously in the previous time frame for every  $x_i$  where  $e_n$  is violated.

$e_n$  corresponds to the evaluation of non-controlling value criterion while  $e_{rb}$  corresponds to the evaluation of revised before value criterion.

Using this notation, the following algorithm, which we will refer to as algorithm A, was presented in [7], [80].

Given a path P with  $e_a$ ,  $e_{rb}$  and  $e_n$  if  $e_a = false$ , then

```

P is a false path (f_a)

else if e_n = true then

P is an active critical path

else if e_{rb} = false

then P is a false path (f_{rb})

else P is an active critical path

```

The labels in parenthesis represent the group of paths which are identified false at a particular step in the algorithm. We also call the false paths identified in algorithm A logically false paths since only logic information is utilized for FPI. If a path is not identified as logically false, we call it a logically active path. Besides logical false paths, there will be other kinds of false paths identified as shown later.

In the above algorithm, an *active* path is a path which has not been identified as a *false path*. An *active* path is not necessarily a true path since the algorithm only identifies combinational false paths at this point.

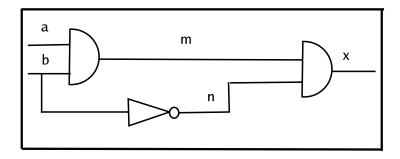

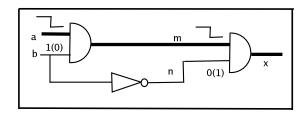

# 2.2.1 Example Circuit

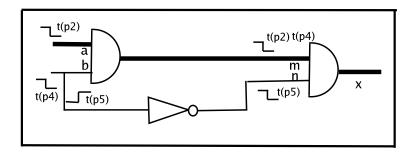

The circuit in Fig. 2.5 will be used to demonstrate the FPI process using logic path sensitization criteria. There are 6 paths in Fig. 2.5.

- $P_1$ : rising transition through nodes "a", "m", "x",

- $P_2$ : falling transition through nodes "a", "m", "x",

- P<sub>3</sub>: rising transition through nodes "b", "m", "x",

- $P_4$ : falling transition through nodes "b", "m", "x",

Figure 2.5: Example Circuit

- P<sub>5</sub>: rising transition through nodes "b", "n", "x",

- $P_6$ : falling transition through nodes "b", "n", "x".

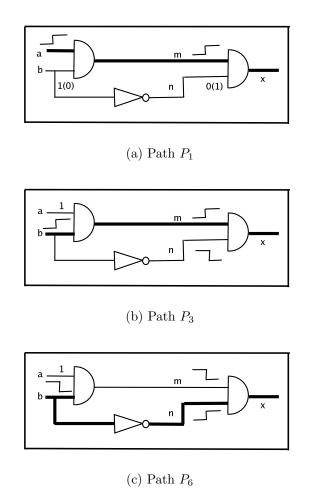

Based on algorithm A,  $After\ value\ criterion\ (e_a)$  is checked first. As a result, paths  $P_1$ ,  $P_3$ ,  $P_6$  are identified as false (Fig. 2.6), while path  $P_2$ ,  $P_4$ ,  $P_5$  are still considered active. non-controlling value criterion  $(e_n)$  is then checked. Paths  $P_4$  and  $P_5$  both satisfy  $e_n$  and can be tested non-robustly (Fig. 2.7). Path  $P_2$  violates  $e_n$ , but not revised before value condition  $(e_{rb})$  (Fig. 2.8). Based on logic sensitization criteria presented so far, path  $P_2$  is still an active path.

# 2.3 Slow Path Condition: False Path Identification Using Logic and Delay Information

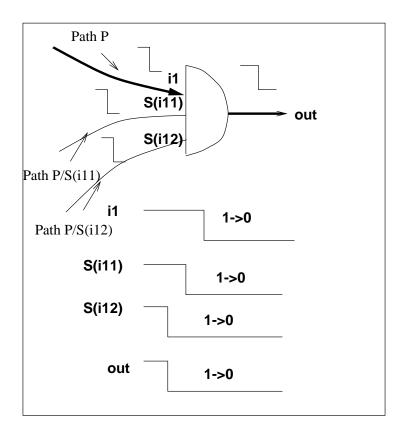

In general, due to reconvergent fanouts in the circuits, race conditions between timing paths exist. In Fig.2.9, both side input nodes of the AND gate S(i11), S(i12), along with the on-node  $i_1$ , transition from 1 (non-controlling value) to 0 (controlling value) of the AND gate. Here  $e_a$  and  $e_{rb}$  are satisfied for both the inputs and the output of the gate, but  $e_n$

is violated since S(i11) and S(i12) assume the controlling value during the current time frame.

In a **race condition**, more than one inputs of a gate on the path under consideration (PUC) transition from the NCV (non-controlling value) to the CV (controlling value). The input(s) of the gate in a race condition

Figure 2.6: Logical False Paths: Path  $P_1,\,P_3$  and  $P_6$

which are side-node(s) corresponding to the on-node  $n_i$  of the PUC are called  $S(n_{ij})$ . All the  $S(n_{ij})$  for a PUC form a set **SN**. The path which forms a race condition with the PUC at  $S(n_{ij})$  is called  $P/S(n_{ij})$ . All the  $S(n_{ij})$  corresponding to  $P/S(n_{ij})$  with longer delay than PUC form a set **SSN**. SSN is a subset of SN.

Figure 2.7: Non-Robust Testable Paths: Path  $P_4$  and  $P_5$

In Fig. 2.9, due to the race condition between the transitions of the paths associated with the inputs of the AND gate, the transition at the output of the gate is associated with that of the *faster* path. So unless the arrival times of the transitions associated with the side nodes of the AND gate,  $S(i_{11})$ ,  $S(i_{12})$  are slower than that associated with the on-node  $i_1$ ,

Figure 2.8: Path  $P_2$ : violates  $e_n$

the delay effect of the on-path will not be sensitized.

One way of deciding whether the transition associated with the onnode is sensitized, is to keep track of the arrival time information at each node during the race condition analysis. But since we have a timing report generated already, we can utilize the delay information of timing paths from the timing report efficiently.

Notice in Fig.2.9, since the path section from the output of the AND gate to the capture point is shared among all  $P/S(n_{11})$ ,  $P/S(n_{12})$  and P, a slower arrival time at the side node  $S(n_{11})$ ,  $S(n_{12})$  implies that paths  $P/S(n_{11})$ ,  $P/S(n_{12})$  have longer delays than path P.

Thus the condition when the on-path transition can be sensitized in a race condition can be checked based on the delay information of converging timing paths. For any timing path P, which may or may not be a main path, we have the following theorem.

**Theorem I**: A timing path P with race condition(s), is a false path if there is not a logically active  $P/S(n_{ij})$  of longer delay than P at any  $S(n_{ij})$ .

**Proof**: In Fig. 2.10, an "x" indicates a  $S(n_{ij})$  node.

Take for example, two side-nodes  $S(n_{11})$ ,  $S(n_{12})$  and the corresponding on-node  $n_1$  in a race condition. If either of the two side paths

Figure 2.9: Path with Race Condition

Figure 2.10: General Multiple Race Condition

$P/S(n_{11})$ ,  $P/S(n_{12})$  corresponding to  $S(n_{11})$ ,  $S(n_{12})$  has been identified as logically false, then it would not help to sensitize the transition of path P. If either of the two side paths  $P/S(n_{11})$ ,  $P/S(n_{12})$  corresponding to  $S(n_{11})$ ,  $S(n_{12})$  is of shorter delay than path P, it would kill the propagation of the transition on node  $n_1$ .

The same condition needs to be true for all  $S(n_{ij})$ s simultaneously, otherwise P is a false path.

$\square$ .

We call the condition defined in Theorem I the *Slow Path Condition*. The false paths identified based on the slow path condition are not logically false paths. Whether they can be sensitized depending on the delays of other logically active paths.

It is straightforward to reason that a main path with a race condition violates Theorem I.

**Corollary I.** A main path P with a race condition is false.

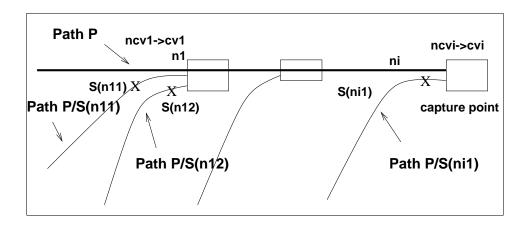

To check Theorem I, we can identify the exact locations of race conditions where  $e_a$ ,  $e_b$  are satisfied, but  $e_n$  is violated. We can then check if there are logically active paths of longer delays associated with these nodes. This can be expensive. Instead, we identify the upper bound of the locations of race conditions while allowing the PUC sensitization using efficient structural analysis as follows. First we have the following definition. Race condition intersection: an intersection node where path P forms race condition with one of its converging path P' based on the transitions propagated through path P and P'.

Corollary II. A timing path P with race condition(s) is false if a race condition happens at a node which is not among the race condition intersection nodes between path P and its converging paths with longer delays.

The converging paths of P with longer delays can be identified from the delay information in the timing report. Their race condition intersections with path P can be identified by comparing path nodes and checking the transitions along the paths.

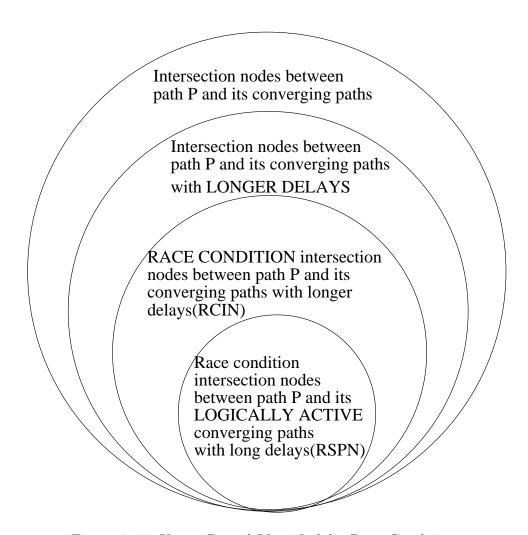

Corollary II avoids explicitly stating exactly where the race conditions are, but provides an upper limit for them for path P to be sensitized. We call this restricted subset of race condition intersection nodes **RCIN**.

If a converging path P' with longer delay is logically false, it cannot help propagate path P at their intersection node(s). A path P with race conditions is false if none of its converging paths with longer delays is logically active. Thus we have Corollary III.

**Corollary III.** A timing path P with race conditions is false if the corresponding converging paths of RCIN nodes are not logically active paths.

We call the FPI condition defined by Corollary II, III a revised slow path condition since it does not attempt to identify the exact locations of race conditions, only the upper bound. We called the final upper bound identified using the above corollaries **RSPN**. Fig. 2.11 illustrates the boundary of **RSPN**.

Figure 2.11: Upper Bound Identified for Race Conditions

# 2.4 Improved False Path Identification Algorithm

Besides  $e_a$ ,  $e_{rb}$ , and  $e_n$  already defined while describing Algorithm A, we have the following additional definitions.

- $e_s$  = True iff the set RSPN is non-empty,

- $e_{rn}$  = True iff respective NCVs can be assigned simultaneously at non- $S_n$  nodes.

Item  $e_s$  is for the evaluation of the revised slow path criterion, while  $e_{rn}$  is for the evaluation of the revised non-controlling value criterion.

We check if RSPN is empty when  $e_n$  is violated, to see if there are race condition locations which *still allow* timing path P to stay *sensitizable*.

Corollary IV. A timing path P which violates  $e_n$  is false if RSPN is empty.

In Corollary IV, when  $e_n$  is violated:

- either  $e_a$ ,  $e_{rb}$  is violated also, thus P is a logic false path,

- or race condition exists. Since RSPN is empty, P is a false path.

Additional logic checks need to be performed at nodes outside RSPN to further perform FPI on path P.

Corollary V. A timing path P is false if  $e_{rn}$  is not satisfied for all of its side-nodes outside RSPN.

Corollary IV, V allow efficient identification of a false path without specifying the exact cause of it being false. This allows earlier and more efficient identification of false paths.

Given a path P with  $e_a$ ,  $e_s$ ,  $e_{rn}$  and  $e_{rb}$ , Fig. 2.12 shows our improved algorithm B. The labels in parenthesis represent the group of paths which are identified false at a particular step in the algorithm.

The main advantages over algorithm A are the following.

- Additional false paths  $(f_s \text{ and } f_{rn})$  are identified.

- The simultaneous checking of the satisfiability of  $e_n$  and  $e_a$  to ensure that a specific transition can be sensitized.

- The locations where  $e_{rb}$  is checked are identified efficiently using the corollaries which do not take additional ATPG run time, compared to being checked exactly where  $e_n$  is violated in algorithm A.

- The checking of  $e_{rn}$  after  $e_s$  is done at a node  $\notin RSPN$

- Paths which fail  $e_{rb}$  can be identified false as early as during the checking of  $e_s$ .

## 2.4.1 Example Circuit

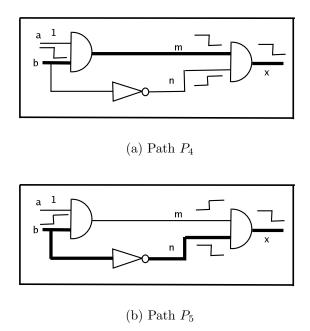

We reconsider the circuit in Fig. 2.5. The checking of After value Criterion and Non-Controlling Value Criterion in our improved algorithm B remains the same as that in algorithm A. We conclude that paths  $P_1$ ,  $P_3$  and  $P_6$  are false paths, while paths  $P_4$  and  $P_5$  can be tested non-robustly.

```

if e_a = false, then P is false(fa)

else

if e_a and e_n are true, then P stays active

else

if e_s = false, then P is false(fs)

elsif e_r = false, while e_s is true

then P is false(frn)

elsif e_{rb} = false, while e_{rn}, e_s are true

then P is false(frb)

else P stays active

```

Figure 2.12: Algorithm B

Path  $P_2$  is identified to violate  $e_n$ . To further decide whether path  $P_2$  is a false path, we need to utilize timing information. We will analyze timing information under several scenarios.

Since there is only a single output of the circuit, all the paths from the input signals converge at the output. Based on the transitions at the path nodes, path  $P_2$  could form race conditions with path  $P_4$  and  $P_5$  at node "b", "n" (Fig. 2.13). The transitions associated with paths  $P_2$ ,  $P_4$  and  $P_5$  are labeled in Fig. 2.13. For example, at node "m", path  $P_2$  and  $P_4$  converge. The falling transition at node "m" is labeled with  $t(p_2)$  and  $t(p_4)$ .

Even though the potential race conditions at node "b" and "n" could not happen simultaneously, that information is functional and is

not available to timing analysis tool. Note both path  $P_4$  and  $P_5$  are non-robustly testable, thus *logically active*. Consider the following scenarios of timing information.

- 1. if path  $P_2$  is the main path at the output port, i.e., it has the worst case timing out of all the converging paths, then revised slow path criterion is violated ( $e_s$  is false). As a result, path  $P_2$  is false.

- 2. if path  $P_2$  is faster than either  $P_4$  or  $P_5$  or both, revised slow path criterion ( $e_s$  is satisfied) path  $P_2$  is active.

Figure 2.13: Path  $P_2$  and Converging Paths:  $P_4$  and  $P_5$

We see since path  $P_2$  violates  $e_n$ , whether it stays active depends on its timing relative to other timing paths.

## 2.4.2 Efficiency of Revised Slow Path Criterion

Revised slow path condition identifies the upper bound of locations where race conditions could happen. This is especially true for our example circuit since race conditions could not happen simultaneously at nodes "b" and "n" due to the logic of the circuit.

To appreciate the efficiency of our revised slow path criterion, we perform the following calculation. Suppose a path P with 15 path nodes. Only 4 of the intersecting path nodes of path P with other converging paths, transition from NCVs to CVs of the corresponding gates. These are fairly reasonable, conservative numbers based on the timing analysis of the industrial circuit we experimented with. We need to perform the following logic checking if we are to determine exactly where the race condition(s) happen.

- Assume exactly 1 out of 4 intersecting path nodes forms race condition with another converging path (4).

- Assume exactly 2 out of 4 intersecting paths nodes form race conditions with 2 other converging paths (6).

- Assume exactly 3 out of 4 intersecting path nodes forms race conditions with 3 other converging paths (4).

- Assume exactly 4 out of 4 intersecting path nodes forms race conditions with 4 other converging paths (1).

The numbers in the parentheses are for the number of logic checks that need to be performed. We would need to perform a total of 15 (4 + 6 + 4 + 1) logic checks to determine the exact locations of race condition before checking whether the timing information at these race condition locations satisfy the *slow path condition* requirements. We can see that the number of logic checks required for *slow path condition* can quickly add up and become prohibitively expensive.

It should be noted that if we still decide to determine the exact locations of the race conditions after the tight upper bound of these locations is identified using *revised slow path condition*, the number of corresponding logic checking would be much reduced.

# 2.4.3 The Effectiveness and Limitation of Revised Slow Path Criterion

In order to make sure timing requirements are met at all the capture points of a circuit, the timing path with the worst delay at each capture point, i.e., main path, is included in the timing analysis report. For each corresponding capture point, other converging paths with differences in timing slacks from that of the main path within a given threshold are also included in the timing analysis report.

When handling the timing paths with worst timing slacks at each capture point, revised slow path criterion prove to be very effective as will be shown in our experimental results. We can normally identify tighter upper bounds for race condition locations for a timing path P, compared to just the intersecting path nodes of path P with other converging paths, transitioning from NCVs to CVs of the corresponding gates.

On the other hand, the lower the rank of a timing path P is, or the faster a timing path is, the less effective the criterion is. There is because there would be many timing paths which are slower than path P, which converge at the same capture point. As a result, an upper bound of race condition locations could not be achieved as effective as in the case of more critical timing paths. Notice the application of our criterion is for false timing path identification of critical timing paths where optimization of false paths is a more pressing issue.

# 2.4.4 Timing Accuracy

The comparison of timing slacks of paths depends on how accurately delays are estimated. A threshold is needed to estimate how close the timing slacks of two timing paths can be and still be differentiated. In a race condition, if timing path  $P_1$  has a slightly faster timing than  $P_2$ ,  $P_1$  might still be able to activate  $P_2$  if  $P_1$  ends up with slower timing in real silicon. To accurately determine the threshold in timing analysis which can also be used to differentiate two timing paths in silicon, correlation of timing prediction of timing paths in timing analysis and timing measurement of the corresponding paths in real silicon needs to be established.

# 2.5 A More Efficient Version of the Improved Algorithm

In the first two steps of Algorithm B, logic checking of  $e_a$  and the satisfiability of  $e_a$ ,  $e_n$  simultaneously is carried out before the structural checking  $e_s$ . To minimize ATPG run time, we need to minimize the amount of logical checking and perform the structural checking as early as possible. We observe that the set of timing paths which fail the simultaneous satisfaction of  $e_a$  and  $e_n$  is the upper bound of all the false timing paths we identified in algorithm B.

With  $e_a$ ,  $e_s$ ,  $e_{rn}$  and  $e_{rb}$ , we propose algorithm C (Fig.2.14) for path P. Similarly, the labels in parenthesis represent the group of paths which are identified false at a particular step in the algorithm. The main efficiency advantage of algorithm C over Algorithm B is that the upper bound of all

```

if e_a and e_n are true,

then P stays active

else

if e_s = false, then P is false(fs)

elsif e_a = false, while e_s is true

then P is false(fa)

elsif e_{rn} = false, while e_a, e_s are true

then P is false(frn)

else

if e_{rb} = false, the P is false(frb)

else P stays active

```

Figure 2.14: Algorithm C

the false paths is identified by  $e_a$  and  $e_n$ . This reduces the amount of paths that need be checked by further logic conditions, especially  $e_a$ . As in algorithm B, the upper bound is further reduced by checking  $e_s$ .

Note that we perform  $e_s$  on more timing paths in algorithm C than in algorithm B. This trade-off is minimal for structural analysis. Also, paths which fail  $e_a$  by itself and  $e_b$  can be identified as early as during the checking of  $e_s$ .

# 2.6 Bridging the Gap between the Physical Design and Testing Model

To check criteria  $e_a$ ,  $e_{rb}$  and  $e_{rn}$ , we can set the corresponding values at the nodes along the path simultaneously using commands in the ATPG

# IN1 I1(AND2) din0 out din1 I2(NOR2) din0 out din1 OUT

Figure 2.15: Ports of Custom Design Blocks

tool. In the current methodology, most of the pre-characterized design blocks are not gate level primitives understood by the ATPG tool. To specify the nodes which are ports for these design blocks, we analyze the gate-level models for the blocks to determine the gate primitives inside the blocks which are connected to these ports.

We implemented a path extractor which analyzes all of the custom designs and extracts all of the paths associated between each pair of input/output pins in a design.

For example, the design block in Fig. 2.15 is not a gate-level primitive. It contains gate-level primitives  $I_1$ ,  $I_2$  and  $I_3$ . Its input/output pins  $IN_1,IN_2$  and OUT would then be specified as the following.

- 1.  $IN_1$ : /I1/din0, where din0 is an input port for I1,

- 2.  $IN_2$ : /I2/din0, where din0 is an input port for I2,

### 3. OUT: /I3/out, where out is an output port for I3.

There are 2 paths between IN1 and OUT, one is activated when IN2 is 0, the other when IN2 is 1. Our path extractor would extract both. We call a timing path with only library components along it a fully specified **logic path**. A timing path through a complex custom design can correspond to more than one logic paths. We will not label such a timing path false unless we can identify every one of its logic paths to be false. In this way, we are being conservative.

# 2.7 Experimental Results

We considered a circuit as being consisted of sub-circuits and RC networks. The timing behaviors of the sub-circuits were pre-characterized under numerous environmental parameters using transistor-level simulation. The RC nets were for the estimation of interconnect timing behavior using an extraction tool. Timing analysis was then performed on the whole chip. The output of the timing analysis consisted of a set of critical paths.

We show our results on latch to latch timing paths, but our techniques are generally enough to identify any type of false timing path. The output of the timing analysis consisted of a set of critical paths along with the transition for every node on each path. Our FPI engine post-processed the generated outputs from the timing analyzer.

Our FPI engine translated timing paths into delay paths for ATPG tools [80]. It checked the satisfiability of different criteria for the path by setting the corresponding values at the nodes along the path simultaneously using the ATPG tool commands. Based on the status returned after

running the ATPG tool with command files, we used our FPI engine again to identify a list of false paths. For further logic checking, additional command files were fed to the ATPG tool and the log files from the ATPG tool were analyzed.

| # of Transistors | Frequency | # of IO pins | # of latches | Stuck-at faults |

|------------------|-----------|--------------|--------------|-----------------|

| 33 million 1Ghz+ |           | 281          | 90k          | 6.2M            |

Table 2.1: Statistics for MPC7455

We ran our experiments on the circuit description for the MPC7455 microprocessor. Statistics are shown in Table 2.1. All runs were performed on a 400MHz Ultra60 running Solaris 5.6 with 1GB memory. Three sets of most critical timing paths were generated using the timing analyzer. We simplified the issue by analyzing only most critical latch to latch timing paths, but it was straightforward to extend the analysis to other kinds of paths. The cycle time target was 950ps. The threshold for generating subpaths was 3ps. The threshold for differentiating between the timing slacks of two timing paths was set to be 0.5ps. Any two timing paths with timing slacks of less than 0.5ps difference were considered to be of comparable delay. False paths identified in different groups following the convention described earlier are shown in Table 2.2.

Our additional checking of  $f_s$  and  $f_{rn}$  was effective in identifying false paths. This highlights the need of taking into consideration delay information of the paths besides logic value justification when performing FPI. The last column in Table 2.2 shows the number of false paths identified using algorithms B and C, both utilizing  $f_s$  and  $f_{rn}$ , over algorithm

|          |                    |    |    |    |    |    |                | False Path  |    |        |

|----------|--------------------|----|----|----|----|----|----------------|-------------|----|--------|

| Latch to | ${\bf Algorithms}$ |    |    |    |    |    | Identification |             |    |        |

| latch    |                    |    |    |    |    |    |                | improvement |    |        |

| timing   | A                  | В  |    |    | С  |    |                | of B, C     |    |        |

| paths    | fa                 | fa | fs | fn | fb | fs | fa             | fn          | fb | over A |

| 61       | 6                  | 6  | 9  | 5  | 0  | 12 | 3              | 5           | 0  | 3.3    |

| 332      | 26                 | 26 | 36 | 6  | 0  | 54 | 8              | 6           | 0  | 2.6    |

| 566      | 54                 | 54 | 56 | 6  | 0  | 95 | 15             | 6           | 0  | 2.1    |

Table 2.2: False Paths Identified using Different Algorithms

A. At least twice as many false paths were identified using  $f_s$  and  $f_{rn}$ , or at least 10% additional false timing paths out of the total timing paths analyzed in all three sets of latch to latch timing paths. Note that only  $f_a$  was identified in algorithm A since identifying  $f_{rb}$  without structural analysis information was expensive.

We can see that the number of false paths in different columns identified using algorithm C were different from those identified using algorithm B. Structural analysis  $e_s$  was performed earlier in algorithm C allowing it to identify false paths which were under category  $f_a$  in algorithm B. This results in the number under the  $f_a$  using algorithm C being much less than that using algorithm B. The number of timing paths which needed to be checked using  $f_a$  was also reduced. In general, algorithm C performed much less logic checking than algorithm B, thus algorithm C took much less time than algorithm B since the run time of the algorithms mainly came from running the ATPG tool for logical checking. The run time for

the 3 sets of timing paths was listed in Table 2.3. The ATPG abort limit was set to 100.

| latch to latch timing paths | A (mins) | B (mins) | C (mins) |

|-----------------------------|----------|----------|----------|

| 61                          | 30       | 63       | 33       |

| 332                         | 68       | 141      | 73       |

| 566                         | 94       | 195      | 101      |

Table 2.3: Comparison of Algorithms

We see algorithm C requires comparable amount of time to algorithm A, which is about 50% of what it took for algorithm B. With a set abort limit, in the worst case, the overall run time scaled linearly with the total number of paths. If the logic checking for most timing paths took much less time than the abort limit, the ratio of overall run time for two sets of timing paths could be smaller than the ratio of the numbers of timing paths of two different runs. From Table 2.3, between the first two data groups, the ratio of timing path number was 5.4 (332/61), while the ratio of run time was 2.3. The same was true for comparison between all of the data groups. The loading of the gate-level model required around 1 hour and was not included in the run time since it was an one-time cost and was the same for all algorithms.

# 2.8 Conclusions

We demonstrate new techniques to perform false path identification utilizing both logic and delay-based information of the paths in the circuit. We were able to identify at least 20% false paths out of latch to latch main paths and subpaths within the different groups of timing paths. The false

path identification criteria using delay-based information identify at least 10% more false paths out of all the latch to latch timing paths.

Our algorithms can be applied using any commercial ATPG tool and utilizing timing information from any static timing analyzer. Our algorithm using delay-based information is particularly effective for identifying the false paths among the most critical timing paths where most optimization efforts are spent.

# Chapter 3

# Correlating Structural Tests with Functional Tests for Speed Binning

# 3.1 Definition of Speed Binning

In general, the purpose of testing is to bin the tested ICs based on certain criteria. Most of the research and industry work on testing has focused on binning to identify defective ICs. Binning requires an efficient and affordable mechanism to categorize the ICs. The mechanism to evaluate the ICs needs to correlate with the characteristic that the tester wishes to identify.